второго сумматора, а третий вход бло1ка сравнения соединен с первыми входами первого и второго сумматоров и блока управления, второй вход второго сумматора соединен с вторым входом первого сумматора и информационным входом третьего коммутатора, а третий вход вторЬго сумматора сое-: динен с вторым входом первого сумматора и информационным входом третьего коммутатора, а третий вход второго сумматора подключен к выходу второго блока умножения, первый и второй входы которого соответственно через второй функциональный) и аналого-цифровой преобразователи подключены к выходам первого сумматора И цифро-аналогового преобразователя, третий вход первого сумматора соединен с выходом второго регистра памяти и объединен с третьим входом блока управления, а четвертый, вход первого сумматора подключен к выходу первого регистра памяти, первый и второй входы которого соединены соответственно с четвертым входом блока управления и выходом датчика случайных чисел.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор случайного процесса | 1982 |

|

SU1068935A1 |

| Генератор случайного процесса | 1981 |

|

SU972505A1 |

| Генератор случайного процесса | 1981 |

|

SU1015381A1 |

| Анализатор спектра Фурье | 1984 |

|

SU1226486A1 |

| Устройство для формирования случайных процессов с заданным спектром | 1981 |

|

SU1027723A1 |

| Устройство для вычисления спектра Фурье | 1983 |

|

SU1121678A1 |

| Способ воспроизведения случайной вибрации с заданным спектром плотности мощности и устройство для его осуществления | 1988 |

|

SU1518691A1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1988 |

|

SU1640710A1 |

| Цифровой двоичный коррелометр | 1979 |

|

SU832561A1 |

| Цифровой анализатор спектра | 1987 |

|

SU1413545A1 |

1

Изобретение относится к вычислительной технике и может быть использовано для имитации случайных процессов с заданными и программно управляемыми спектральными характеристиками в вычислительно-моделирующих комплексах для управления испытаниями изделий электронной и другой техники на механические, электрические и другие воздействия, а также при построении моделирующей аппаратуры для исследования и оптимизации структурно-сложных систем.

Известен генератор случайного процесса, содержащий формирующие фильтру для придания случайному процессу требуемых спектральных свойста Управление спектральной плотностью мощности случайного процесса на выходе таких генераторов выполняется изменением частотной характеристики формирующих фильтров Л.

Однако с практической точки зрения проектирование и изготовление формирующих фильтров с перестраиваемой в широком диапазоне частотной характеристикой представляет собой достаточно трудную техническую задачу. .

Известно также устройство, использующее для формирования выходного случайного процесса множество импульных потоков, содержащее множество генераторов импульсов, элементы И, элементы ИЛИ и некоторые другие вспомогательные элементы 2. .

Процесс на выходе такого генератора представляет собой последовательность импульсных сигналов определенной формы, следующих через случайные интервалы времени, причем управляемой статистической характеристикой выходного случайного процесса является закон распределения возможности использования их для генерирования случайного процесса с заданными спектральными характеристиками, так как определить требуемую функ цию распределения случайных временных интервалов по заданной спектральной плотности мощности оказывается затруднительным как из-за сложности

математических преобразований, так и из-за ограниценности класса воспроизводимых плотностей мощности.

Наиболее близким техническим решением к предлагаемому является устройство, содержащее три блока памяти, три коммутатора, блок быстрого преобразования Фурье, блок умноженияj датчик случайных чисел, функциональный преобразователь, блок формирования интервалов времени, цифро-аналоговый преобразователь, блок управления и соответствующие связи.

Данное устройство позволяет получать на выходе случайный процесс вибрационного типа с заданными спектральными характеристиками З.

Недостатком устройства является невысокая надежность функционирования, так как в нем не приняты специ-альные меры для обнаружения ошибок.

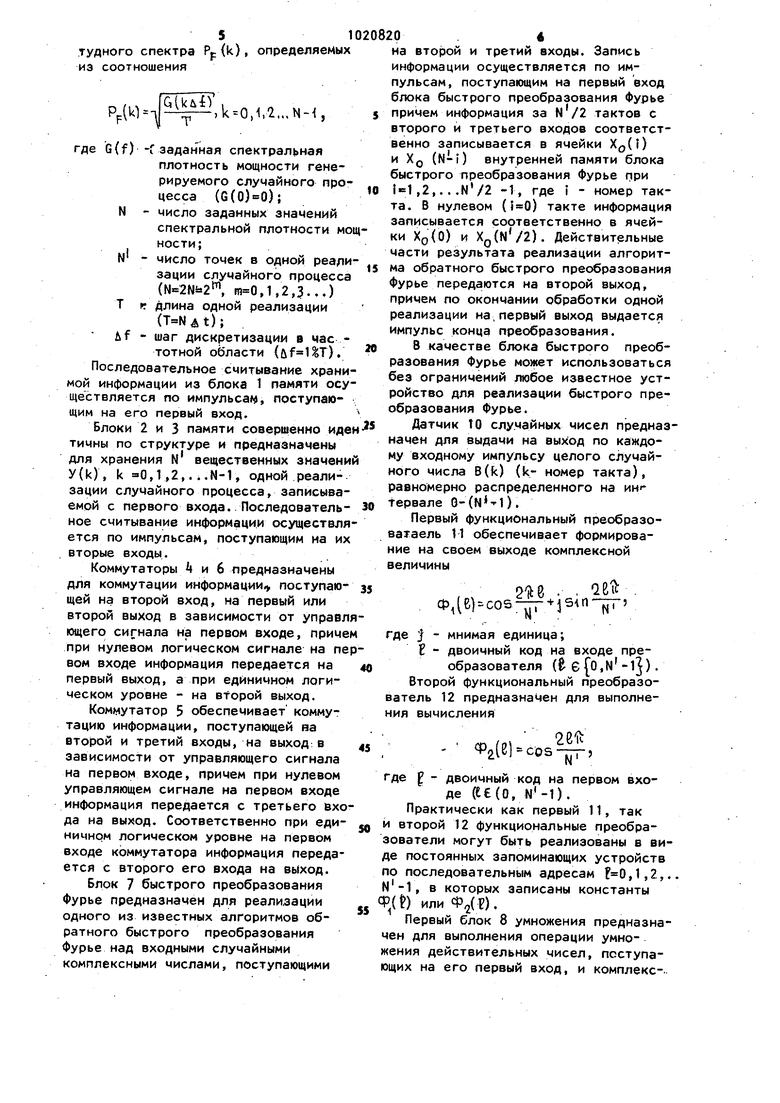

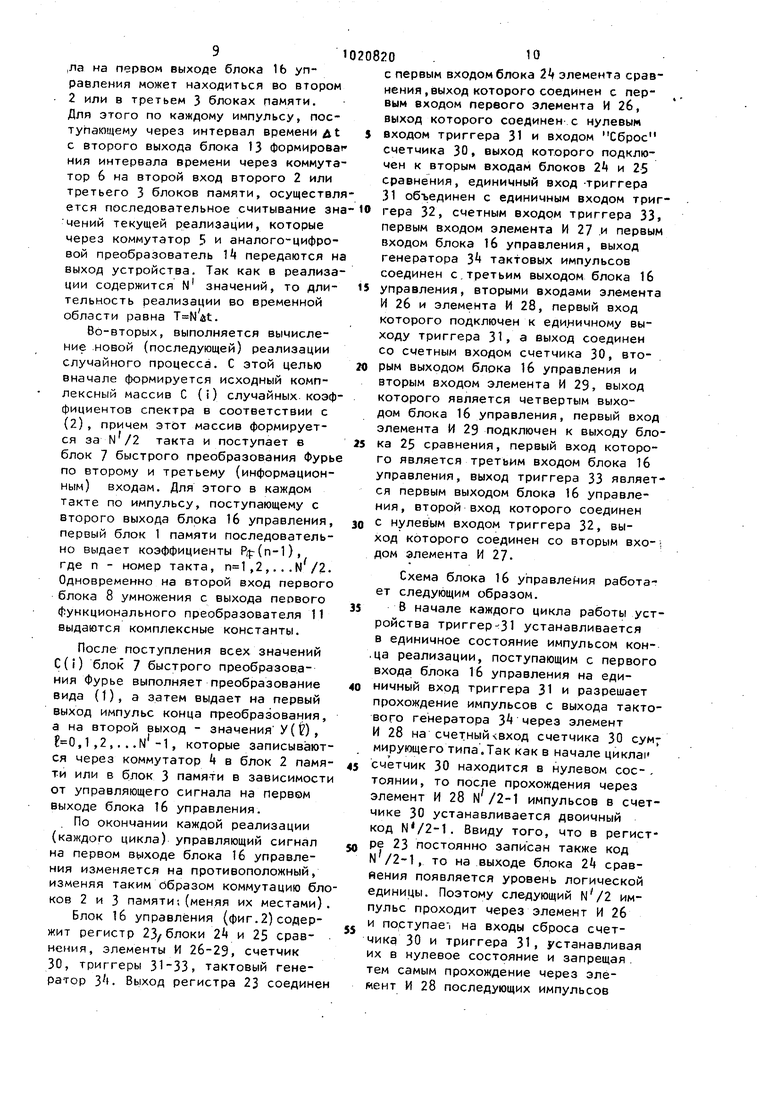

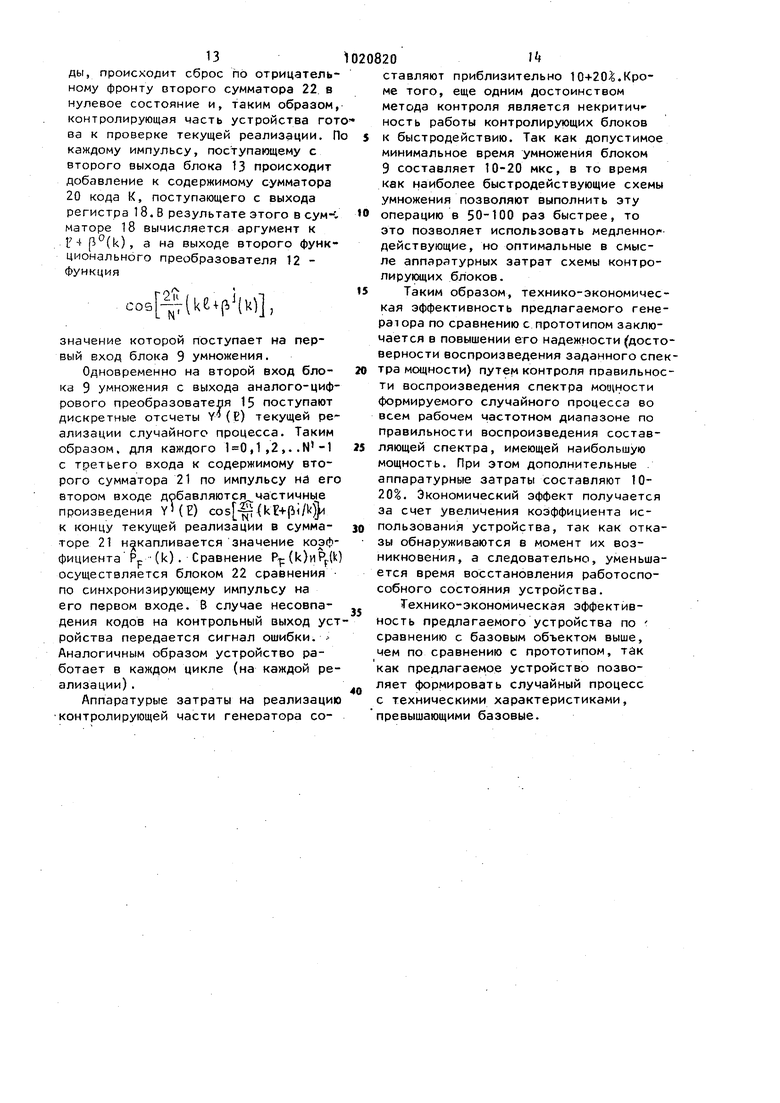

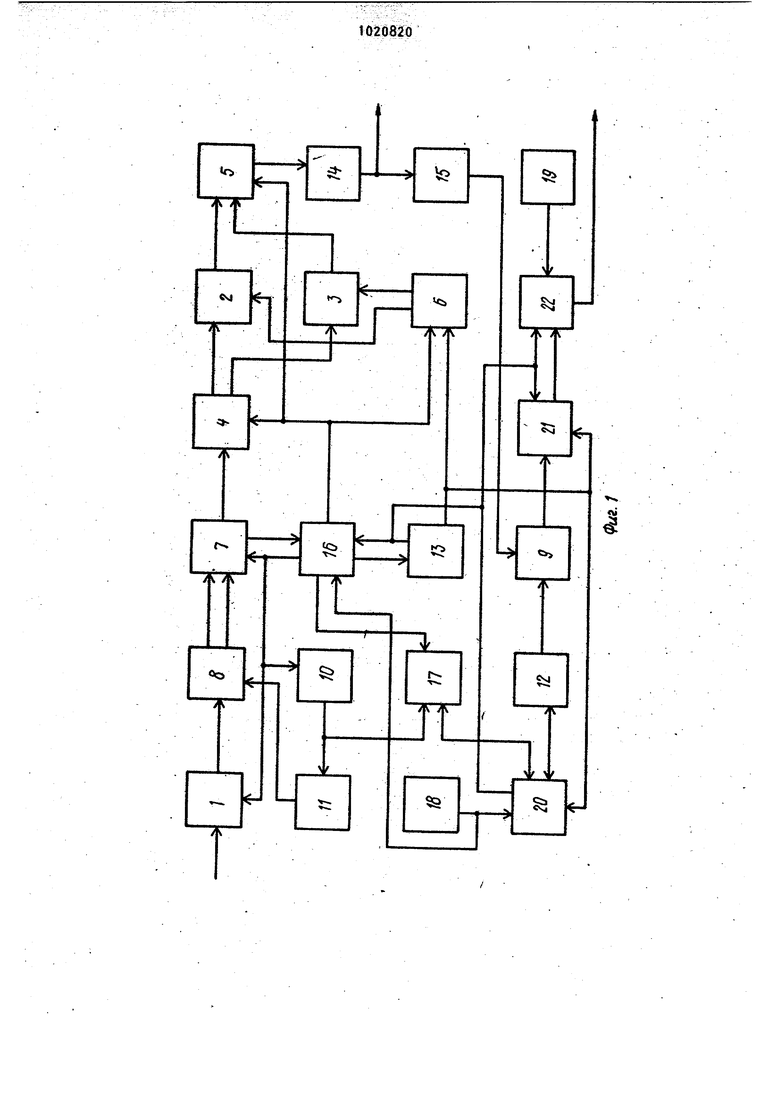

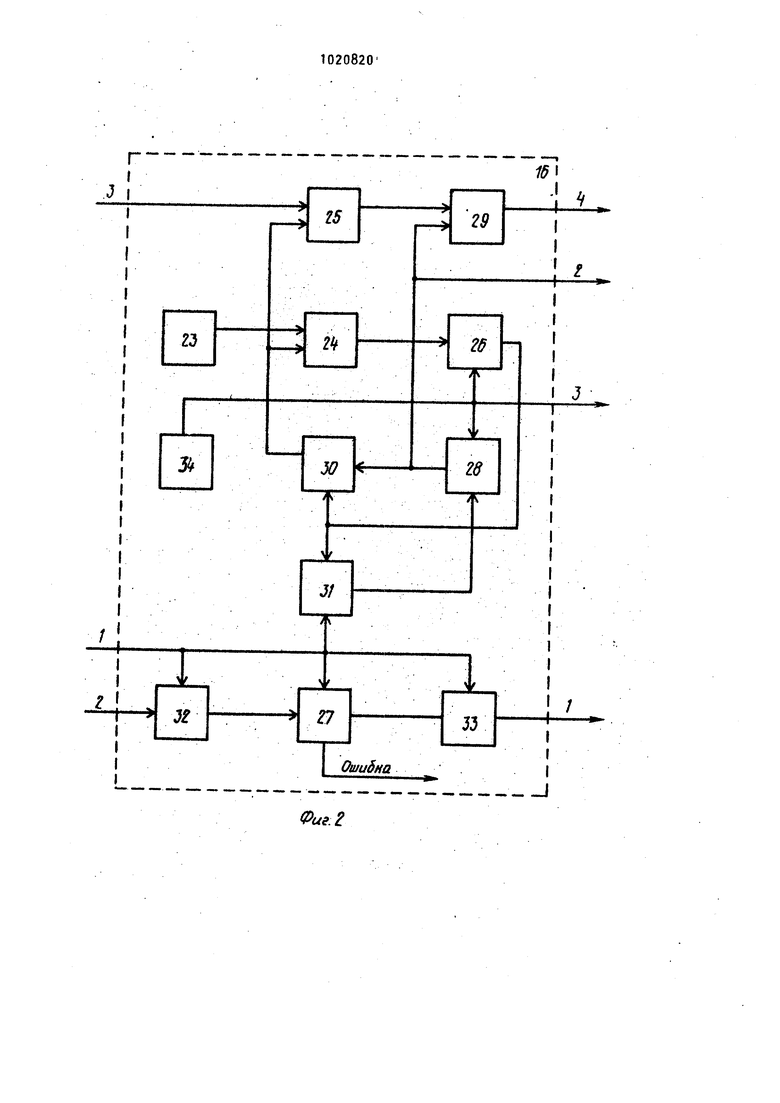

Цель изобретения - повышение надежности функционирования устройства путем контроля правильности воспроизведения спектральной плотности мощ ности формируемого случайного процесса во всем рабочем диапазоне час тот по одной составляющей спектра,, имеющей наибольшую мощность. Поставленная цель достигается те Что в устройство, содержащее три бл ка памяти, три коммутатора, первый блок умножения, блок быстрого преоб разования Фурье, датчик случайных ч сел, первый функциональный преобраз ватель, блок формирования интервало времени, цифро-аналоговый преобразователь и блок управления, входом г нератора является информационный .вход первого блока памяти, управляю щий вход которого объединен с входо датчика случайных чисел и первым вх дом блока быстрого преобразования Фурье и подключен к первому выходу блока управления, первый и второй входы которого соединены с первыми выходами- соответственно блока форми рования интервалов времени и блока быстрого преобразования Фурье, второй выход блока управления соединен с управляющими входами первого, вто рого и третьего коммутаторов, первы и второй входы первого блока умноже ния: подключены соответственно к выходам первого блока памяти и первого функционального преобразователя , вход которого подключен к вых ДУ датчика случайных чисел, а первый и второй выходы первого блока умножения подключены соответственно к второму и третьему входам блока быстрого преобразования Фурье, второй выход которого соединен с информационным входом первого коммутатора, первый и второй выходы которого соединены с информационными входами соответственно второго и третьего блоков памяти, выходы которых подключены соответственно к первому и второму информационным входам второго коммутатора, выход которого соединен с входом цифроаналогового преобразователя, выход которого является выходом генератора, вход блока формирования интер валов времени подключен к третьему выходу блока управления, а второй выход блока формирования интервалов времени соединен с информационным входом третьего коммутатора, первый и второй выходы которого соединены с управляющими входами соответ ственно второго и третьего блоков памяти, дополнительно введены аналого-цифровой преобразователь, первый второй, третий регистры памяти, второй функциональный преобразователь, второй блок умножения, первый и второй сумматоры и блок сравнения, выход которого соединен с контрольным выходом генератора, первый и второй рходы блока сразнения соединены соответственно с выходами третьего регистра памяти и второго сумматора, а третий вход блока сравнения соединен с первыми входами первого и второго сумматоров, и блока управления, второй вход второго сумматора соединен с вторым входом первого сумматора и информационным входом третьего коммутатора, а третий вход второго сумматора подключен к выходу второго блока умножения, первый и второй входы которого соответственно через второй функциональный и аналого-цифровой преобразователи подключены к выходам первого сумматора и цифроаналогового преобразователя, третий вход первого сумматора соединен с выходом второго регистра памяти и объединен с третьим входом блока управления, а четвертый вход первого сумматора подключен к выходу первого регистра памяти, первый и второй входы которого соединены соответственно с четвертым входом блока управления и выходом датчика случайных чисел. На фиг.1 представлена структурная схема генератораJ на фиг.2 - пример схемной реализации блока управления; на фиг.З - схема блока формирования интервалов времени. . Устройство содержит блоки 1-3 памяти, коммутаторы ki6, блок 7 быстрого преобразования Фурье, первый 8 и второй 9 блоки умножения, датчик 10 случайных чисел, первый 11 и второй 12 функциональные преобразователи, блок 13 формирования.интервалов времени, цифро-аналоговый I и аналого-цифровой 15 преобразователи, блок 16 управления, первый 17, второй 18 и третий 19 регистры памяти, первый 20 и второй 21 сумматоры, блок 22 сравнения. Функциональное назначение структурных элементов устройства следующее. Первый блок 1 памяти предназначен для приема с его функционального входа и хранения коэффициентов амплитудного спектра ), определяемых из соотношения Pp(,k 0,1,2...N4, где G(f) -заданная спектральная плотность мощности генерируемого случайного про цесса {G(0)0); N - число заданных значений спектральной плотности мо ности; N - число точек в одной реали зации случайного процесса (, ,1,2,3...) Т к длина одной реализации (); if - шаг дискретизации в частотной области ), Последовательное считывание храни мой информации из блока 1 памяти осу ществляется по импульса, поступающим на его первый вход. Блоки 2 и 3 памяти совершенно иде тичны по структуре и предназначены для хранения N вещественных значени y{k), k 0,1,2,.i.N-1, одной реализации случайного процесса, записываемой с первого входа. .Последовательное считывание ин юрмации осуществля ется по импульсам, поступающим на их вторые входы. Коммутаторы 4 и 6 предназначены для коммутации информации поступающей на второй вход, на первый или второй выход в зависимости от управл ющего сигнала на первом входе, приче при нулевом логическом сигнале на пе вом входе информация передается на первый выход, а при единичном логическом уровне - на второй выход. Коммутатор 5 обеспечивает коммутацию информацией, поступающей на второй и третий входы, на выход:в зависимости от управляющего сигнала на первом входе, причем при нулевом управляющем сигнале на первом входе информация передается с третьего вхо да на выход. Соответственно при единичном логическом уровне на первом входе коммутатора информация передается с второго его входа на выход. Блок 7 быстрого преобразования Фурье предназначен для реализации одного из известных алгоритмов обратного быстрого преобразования Фурье над входными случайными комплексными числами, поступающими на второй и третий входы. Запись информации осуществляется по импульсам, поступающим на первый вход блока быстрого преобразования Фурье причем информация за N /2 тактов с второго и третьего входов соответственно записывается в ячейки X(i) и XQ (N-i) внутренней памяти блока быстрого преобразования Фурье при ,2,...N/2 -1, где I - номер такта. В нулевом () такте информация записывается соответственно в ячейки Хо(0) и XQ(N/2). Действительные части результата реализации алгоритма обратного быстрого преобразования Фурье передаются на второй выход, причем по окончании обработки одной реализации на,первый выход выдается импульс конца преобразования. В качестве блока быстрого преобразования Фурье может использоваться без ограничений любое известное устройство для реализации быстрого преобразования Фурье. Датчик ТО случайных чисел предназначен для выдачи на выход по каждому входному импульсу целого случайного числа B(k) (k- номер такта), равномерно распределенного на ин тервале 0-(). Первый функциональный преобразоватаель 11 обеспечивает формирование на своем выходе комплексной величины 2118 .,261. . ФДе)--со&- - 55 п-1Г где J - мнимая единица; Е - двоичный код на входе преобразователя ( ,N-i5). Второй функциональный преобразователь 12 предназначен для выполнения вычисления 2(21 cos Где - двоичный код на первом входе (е(0, N-l). Практически как первый 11, так и второй 12 функциональные преобразователи могут быть реализованы в вие постоянных запоминающих устройств о последовательным адресам ,1,2,.. -I, в которых записаны константы { t) или (). Первый блок 8 умножения предназнаен для выполнения операции умноения действительных чисел, поступащих на его первый вход, и комплексных чисел, поступающих на второй гход, причем на второй выход результат умножения выдается в комплексносопряженном виде по отношению к первому выходу. Второй блок 9 умножения обеспечивает перемножени.е двоичных кодов, по ступающих на его первый и второй входы. Блок 13 формирования интервалов времени предназначен для формирования на первом и втором выходах регулярной последовательности импульсов с периодами следования соответст венно Nut и ut Cut - шаг дискретизации случайного процесса во временной области). Синхронизация работы блока 13 осуществляется входной импульсной последовательностью. Практически блок 13 представляет собой обычную пересчетную схему. Цифро-аналоговый преобразователь предназначен для представления входного дискретного случайного процесса в аналоговой форме. . Аналого-цифровой преобразователь 15 осуществляет обратное преобразование выходного аналогового случайно го процесса в дискретную форму. Блок 1б управления осуществляет общую синхронизацию работы устройства. Регистр 17 памяти предназначен дл записи и хранения информации, поступающий на второй В.ХОД. Запись информации синхронизируется импульсом, по тупающим на первый вход. Регистр 18 памяти хранит номер k коэффициента заданного амплитудного спектра, имеющего наибольшее значени т.е. выполняется условие Рр (k) РрСг), (kjtr). Регистр 19 памяти хранит значение наибольшего коэффициента PrCk) ампли тудного спектра. Первый 20 и второй 21 сумматоры накапливающего типа предназначены дл суммирования кодов, поступающих на их третьи входы. Выполнение операции синхронизируется импульсами на второ входе. Установка сумматора в исходное состояние осуществляется импульсами, поступающими на их первые входы, причем исходное состояние второго сумматора 21 является нулевым, а исходное состояние первого сумматора 20 определяется кодом на его четвертом входе. Блок 22 сравнения осуществляет сравнение двоичных кодов, поступаюих на второй и третий входы при разрешающем сигнале на первом входе. Предлагаемый генератор случайного процесса можно разделить на две части: контролируемую и контролирующую. Контролируемая часть предназначена для формирования случайного процесса и включает блоки памяти 1-3, коммутаторы k-(, блок 7 быстрого преобразования Фурье, первый блок 8 умножения, датчик 10 случайных чисел первый функциональный преобоазователь 11, блок 13 формирования интервалов времени, цифро-аналоговый преобразователь 1, блок 16 управления. Работа контролируемой части устройства полностью совпадает с работой прототипа и происходит следующим образом. Случайный процесс на выходе генератора представляет собой последовательность реализаций длительностью каждая. Алгоритм формирования одной реализации случайного процзсса представляется в виде преобразования С - РоБпф-У (1) где С - исходный массив комплексных коэффициентов спектра, состоящий из элементов C(i), ,1,2,... N -1, (для каждой реализации вычисляется новый массив с); обпф оператор обратного быстрого преобразования Фурье; У - выходной случайный массив (реализация случайного процессе), со ст.оящий из действительных элементов У(), 0,1,2,.... С целью облегчения описания работы устройства введем понятие цикла под которым будем понимать интервал времени функционирования устройства, совпадающий с длитель 1остью Т реализации на его выходе. I Будем также различать текущую реализацию (реализацию, которая передается на выход устройства в текущем цикле) и последующую реализацию (реализацию, которая передается на выход в следующем цикле). В каждом цикле работы контролируемой части устройства параллельно протекают два процесса. Во-первых, осуществляется последовательная передача на выход устройства значений Y()-текущей реализации, которая в зависимости от текущего состояния управляющего сигна- 10 |Ла на первом выходе блока 16 управления может находиться во втором 2 или в третьем 3 блоках памяти. Для этого по каждому импульсу, поступающему через интервал времени Д1 с второго выхода блока 13 формироваг ния интервала времени через коммутатор 6 на второй вход второго 2 или третьего 3 блоков памяти, осуществляется последовательное считывание зн чений текущей реализации, которые через коммутатор 5 и аналого-цифровой преобразователь I передаются н выход устройства. Так как в реализа ции содержится N значений, то длительность реализации во временной области равна . Во-вторых, выполняется вычисление .новой (последующей) реализации случайного процесса. С этой целью вначале формируется исходный комплексный массив С () случайных, коэф фициентов спектра в соответствии с (2) , причем этот массив формируется за N/2 такта и поступает в блок 7 быстрого преобразования Фурь по второму и третьему (информационным) входам. Для этого в каждом такте по импульсу, поступающему с второго выхода блока 16 управления, первый блок 1 памяти последовательно выдает коэффициенты R}r(n-1), где п - номер такта, ,2,...N /2. Одновременно на второй вход первого блока 8 умножения с выхода пеового функционального преобразователя 11 выдаются комплексные константы. После поступления всех значений C(i) блок 7 быстрого преобразов.ания Фурье выполняет преобразование вида (1), а затем выдает на первый выход импульс конца преобразования, а на второй выход - значенияУ (t) , 0,1,2,...N -1, которые записываются через коммутатор 4 в блок 2 памяти или в блок 3 памяти в зависимости от управляющего сигнала на первом выходе блока 16 управления. По окончании каждой реализации (каждого цикла) управляющий сигнал на первом выходе блока 16 управления изменяется на противоположный, изменяя таким ббразом коммутацию бло ков 2 и 3 памяти;(меняя их местами) Блок 16 управления (фиг.2)содержит регистр 23/блоки и 25 сравнения, элементы И 26-29, счетчик 30, триггеры 31-33, тактовый генератор 3i. Выход регистра 23 соединен 20 . с первым входом блока 2 элемента сравнения, выход которого соединен с первым входом первого элемента И 26, выход которого соединен с нулевым входом триггера 31 и входом Сброс счетчика 30, выход которого подключен к вторым входам блоков 2 и 25 сравнения, единичный вход -триггера 31 объединен с единичным входом триггера 32, счетным входом триггера 33, первым входом элемента И 27 и первым входом блока 1б управления, выход генератора 3 тактовых импульсов соединен с.третьим выходом блока 16 управления, вторыми входами элемента И 26 и элемента И 28, первый вход которого подключен к единичному выходу триггера 31, а выход соединен со счетным входом счетчика 30, вторым выходом блока 16 управления и вторым входом элемента И 23, выход которого является четвертым выходом блока 16 управления, первый вход элемента И 29 подключен к выходу блока 25 сравнения, первый вход которого является третьим входом блока 16 управления, выход триггера 33 является первым выходом блока 16 управления , второй вход которого соединен с нулевым входом триггера 32, выход которого соединен со вторым вхо- дом элемента И 27. Схема блока 16 управления работает следующим образом. В начале каждого цикла работы устройства триггер-З устанавливается в единичное состояние импульсом конца реализации, поступающим с первого входа блока 16 управления на единичный вход триггера 31 и разрешает прохождение импульсов с выхода тактового генератора З через элемент И 28 на счетный вход счетчика 30 сум7 мирующего типа.Так как в начале цикла сметчик 30 находится в нулевом сое- тоянии, то после прохождения через элемент И 28 N/2-1 импульсов в счетчике 30 устанавливается двоичный код N/2-1. Ввиду того, что в регистре 23 постоянно записан также код N /2-1, то на выходе блока 2k сравнения появляется уровень логической единицы. Поэтому следующий N/2 импульс проходит через элемент И 26 и поступает на входы сброса счетчика 30 и триггера 31, устанавливая их в нулевое состояние и запрещая . тем самым прохождение через элемент И 28 последующих импульсов V10 текущего цикла. Триггер 3 будет оставаться в нулевом состоянии до появления очередного импульса на пер вом входе блока 1б управления. Триггер 33 работает в счетном режиме и по каждому входному сигналу перебрасывается в противоположное состояние Триггер 32 и элемент И 27 предназначены для выявления сбойной ситуации в устройстве,«которая эаключа ется а том, что сигнал конца преобра зования на втором входе поступает позже сигнала конца развертки на пер вом входе). В начале цикла триггер 32 находится в единичном состоянии. Поэтому если после начала цикла первым поступает импульс конца преобразования (триггер находится в единичном состоянии), то он проходит через элемент И 27, сигнализируя об ошибке. Остальные элементы: блок 25 срав нения и элемент И 29 обеспечивают выделение из каждой серии по N /2 импульсов на втором выходе блока 16 управления (m+l)-ro импульса, где m - двоичный код на третьем входе блока 16 управления. Выделенный импульс передается на четвертый выход блока 1б управления. i. Блок 13 формирования .интервалов времени (фиг.З) содержит счетчики 35 ИЗб суммирующего типа, регистры 37 и 38, блоки 39 и 40 сравнения и элементы И ,1 и 42. Счетчик 36, регистр 37, блок 39 сравнения и элемент И 41 обеспечивают формиро вание на втором выходе блока 13 рег лярной последовательности импульсов с регулируемым интервалом следования. По каждому импульсу, поступающему с входа блока 13 на ,счет ный вход счетчика 35, его состояние увеличивается на единицу. На второй вход элемента И 41 с вьгхода 39 срав нения поступает высокий разрешающи логический уровень при совпадении двоичных кодов счетчика 35 и регистра 37. Установка счетчика в ну левое положение осуществляется каждым импульсом, поступающим с выхода элемента И 41 на вход сброса счетчика 35. Поэтому на второй выхо блока 13 формирований интервалов времени поступает каждый т-й входной импульс. Изменяя содержимое регистра 37, можно управлять интервалом . Вторая часть блока 13: счетчик .36. регистр 38,блок 40 сравнения и элемент И 42 совершенно идентична первой и пропускает на первый выход олока 13 каждый N -и импульс, поступающий с выхода элемента И 41 на счетный вход счетчика 36 и первый вход элемента И 42, причем в рег 1стре 38 хранится двоичный код, равный N . Новым в устройстве является введение контролирующей части, состоящей из аналого-цифрового преобразователя 15, регистров 17-13, первого 20 и второго 21 сумматоров и блока v22 сравнения, предназначенных для контроля правильности воспроизведения на выходе устройства спектральной плотности мощности формируемого случайного процесса. Будем также отличать от заданного амплитудного спектра Р-рС I), (,1 ,2 ,...N /2-1)воспроизводимый амплитудный спектр Рр () (,l,2),...N/2-n учитывающий появление неисправностей в работе устройства. Большинство неисправностей/сбоев и устойчивых отказов J приводит к появлению ошибок в реализациях случайного процесса. Под ошибкой понимается событие, заключающееся в том, что хотяЬы для одной пары коэффициентов Рр(0, Рр()дНе выполняется условие Рр (i)Pp(i)(,2,...v N/2-1). При этом, проигрывая в глубине обнаружения ошибок на 1-5%, используемый метод позволяет сократить аппаратурные затраты на 25-35, причем проверке подвергается коэффициент амплитудного спектра Pr(i) которому соответствует наибольший заданный коэффициент амплитудного спектра Рр{i). Поэтому одновременно с загрузкой в блок 1 памяти амплитудного спектра Рр{i), ,1 ,2 ,.. N/2-1 в регистр 19 загружается наибольший коэффициент спектра Pp(k), а в регистр 18 - его номер К. 8 начале любой (j-й) реализации по импульсу конца развертки конец предыдущей реализации , поступающему с первого выхода блока 13 формирования интервалов времени, осуществляется запись содержимого (j}j(k)) первого регистра 17 в первый сумматор 20; блок 22 сравнения проверяет на равенство коды, поступающие на его второй и третий вхо13ды, происходит сброс по отрицательному фронту второго сумматора 22. в нулевое состояние и, таким образом, контролирующая часть устройства гот ва к проверке текущей реализации. П каждому импульсу, поступающему с второго выхода блока 13 происходит добавление к содержимому сумматора 20 кода К, поступающего с выхода регистра 18.8 результате этого в сум-с маторе 18 вычисляется аргумент к f4 (k) , а на выходе второго функционального преобразователя 12 ФункцияcoB(ke.(iV), значение которой поступает на первый вход блока 9 умножения. Одновременно на второй вход блока 9 умножения с выхода аналого-цифрового преобразователя 15 поступают дискретные отсчеты УМЕ) текущей реализации случайного процесса. Таким образом, для каждого ,1 ,2 ,..N-1 с третьего входа к содержимому второго сумматора 21 по импульсу ни его втором входе добавляются частичные произведения YM) cos - {kt+fii/t)n к концу текущей реализации в сумматоре 21 накапливается значение коэффициента Рр (k). Сравнение Р (k}nP5,(i:) осуществляется блоком 22 сравнения по синхронизирующему импульсу на его первом входе. В случае несовпадения кодов на контрольный выход уст ройства передается сигнал ошибки. Аналогичным образом устройство работает в каждом цикле (на каждой реализации) . Аппаратурые затраты на реализацию контролирующей части генератора со20ставляют приблизительно 10+20.Кроме того, еще одним достоинством метода контроля является некритич ность работы контролирующих блоков к быстродействию. Так как допустимое минимальное время умножения блоком 9 составляет 10-20 мкс, в то время как наиболее быстродействующие схемы умножения позволяют выполнить эту операцию в 50-100 раз быстрее, то это позволяет использовать медленног действующие, но оптимальные в смысле аппаратурных затрат схемы контролирующих блоков. Таким образом, технико-экономическая эффективность предлагаемого генератора по сравнению с прототипом заключается в повышении его надежности(достоверности воспроизведения заданного спекграмотности) путем контроля правильности воспроизведения спектра мощности формируемого случайного процесса во всем рабочем частотном диапазоне по правильности воспроизведения составляющей спектра, имеющей наибольшую мощность. При этом дополнительные . аппаратурные затраты составляют 1020. Экономический эффект получается за счет увеличения коэффициента использования устройства, так как отказы обнаруживаются в момент их возникновения, а следовательно, уменьшается время восстановления работоспособного состояния устройства. Технико-экономическая эффективНОСТЬ предлагаемого устройства по сравнению с базовым объектом выше, чем по сравнению с прототипом, так как предлагаемое устройство позволяет формировать случайный процесс с техническими характеристиками, превышающими базовые.

15

23

2f

3

Jfe7

г

27

J

Фиг.г

29

26

28

53

Ошибна

Г

Фиг.д

Авторы

Даты

1983-05-30—Публикация

1982-02-08—Подача