ется первым входом блока и объединен с первым входом-элемента И, выход которого соединен с единичным входом первого триггера, нулевой вход которого соединен с первым входом эле мента ИЛИ,выход которого соединен с единичным входом второго триггера ,выход которого соединен с вторым входом второго элемента И, второй вход (блока подклнэчен к единичному входу

третьего триггера,нулевой Е(Ходкоторого объединен с нулевым входом первого триггера и подключен к шине Установ;. ка, выход элемента задержки соединен с вторым входом элемента ИЛИ,ну левой вход второго триггера является третьим входом блока, первый и вторым выходами которого являются соответственно выходы третьего и первого триггеров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор случайного процесса | 1981 |

|

SU972505A1 |

| Генератор случайного процесса | 1982 |

|

SU1020820A1 |

| Генератор случайного процесса | 1982 |

|

SU1068935A1 |

| Цифровой двоичный коррелометр | 1979 |

|

SU832561A1 |

| Устройство для вычисления спектра Фурье | 1983 |

|

SU1121678A1 |

| Дифференцирующе-сглаживающее устройство | 1975 |

|

SU610115A1 |

| Спектральный анализатор случайных сигналов | 1984 |

|

SU1269048A1 |

| Генератор случайного процесса | 1982 |

|

SU1068936A1 |

| Способ воспроизведения случайной вибрации с заданным спектром плотности мощности и устройство для его осуществления | 1988 |

|

SU1518691A1 |

| Генератор случайных процессов | 1981 |

|

SU985786A1 |

1.ГЕНЕРАТОР СЛУЧАЙНОГО ПРОЦЕССА, содержащий датчик случайных чисел, выход которого через блок -, формирования тригонометрических функций соединён с первым входом блока умножения, второй Е1ход которого подключен к выходу первого блока памяти, вход которого является входом генератора, блок быстрого преобразования Фурье первый выход которого соединен с информационным входом первого коммутатора, первый и второй выходы которого соединены с информационными входами соответственно второго и третьего блоков памяти, управляющие входы которых подключены соответственно к первому и второму выходам второго коммутатора, информационный вход которого подключен к первому выходу блока формирования интервалов времени, второй выход которого соединен с первым входом блока выбора реализации, второй вход которого сйедйнен с вторым выходом блока быстрого преобразования Фурье, первый вход которого подключен к первому выходу блока выбора реализации, выход второго блока пймяти соединен с первым информационным входом третьего коммутатора, первый выход которого соединен с входом цифро-аналого-. вого преобразователя, выход которого, является выходом генератора, второй выход блока выбора реализации coejc iHeH с управляющими входами первого, второго и третьего коммутаторов, выход третьего блока памяти соединен с вторым информационным входом третьего коммутатора, о т л и ч а ю щ и и с я тем, что, с целью повышения надежности генаратора, он содержит схему сравнения, четвертый коммутатор, четвер-, тый блок памяти, управляющий и ин;формационный входы которого подключены соответственно к первому и даторому выходам блока умножения, а выход четвертого блока памяти соединен с первыми входами схемы сравнения и четвертого коммутатора, выход которого соединен с вторым вхоО1 дом блока быстрого преобре13ования оо Фурье, выход которого соединен с вто00 рым входом схемы сравнения-, выход которой соединен с третьим входом блока выбора реализации, первый выход которого соединен с вторым входом четвертого коммутатора, третий вход которого подключен к второму выходу третьего коммутатора. 2. Генератор по п. 1, о т л иг чающийся тем, что блок выбора реализации содержит три триггера, элемент И, элемент ИЛИ и элемент задержки, вход которого явля-

.. . .. :

Изобретение относится к вычислительной технике и может быть использовано для имитации случайных процессов с заданными и программно управляемыми спектральными характеристиками в вычислительно-моделирующих комплексах для управления испытаниями изделий электронной и другой техники на механические, вибрационные, электрические и другие воздействия, а также при построении моделирующей аппаратуры, для исследования и оптимизации структурно сложных систем.

Известен генератор случайного процесса содержащий один или несколько формирующих фильтров для придания случайному процессу требуемых спектральных свойств. Управление спектральной плотностью мощности случайного процесса на выходе таких генераторов осуществляется изменением частотной характеристики формирующих фильтров. Однако с практической точки зрения проектирова-ние и изготовление формирукицих фильтров с перестраиваемой в широком частотном диапазоне характеристикой представляет собой достаточно трудную техническую задачу t1 3.

Формирующие фильтры, разработанные на основе аналогичных средств, достаточно просты и стабильны, однако нетехнояогичны и их простые конфигурации допускают перестройку , частотных свойств в широких диапазонах только механическим путем. Реализация формирующих цепей цифровыми . средствами частично лишена этих недостатков, однако расчет параметров формирующих фильтров по известной частотной характеристике достаточ но сложен, так как требует вьшолнемия интегральных преобразований. Кррме того, с .аппаратурной точки зрения эти устройства оказываются очень емкими при воспроизведении случайных процессов с высокой разрешающей способностью, т.е. при задании большого числа значений спектральной плоности мощности случайного процесса так как аппаратурные затраты растут пропорционально числу заданных значений спектральной характеристики.

Известно также устройство, использующее для формирования выходного случайного процесса множество импульсных потоков. Такое устройство содержит в. Сбоем составе множество генераторов импульсов, элементыИ, элемент ЛИ и некоторые другие вспомогательные элементы. 11роцесс на выходе таких генераторов представляет собой последовательность импульсных сигналов определенной формы, слдукмцих через случайные интервалы вре мени, причем управляемой статистической характеристикой выходного случайного процесса является функция распределения случайных вреМенных интервалов 12. . , .

Недостатком данных устройств являются ограниченные возможности их использования для генерирования случайных процессов с заданными .спект- ральными характеристиками, так как несмотря на однозначную связь спектральных характеристик процесса и функции распределения случайных временных интервалов решить нуЮ1 задачу, т.е. определить требуемую функцию распределения случайных временных интервалов по заданной спектральной плотности мощности оказывается затруднительным как из-за

сложности матемзтических преобразований| так и из-за ограниченности класса воспроизводимых спектральных плотностей мощности.

Наиболее (хпизким к Предлагаемому ехни еским решением является генератор случайного процесса, содержащий датчик случайных чисел, блок умножения, блок формирования тригоНометрйческих-функций, блок формирования интервалов времени, блоки памяtи, коммутаторы блок выбора реализации, блок быстрого преобразования Фурье и цифро-аналоговый преобразователь Сз 3i

Известное устройство позволяет получать на выходе случайный процесс с заданными спектральными характеристиками.

Основным недостатком известных устройств является невысокая надежность их функционирования, так как в них не применены специальные средства для обнаружения и устранени ошибок. В то же время в ряде прак-г тических применений устройства к йе- му предъявляются высокие требования ПО надежности,

Цель изобретения - повышение на- дежнрсти функционирования устройства за счёт контроля его работы.

Для достижения поставленной мели в генератор случайного процесса, с6 держащий датчик случайных чисел, выход которого через блок формирова ния тригонометрических функций соединен с первым входом блока умножения, второй вход которого подключен к выходу первого блока памяти, вход котсфого является входом генератЬра, блок быстрого преобразова.ния Фурье, первый выход .которого соединен с информационным входом первого коммутатора,, первый и второй выходы которого Соединены с информационными входами соответственно второго и третьего блоков памяти, управляющие входы которых подключены соответственно к первому и второму. выходам второго коммутаторау информационный вход которого подключен к первому выходу блока формирования интервалов времени, второй выход которого соединен с первым входом блока выбора реализаций, второй вход которого соединен с вторым вы- ходом блока быстрого преобразования Фурье, первый .вход которого подключен к первому выходу блока выбора

реализации, выход второго Ълрка памяти соединен с первым информационным входом третьего коммутатора., первый выход которого соединен с входом цифро-аналогового преобразо1вателя, выход которого является выходом генератора, второй выход блока выбора реализации соединен с управляющими входами первого . второго и третьего кс 4мутаторов, выход третьего блока памяти соединен с вторым информационным входом третьего коммутатора, введены схема сравнения, четвертый коммутатор, четаертый блок памяти, управляюир 1Й и инфс мационный входы которого подключены соответственно к первому и второму выходам блока умнсжения, а выход четвертого блока памяти соединен с. первыми входами схемы сравнения и четвертого кокмутатора, выход которого соединен с вторым входом блока быстрого преобразования Фурье , выход которого соединен с вторым входом схемы сравнения ,выход которой соединен с трет ьим входом блока выбора реализации :Ьервый выход которого соединен, .с вторым входом четвертого коммутатора, третий вход которого подключен к второму выходу третьего коммутатора. Кроме того, блок выбора реализации содержит три триггера, элемент И, элемент ИЛИ и элемент задержки, вход которого является первым входом блока и объединен с первым входом, элемента И, выход которого соединен с единичным входом первого триггера, нулевой вход которого соединен с первым входом элемента ИЛИ, выход которого соединен с единичным входснч etoporo триггера выход которого соединен с вторым входом второго элемента И, второй вход блока подключен к единичному входу третьего триггера, нулевой вход,которого объединен, с нулевым входом первого t триггера и подключен к шине Установка, выход элемента задержки соединен с вторым входом (Элемента ИЛИ, нулевой вход второго триггера является третьим входом блока, перёым и вторым выходами которого являются соответственно выходы третьего и первого триггеров,

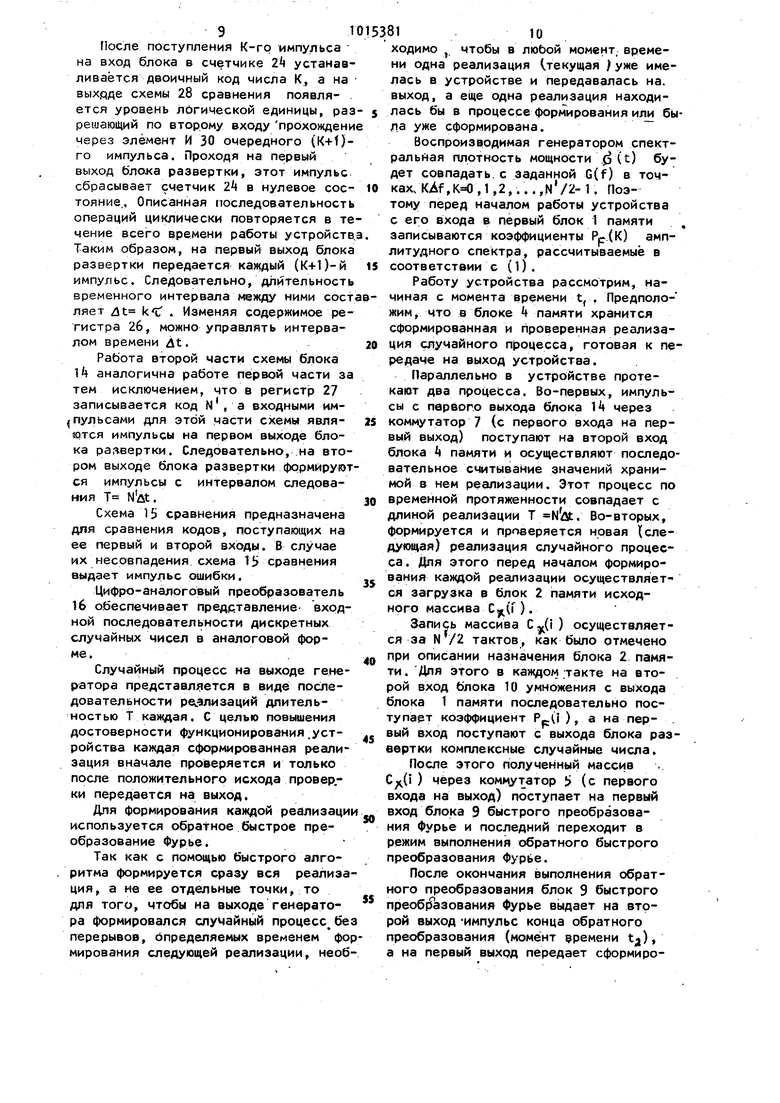

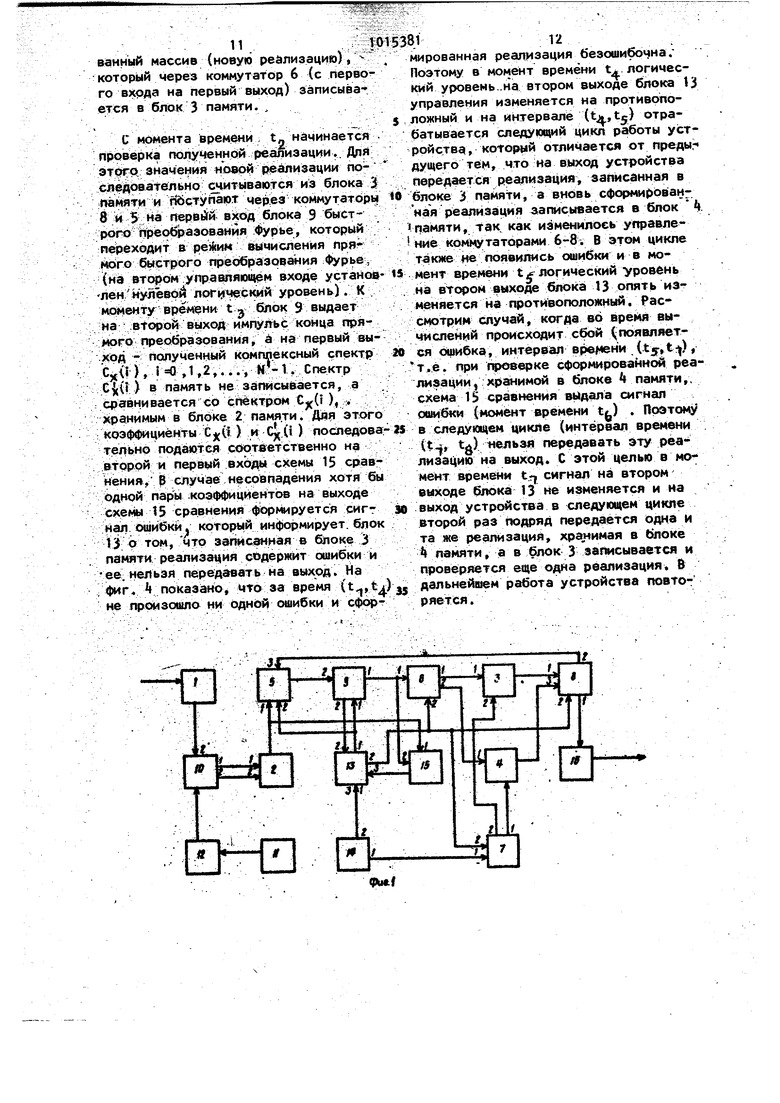

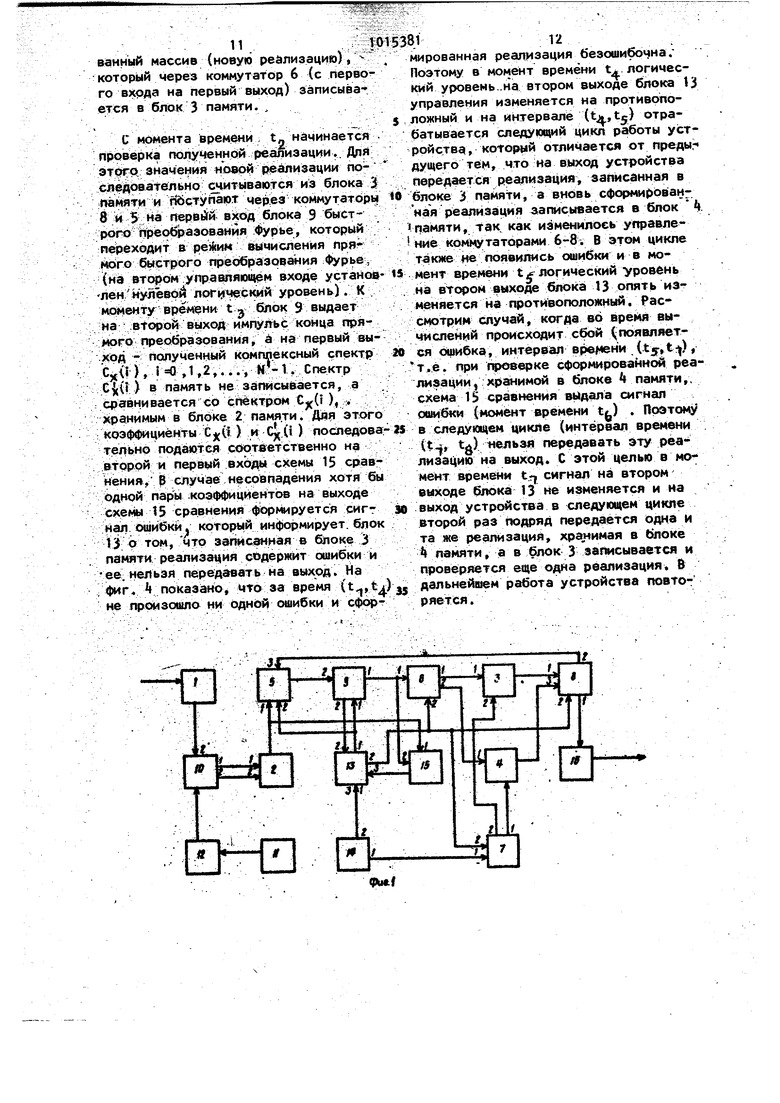

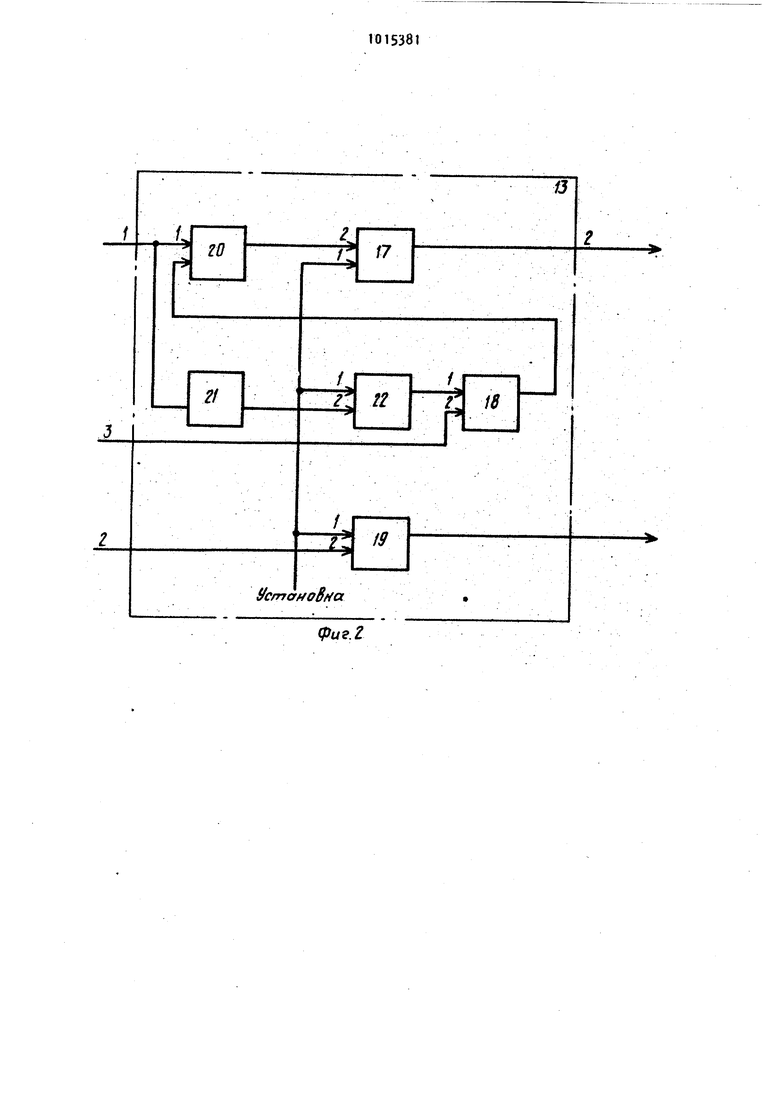

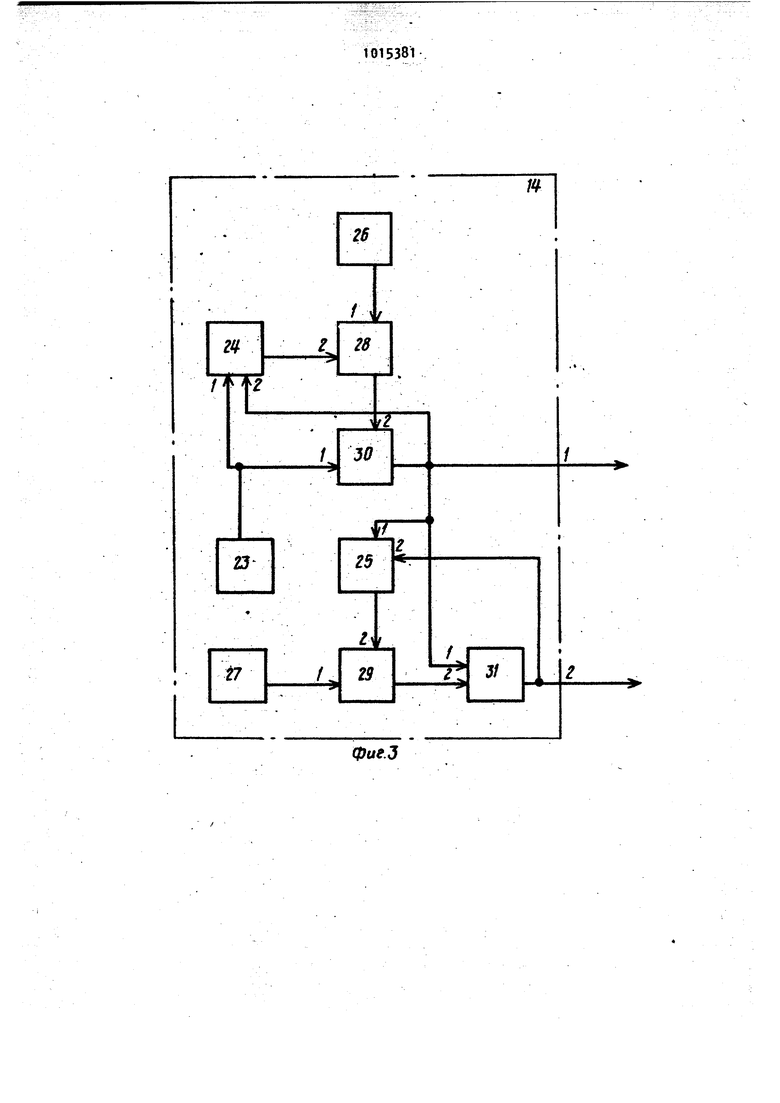

На фиг. t приведена блок-схема предлагаемого генератора; на фиг. 2 схеме блока выбора реализации; на фиг. 3 - схема блока формирования интервалов времени;, на фиг.- дидграмма работы генератора. Генератор содержит блоки I- памяти, коммутаторы 5-8, блок 9 быстрого преобразования Фурье, блок -ТО умножения, датчик 11 случайных чисел, блок 12 формирования тригономет рических функций, блок 13 выбора ре ализаци 1, блок 1 формирования интервалов времени, схему 15 сравнения цифро-аналоговый преобразователь 16 Рассмотрим основные функции,, вы полняемые каждым из структурных эле ,ментов устройства., Первый блок 1 памяти предназначен для приема с входа устройства и хранения коэффициентов амплитудного спектра Pp. (k), определяемых из соотношения ,(k) f 6 (kAf) где G(t) - заданная спектральная пло ность мощности генерируемого случайного процесса;N - число заданных значений спектральной плотности мо длина одной реализации (Т Nbt) ; число точек в одной реали зации случайного процесса (,; . ffl 2,3,... At - шаг дискретизации по времени;uf - шаг дискретизации по частоте ( Af 4 1/Т). Второй блок 2 памяти предназначен лоя хранения исходного массива комплексных случайных коэффициентов спек ра ) по адресам i 0,1,2,... ,N-1 Запись этого массива осуществляется за N/2 такта (по два коэффициента каждом такте). В первом такте информация , поступающая на первый и второй входы, записывается соответствен но в ячейки с адресами О и ы/2, В остальных тактах информация с первого и второго выходов записывается в ячейки памяти (j-1) и (N - j + 1) соответственно (j - номер такта записи, ,3,...., м/2). . Блоки 3 и памяти совершенно идентичны и предназначены для хранения N вещественных значений У (i ), i 0 ,1 ,2,..., N- 1, представляющих од 816 ну реализацию случайного процесса, записываемых с первых входов блоков. Последовательное считывание информации осуществляется по импульсам, поступаюдим на их вторые входы. Коммутаторы 6 и 7 предназначены для коммутации информации, поступающей на их первые входы, на первый (второй) выходы при единичном (нулевом) сигнале на вторых (управляющих) входах. Коммутатор 8 обеспечивает передачу информации, поступающей на его первый и третий входы, соответственно на второй и первый выходы при единичном сигнале на втором (управля- ; щем) входе и соответственно на первый и второй выходы при нулевом сигнале на втором входе. Блок 9 быctpoгo преобразования Фурье предназначен для выполнения по одному из известных алгоритмов быстрого преобразования Фурье, причем при единичном управляющем сигнале на его втором входе он выполняет обратное быстрое преобразование Фурье, а при нулевом сигнале на вторЪм входе - прямое быстрое преобразование Фурье. После окончания каждого преобразования (прямого или обратного) блок 9 быстрого преобразования Фурье формирует на втором выходе импульс конца преобразования. S качестве блока 9 может быть использовано любое известное устройство, осуществляющее как прямое, так и обратное быстрое преобраг зование Фурье. Датчик 11 случайных чисел предназначен дпя формирования на своем . выходе случайных равномерно распре-, деленных на интервале С О, (N-l)) целых двоичных чисел. Блок 12 формирования тригонометрических функций предназначен для формирования на своем выходе комплексных величин cos (-НЬ.) - J.sin ( (2) по каждому значению К, поступающему на его вход. Практически блок 12 может быть реализован в виде постоянного запоминающего устройства, по последова ельным адресам К (К«0,1,2.. .N-1) которого записаны комплексные константы вида (2). Блок 10 умножения вы1золняет операцию умножения действительных чисел, поступающих на его- второй вход, и комплексных чисел, поступающих на его первый вход. Для загрузки второго блока 2 памяти необходи« МО выполнить тактов умножения, причем блок 1.0 умножения имеет ту особенность, что в первом такте он выполняет непосредственную передачу числа на втором входе на первый выход (без умножения), а на втором выходе формируется нулевой двоичный код. В остальйых м/2-1 тактах на первый выход результат умножения передается без изменения, а на второй выход - в комплексно-сопряженном по отношению к первому выходу виде. Блок 13 осудцёствляет синхронизацию работы всех блоков устройства. ,Пример схенной реализации блока 13 приведен на фиг. 2. Для описания его работы воспользуемся временной диаграммой, представленнбй на фиг, k, Блок 13 содержит триггеры 17т19, элемент И 20, элемент 21 задержки, элемент ИЛИ 22, тактовый генератор 23 Работу блока 13 рассмотрим, начйная с момента времени tij (фиг.2). В этот же момент все триггеры находятся в единичном состоянии. Тактовыйгенератор 23 предназначен для формирования регулярной, последовательнбсти импульсов с периодом следования т. В момент времени t импульс, поступивший со второго входа блока на в.торой (счетный) вход триггера 19, перебрасывает последний в противоположное (нулевое) состояние. Следующий импульс на втором входе блока 13 управления (момент времени t) пе рабрасывает триггер 19 в единичное состояние. Появление на интервале вр |Мени (t,t) хотя бы од : 6гоимпульса I на третьем входе блока 13 вызыва ет установку по второму (установочному) входу триггера 18 в нулевое состояние, запрещая по второму входу прохождение через элемент И 20 импульса, поступившего в момент времени на первый вход блока 13,еле-, доват.ельно, триггер 17 продолжает оставаться в прежнем состоянии. Этот же импульс (на первом входе блока) проходит через элемент 21 задержки, . элемент ИЛИ 22 на первый (установоч ный) вход триггера 18, устанавливая его в единичное -состояние. Элемент 21 задержки должен задерживать импул сы на время, превышающее их длительность.. 1 818 Если же к моменту времени t триггер 18 не сбросился внулевое состояние, то поступивший в этот момент времени импульс на первом-входе блока поступает на второй (счетный) вход триггера 17 и перебрасывает его в противоположное состояние. В даяьнейшем описанная последовательность операций повторяется. Для того, чтобы триггеры 17-19 перед началом работы находились в единичном состоянии, необходимо подать одиночный импульс, на шину Установка. Блок 1 -предназначен для фсч мирования :на первом своем выходе импульсов с интервалом следования длина ОДНОЙ -реализации случайгде Т г . ного процесса; N количество точек в одной реа. лизации; X интервал между импульсами на входе блока 1А; k масштабный коэффициент, . няя который можно управлять длительностью реализации случайного процесса. На втором выходе блока Н формируются через интервалы;времени Т импульсы конца развертки, йнформируюе4ие блок 13 с окончании передачи на выход устройства очередной реали, эации и о необходимости передавать на вход устройства Следующую реализацию. Одна из возможных Схемных реализа- . ций блока 14 приведена на фиг. 3 и включает счетчики 24 и 25 суммирующего типа, регистры 26 и 27, схемы 28 и 29,сравнения,элементы И 30 и 31 Счетчик 24, регистр 26, схема 28 сравнения и элемент И 30 предназна 4еныдля формирования на первом выходе блока регулярной последователцности имг льсов с управляемым интервалом между; ними t. На вход блока развертки поступают опорные регулярные импупьс.ы с интервалом следования Т. В регистре 2б хранится двоичный код К развертки. По каждому импульсу на входе блока развертки счетчик .24 увеличивает свое состояние на единицу. Работу блока 14 рассмотрим с момента времени, когда .счетчики 24 и 2$ находятся в нулевом состоянии. 1осле поступления К-гр viwnyjibca на вход блока в счетчике Zk устанавливается двоичный код числа К, а на выходе схемы 28 сравнения появляется уровень логической единицы, раз решающий по второму входу прохождени через элемент И 30 очередного (K+t)го импульса. Проходя на первый выход блока развертки, этот импульс сбрасывает счетчик 2k в нулевое соетояние.. Описанная последовательность операций циклически повторяется в те чение всего времени работы устройств Таким образом, на первый выход блока развертки передается каждый (К+1)-и импульс. Следовательно, длительность временного интервала между ними сост ляет 4t k . Изменяя содержимое регистра 26, можно управлять интервалом времени At. Работа второй части схемы блока }k аналогична работе первой части за тем исключением, что в регистр 27 записывается код N, а входными нм пульсами для этой части схемы являадтся импульсы на первом выходе блока раявертки. Следовательно, на втором выходе блока развертки формируют ся импульсы с интервалом следования Т Мд1. Схема 15 сравнения предназначена для сравнения кодов, поступанэщих на ее первый и второй входы. 8 случае их несовпадения схема 15 сравнения выдает импульс ошибки. Цифро-аналоговый преобразователь 16 обеспечивает пред|с;тавление- входной последовательности дискретных случайных чисел в аналоговой форме. Случайный процесс на выходе генератора представляется в виде: последовательности радлизацйЙ длительностью Т каждая. С целью повышения достоверности функционирования.устройства каждая сформированная реализация вначале проверяется и только после положительного исхода провер,ки передается на выход. Для формирования каждой реализаци используется обратное быстрое преобразование Фурье. Так как с помощью быстрого алгоритма формируется сразу вся реализа ция, а не ее отдельные точки, то для того, чтобы на выходе генератора формировался случайный процесс бе перерывов, определяемых временем фо мирования следующей реализации, необ ходимо , чтобы в любой момент, времени одна реализация (.текущая ) уже имелась в устройстве и передавалась на. выход, а еще одна реализация находилась бы в процессе формирования илJи была уже сформирована. Воспроизводимая генератором спектральная плотность мощности .$эЛt) будет совпадать, с заданной G(f) в точках. KAf ,,1,2,... ,N/2-1. Поэтому перед началом работы устройства с его в:хода в первый блок 1 памяти записываются коэффициенты Рр{К) амплитудного спектра, рассчитываемые в соответствии с (1) . Работу устройства рассмотрим, начиная с момента времени t,. Предположим, что S блоке памяти хранится сформированная и проверенная реализация случайного процесса, готовая к передаче на выход устройства. Параллельно в устройстве протекают два процесса, go-первых, импульсы с первого выхода блока 1 через коммутатор 7 (с первого входа на первый выход) поступают на второй вход блокад памяти и осуществляют последовательное с «1тываНие значений хранимой в нем реализации. Этот процесс по временной протяженности совпадает с длиной реализации Т N/X. Во-вторых, формируется и проверяется новая 1( следующая) реализация случайного процесса. Для этого перед началом формирования ка)кдой реализации осуществляется загрузка в блок 2 памяти исходного массива С (Г). Запись массива Cy(i ) осуществляется за N /2 тактов, как было отмечено при описании назначения блока 2 памяти. Для этого в каждом такте на второй вход блока 10 умножения с выхода блока 1 памяти последовательно поступает коэффициент Рр(1 ), а на пер- . вый вход поступают с выхода блока развертки комплексные случайные числа. После этого полученный массив С(1 ) через коммутатор 5 (с первого входа на выход) поступает на первый вход блока 9 быстрого преобразования Фурье и последний переходит в режим выполнения обратного быстрого преобразования Фурье. После окончания выполнения обратного преобразования блок 9 быстрого преобразования Фурье выдает на второй выход -импульс конца обратного преобразования (момент времени t;j), а на первый выход передает сформиро11Wванный массив (новую реализацию), который через коммутатор 6 (с первого входа на первый выход) записыва ется в блок 3 памяти. С момента времши tn начинается проверка nojiiyMeHHOfl реализации. Для , значения fioeo0оеапизации посяе| оаательно считываются из блока 3 памяти и пбстуйают через коммутаторы 8 и $ на первьГЙ вход блока 9 быстрот Н|реоб пе)ёходит & ре:}иим ||ычисленйя пряfwaro быстрого преобразования Фурье, (на втором входе устаноц лен;|+уЙ1ёвойлоП 1№с ««й уровень). К мсйенту времени t блок 9 выдает навТсч)ой выход импуп1 6 конца пря: 4ого преобразования, а на первый - Полученный крмпп:ексный спектр Cj((l 1,1 0 ,1,2,. ..,. Спектр С(} ) Ef память не запйсые ается, а сравнивается сР cirteKTpoM Cjf(I ), . Хранимым в блоке 2 памяти. Дяя этого коэффициенты Сjj(i) и C(i) последовательно подается срртветственно на в трррй и первый входа схемы 15 сравнения, Э случае нес;рвпадёния хотя бы Одной пары коэф 4Цйент6в на выходе схемы 15 сравнения фрркмруется сиг нал. снийЪкй.крторыЙ информирует, блок 13 о том, чтр зэпйс иая в блоке 3 памяти реализация содержит ошибки и ее.нейьзя передавать на выход. На фиг;, показаноj что за время (t,tJ не произошло ни Рдной ошибки и сфор8112мированная реализация безошибочна; Поэтому в момент времени ti логический уровень..на втором выходе блока 13 управления изменяется на противотюложный и на интервале (tjt.tj) отрабатывается следутций цикл работы устройству, который отличается от преды:дущего тем, что на выход устройства передается реализация, записанная в блоке 3 памяти, а вновь сформированная реализация записывается в блок памяти, так как изменилось управление коммутаторами 6-8. В этом цикле также не поя19ились схиибки и в мо мент времени t логический уровень на втором выходе блока 13 опять изменяется на противоположный. Рассмотрим Случай, когда во время вычислений происходит сбой (;появляется ошибка, интервал вренени(.)) т,е. при г оверке сформированной реалиэации,:хранимой в блоке памяти,, схема Ib сравнения выдала сигнал ромбки (момент времени t/) . Пратому в следующем цикле (интервал времени (t, 1)иельэд передавать эту рёализа1|ию на выход. С этой целью в мо мент времени t.r сигнал на втором выходе блока 13 не изменяется и на выход устройства в следующем цикле второй раз подряд передается одна и та же реализация, хра)1имая в блоке памяти, а в блок 3 записывается и проверяется еще одна реализация. В дальнейшем работа устройства повторяется.

фиг. г

фие.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| П | |||

| Генерирование случайных сигналов | |||

| М., Энергия, -1971., 2.Авторское свидетельство СССР № 370717, кя.С 06 F 7/58, 1971 | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| G 0:6 F 7/58, 1981 (прототип) | |||

Авторы

Даты

1983-04-30—Публикация

1981-06-04—Подача