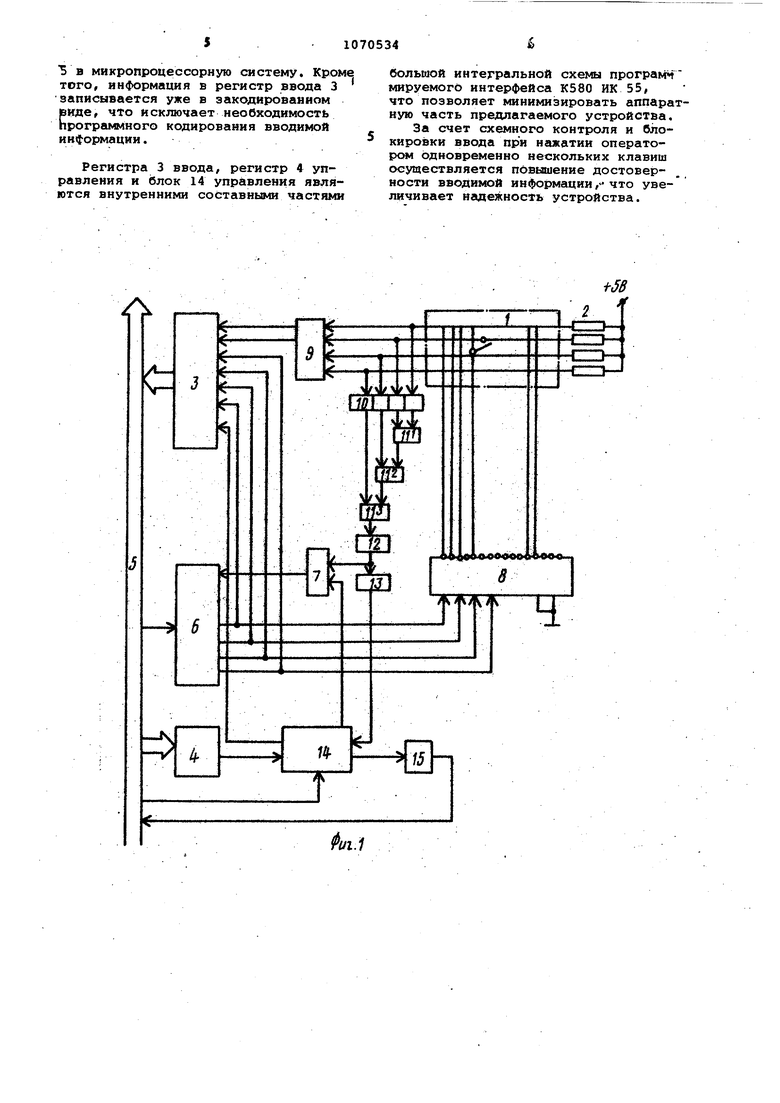

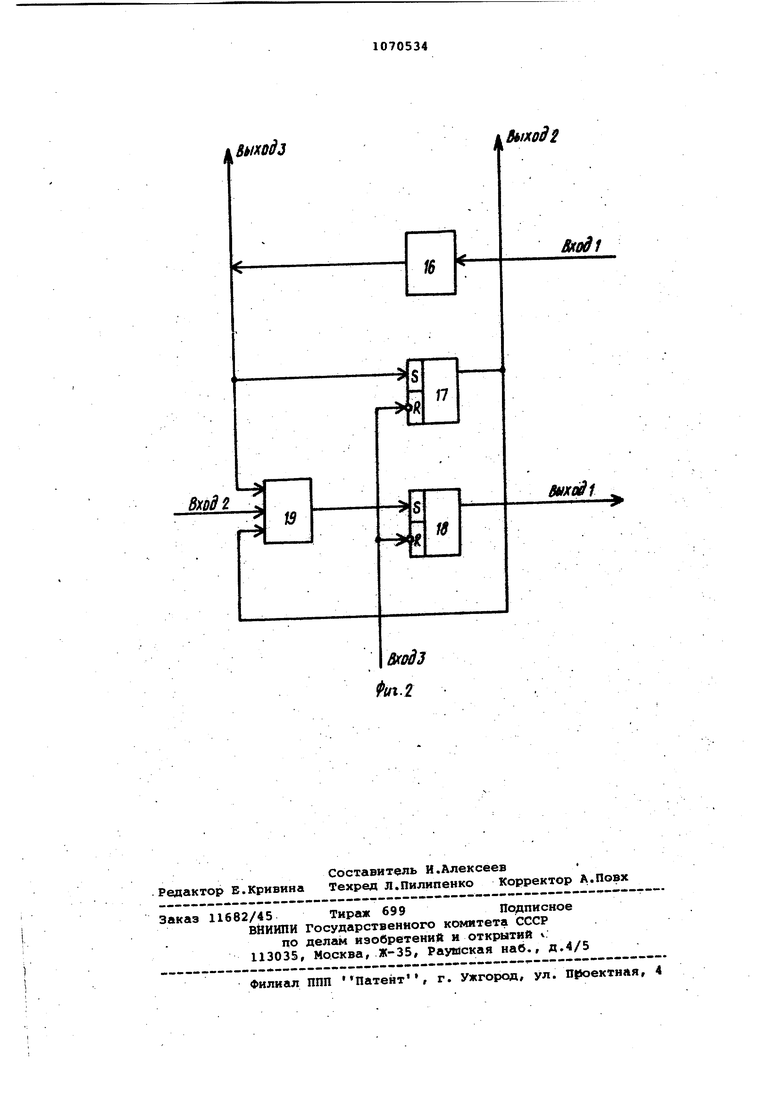

Изобретение относится к вычислительной технике и может найши применение в микропроцессорных системах для ввода данных. Известно устройство для ввода информации, содержащее узел управления, соединенный первым выходом со счетным входом первого счетчика, который подключен выходом переполнения к счетному ; входу второго счетчика, причем выходы первого счетчика являются соответствующими выходами младших разрядов кода адреса устройства, управляющие входы которого подключены соответственно к первому входу узла управления и входам сброса счетчиков, сумматор, первая группа входов которого подключена к соответствунвдим выходам первого счетчика, вторая группа входов - к соответствующим выходам второго счет чика, выходы сумматора являются соответствуюищми выходами старших разрядов кода адреса устройства, выходы перевыполнения первого и второго счетчиков подключены соответственно к второму и третьему входам узла управления, второй выход которого является управлянацим выходом устройства СИ . , Недостатком известного устройства является снижение надежности, так как не обеспечивается защита от одно временного нажатия нескольких клавишей . Наиболее близким по технической сущности к предлагаемому является устройство для ввода информации, содержащее регистр ввода, соединенный с горизонталями тастатурной вертикали которой через усилители соединены с выходами регистра управления, и оба регистра управляются От микропроцессорной магистрали 21. Недостатком известного устройства 1 :Является снижение его надежности, Уак как не обеспечивается заьщта от одновременного нажатия нескольких клавишей. цель изобретения - повышение на: д:ежности устройства за счет -схемной : блокировки ошибок оператора, Поставленная цель достигается тем : Что в устройство для ввода информаЙ ги, содержащее регистры ввода и уп|р|авления к матричную клавиатуру, йходная шина регистра управления Йвляется входной шиной управления устройства, выходная шина регистра ввода является выходной информаиионВой шиной устройства, введены счвтЧик, блок управления, фо1 1Ирователь ямпульсов, блок инверторов, шифратор Элементы ИЛИ, задержки, первый элеЙент НЕ, с первого по третий элементы ИСКЛЮЧАЮЩЕЕ ИЛИ И дешифратор, лыходы которого подключены через матричную клавиатуру, к входам шифра.тора и к входам блока инверторов, выходы шифратора соединены с одними информационными входами регистра ввода, выходи блока инверторов соответственно соединены с первым и вторым входами первого и с первыми входами второго и третьего элементов ИСКЛЮЧАЮ {ЕЕ ИЛИ, выход первого элемента ИСКЛОЧАЮидаЕ ИЛИ. соединен с вторым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к второму входу третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого через элемент задержки соединен с первым входом элемента ИЛИ и с входом формирователя импульсов, выход которого подключен к первому входу блока управления, второй и третий входь которого соединены соответственно с выходом регистра управления и входом ЧТЕНИЕ устройства, а выходы с первого по третий соединены с входами -первого элемента НЕ, вторым входом элемента ИЛИ и со стробируюищм входом регистра ввода соответственно, выход первого элемента НЕ является выходом запроса прерывания устройства, счетный вход счетчика является тактовым входом устройства, а вход останова подключен к выходу элемента ИЛИ, выходная шина счетчика подключена к входам дешифратора и к другим информационным входам регистра ввода. Блок управления содержит первый и второй триггеры, элемент И и второй элемент НЕ, вход которого является первым входом блока, входы установки в ноль первого и второго триггеров, а также первый вход элемента И являются вторым и третьим входами блока соответстаенно, выход первого триггера подключен к второму входу элемента И, выход второго элемента НЕ подключен к третьему входу элемента И и к входу установки в единицу первого триггера, выход второго триггера, выход первого триггера и выход второго элемента НЕ являются соответственно первым, вторым и третьим выходами блока, выход элемента И подключен к входу установки в единицу второго триггера. На фиг. 1 приведена блок-схема устройства; на фиг. 2 - функциональная блок-схема блока управления. Устройство содержит матричную Клавиатуру 1, нагрузочные элементы 2, регистр 3 ввода, регистр 4 управления, микропррцессорную магистраль 5, счетчик 6,элемент ИЛИ 7,дешифратор 8, шифратор;, 9, блок 10 инвер- торов, с первого по третий элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 11-11 , элемент 12 задержки, формирователь 13 импульсов, блок 14 управления, первый и второй .

элементы НЕ 15 и 16, первый и второй триггеры 17 и 18, элемент И 19. Матрица 1 представляет собой набор клавишей с замыкающими контактами без фиксации.

Регистр 4 управления представляет собой запоминаюртий элемент и служит для приема из микропроцессорной магистрали 5 и хранения сигнала разрешения выборки запроса на прерывание блоками управления.

Микропроцессорная магистраль 5 содержит три группы сигнальных шин: адресные шины для адресации устройства, шины данных для пересылки информации и шины сигналов управления. Работа блоков устройств синхронизируется тактовым сигналом магистрали. Шифратор 9 представляет собой комбинационную схему из элементов ИЛИ и обеспечивает перекодировку чо,тырех сигналов горизонталей матрицы 1 в двоичный код и формирование для регистра 3 ввода двух младших разрядов кода нажатой клавиши.

Устройство работает следующим образом.

Счетчик 6 считает тактовые.импульсы, приходящие из микропроцессорной магистрали 5. Число импульсов в виде двоичного коДа поступает на вход дешифратора 8, который согласно коду в.ыдает сигнал низкого уровня на соответствующую вертика/tb матрицы 1. .Пока клавиши матрицы 1 не нажаты, на горизонталях ее при помощи элементов

2поддерживаются сигналы высокого уровня. Элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 11, элемент.12 задержки и формирователь

13импульсов не срабатывают, и блок

14управления сигналов не выдает.

По приходу из микропроцессорной магистрали очерёдного тактового импульса счетчик б изменяет двоичный код числа импульсов, тем самым через дешифратор 8 выбирая следуннцую вертикаль матрицы 1.

Описанным способом циклически сканируются все вертикали матрицы 1.

При нажатии клавиши, в момент появления сигнала низкого уровня на соответствующую вертикаль, через замкнутый контакт нажатой клр.вишиформируется низкий уровень сигнала на соответствующую горизонталь матрицы 1.

Данный сигнал кодируется шифратором 9 и поступает на вход регистра

3ввода. Одновременно сигнал с горизонталей матрицы 1 с помсяцью инверторов 10 преобразуется в сигнал высокого уровня и поступает на элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 11. Если нажата только одна клавиша, т.е. сигнал выjcoKoro уровня присутствует только

на одном входе элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 11 -11, то на вход элемента 12

задержки поступает сигнал нажатия клавиши высокого уровня. Элемент I2 задержки обеспечивает згадержку проI хождения переднего фронта сигнала к формирователю 13 импульсов на время, необходимое для затухания переходных процессов при зашжании контактов. Пос-е задержки сигнал нажатия клавиши через элемент ИЛИ 7 останавливает счетчик 6 и запускает формирователь 13 импульсов, который подает на вход 1 блока 14 управления (фиг. 2) короткий стробиругощий импульс. Данный импульс инйСертируется элементом НЕ 16, по выходу 3 блока 14 управления стробирует запись информации в регистр ввода 3

,и устанавливает первый триггер 17, который через выход 2 подает сигнал на второй .вход элемента ИЛИ 7 для останова счетчика 6.

После установки первого триггера 17 через элемент И 19 устанавливается второй триггер 18, если уста-новлен разрешагаций разряд в регистра

-управления 4 и на вход 2 блока 14 управления поступает сигнал высокого уровня. Второй триггер 18 на выходе

Iвырабатывает сигнал запроса прерывания, который инвертируется элементом НЕ 15 и передается в микропроцессорную магистраль 5, сообщая о наличии новой информации в регистре ввода 3. Для приема информации в виде двоичного кода посредством микропроцессорной магистрали 5 микропроцессорная система передает по магистрали стробирующий импульс ЧТЕНИЕ, который разрешает информации

из регистра 3 ввода поступить на шин данных микропроцессорной магистрали 5, а также по входу 3 блока 14 управления сбрасывает первый и второй триггеры 17 и 18.

Отпуская нажатую клавишу в матрице 1, контакты клавиши размыкаются, на соответствующей горизонтали устанавливается сигнал высокого уровня, через элементы ИСКЛЮЧАЮЩЕЕ.ИЛИ 11 и элемент 12 задержки снимается сигнал с первого входа элемента ИЛИ 7. Если информация из регистра 3 ввода поступила в микропроцессорную магистраль 5 и первый триггер 17 сброшен, снимается сигнал останова счетчика 6 и возобновляется циклическое сканирование вертикалей матрицы 1. :i При одновременном нажатии двух клавиш сигналы нажатия клавиш) поступают с горизонталей матрицы 1 на два входа элементов ИСКЛЮЧАЮЩЕЕ ИЛИ

II-11 , которые блокируют проход сигнала, таким образом исключая запись ложной информации в регистр ввода 3. Это обеспечивает высокую достоверность информации, вводимую через микропроцессорную магистраль

3 в микропроцессорную систему. Кроме того, информация в регистр ввода 3 записывается уже в закодированном 1зиде, что исключает необходимость программного кодирования вводимой информации.

Регистра 3 ввода, регистр 4 управления и блок 14 управления являются внутренними составными частями

большой интегральной схемы программ мируемого интерфейса К580 ИК 55, что позволяет минимизировать аппаратную часть предлагаемого устройства. За счет схемного контроля и блокировки ввода при нажатии оператором одновременно нескольких клавиш осуществляется повышение достоверности вводимой информации,-что уве- личивает надежность устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования серий импульсов | 1985 |

|

SU1309269A1 |

| Устройство для ввода информации | 1983 |

|

SU1141393A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для ввода информации | 1989 |

|

SU1682996A1 |

| Устройство для ввода информации | 1982 |

|

SU1089566A1 |

| Устройство для ввода информации | 1980 |

|

SU885986A1 |

| Стохастический аналого-цифровой преобразователь | 1985 |

|

SU1267615A1 |

| Устройство для сопряжения микропроцессорной системы с внешними устройствами с контролем | 1984 |

|

SU1242956A1 |

| Устройство для ввода информации | 1982 |

|

SU1048465A1 |

| СИГНАЛИЗАТОР ЗАГРУЗКИ ДВИГАТЕЛЯ | 1992 |

|

RU2027979C1 |

1.. УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ, содержащее регистры, ввода и управления и матричную клавиатуру, входная шина регистра управления является входной шиной управления устройства,, выходная шина регистра ввода является выходной информационной шиной устройства, отличающ е е с я тем,что,с целью повышения надежности устройства за счет блокировки ошибочных действий оператора, в него введены счетчик., блок управления, формирователь импульсов, блок инверторов, шифратор, элементы ИЛИ, задержки, первый элемент НЕ, с первого по третий элементы ИСКЛЮЧАЩЕЕ ИЛИ и дешифратор, выходы которого подключены через матричную клавиатуру к входам шифратора и к входам блока.инверторов,выходы шифратора соединены с одними информационными входами регистра ввода, выходы блока инверторов соответственно соединены с первым и вторым входами первого и с первыми входами второго и третьего элементов ИСКЛЮЧА б|ЦЕЕ ИЛИ, -выход первого элемента ИСКЖ) ИЛИ соединен с вторым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к второму входу третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого через элемент задержки соединен с первым входом элемента ИЛИ иВХОДОМ формирователя импульсов/ выход которого подключен к первому входу блока управления, второй и третий входы которого соединены соответственно с выходом регистра управления и входом ЧТЕНИЕ устройства а выходы с первого по третий соединены с входами первого элемента НЕ, вторым входом; элемента ИЛИ и со стробирующим входом регистра ввода соответственно, выход первого элемента НЕ является выходом запроса прерывания устройства, счетный вход счетчика является тактовым входом устройства, а вход останова подключен к выходу элемента ИЛИ, выходная шина счетчика подключена к входам дешифратора и другим информационным входам регистра ввода. 2. Устройство по п, 1, отличающееся тем, что блок управления содержит первый и второй триггеры, элемент И и второй элемент НЕ, которого является первым блока, входы установки в ноль перО СП вого и второго триггеров, а также первый вход элемента И являются вторым и третьим входеши блоха со: ответственно, выход первого триггера подключен к второму входу элемента И, выход второго элемеятЛ НЕ подключен к третьему входу элемента И и к входу установки в единицу первого триггера, выход второго триггера, выход первого триггера и выход второго элемента НЕ являются соответственно первым, вторым и третьим выходами блока, выход элемента И подключен к входу установки в ед иницу второго триггера.

вшодз

I

BXDS2

13

Btixodl

Ы1

№

f7

5

«im

W

ЛгЛ Й«.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для формирования адреса | 1976 |

|

SU652563A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Radio, fernsehen, elektronik, 1981, № 4, с | |||

| Стиральная машина для войлоков | 1922 |

|

SU210A1 |

Авторы

Даты

1984-01-30—Публикация

1982-10-14—Подача