f1

Изобретение относится к микропроцессорной технике и может быть использовано при проектирован1-1и микро- процессор1- ь х систем и микро-ЭВМ с высокими показателями надежности.

Целью изобретения является повьше нк-е надежности устройства за счет осуществления контроля времени ответной реакг,ии адресуемого внешнего устройства.

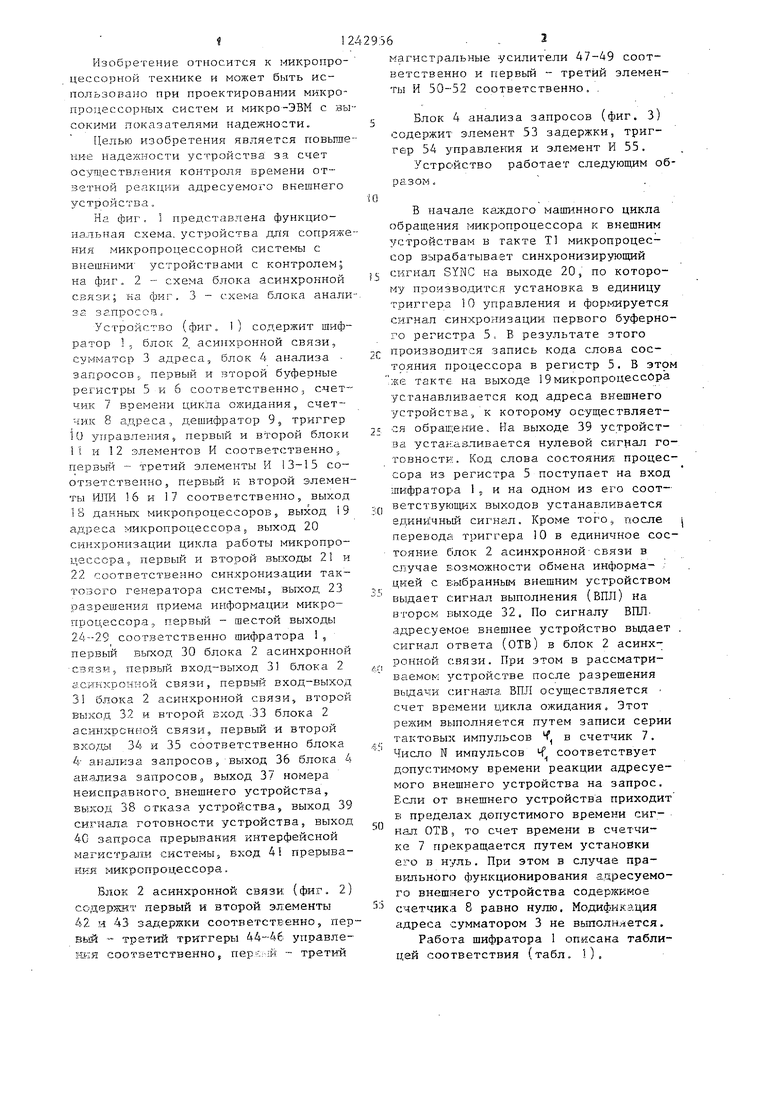

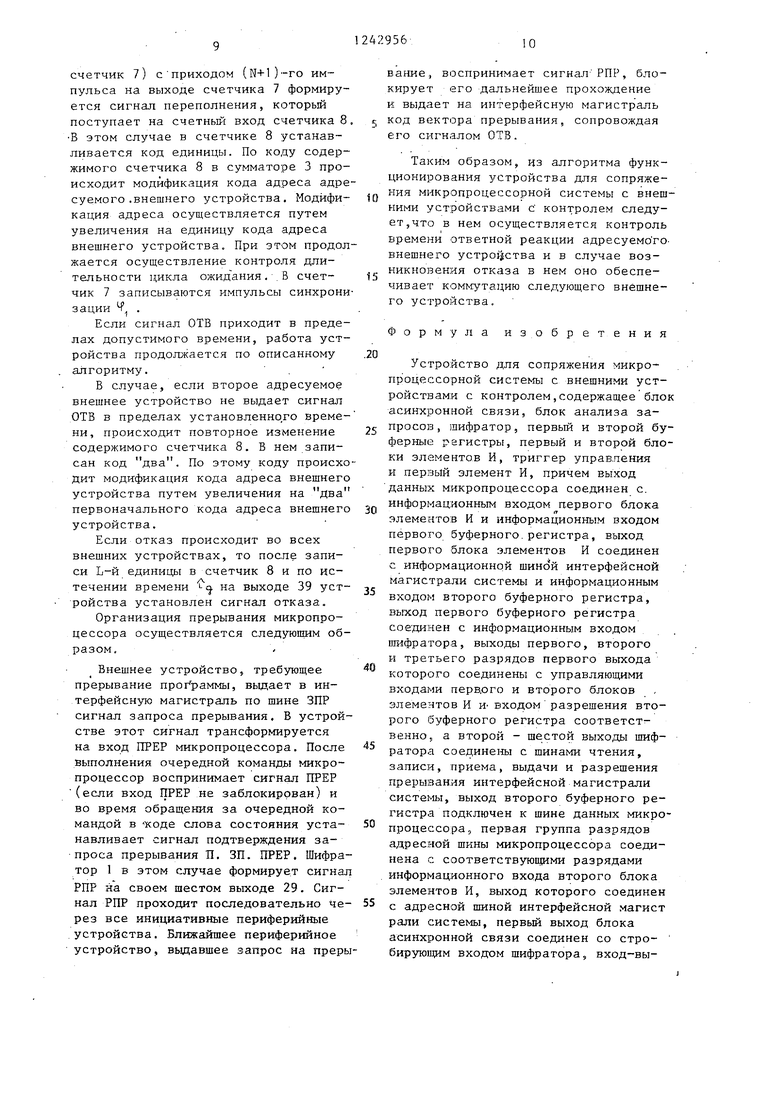

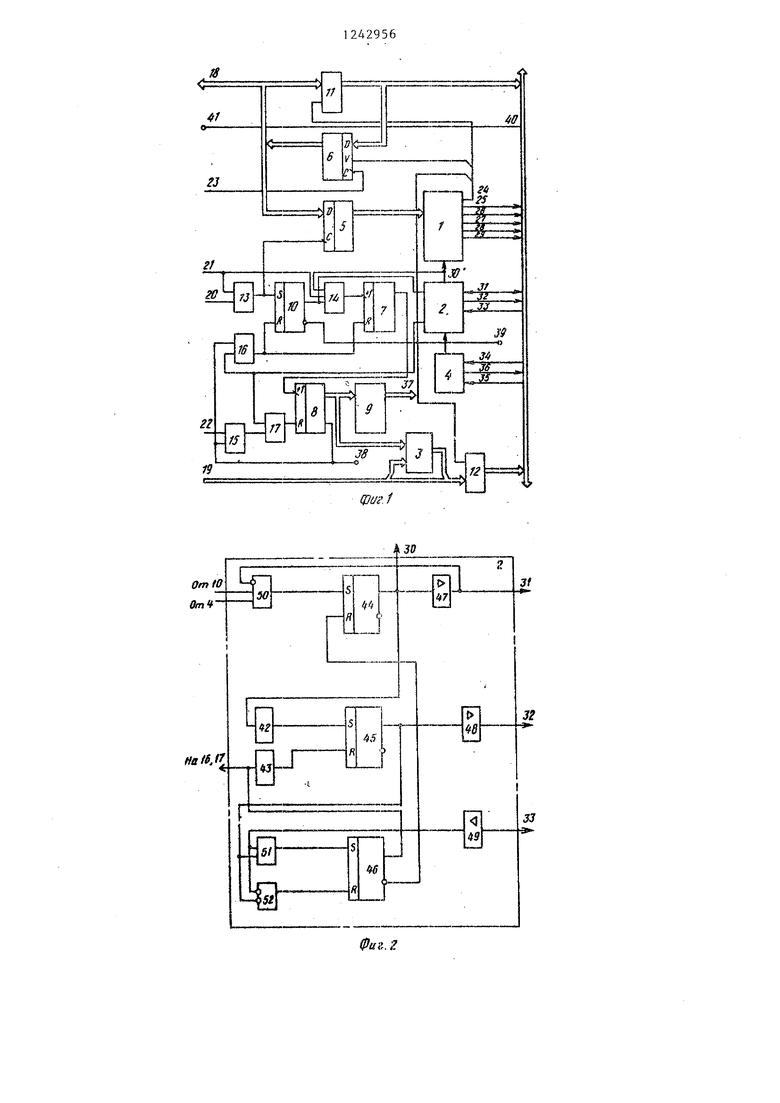

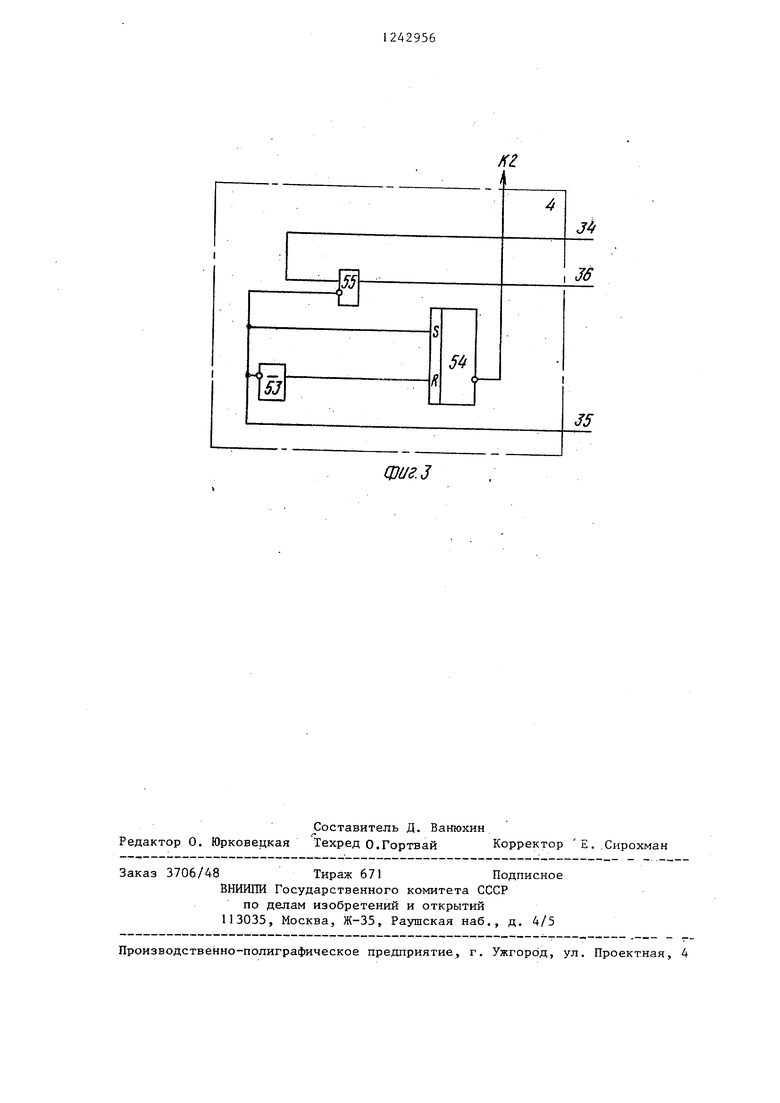

На фиг. 1 представлена функциональная схема, устройства для сопряжения микропроцессорной системы с внешними устройствами с контролем; на фиг. 2 - схема блока асинхронной связи; на фиг. 3 - схема блока анали за запросов.

Устройство (фиг, 1) содержит шифратор 1; блок 2, асинхронной связи, сумматор 3 адреса, блок 4 анализа - запросов,, первый и второй буферные регистры 5 и 5 соответственно, счетчик 7 времени цикла ожидания, счетчик 8 адреса, дешифратор 9, триггер

10управления, первый и второй блоки

11и 12 элементов И соответственно, перзъй - третий элементы И 13-15 соответственно, первый и второй элементы ИЛИ 16 и 17 соответственно 5 выход

i 8 данных микропроцессоров, выход 19 адреса микропроцессора, выход 20 синхронизации цикла работы i niKponpo- цесссра, первый и второй выходы 21 и 22 соответственно синхронизации тактового генератора системы, выход 23 разрешения приема информации микропроцессора, парвьм - шестой выходы 24--29 соответственно шифратора 1 , первый выход 30 блока 2 асинхронной сзпзи, первый вход-выход 31 2 асинхронной связи, первый вход-выход 3 блока 2 асинхронной связи., второй выход 32 и второй вход .33 блока 2 асинхрснной связи, первый и второй входа 34 и 35 соответственно блока 4- анализа запросов, вьаход 36 блока 4 ав:алкза запросов,, выход 37 номера неисцравкого внешнего устройства, выход 38 отказа устройства, выход 39 сигнала готовности устройства, выход 40 запроса прерывания интерфейсной магистрали системы, вход 4 прерыва- кня микропроцессора.

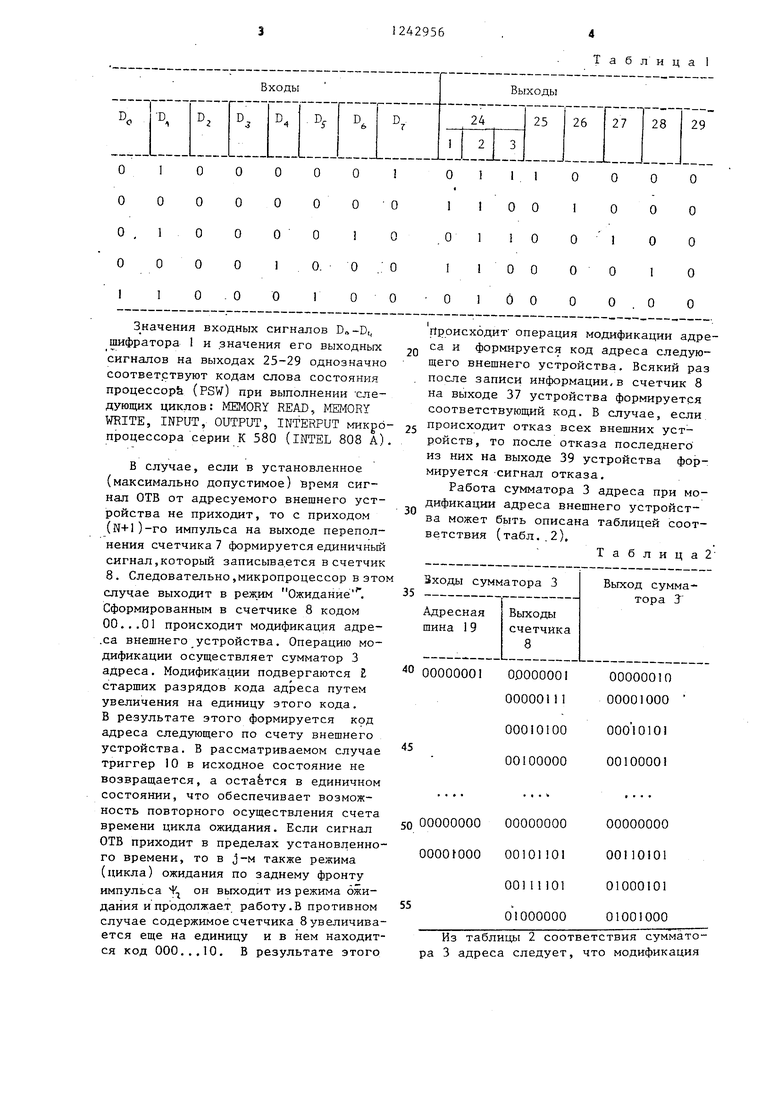

Блок 2 асинхронной связи (фиг. 2) содержит первый и второй элементы 42 и 43 задержки соответственно, пер- вьй - третий триггеры 44-46 управле- ьжя соответственно, пер.-м - третий

6 . . 2 магистральные усилители 47-49 соответственно и первый - третий элементы И 50-52 соответственно. .

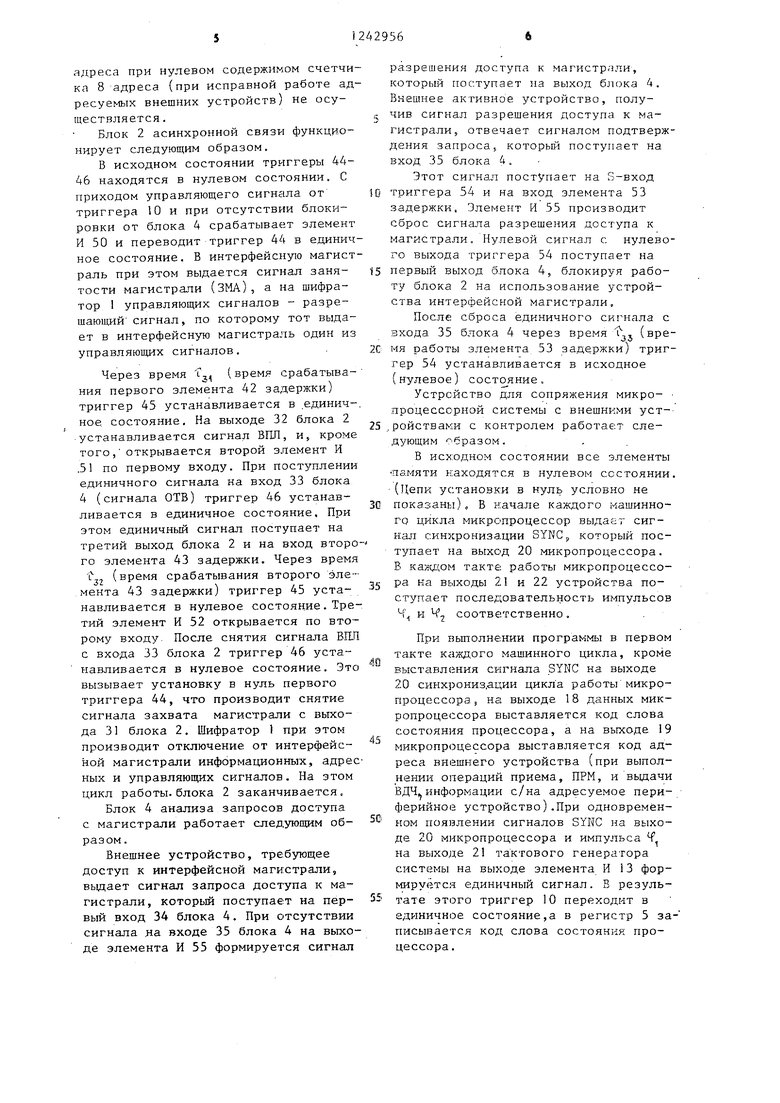

Блок 4 анализа запросов (фиг. З) содержит элемент 53 задержки, триггер 54 управления и элемент Р1 55.

Устройство работает следующим образом.

В начале кaJкдoгo машинного цикла обращения микропроцессора к внешним устройствам в такте Т микропроцессор вырабатывает синхронизирующий сигнап SYNC на выходе 20, по которому производится установка в единицу триггера 10 управления и формируется сигнал синхронизации первого буферного регистра 5. Б результате этого производится запись кода слова состояния процессора в регистр 5, В этом же такте на выходе 19микропроцессора

устанавливается код адреса внешнего устройства, к которому осуществляется обращение. На выходе 39 устройства устанавливается нулевой сигнал готовности. Код слова состояния: процессора из регистра 5 поступает на вход шифратора 1, и на одном из его соот- ветствукшщх выходов устанавливается единичный сигнал. Кроме того, после | перевода триггера 10 в единичное состояние блок 2 асинхронной связи в случае ЕЮЗМОЖНОСТИ обмена информацией с выбранным внешним устройством выдает сигнал выполнения (ВПЛ) на втором выходе 32. По сигналу ВПЛ. адресуемое внешнее устройство выдает . сигнал ответа (ОТВ) в блок 2 асинхронной связи. При этом в рассматриваемом устройстве после разрешения выдачи сигнала ВПЛ осуществляется счет времени тдикла ожидания. Этот режим выполняется путем записи серии тактовых импульсов в счетчик 7. Число N импульсов соответствует доцус;тимому времени реакции адресуемого внешнего устройства на запрос. Если от вн:ешн€ го устройства приходит в пределах допустимого времени скг- нал ОТВ 5 то счет времени в счетчике 7 прекращается путем установки его в нуль. При этом в случае правильного функционирования адресуемого внешнего устройства содержимое счетчика 8 равно нулю. Модификация адреса сумматором 3 не выполнлется.

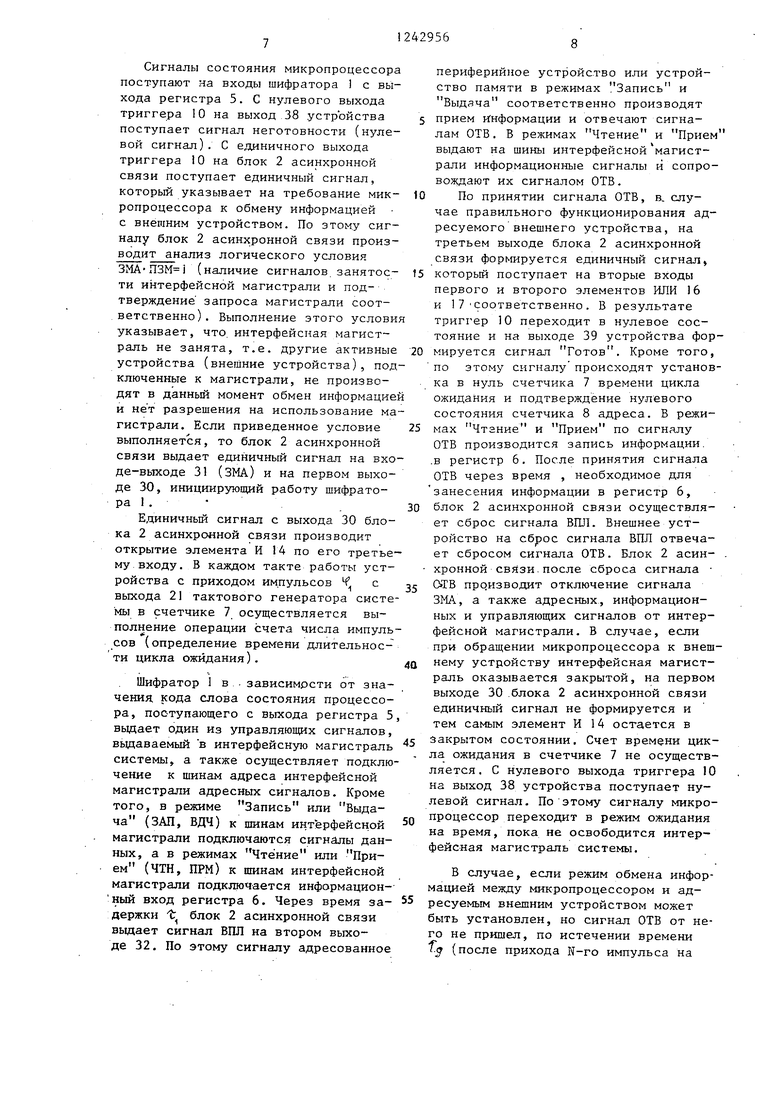

Работа шифратора 1 описана таблицей соответствия (табл. ),

Значения входных сигналов ,, шифратора 1 и значения его выходных сигналов на выходах 25-29 однозначно соответствуют кодам слова состояния процессора (PSW) при выполнении следующих циклов: MEMORY READ, MEMORY VffilTE, INPUT, OUTPUT, INTERPUT микропроцессора серии К 580 (INTEL sos A)

в случае, если в установленное (максимально допустимое) время сигнал ОТВ от адресуемого внешнего устройства не приходит, то с приходом (N+l)-ro импульса на выходе переполнения счетчика 7 формируется единичный сигнал,который записывается в счетчик 8. Следовательно,микропроцессор в это случае выходит в режим Ожидание , Сформированным в счетчике 8 кодом 00.,.01 происходит модификация адре- .са внешнего устройства. Операцию модификации осуществляет сумматор 3 адреса. Модификации подвергаются старших разрядов кода адреса путем увеличения на единицу этого кода. В результате этого формируется коц адреса следующего по счету внешнего устройства. В рассматриваемом случае триггер 10 в исходное состояние не возвращается, а остается в единичном состоянии, что обеспечивает возможность повторного осуществления счета времени цикла ожидания, Если сигнал ОТВ приходит в пределах установленного времени, то в j-м также режима (цикла) ожидания по заднему фронту импульса 4 он выходит из режима ожидания и продолжает работу.В противном случае содержимое счетчика 8 увеличивается еще на единицу и в нем находится код 000...10. В результате этого

Таблица

I

Происходит операция модификации адреса и формируется код адреса следующего внешнего устройства. Всякий раз после записи информации,в счетчик 8 на выходе 37 устройства формируется соответствующий код. В случае, если происходит отказ всех внешних устройств, то после отказа последнего из них на выходе 39 устройства формируется сигнал отказа.

Работа сумматора 3 адреса при модификации адреса внешнего устройства может быть описана таблицей соответствия (табл.. 2),

Таблица 2

00000000 00101101 00111101 o l 000000

00000000 00110101 01000101 01001000

Из таблицы 2 соответствия сумматора 3 адреса следует, что модификация

дреса при нулевом содержимом счетчиа 8 адреса {при исправной работе адесуемых внешних устройств) не осуествляется .

Блок 2 асинхронной связи функциоирует следующим образом.

В исходном состоянии триггеры 44- 46 находятся в нулевом состоянии. С риходом управляющего сигнала от триггера 10 и при отсутствии блокировки от блока 4 срабатывает элемент И 50 и переводит триггер 44 в единичное состояние. В интерфейсную магистраль при этом выдается сигнал занятости магистрали (ЗМА), а на шифратор 1 управляющих сигналов - разрешающий сигнал, по которому тот выдает в интерфейсную магистраль один из управляющих сигналов.

Через время L,, (время срабатыва- ния первого элемента 42 задержки) триггер 45 устанавливается в .единич-. ное состояние. На выходе 32 блока 2 устанавливается сигнал ВГШ, и, кроме того, открывается второй элемент И .5 по первому входу. При поступлении единичного сигнала на вход 33 блока 4 (сигнала ОТВ) триггер 46 устанавливается в единичное состояние. При этом единичный сигнал поступает на третий выход блока 2 и на вход второ- го элемента 43 задержки. Через время t . (время срабатывания второго элемента 43 задержки) триггер 45 устанавливается в нулевое состояние . Третий элемент И 52 открывается по второму входу. После снятия сигнала ВШ1 с входа 33 блока 2 триггер 46 уста- навливается в нулевое состояние. Это вызывает установку в нуль первого триггера 44, что производит снятие сигнала захвата магистрали с выхода 31 блока 2. Шифратор 1 при этом производит отключение от интерфейсной магистрали информационных, адресных и управляющих сигналов. На этом цикл работы.блока 2 заканчивается.

Блок 4 анализа запросов доступа с магистрали работает следующим образом .

Внешнее устройство, требующее доступ к интерфейсной магистрали, выдает сигнал запроса доступа к магистрали, который поступает на первый вход 34 блока 4. При отсутствии сигнала .на входе 35 блока 4 на выходе элемента И 55 формируется сигнал

0

s

0

5

0

i

разрешения доступа к магистрали, который поступает на выход блока 4. Внешнее активное устройство, получив сигнал разрешения доступа к магистрали, отвечает сигналом подтверждения запроса, который поступает на вход 35 блока 4.

Этот сигнал поступает на S-вход триггера 54 и на вход элемента 53 задержки. Элемент И 55 производит сброс сигнала разрешения доступа к магистрали. Ну.левой сигнал с нулевого выхода триггера 54 поступает на первый выход б.лока 4, блокируя работу блока 2 на использование устройства интерфейсной магистрали.

Пос.ле сброса единичного сигнала с входа 35 блока 4 через время f jj (время работы .элемента 53 задержки) триггер 54 устанав.ливается в исходное (нулевое) состояние.

Устройство для сопряжения микро- процессорной системы с внешними уст- .ройствами с контролем работает следующим образом.

В исходном состоянии все элементы памяти находятся в нулевом состоянии. (Цепи установки в нуль условно не показаны), В н:ачале каждого машинного цикла микропроцессор выдает сигнал синхронизации SYNCj который поступает на выход 20 микропроцессора. В кахсдом такте работы микропроцессора ка выходы 2 и 22 устройства по- ст упает последовательность импульсов Ч и 2 соотв€1тственно .

При вьшолнении программы в первом такте каждого машинного цикла, кроме выставления сигнала SYNC на выходе 20 синхрониз.ации цикл а работы микропроцессора, на выходе 18 данных микропроцессора выставляется код слова состояния процессора, а на выходе 19 микропроцессора выставляется код адреса внешнего устройства (при выполнении операций приема, ИРМ, и вьщачи ВДЧ информации с/на адресуемое периферийное устройство).При одновременном появлении сигналов SYNC на выходе 20 микропроцессора и импульса f на выходе 2 тактового генератора системы на выходе элемента И 13 фор- труется единичный сигнал. В результате этого триггер 10 переходит в единичное состояние,а в регистр 5 записывается код слова состояния процессора .

Сигналы состояния микропроцессора поступают на входы шифратора 1 с выхода регистра 5. С нулевого выхода триггера 10 на выход 38 устройства поступает сигнал неготовности (нулевой сигнал). С единичного выхода триггера 10 на блок 2 асинхронной связи поступает единичный сигнал, который указывает на требование мик- ропроцессора к обмену информацией с внешним устройством. По этому сигналу блок 2 асинхронной связи произ- водит анализ логического условия (наличие сигналов занятое- ти интерфейсной магистрали и подтверждение запроса магистрали соответственно). Выполнение этого услови указывает, что, интерфейсная магистраль не занята, т.е. другие активные устройства (внешние устройства), подключенные к магистрали, не производят в данный момент обмен информацие и не т разрешения на использование магистрали. Если приведенное условие выполняется, то блок 2 асинхронной связи выдает единичный сигнал на входе-выходе 31 (ЗМА) и на первом выходе 30, инициирующий работу шифратора 1 .

Единичньш сигнал с выхода 30 блока 2 асинхронной связи производит открытие элемента И 14 по его третье- му.входу, в каждом такте работы устройства с приходом импульсов с выхода 21 тактового генератора систе мы в счетчике 7, осуществляется выполнение операции счета числа импульсов (определение времени длительности цикла ожидания),

Шифратор I в . зависимости от значения кода слова состояния процессора, поступающего с выхода регистра 5 выдает один из управляющих сигналов, вьщаваемый в интерфейсную магистраль системы, а также осуществляет подключение к шинам адреса интерфейсной магистрали адресных сигналов. Кроме того, в режиме Запись или Выдача (ЗАЛ, ВДЧ) к шинам интерфейсной магистрали подключаются сигналы данных, а в режимах Чтение или Прием (ЧТН, ПРМ) к шинам интерфейсной магистрали подключается информацион- ный вход регистра 6. Через время за- держки Г| блок 2 асинхронной связи вьщает сигнал ВПЛ на втором выходе 32. По этому сигналу адресованное

периферийное устройство или устройство памяти в режимах Запись и Выдача соответственно производят прием информации и отвечают сигналам ОТВ. В режимах Чтение и Прием выдают на шины интерфейсной магистрали информационные сигналы и сопро- воядз,ают их сигналом ОТВ.

По принятии сигнала ОТВ, в, случае правильного функционирования адресуемого внешнего устройства, на третьем выходе блока 2 асинхронной связи формируется единичный сигнал который поступает на вторые входы первого и второго элементов ИЛИ 16 и 17 Соответственно. В результате триггер 10 переходит в нулевое состояние и на выходе 39 устройства формируется сигнал Готов. Кроме того, по этому сигналу происходят установка в нуль счетчика 7 времени цикла ожидания и подтверждение нулевого состояния счетчика 8 адреса. В режимах Чтгние и Прием по сигналу ОТВ производится запись информации, .в регистр 6. После принятия сигнала ОТВ через время , необходимое для занесения информации в регистр 6, блок 2 асинхронной связи осуществляет сброс сигнала ВПЛ. Внешнее устройство на сброс сигнала ВПЛ отвечает сбросом сигнала ОТВ. Блок 2 асин- хронной связи.после сброса сигнала производит отключение сигнала ЗМА, а также адресных, информационных и управляющих сигналов от интерфейсной магистрали. В случае, если при обращении микропроцессора к внешнему устройству интерфейсная магистраль оказывается закрытой, на первом выходе 30 .блока 2 асинхронной связи единичный сигнал не формируется и тем самым элемент И 14 остается в Закрытом состоянии. Счет времени цикла ожидания в счетчике 7 не осуществляется. С нулевого выхода триггера 10 на выход 38 устройства поступает нулевой сигнал. По этому сигналу микропроцессор переходит в режим ожидания на время, пока не освободится интерфейсная магистраль системы.

В случае, если режим обмена информацией между микропроцессором и адресуемым внешним устройством может быть установлен, но сигнал ОТВ от него не пришел, по истечении времени 1 (после прихода N-ro импульса на

счетчик 7) с приходом (N+l)-ro импульса на выходе счетчика 7 формируется сигнал переполнения, которьй поступает на счетный вход счетчика 8 В этом случае в счетчике 8 устанавливается код единицы. По коду содержимого счетчика 8 в сумматоре 3 происходит модификация кода адреса адресуемого .внешнего устройства. Модификация адреса осуществляется путем увеличения на единицу кода адреса внешнего устройства. При этом продолжается осуществление контроля длительности цикла ожид ания . . В счетчик 7 записываются импульсы синхронизации Ч .

Если сигнал ОТВ приходит в пределах допустимого времени, работа устройства продолжается по описанному алгоритму. .

В случае, если второе адресуемое внешнее устройство не выдает сигнал ОТВ в пределах установленно.го времени, происходит повторное изменение содержимого счетчика 8. В нем записан код два. По этому коду происходит модификация кода адреса внешнего устройства путем увеличения на два первоначального кода адреса внешнего устройства.

Если отказ происходит во всех внешних устройствах, то после записи L-й единицы в счетчик 8 и по истечении времени i на выходе 39 устройства установлен сигнал отказа.

Организация прерывания микропроцессора осуществляется следующим образом.

Внешнее устройство, требующее прерывание прог раммы, вьщает в интерфейсную магистраль по шине ЗПР сигнал запроса прерывания, В устройстве этот сигнал трансформируется на вход ПРЕР микропроцессора. После Выполнения очередной команду микропроцессор воспринимает сигнал ПРЕР (если вход ПРЕР не заблокирован) и во время обращения за очередной командой в «коде слова состояния устанавливает сигнал подтверждения запроса прерывания П. ЗП. ПРЕР. Шифратор 1 в этом случае формирует сигнал РПР на своем шестом выходе 29. Сигнал РПР проходит последовательно через все инициативные периферийные устройства. Ближайшее периферийное устройство, вьздавшее запрос на прерывание, воспринимает сигнал РПР, блокирует его дальнейшее прохождение и выдает на интерфейсную магистраль код вектора прерывания, сопровождая его сигналом ОТВ.

Таким образом, из алгоритма функционирования устройства для сопряже

ния микропроцессорной системы с внешними устройствами с контролем следует, что в нем осуществляется контроль времени ответной реакции адресуемого- внешнего устройства и в случае воз- никновения отказа в нем оно обеспечивает коммутацию следующего внешнего устройства.

Формула изобретения

Устройство для сопряжения микропроцессорной системы с внешними устройствами с контролем,содержащее блок асинхронной связи, блок анализа запросов, шифратор, первый и второй буферные регистры, первый и второй блоки элементов И, триггер управления и первый элемент И, причем выход данных микропроцессора соединен с.

информационным входом первого блока алементов И и информационным входом первого буферного.регистра, выход первого блока элементов И соединен с информационной шиной интерфейсной магистрали системы и информационным входом второго буферного регистра, выход первого буферного регистра сое динен с информационным входом шифратор.а, выходы первого, второго и третьего разрядов первого выхода которого соединены с управляющими входами перв.ого и второго блоков элементов И И Е1ходом разрешения второго буферного регистра соответственно, а второй - шестой выходы шифратора соединены с шинами чтения, записи, приема, выдачи и разрешения прерывания интерфейсной магистрали систе1У1ы, выход второго буферного регистра подключен к шине данных микропроцессора, первая группа разрядов адресной шины г шкропроцессора соединена с соответствующими разрядами информационного входа второго блока элементов И, выход которого соединен

с адресной шиной интерфейсной магист рали системы, первьй выход блока асинх)онной связи соединен со стро- бируюпщм входом шифратора, вход-вы11

ход блока acHHXpoHiioti СВУПН соединен с шиной сигнала занятости интерфе 1С- ной маг истрали системы, первый вход блока асинхронной связи соединен с первым.выходом блока анализа запросов , второй выход которого соединен с шиной разрешения доступа интерфейсной магистрали системы, второй выход блока асинхронной связи соединен с шиной выполнения интерфейсной магистрали системы, второй вход блока асинхронной связи соединен с шиной ответа интерфейсной магистрали системы, первый, и второй вхрды блока анализа запроса соединены с шинами запроса доступа и подтверждения запроса интерфейсной магистрали системы соответственно, выход синхронизации цикла работы микропроцессора подключен к первому входу первого элемента И, первый выход синхронизации тактового генератора системы подключен к второму входу первого элемента И, выход которого соединен с S-входом триггера управления и входом синхронизации первого буферного регистра, единичный выход триггера управления соединен с. третьим входом блока асинхронной связи, нулевой

выход триггера управления является выходом готовности устройства, выход разрешения приема информации микропроцессора соединен с входом синхронизации второго буферного регистра,, шина запроса прерывания интерфейсной магистрали системы соединена с входом прерывания микропроцессора, отличающееся тем, что, с целью

повышения надежности устройства за счет осуществления контроля времени ответной реакции адресуемого внешнего устройства, оно содер жит счетчик времени цикла ожидания, счетчик ад

2429S61

реса, су.чматор адреса, дешифратор, iiepisbiii и второй элементы ИЛИ, второй и третий элементы И, причем первый выход синхронизации так-тового

5 генератора системы соединен с первым входом второго элемента И, выход которого соединен со счетным входом счетчика времени цикла ожидания, выход переполнения которого соединен

10 со ачетным входом счетчика адреса, информационный выход которого соединен с входом дешифратора и первым входом сумматора адреса, выход переполнения счетчика адреса соединен с

15 выходом отказа устройства и первыми входами первого элемента ИЛИ и третьего элемента И, второй выход синхронизации тактового генератора системы соединен с вторым входом третьего

20 элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с установочным входом счетчика адреса, вторая группа разрядов шины адреса микро25 процессора соединена с вторым входом сумматора.адреса, выход которого соединен с соответствующими разрядами информационного входа второго блока элементов И, третий выход блока

30 асинхронной связи соединен с вторыми входами первого и второго элементов ИЛИ, выход перЬого элемента ИЛИ соединен с R-входом триггера управления и установочным входом счетчика вре25 мени цикла ожидания, выход дешифратора является выходом индикации номера отказавшего внешнего устройства, единичный выход триггера управления соединен с вторым входом

40 второго элемента И, третий вход которого срединен с первым выходом блока асинхронной связи.

фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропроцессорной связи | 1978 |

|

SU734657A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Устройство микропроцессорной связи | 1983 |

|

SU1124275A1 |

| Устройство для сопряжения микропроцессора с периферийными устройствами | 1987 |

|

SU1434440A1 |

| Устройство микропроцессорной связи | 1986 |

|

SU1361568A2 |

| Устройство для сопряжения абонентов с каналом связи | 1987 |

|

SU1432537A1 |

| Устройство для сопряжения микроЭВМ с внешним устройством | 1985 |

|

SU1283780A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Система для отладки программ | 1987 |

|

SU1481774A1 |

| Устройство для обмена данными в вычислительной сети | 1988 |

|

SU1599864A1 |

Изобретение относится к микропроцессорной технике и может быть использовано при проектировании микропроцессорных систем и микро-ЭВМ с высокими показателями надежности. Целью изобретения является повьшение надежности устройства за счет осуществления контроля времени ответной реакции адресуемого внешнего устройства. В случае возникновения отказа внешнего устройства устройство для сопряжения обеспечивает коммутацию следующего внешнего устройства. Устройство содержит шифратор, блок асинхронной связи, сумматор адреса, блок анализа запросов, два буферных регистра, счетчик времени цикла ожидания, счетчик адреса, дешифратор. Триггер управления, два блока элементов И, три элемента И и два элемента ИЛИ, 3 ш1., 2 табл. (Л ю со сд Од

| Коффрон Дж | |||

| Технические средства микропроцессорных систем | |||

| - М.: Мир, 1983 | |||

| Устройство микропроцессорной связи | 1978 |

|

SU734657A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

Авторы

Даты

1986-07-07—Публикация

1984-11-19—Подача