Изобретение относится к цифровой и вычислительной технике, в частности к средствам контроля работы и поиска неисправностей в цифровых системах, и может использоваться при проектировании, отладки программ и проверке качества функционирования микропроцессорных систем (МПС).

Целью изобретения является повышение эффективности и полноты отладки и контроля,,

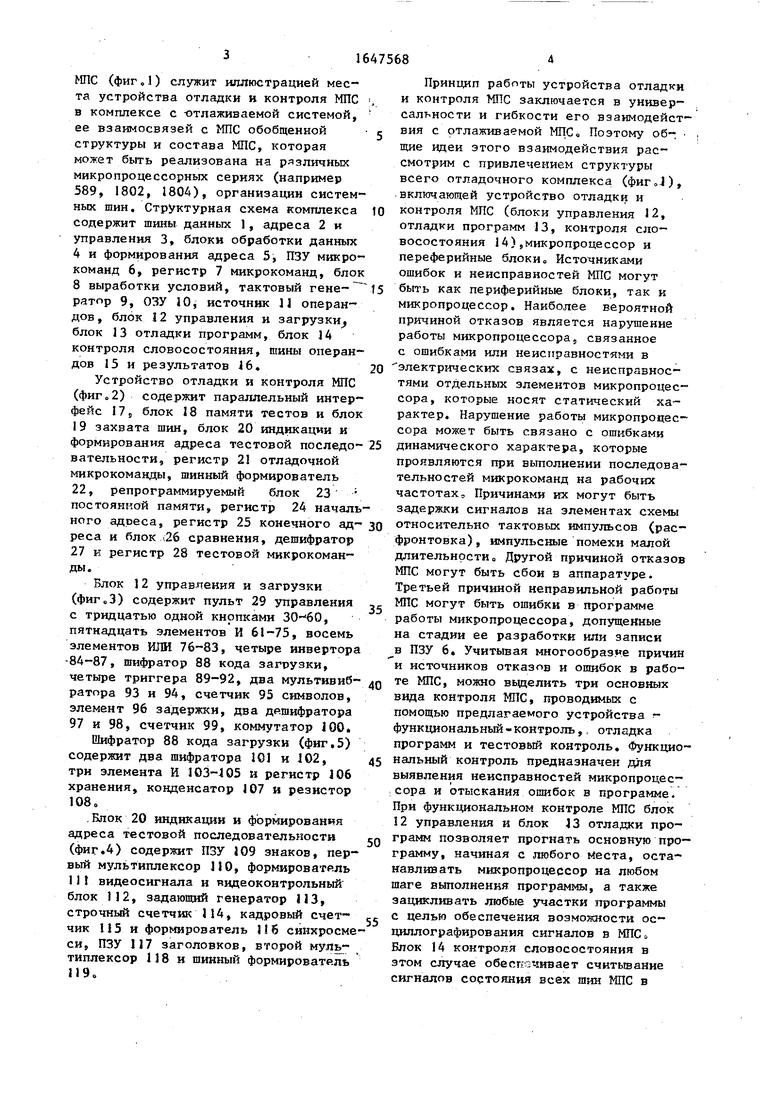

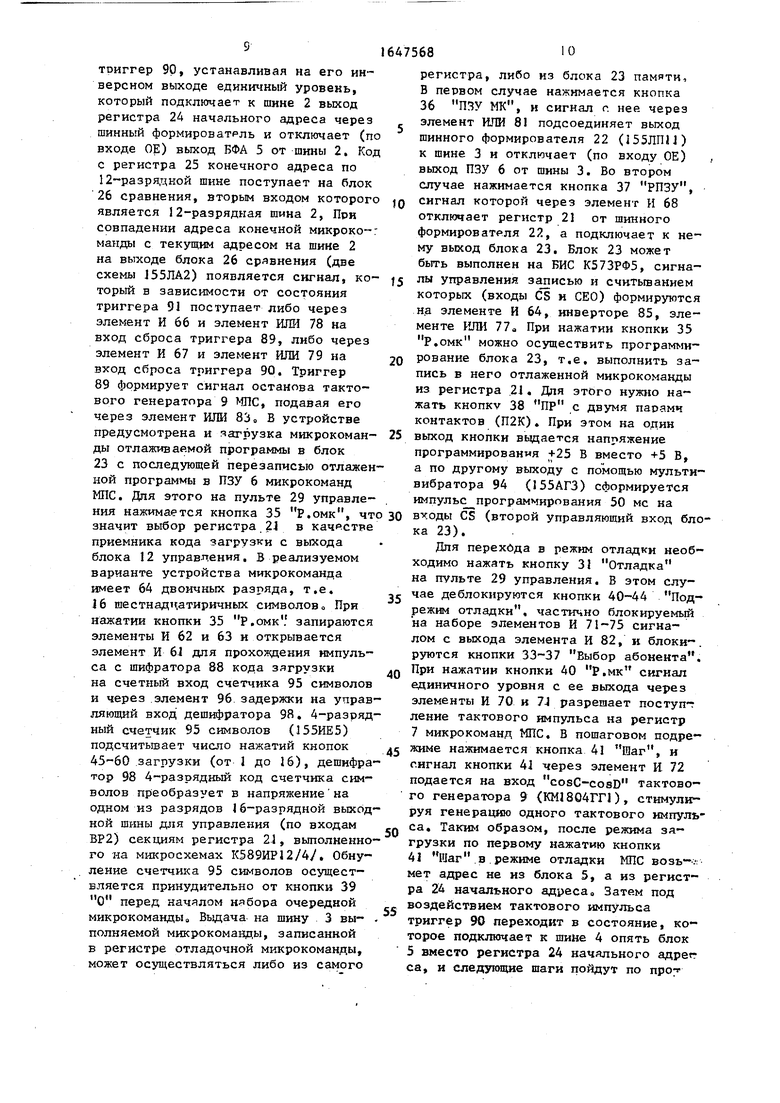

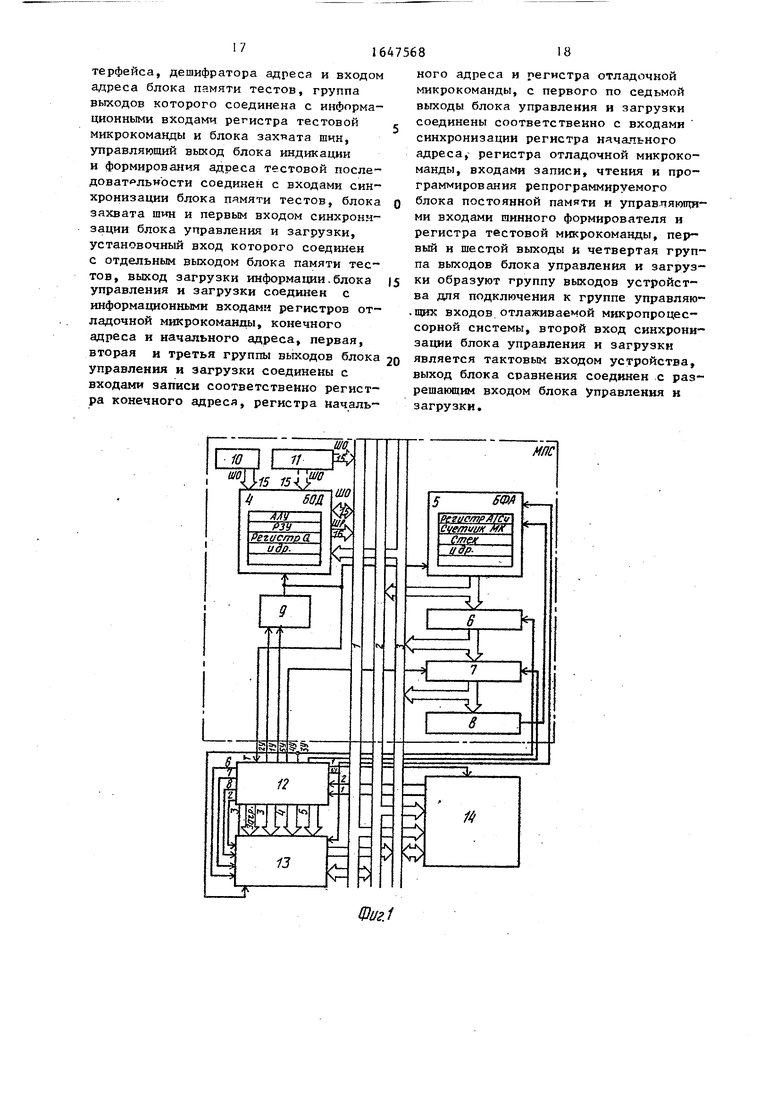

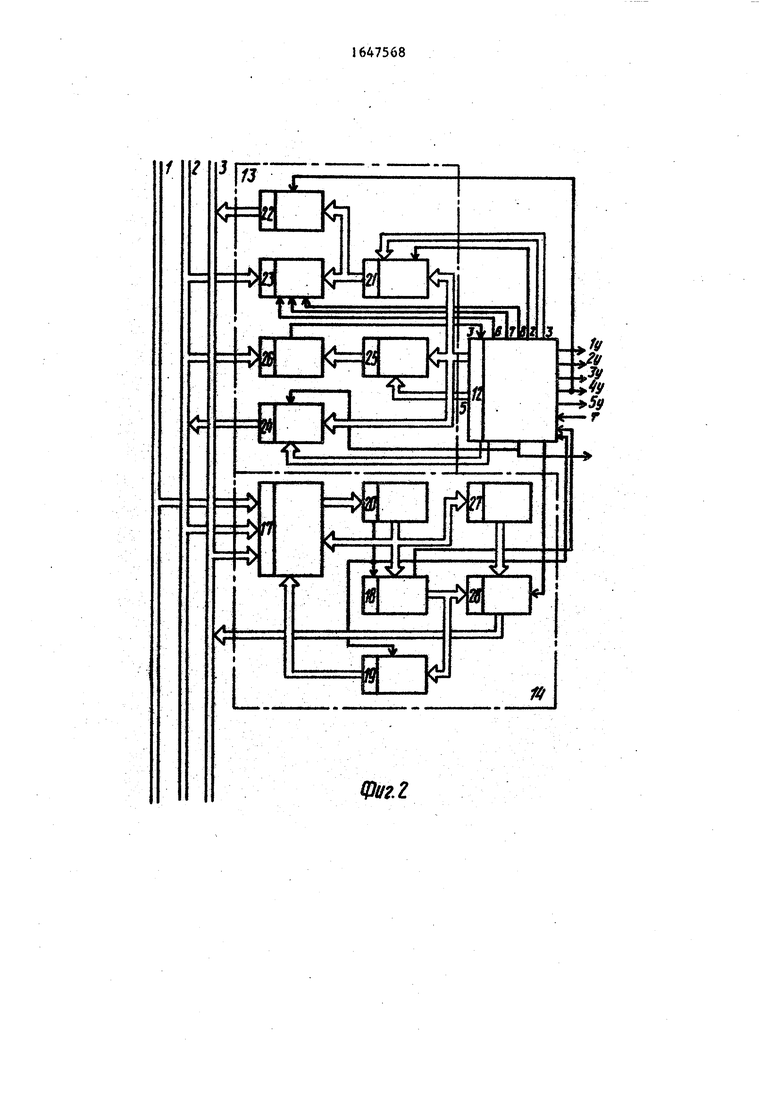

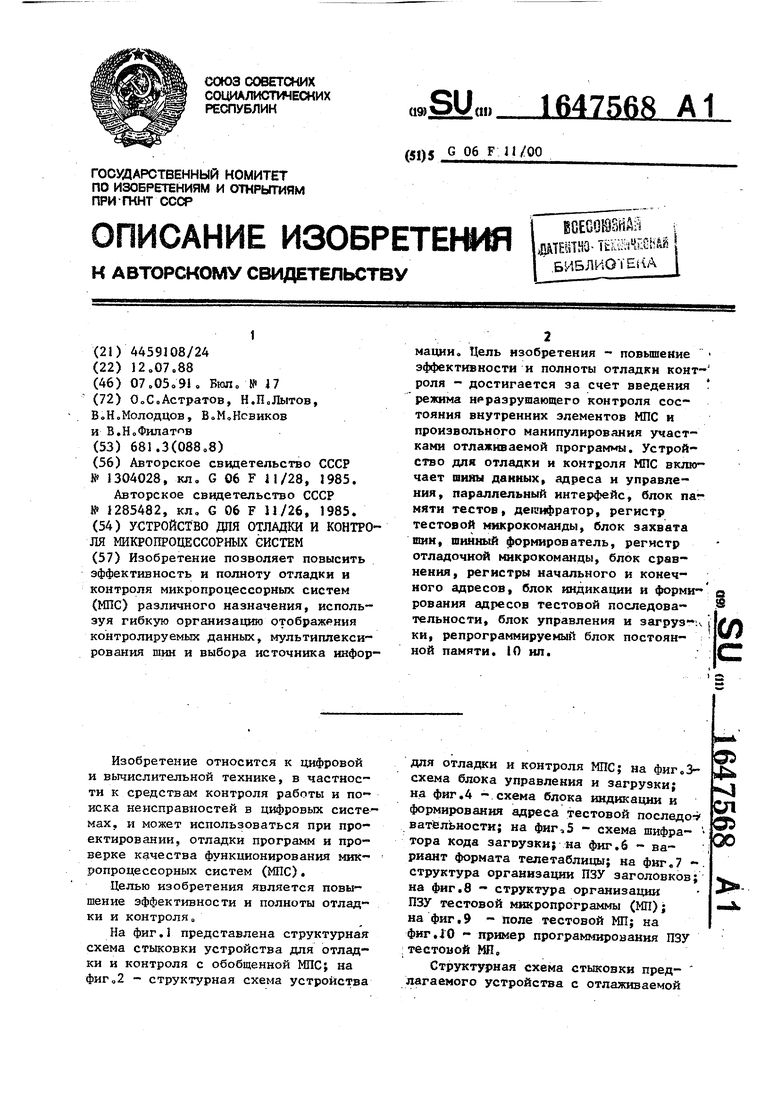

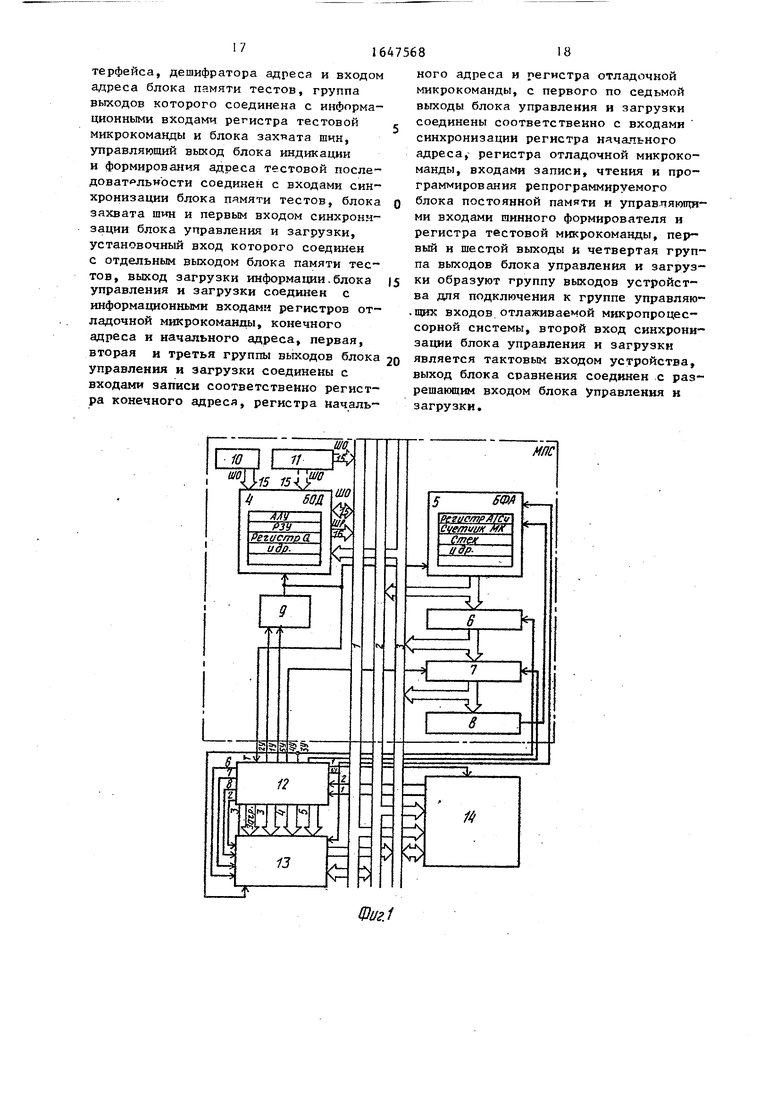

На фиг.1 представлена структурная схема стыковки устройства для отладки и контроля с обобщенной МПС; на фиг„2 - структурная схема устройства

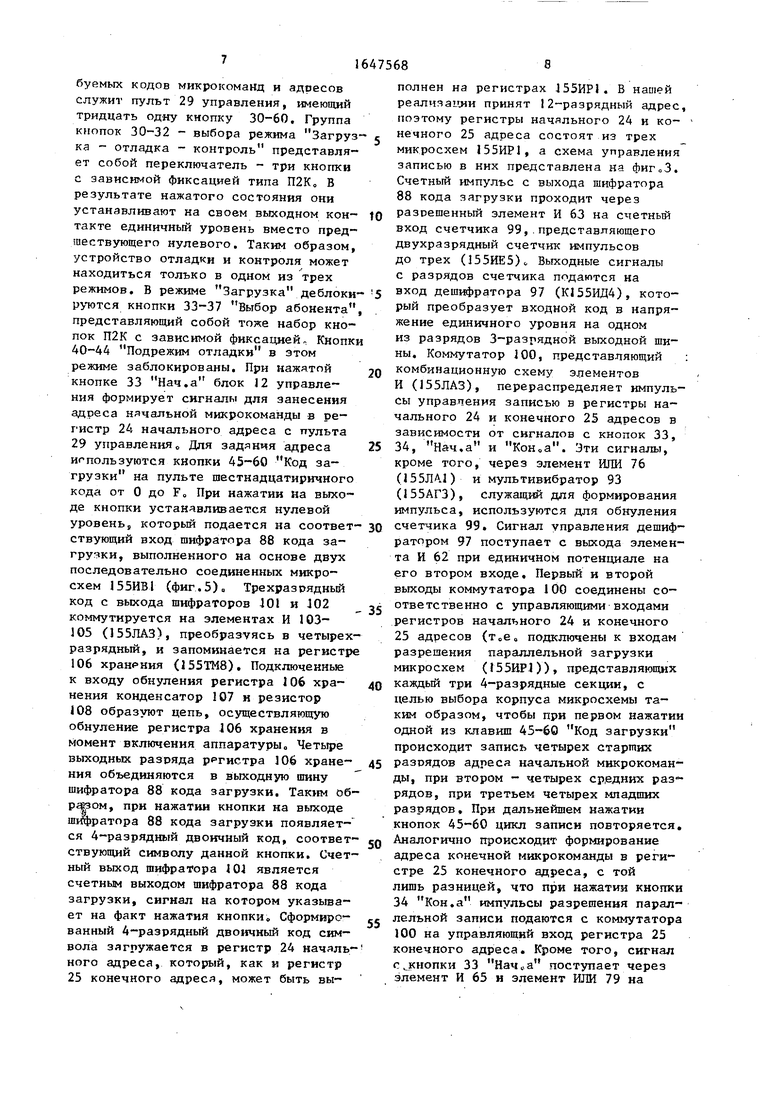

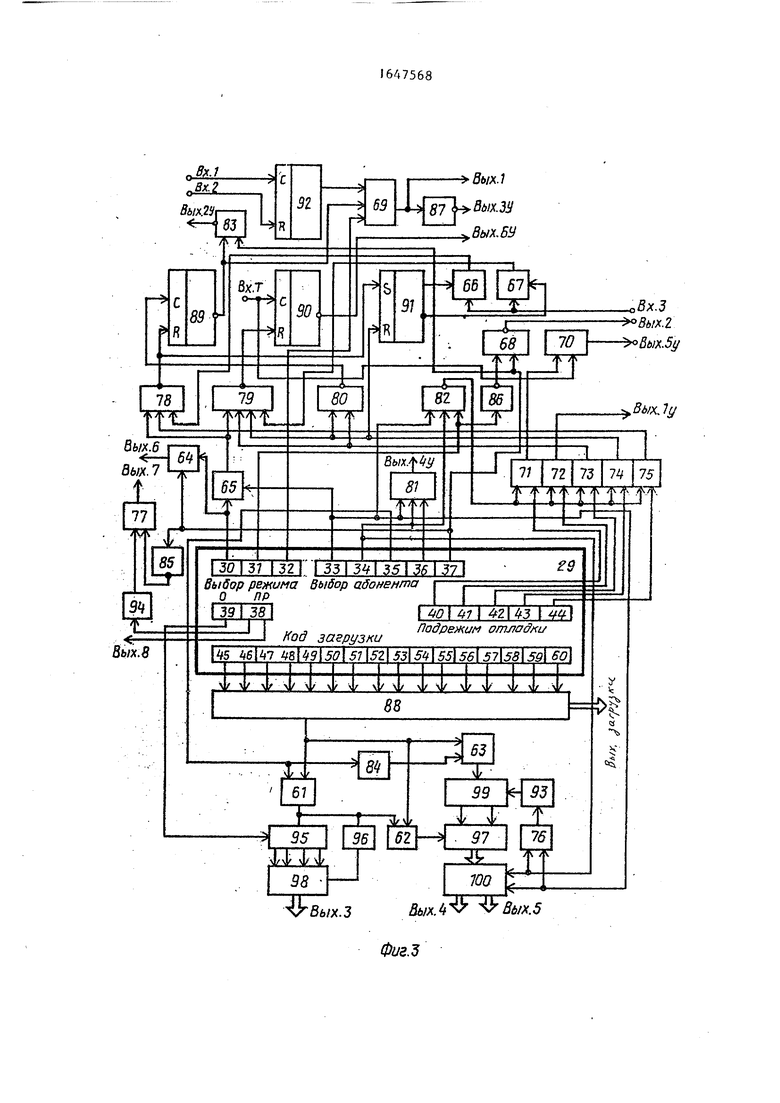

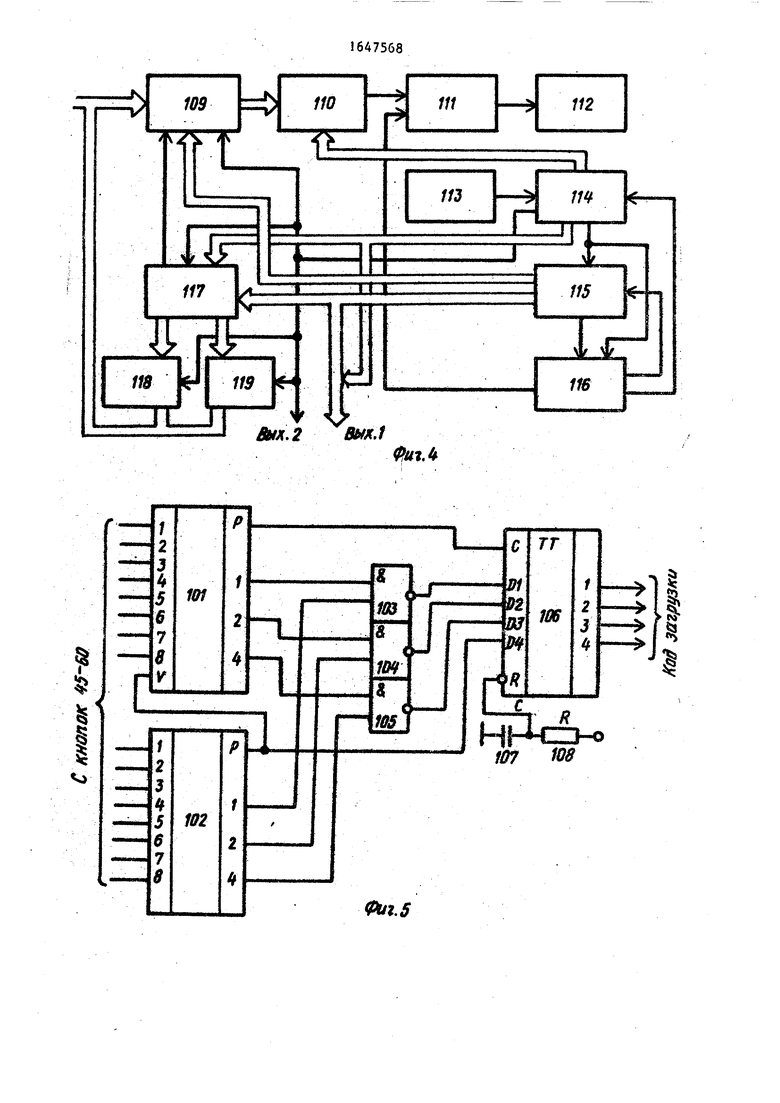

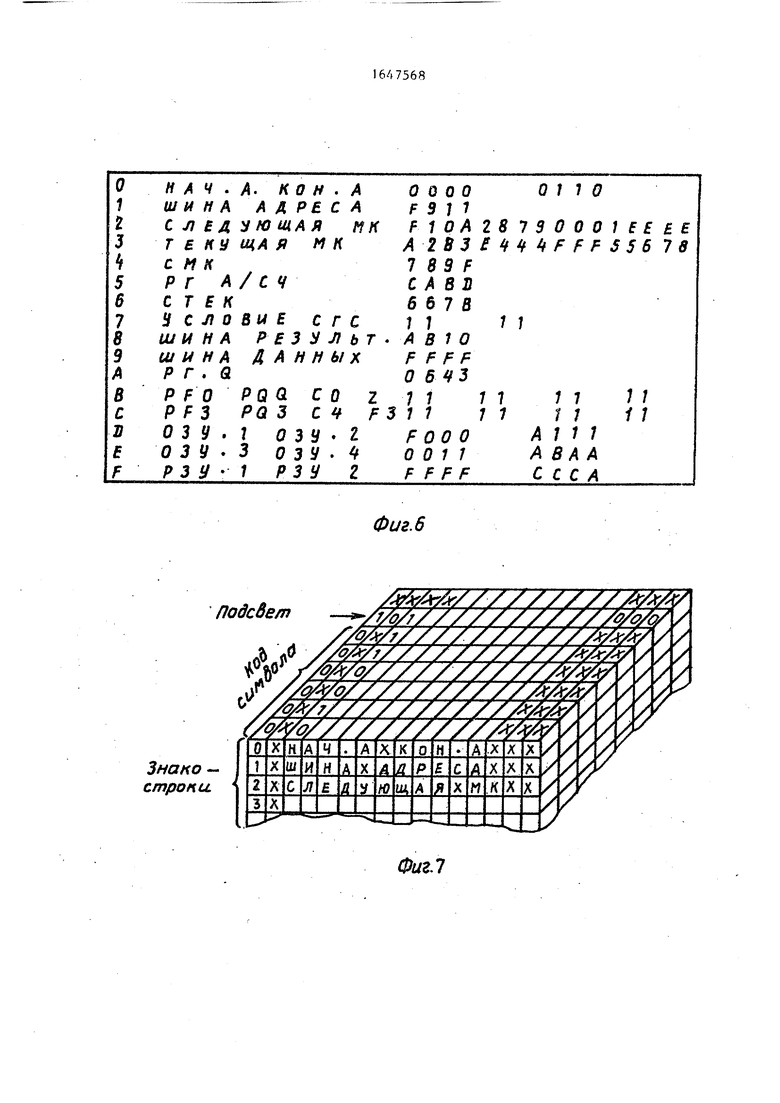

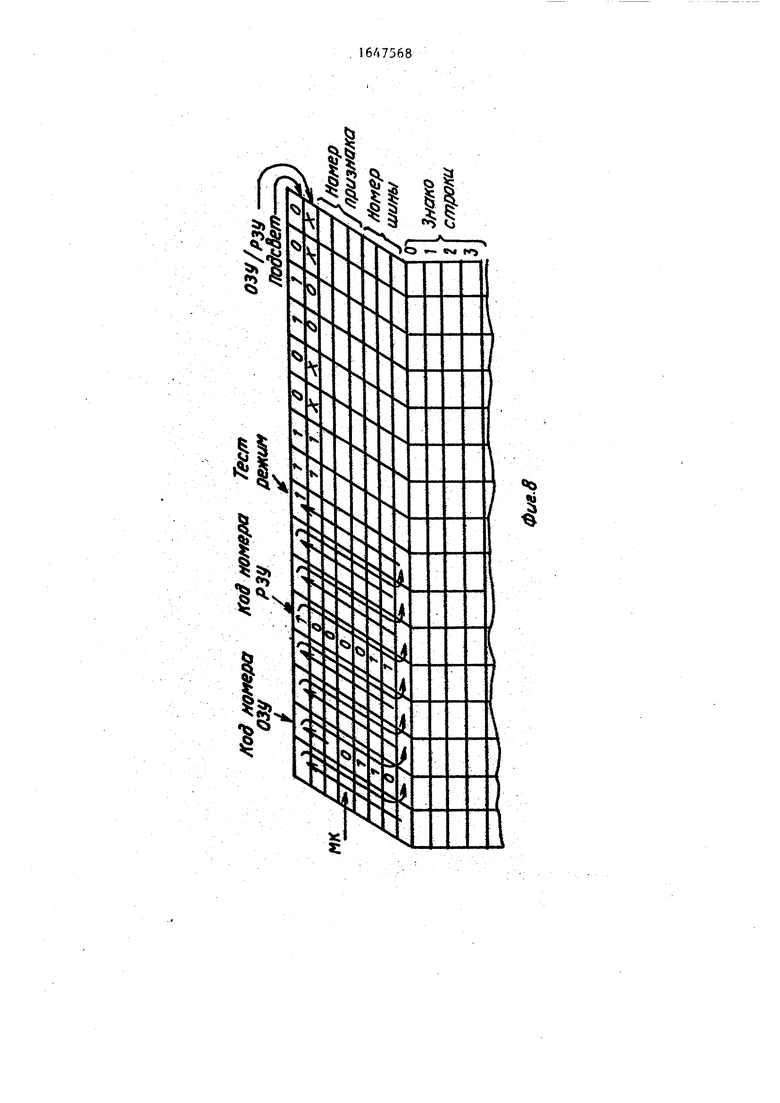

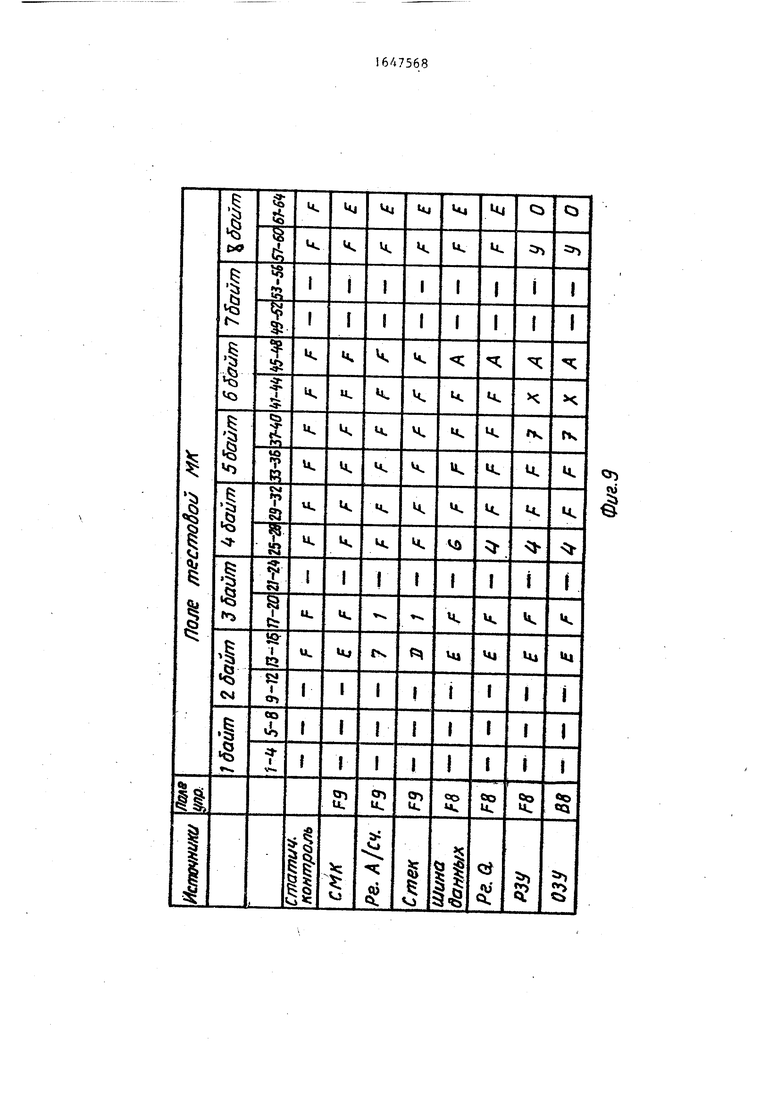

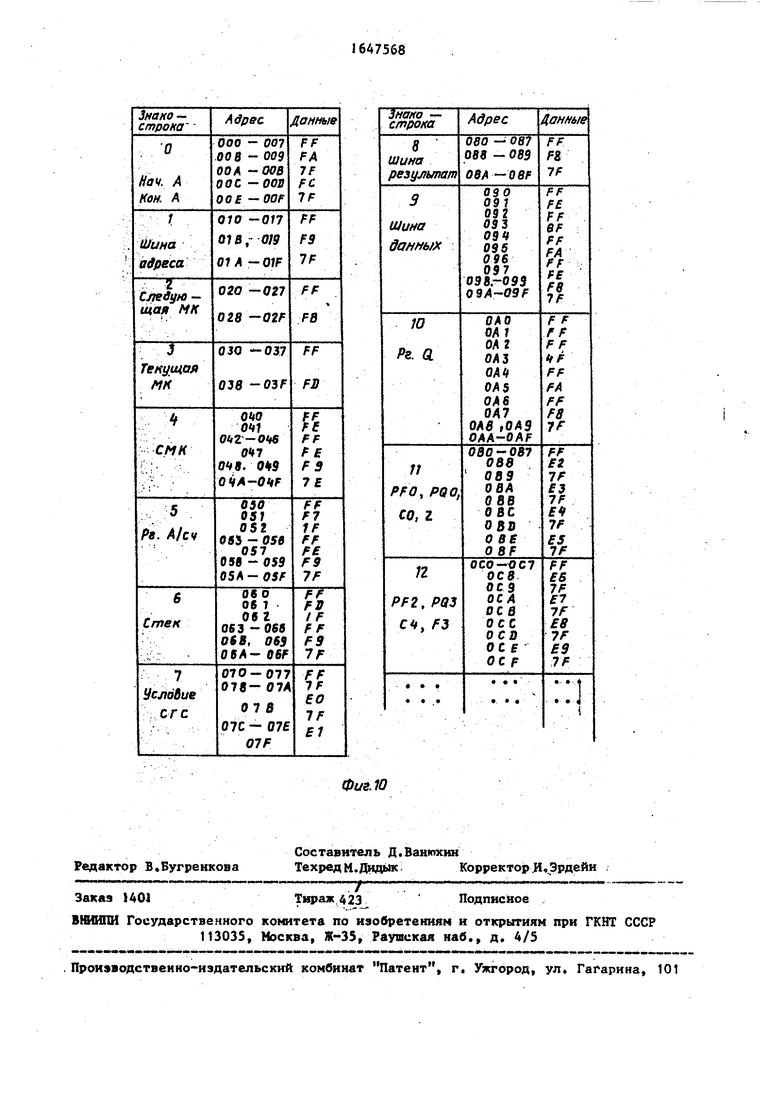

для отладки и контроля МПС; на фиг.З- схема блока управления и загрузки; на фиг.4 - схема блока индикации и формирования адреса тестовой последов вательности; на фиг,5 - схема шифра- тора кода загоузки; на фиг.6 - вариант формата телетаблицы; на фиг. 7 - структура организации ПЗУ заголовков; на фиг.8 - структура организации ПЗУ тестовой микропрограммы (МП); на фиг.9 - поле тестовой МП; на фиг,10 - пример программирования ПЗУ тестокой МП,

Структурная схема стыковки пред- лагаемого устройства с отлаживаемой

9

Јь СД

О5 00

МПС (фиг.1) служит иллюстрацией места устройства отладки и контроля МПС в комплексе с отлаживаемой системой, ее взаимосвязей с МПС обобщенной структуры и состава МПС, которая может быть реализована на различных микропроцессорных сериях (например 589, 1802, 1804), организации систем- ных шин. Структурная схема комплекса содержит шины данных 1, адреса 2 и управления 3, блоки обработки данных 4 и формирования адреса 5, ПЗУ микрокоманд 6, регистр 7 микрокоманд, блок 8 выработки условий, тактовый генератор 9, ОЗУ 10, источник 11 операн- дов, блок I2 управления и загрузки, блок 13 отладки программ, блок 14 контроля словосостояния, шины операндов 15 и результатов 16.

Устройство отладки и контроля МПС (фиг02) содержит параллельный интерфейс 175 блок 18 памяти тестов и блок 19 захвата шин, блок 20 индикации и формирования адреса тестовой последо- вательности, регистр 21 отладочной микрокоманды, шинный формирователь 22, репрограммируемый блок 23 ; постоянной памяти, регистр 24 начального адоеса, регистр 25 конечного ад- реса и блок 26 сравнения, дешифратор 27 к регистр 28 тестовой микрокоманды.

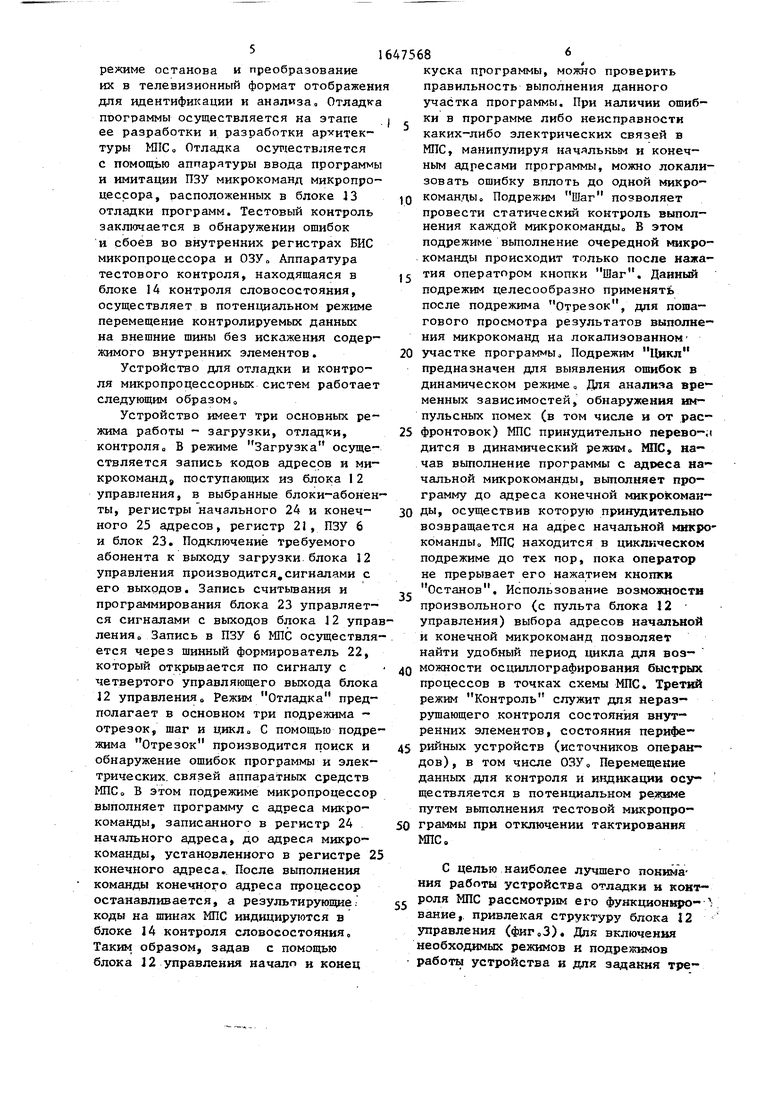

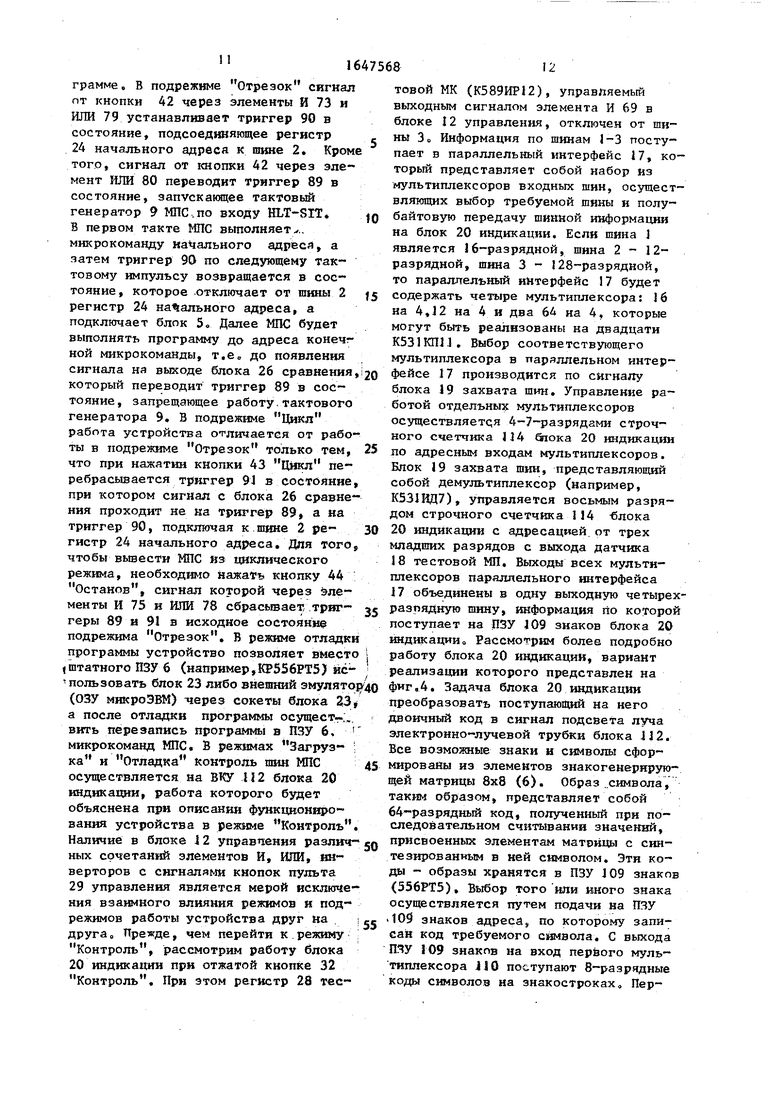

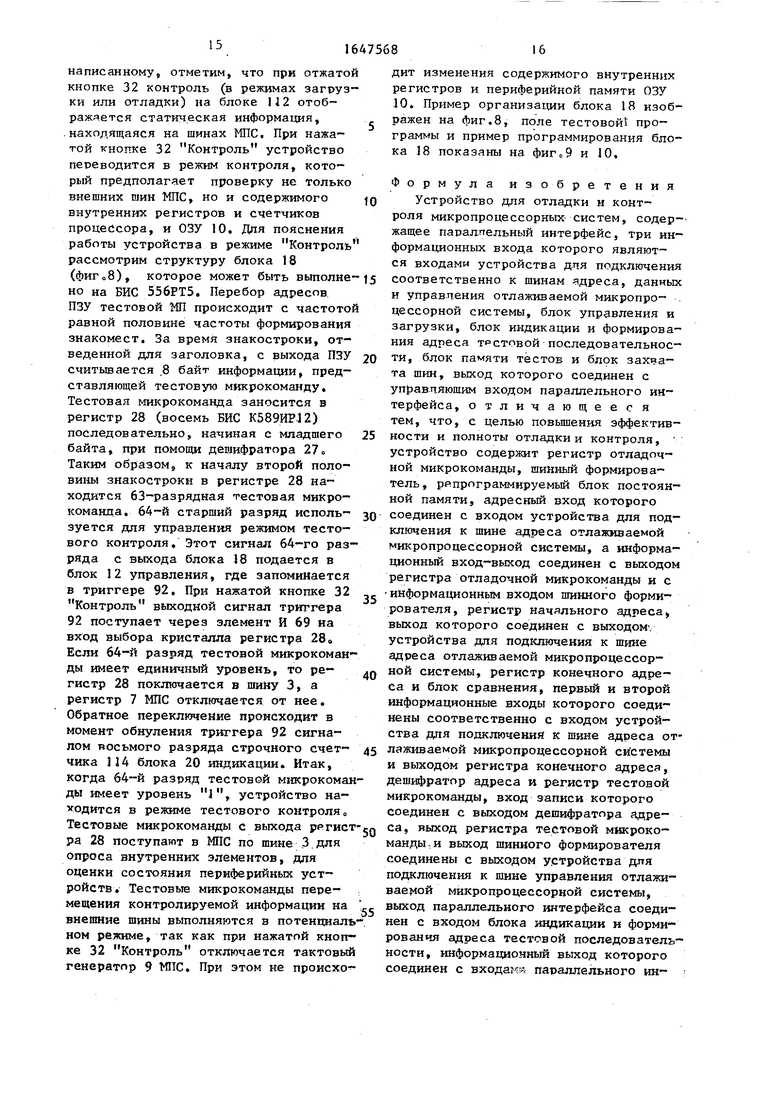

Блок 12 управления и загрузки (фиг«3) содержит пульт 29 управления с тридцатью одной кнопками ЗО- бО, пятнадцать элементов И 61-75, восемь элементов ИЛИ 76-83, четыре инвертора 84-87, шифратор 88 кода загрузки, четыре триггера 89-92, два мультивиб- ратора 93 и 94, счетчик 95 символов, элемент 96 задержки, два дршифратора 97 и 98, счетчик 99, коммутатор 100.

Шифратор 88 кода загрузки (фиг.5) содержит два шифратора 101 и 102, три элемента И 103-405 и регистр 106 хранения, конденсатор 107 и резистор 108.

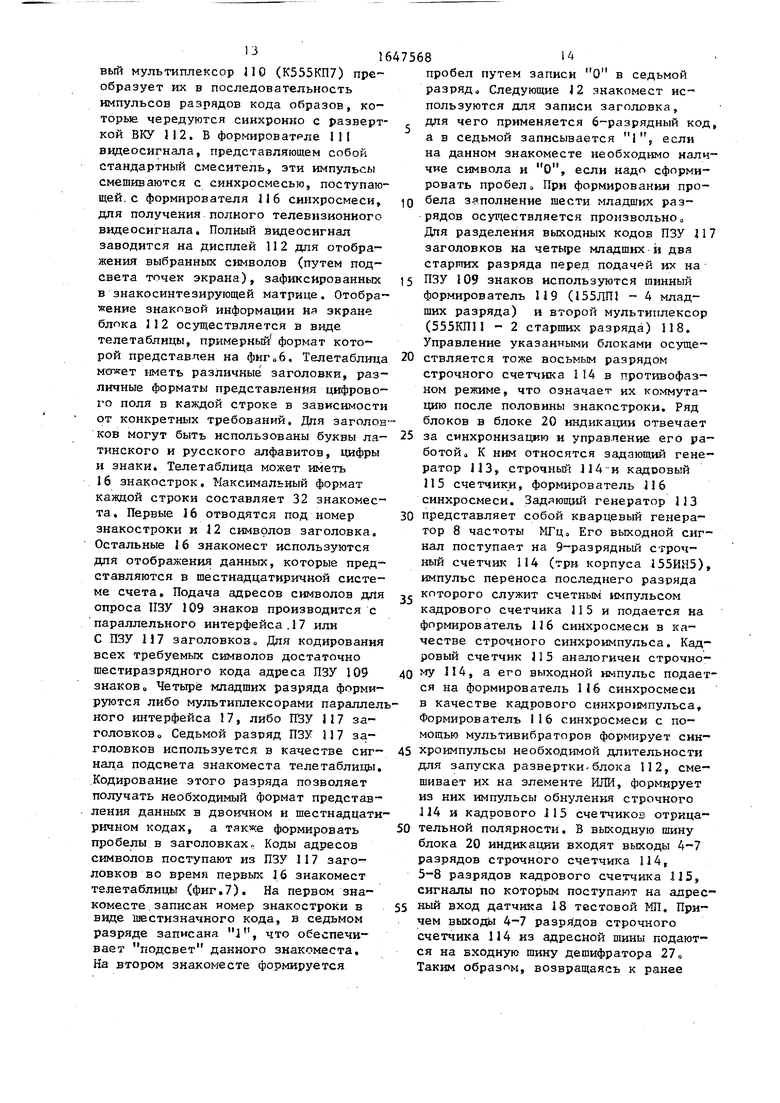

Блок 20 индикации и формирования адреса тестовой последовательности (фиг.4) содержит ПЗУ 109 знаков, первый мультиплексор 110, формирователь 111 видеосигнала и видеоконтрольный блок 112, задающий генератор 113, строчный счетчик 114, кадровый счет- чик 115 и формирователь 116 синхросме си, ПЗУ 117 заголовков, второй мультиплексор 118 и шинный формирователь 119

0

д

5

Q

5

Принцип работы устройства отладки и контроля МПС заключается в универсальности и гибкости его взаимодействия с отлаживаемой МПС. Поэтому об- щие идеи этого взаимодействия рассмотрим с привлечением структуры всего отладочного комплекса (фиго.1), включающей устройство отладки и контроля МПС (блоки управления 12, отладки программ 13, контроля словосостояния 14),микропроцессор и переферийные блоки,, Источниками ошибок и неисправностей МПС могут быть как периферийные блоки, так и микропроцессор. Наиболее вероятной причиной отказов является нарушение работы микропроцессора, связанное с ошибками или неисправностями в электрических сзязах, с неисправностями отдельных элементов микропроцессора, которые носят статический характер. Нарушение работы микропроцессора может быть связано с ошибками динамического характера, которые проявляются при выполнении последовательностей микрокоманд на рабочих частотах. Причинами их могут быть задержки сигналов на элементах схемы относительно тактовых импульсов (рас- фронтовка), импульсные помехи малой длительности0 Другой причиной отказов МПС могут быть сбои в аппаратуре. Третьей причиной неправильной работы МПС могут быть ошибки в программе работы микропроцессора, допущенные на стадии ее разработки или записи в ПЗУ 6. Учитывая многообразие причин и источников отказов и ошибок в работе МПС, можно выделить три основных вида контроля МПС, проводимых с помощью предлагаемого устройства - функциональный-контроль,, отладка программ и тестовый контроль. Функциональный контроль предназначен для выявления неисправностей микропроцессора и отыскания ошибок в программе. При функциональном контроле МПС блок 12 управления и блок 43 отладки программ позволяет прогнать основную программу, начиная с любого места, останавливать микропроцессор на любом шаге выполнения программы, а также зацикливать любые участки программы с целью обеспечения возможности ос- циллографирования сигналов в МПС Блок 14 контроля словосостояния в этом случае обеспечивает считывание сигналов состояния всех шин МПС в

режиме останова и преобразование их в телевизионный формат отображени для идентификации и анализа. Отладка программы осуществляется на этапе ее разработки и разработки архитектуры МНС о Отладка осуществляется с помощью аппаратуры ввода программы и имитации ПЗУ микрокоманд микропроцессора, расположенных в блоке J3 отладки программ. Тестовый контроль заключается в обнаружении ошибок и сбоев во внутренних регистрах БИС микропроцессора и ОЗУ Аппаратура тестового контроля, находящаяся в блоке 14 контроля словосостояния, осуществляет в потенциальном режиме перемещение контролируемых данных на внешние шины без искажения содержимого внутренних элементов.

Устройство для отладки и контроля микропроцессорных систем работает следующим образом

Устройство имеет три основных режима работы - загрузки, отладки, контроля В режиме Загрузка осуществляется запись кодов адресов и микрокоманд, поступающих из блока 1 2 управления, в выбранные блоки-абоненты, регистры начального 24 и конечного 25 адресов, регистр 21, ПЗУ 6 и блок 23. Подключение требуемого абонента к выходу загрузки блока 2 управления производится.сигналами с его выходов. Запись считывания и программирования блока 23 управляется сигналами с выходов блока J 2 упра ления Запись в ПЗУ 6 МПС осуществляется через шинный формирователь 22, который открывается по сигналу с четвертого управляющего выхода блока 12 управления Режим Отладка предполагает в основном три подрежима - отрезок, шаг и цикл С помощью подрежима Отрезок производится поиск и обнаружение ошибок программы и электрических связей аппаратных средств МПС о В этом подрежиме микропроцессор выполняет программу с адреса микрокоманды, записанного в регистр 24 начального адреса, до адреся микрокоманды, установленного в регистре 2 конечного адреса. После выполнения команды конечного адреса процессор останавливается, а результирующие, коды на шинах МПС индицируются в блоке 14 контроля словосостояния. Таким образом, задав с помощью блока 12 управления начал в конец

|

10

6475686

куска программы, можно проверить правильность выполнения данного участка программы. При наличии ошибки в программе либо неисправности каких-либо электрических связей в МПС, манипулируя начальным и конечным адресами программы, можно локализовать ошибку вплоть до одной микрокоманды. Подрежим Шаг позволяет провести статический контроль выполнения каждой микрокоманды В этом подрежиме выполнение очередной микрокоманды происходит только после нажа-

.с тия оператором кнопки Шаг. Данный подрежим целесообразно применять после подрежима Отрезок, для пошагового просмотра результатов выполнения микрокоманд на локализованном20 участке программы,, Подрежим Цикл предназначен для выявления ошибок в динамическом режиме„ Для анализа временных зависимостей, обнаружения импульсных помех (в том числе и от рас25 фронтовок) МПС принудительно перево-.i дится в динамический режим МПС, начав выполнение программы с адреса начальной микрокоманды, выполняет программу до адреса конечной микрокоман-

30 ды, осуществив которую принудительно возвращается на адрес начальной микрокоманды МПС находится в циклическом подрежиме до тех пор, пока оператор не прерывает его нажатием кнопки Останов. Использование возможности произвольного {с пульта блока 12 управления) выбора адресов начальной и конечной микрокоманд позволяет найти удобный период цикла для воз-

4Q можности осциллографирования быстрых процессов в точках схемы МПС Третий режим Контроль служит для нераз- рушающего контроля состояния внутренних элементов, состояния перифе45 рийных устройств (источников операндов), в том числе ОЗУ Перемещение данных для контроля и индикации осуществляется в потенциальном режиме путем выполнения тестовой микропрограммы при отключении тактирования

35

50

МПС.

С целью наиболее лучшего понимания работы устройства отладки и конт- роля МПС рассмотрим его функционнро- вание, привлекая структуру блока 12 управления (фиг.З). Для включения необходимых режимов и подрежимов работы устройства к для задания тре

буемых кодов микрокоманд и адресов служит пульт 29 управления, имеющий тридцать одну кнопку 30-60. Группа кнопок 30-32 - выбора режима Загруз ка - отладка - контроль представляет собой переключатель - три кнопки с зависимой фиксацией типа П2К„ В результате нажатого состояния они устанавливают на своем выходном кон- такте единичный уровень вместо предшествующего нулевого. Таким образом, устройство отладки и контроля может находиться только в одном из трех режимов. В режиме Загрузка деблоки руются кнопки 33-37 Выбор абонента представляющий собой тоже набор кнопок П2К с зависимой фиксацией. Кнопки 40-44 Подрежим отладки в этом режиме заблокированы. При нажятой кнопке 33 Нач.а блок 12 управления формирует сигналы для занесения адреса начальной микрокоманды в регистр 24 начального адреса с пульта 29 управления0 Для задянчя адреса попользуются кнопки 45-60 Код загрузки на пульте шестнадцатиричного кода от 0 до Г При нажатии на выходе кнопки устанавливается нулевой уровень, который подается на соответ ствующий вход шифратора 88 кода за- гручки, выполненного на основе двух последовательно соединенных микросхем 155ИВ1 (фиг.5)о Трехразрядный код с выхода шифраторов 401 и 402 коммутируется на элементах И 103105(155ЛАЗ), преобразуясь в четырехразрядный, и запоминается на регистре

106хранения (155ТМ8). Подключенные к входу обнуления регистра I06 хранения конденсатор 107 н резистор 108 образуют цепь, осуществляющую обнуление регистра 406 хранения в момент включения аппаратуры. Четыре выходных разряда рргистра 06 хранения объединяются в выходную шину шифратора 88 кода загрузки. Таким об раззом, при нажатии кнопки на выходе шифратора 88 кода загрузки появляется 4-разрядный двоичный код, соответствующий символу данной кнопки. Счетный выход шифратора 104 является счетным выходом шифратора 88 кода загрузки, сигнал на котором указывает на факт нажатия кнопки. Сформированный 4-разрядный двоичный код символа загружается в регистр 24 начального адреса, который, как и регистр 25 конечного адреса, может быть вы

20

25

с ю 5 30

35

40

45

50

55

полней на регистрах 455ИР1. В нашей реалччагуш принят 12-разрядный адрес, поэтому регистры начального 24 и ко- v нечного 25 адреса состоят из трех микросхем 155ИР1, а схема управления записью в них представлена на фиг03. Счетный импульс с выхода шифратора 88 кода загрузки проходит через разрешенный элемент И 63 на счетный вход счетчика 99, представляющего двухразрядный счетчик импульсов до трех (155ИЕ5)о Выходные сигналы с разрядов счетчика подаются на вход дешифратора 97 (К155ИД4), который преобразует входной код в напряжение единичного уровня на одном из разрядов 3-разр.ядной выходной шины. Коммутатор 400, представляющий : комбинационную схему элементов И (155ЛАЗ), перераспределяет импульсы управления записью в регистры начального 24 и конечного 25 адресов в зависимости от сигналов с кнопок 33, 34, Нач.а и Кон„а. Эти сигналы, кроме того, через элемент ИЛИ 76 (155ЛА.4) и мультивибратор 93 (155АГЗ), служащий для формирования импульса, используются для обнуления счетчика 99. Сигнал управления дешифратором 97 поступает с выхода элемента И 62 при единичном потенциале на его втором входе. Первый и второй выходы коммутатора 100 соединены соответственно с управляющими входами регистров начального 24 и конечного 25 адресов (т0е,, подключены к входам разрешения параллельной загрузки микросхем (155ИР4)), представляющих каждый три 4-разрядные секции, с целью выбора корпуса микросхемы таким образом, чтобы при первом нажатии одной из клавиш 45-60 Код загрузки происходит запись четырех старших разрядов адреса начальной микрокоманды, при втором - четырех средних разрядов, при третьем четырех младших разрядов, При дальнейшем нажатии кнопок 45-60 цикл записи повторяется. Аналогично происходит формирование адреса конечной микрокоманды в регистре 25 конечного адреса, с той лишь разницей, что при нажатии кнопки 34 Кон.а импульсы разрешения параллельной записи подаются с коммутатора 100 на управляющий вход регистра 25 конечного адреса. Кроме того, сигнал с.кнопки 33 Начса поступает через элемент И 65 н элемент ИЛИ 79 на

5

тпиггер 90, устанавливая на его инверсном выходе единичный уровень, который подключает к шине 2 выход регистра 24 начального адреса через шинный формироватрль и отключает (п входе ОЕ) выход БФА 5 от шины 2. Ко с регистра 25 конечного адреса по 12 разрядной шине поступает на блок 26 сравнения, вторым входом которог является 12-разрядная шина 2, При совпадении адреса конечной микрокоманды с текущим адресом на шине 2 на выходе блока 26 сравнения (две схемы J55JIA2) появляется сигнал, ко торый в зависимости от состояния триггера 91 поступает либо через элемент И 66 и элемент ИЛИ 78 на вход сброса триггера 89, либо через элемент И 67 и элемент ИЛИ 79 на вход сброса триггера 90. Триггер 89 формирует сигнал останова тактового генератора 9 МПС, подавая его через элемент ИЛИ 830 В устройстве предусмотрена и чагрузка микрокоманды отлаживаемой программы в блок 23 с последующей перезаписью отлаженой программы в ПЗУ 6 микрокоманд МПС. Для этого на пульте 29 управле

ния нажимается кнопка 35 Р.омк, что 30 входы CS (второй управляющий вход блозначит выбор регистра.21 в качестве приемника кода загрузки с выхода блока 12 управления. В реализуемом варианте устройства микрокоманда имеет 64 двоичных разряда, т.е. 16 шестнадцатиричных символов о При нажатии кнопки 35 Р.омк .1 запираются элементы И 62 и 63 и открывается элемент И 61 для прохождения импульса с шифратора 88 кода зягрузки на счетный вход счетчика 95 символов и через элемент 96 задержки на управляющий вход дешифратора 98. 4-разрядный счетчик 95 символов (155ИЕ5) подсчитывает число нажатий кнопок 45-60 загрузки (от 1 до 16), дешифратор 98 4-разрядный код счетчика символов преобразует в напряжение на одном из разрядов 16-разрядной выходной шины для управления (по входам „ ВР2) секциям регистра 21, выполненного на микросхемах К589ИР12/4/. Обнуление счетчика 95 символов осуществляется принудительно от кнопки 39 О перед начялом набора очередной микрокоманды,, Выдача на шину 3 выполняемой микрокоманды, записанной в регистре отладочной микрокоманды, может осуществляться либо из самого

ка 23).

Для перехода в режим отладки необходимо нажать кнопку 31 Отладка на пульте 29 управления. В этом слу- ог чае деблокируются кнопки 40-44 Подрежим отладки, частично блокируемый

на наборе элементов И 71-75 сигналом с выхода элемента И 82, и блоки-, руются кнопки 33-37 Выбор абонента. 4Q При нажатии кнопки 40 Р.мк сигнал единичного уровня с ее выхода через элементы И 70 и 74 разрешает поступт ление тактового импульса на регистр 7 микрокоманд МПС. В пошаговом подрежиме нажимается кнопка 41 Шаг, и сигнал кнопки 41 через элемент И 72 подается на вход cosC-cosD тактового генератора 9 (КМ1804ГГ1), стимулируя генерацию одного тактового импульса. Таким образом, после режима зягрузки по первому нажатию кнопки 41 Шаг в режиме отладки МПС возъ- мет адрес не из блока 5, а из регистра 24 начального адреса Затем под воздействием тактового импульса триггер 90 переходит в состояние, которое подключает к шине 4 опять блок 5 вместо регистра 24 начального адрег са, и следующие шаги пойдут по про;

55

10

0

$

0

5

регистра, либо из блока 23 памяти, В первом случае нажимается кнопка 36 ПЗУ МК, и сигнал г. нее через элемент ИЛИ 81 подсоединяет выход шинного формирователя 22 (155ЛПН) к шине 3 и отключает (по входу ОЕ) выход ПЗУ 6 от шины 3. Во втором случае нажимается кнопка 37 РПЗУ, сигнал которой через элемент И 68 отключает регистр 21 от шинного формирователя 22, а подключает к нему выход блока 23. Блок 23 может быть выполнен на БИС К573РФ5, сигналы управления записью и считыванием которых (входы CS и СЕО) формируются на элементе И 64, инверторе 85, элементе ИЛИ 77„ При нажатии кнопки 35 Р.омк можно осуществить программирование блока 23, т.е. выполнить запись в него отлаженной микрокоманды из регистра 21. Для этого нужно нажать КНОПКУ 38 ПР с двумя парами контактов (П2К) При этом на опин выход кнопки выдается напряжение программирования +25 В вместо +5 В, а по другому выходу с помощью мультивибратора 94 (155АГЗ) сформируется импульс программирования 50 мс на

ка 23).

Для перехода в режим отладки необходимо нажать кнопку 31 Отладка на пульте 29 управления. В этом слу- г чае деблокируются кнопки 40-44 Подрежим отладки, частично блокируемый

на наборе элементов И 71-75 сигналом с выхода элемента И 82, и блоки-, руются кнопки 33-37 Выбор абонента. Q При нажатии кнопки 40 Р.мк сигнал единичного уровня с ее выхода через элементы И 70 и 74 разрешает поступт ление тактового импульса на регистр 7 микрокоманд МПС. В пошаговом подрежиме нажимается кнопка 41 Шаг, и сигнал кнопки 41 через элемент И 72 подается на вход cosC-cosD тактового генератора 9 (КМ1804ГГ1), стимулируя генерацию одного тактового импульса. Таким образом, после режима зягрузки по первому нажатию кнопки 41 Шаг в режиме отладки МПС возъ- мет адрес не из блока 5, а из регистра 24 начального адреса Затем под воздействием тактового импульса триггер 90 переходит в состояние, которое подключает к шине 4 опять блок 5 вместо регистра 24 начального адрег са, и следующие шаги пойдут по про;

5

11164

грамме, В подрежиме Отрезок сигнал от кнопки 42 через элементы И 73 и ИЛИ 79 устанавливает триггер 90 в состояние, подсоединяющее регистр 24 начального адреса к шине 2. Кроме того, сигнал от кнопки 42 через элемент ИЛИ 80 переводит триггер 89 в состояние, запускающее тактовый генератор 9 МПС по входу HLT-S1T. В первом такте МПС выполняет., микрокоманду начального адреса а татем триггер 90 по следующему тактовому импульсу возвращается в состояние , которое отключает от шины 2 регистр 24 начального адреса, а подключает блок 5. Далее МПС будет выполнять программу до адреса конечной микрокоманды, т.е„ до появления сигнала на выходе блока 26 сравнения, который переводит триггер 89 в состояние, запрещающее работу тактового генератора 9. В подрежиме Цикл работа устройства отличается от работы в подрежиме Отрезок только тем, что при нажатии кнопки 43 Цикл перебрасывается триггер 94 в состояние, при котором сигнал с блока 26 сравнения проходит не на триггер 89 а на триггер 90, подключая к шине 2 ре- гястр 24 начального адреса. Для того, чтобы вывести МПС из циклического режима, необходимо нажать кнопку 44 Останов, сигнал которой через элементы И 75 и ИЛИ 78 сбрасывает тряг- геры 89 и 91 в исходное состояние подрежима Отрезок. В режиме отладки программы устройство позволяет вместо (штатного ПЗУ 6 (например,KP556PT5J ис

8

12

товой МК (К589ИР12), управляемый выходным сигналом элемента И 69 в блоке I2 управления, отключен от шины 3„ Информация по шинам 1-3 поступает в параллельный интерфейс 17, который представляет собой набор из мультиплексоров входных шин, осуществляющих выбор требуемой шины и полубайтовую передачу шинной информации на блок 20 индикации. Если шина 1 является 16-разрядной, шина 2-12- разрядной, шина 3 - 128-разрядной, то параллельный интерфейс 17 будет содержать четыре мультиплексора: 16 на 4,12 на 4 и два 64 на 4, которые могут быть реализованы на двадцати К531КП41. Выбор соответствующего мультиплексора в параллельном интерфейсе 17 производится по сигналу блока 19 захвата шин. Управление работой отдельных мультиплексоров осуществляется 4-7 разрядами строчного счетчика 114 йюка 20 индикации по адресным входам мультиплексоров. Блок 19 захвата шин, представляющий собой демультиплексор (например, К531ИД7), управляется восьмым разрядом строчного счетчика 114 -блока 20 индикации с адресацией от трех младших разрядов с выхода датчика 18 тестовой МП. Выходы всех мультиплексоров параллельного интерфейса 17 объединены в одну выходную четыре разпядную шину, информация по которо поступает на ПЗУ J09 знаков блока 20 индикации Рассмотрим более подробно работу блока 20 индикации, вариант реализации которого представлен на

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки специализированных микроЭВМ | 1990 |

|

SU1741135A1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ОТЛАДОЧНОЕ УСТРОЙСТВО ДЛЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2016 |

|

RU2634197C1 |

| Устройство для отладки многопроцессорных систем | 1988 |

|

SU1644145A1 |

| Устройство для контроля устройства микропрограммного управления | 1988 |

|

SU1608674A1 |

| Устройство для отладки многомодульной ЦВМ | 1987 |

|

SU1564630A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1247877A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1587514A1 |

| Устройство для отладки микроЭВМ | 1989 |

|

SU1677708A1 |

| Устройство для обмена информацией междуэлЕКТРОННОй ВычиСлиТЕльНОй МАшиНОй(эВМ) и уСТРОйСТВАМи ВВОдА и ВыВОдА | 1979 |

|

SU809140A1 |

| Устройство для отладки программ | 1988 |

|

SU1608673A1 |

Изобретение позволяет повысить эффективность и полноту отладки и контроля микропроцессорных систем (МПС) различного назначения, используя гибкую организацию отображения контролируемых данных, мультиплексирования шин и выбора источника информации. Цель изобретения - повышение эффективности и полноты отладки конт- роля - достигается за счет введения режима нрраэрушающего контроля состояния внутренних элементов МПС и произвольного манипулирования участками отлаживаемой программы. Устройство для отладки и контволя МПС включает шины данных, адреса и управления, параллельный интерфейс, блок памяти тестов, дешифратор, регистр тестовой микрокоманды, блок захвата шин, шинный формирователь, регистр отладочной микрокоманды, блок сравнения, регистры начального и конечного адресов, блок индикации и формирования адресов тестовой последовательности, блок управления и загруз- i ки, репрограммируемый блок постоянной памяти. 10 ил. (Л

пользовать блок 23 либо внешний эмулятор/до фиг.4. Задяча блока 20 индикации

(ОЗУ микроэвм) через сокеты блока 23, а после отладки программы осущест-, вить перезапись программы в ПЗУ 6, микрокоманд МПС. В режимах Загруэ- ка и Отладка контроль шин МПС осуществляется на ВКУ 112 блока 20 индикации, работа которого будет объяснена при описании функционирования устройства в режиме Контроль.

Наличие в блоке 12 управления различ- JQ присвоенных элементам матрицы ных сочетаний элементов И, ИЛИ, инверторов с сигналами кнопок пульта 29 управления является мерой исключения взаимного влияния режимов и подрежимов работы устройства друг на « друга Прежде, чем перейти к режиму Контроль, рассмотрим работу блока 20 индикации при отжатой кнопке 32 Контроль. При этом регистр 28 тестезированным в ней символом. Э ды - образы хранятся в ПЗУ 409 (556РТ5), Выбор того или кного осуществляется путем подачи на J09 знаков адреса, по которому сан код требуемого символа. С ПЗУ 109 знаков на вход первого типлексора JIO поступают 8-раз коды символов на знакостроках

преобразовать поступающий на него двоичный код в сигнал подсвета луча электронно-лучевой трубки блока 412. Все возможные знаки и символы сфор- мировайы из элементов знакогенерярую- щей матрицы 8x8 (6). Образ символа, таким образом, представляет собой 64-разрядный код, полученный при последовательном считывания значений,

присвоенных элементам матрицы

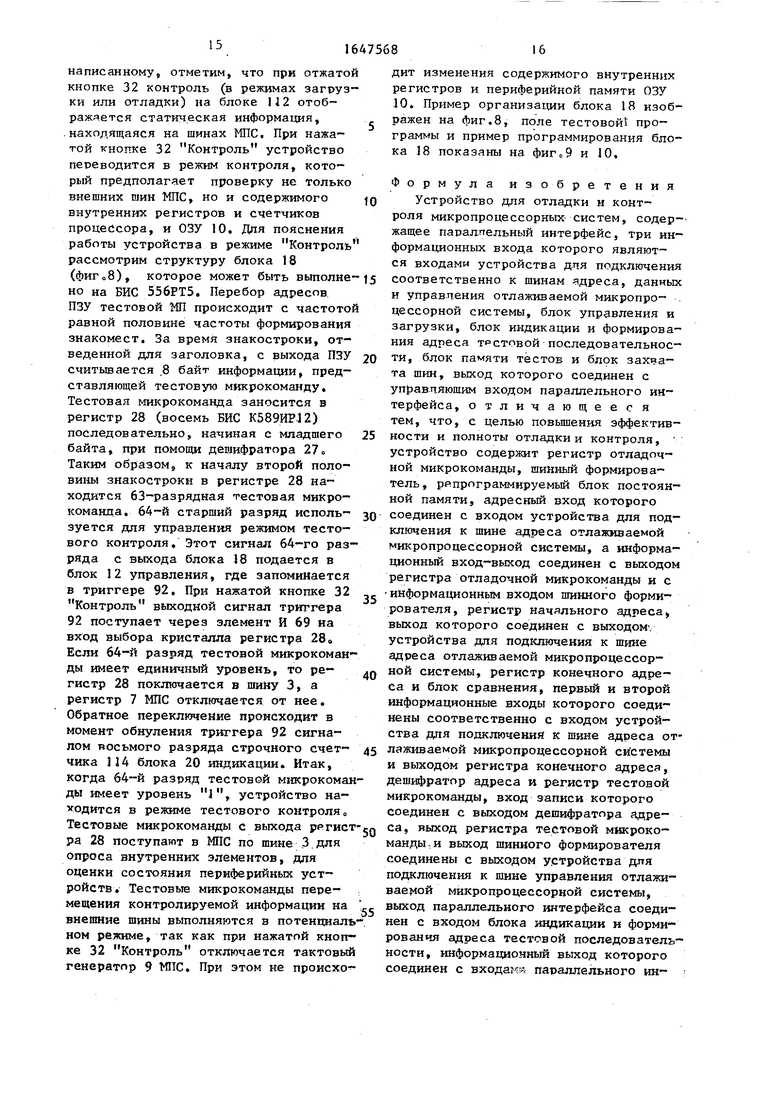

с синтезированным в ней символом. Эти коды - образы хранятся в ПЗУ 409 знако (556РТ5), Выбор того или кного знака осуществляется путем подачи на ПЯУ J09 знаков адреса, по которому записан код требуемого символа. С выхода ПЗУ 109 знаков на вход первого мультиплексора JIO поступают 8-разрядные коды символов на знакостроках. Первый мультиплексор 116 (К555КП7) преобразует их в последовательность импульсов разрядов кода образов, ко- торые чередуются синхронно с разверткой ВКУ 112, В формирователе 111 видеосигнала, представляющем собой стандартный смеситель, эти импульсы смешиваются с синхросмесью, поступающей с формирователя 1J6 синхросмеси, для получения полного телевизионного видеосигнала. Полный видеосигнал заводится на дисплей 112 для отображения выбранных символов (путем подсвета тпчек экрана), зафиксированных в знакосинтезирующей матрице. Отображение знаковой информации ня экране блока I I 2 осуществляется в виде телетаблнцы, примерный1 формат которой представпен на фиг„6. Телетаблица 20 ствляется тоже восьмым разрядом

моткет иметь различные заголовки, различные форматы представления цифрового поля в каждой строке в зависимости от конкретных требований. Для заголовков могут быть использованы буквы ла- 25 за синхронизацию и управпение его ра

тинского и русского алфавитов, цифры и знаки. Телетаблица может иметь 16 знакострок. Максимальный формат каждой строки составляет 32 знакоместа. Первые 16 отводятся под номер энакостроки и 12 символов заголовка. Остальные I6 знакомест используются для отображения данных, которые представляются в шестнадцатиричной системе счета. Подача адресов символов для опроса ПЗУ 109 знаков производится с параллельного интерфейса . 17 или С ПЗУ П7 заголовков о Для кодирования всех требуемых символов достаточно шестиразрядного кода адреса ПЗУ 109 знаков. Четыре младших разряда формируются либо мультиплексорами параллелного интерфейса 17, либо ПЗУ 117 заголовков Седьмой разряд ПЗУ 317 заголовков используется в качестве сигнала подсяета знакоместа телетаблицы. Кодирование этого разряда позволяет получать необходимый формат представления данных в двоичном и шестнадцатиричном кодах, а формировать пробелы в заголовках.- Коды адресов символов поступают из ПЗУ 117 заголовков во время первых 16 знакомест телетаблицы (фиг.7). На первом знакоместе записан номер знакостроки в виде шестизначного кода, в седьмом разряде записана -1, что обеспечивает подсвет данного знакоместа. На втором знакоместе формируется

пробел путем записи О в седьмой разряд Следующие J2 знакомест используются для записи заголовка, для чего применяется 6-разрядный код, а в седьмой записывается 1, если на данном знакоместе необходимо наличие символа и О, если надо сформировать пробел о При формирования пробела заполнение шести младших разрядов осуществляется произвольно Для разделения выходных кодов ПЗУ 111 заголовков на четыре младших и два старших разряда перед подачей их на

ПЗУ 109 знаков используются шинный формирователь И 9 (155ЛП1 - 4 младших разряда) и второй мультиплексор (555КП11 - 2 старших разряда) 118. Управление указанными блоками осуще-

строчного счетчика 114 в противофазном режиме, что означает их коммутацию после половины знакостроки. Ряд блоков в блоке 20 индикации отвечает

ботойо К ним относятся задающий генератор ИЗ, строчный Л4 н кадровый 115 счетчики, формирователь 416 синхросмеси. Задяющий генератор ИЗ

представляет собой кварцевый генератор 8 частоты МГц„ Его выходной сигнал поступает на 9-разрядный строчный счетчик 114 (три корпуса 155ИН5), импульс переноса последнего разряда

которого служит счетным импульсом кадрового счетчика 315 и подается на формирователь 116 синхросмеси в качестве строчного синхроимпульса. Кадровый счетчик 315 аналогичен строчному И 4, а его выходной импульс подается на формирователь 116 синхросмеси в качестве кадрового синхроимпульса, Формирователь 116 синхросмеси с помощью мультивибраторов формирует сннхроимпульсы необходимой длительности для запуска развертки-блока 112, смешивает их на элементе ИЛИ, формирует из них импульсы обнуления строчного П4 и кадрового И5 счетчиког отрицательной полярности. В выходную шину блока 20 индикации входят выходы 4-7 разрядов строчного счетчика И4, 5-8 разрядов кадрового счетчика 115, сигналы по которым поступают на адресный вход датчика 18 тестовой МП. Причем выходы 4-7 разрядов строчного счетчика 114 из адресной шины подаются на входную шину дешифратора 27„ Таким образом, возвращаясь к ранее

написанному, отметим, что при отжатой кнопке 32 контроль (в режимах загрузки или отладки) на блоке 112 отоб- ражяется статическая информация, находящаяся на шинах МПС, При нажатой кнопке 32 Контроль устройство переводится в режим контроля, который предполагает проверку не только внешних шин МПС, но и содержимого внутренних регистров и счетчиков процессора, и ОЗУ 10, Для пояснения работы устройства в режиме Контроль рассмотрим структуру блока 18 (фигов), которое может быть выполне но на БИС 556РТ5. Перебор адресов ПЗУ тестовой МП происходит с частотой равной половине частоты формирования знакомест. За время знакостроки, отведенной для заголовка, с выхода ПЗУ считывается 8 байт информации, представляющей тестовую микрокоманду. Тестовая микрокоманда заносится в регистр 28 (восемь БИС К589ИР42) последовательно, начиная с младшего байта, при помощи дешифратора 27 Таким образом9 к началу второй половины знакостроки в регистре 28 находится 63-разрядная тестовая микрокоманда. 64-и старший разряд исполь- зуется для управления режимом тестового контроля. Этот сигнал 64-го разряда с выхода блока J8 подается в блок 12 управления, где запоминается в триггере 92. При нажатой кнопке 32 Контроль выходной сигнал триггера 92 поступает через элемент И 69 на вход выбора кристалла регистра 28 Если 64-й разряд тестовой микрокоманды имеет единичный уровень, то ре- гистр 28 исключается в шину 3, а регистр 7 МПС отключается от нее. Обратное переключение происходит в момент обнуления триггера 92 сигналом иосьмого разряда строчного счет- чика 314 блока 20 индикации. Итак, когда 64-й разряд тестовой микрокоманды имеет уровень 1, устройство находится в режиме тестового контроля„ Тестовые микрокоманды с выхода рягист ра 28 поступают в МПС по шине 3 для опроса внутренних элементов, для оценки состояния периферийных устройств. Тестовые микрокоманды перемещения контролируемой информации на внешние шины выполняются в потенциальном режиме, так как при нажатой кнопке 32 Контроль отключается тактовый генератор 9 МПС. При этом не происхо

Q Q 5 д

5

дит изменения содержимого внутренних регистров и периферийной памяти ОЗУ 10. Пример организации блока 18 изображен на фиг.8, поле тестовой программы и пример программирования блока 18 показаны на фиг„9 и 10,

Формула изобретения

Устройство для отладки и контроля микропроцессорных систем, содержащее параллельный интерфейс, три информационных входа которого являются входами устройства дня подключения соответственно к шинам ядреса, данных и управления отлаживаемой микропроцессорной системы, блок управления и загрузки, блок индикации и формирования адреса тестовой последовательности, блок памяти тестов и блок захвата шин, выход которого соединен с управляющим входом параллельного интерфейса, отличающееся тем, что, с целью повышения эффективности и полноты отладки и контроля, устройство содержит регистр отладочной микрокоманды, шинный формирователь, ррпрограммируемый блок постоянной памяти, адресный вход которого соединен с входом устройства для подключения к шине адреса отлаживаемой микропроцессорной системы, а информационный вход-выход соединен с выходом регистра отладочной микрокоманды и с информационным входом шинного формирователя, регистр начального адреса выход которого соединен с выходом устройства для подключения к шине адреса отлаживаемой микропроцессорной системы, регистр конечного адреса и блок сравнения, первый и второй информационные входы которого соединены соответственно с входом устройства для подключений к шине адреса отлаживаемой микропроцессорной системы и выходом регистра конечного адреса, дешифратор адреса к регистр тестовой микрокоманды, вход записи которого соединен с выходом дешифратора адреса, выход регистра тестовой микрокоманды -и выход шинного формирователя соединены с выходом устройства для подключения к шине управления отлаживаемой микропроцессорной системы, выход параллельного интерфейса соединен с входом блока индикации и формирования адреса тестовой последовательности, информационный выход которого соединен с входаг-я параллельного интерфейса, дешифратора адреса и входом адреса блока памяти тестов, группа выходов которого соединена с информационными входами регистра тестовой микрокоманды и блока захвата шин, управляющий выход блока индикации и формирования адреса тестовой последов ат льности соединен с входами синхронизации блока памяти тестов, блока захвата шин и первым входом синхронизации блока управления и загрузки, установочный вход которого соединен с отдельным выходом блока памяти тестов, выход загрузки информации. блока управления и загрузки соединен с информационными входами регистров отладочной микрокоманды, конечного адреса и начального адреса, первая, вторая и третья группы выходов блока управления и загрузки соединены с входами записи соответственно регистра конечного адреса, регистра начальЖ

I У Р ПТ/5 f°

L.

таш

9 -э

13

ного адреса и регистра отладочной микрокоманды, с первого по седьмой выходы блока управления и загрузки соединены соответственно с входами синхронизации регистра начального адреса, регистра отладочной микрокоманды, входами записи, чтения и программирования репрограммируемого блока постоянной памяти и управляющими входами шинного формирователя н регистра тестовой микрокоманды, первый н шестой выходы и четвертая группа выходов блока управления и загрузки образуют группу выходов устройства для подключения к группе управляю- .щих входов отлаживаемой микропроцессорной системы, второй вход синхронизации блока управления и загрузки является тактовым входом устройства, выход блока сравнения соединен с раз- решающим входом блока управления и загрузки.

мпс

5ФА

Регистр А (Си Счетчик т

С/лех

цдру

Ј

Ј

1Г

в

J-J

-N

$

о

14

I

«s

оЖ1

39 I 38 I

- | |

I Код загрузки

W

Подрежим отладки

WW Ы№ 50 5ПЩК 5ЩВЯ5б 57 5В 59 ер

.. f г(

4rs6/x.:

Вш.1 .ЭУ

0Вх.З °3ьгх.2

оВшх.Зу

Вб/х. Ту

W

Подрежим отладки

У

Sc

Вь/хЛ Вых.5

109

1

0

110 Т

ш

JjF

/f7

E

т

el f

Awr. awr./

§

1

111

т

т

т

з;

i l

//5

Ј

/f5

$tn.b

Д

1

Подсвею

yo/ /////////// W / /4

////) ///У

н

ш

и

л

н

Фиг. 6

/tf / /////////Jtfxrt/

////// W / /

////) ///У

л

ю

ML

м

к

W

ФигЛ

«к

/ /// /// g // /// /// / /

У 7/ /// /// 0 // /// ///

/ //У /// /// /// /// / /

/ //А/// /// //У /// /// //У А/ / / U QV /// /// ////// / /

-v

g.XQg.

/(од номера

ОЗУ

t

If од номера Тест РЗУрежим

УУ

ОЗУ/РЗУ лодсвы

,// / / / ° f/ О /У Г// f// Т / У / 7 / Л / ИГУ

// /// g // /// /// / /

/ /// 0 // /// ///

/// /// / /

//У /// /// //У А/ // ////// / /

g.XQg.

/ ./ / / / / //

/ / / / / //

/ / / / / 7/

и

Номер признано

//опер шины

01

J г з

Знако строки

UT

О С

0U8.8

Фиг. Ю

Редактор В.Бугреккова

Составитель Д.Ванюхин

Техред М. Дидык Корректор Ji,Эрдейн

Закаэ 140J

Тираж 423

ВШИЛИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, , Раушская наб., д. 4/5

Подписное

| Устройство для визуального контроля исполнения программ | 1985 |

|

SU1304028A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для отладки микропроцессорных систем | 1985 |

|

SU1285482A1 |

Авторы

Даты

1991-05-07—Публикация

1988-07-12—Подача