I1

Изобретение относится к измерительной технике, а именно к цифровь м устройствам для измерения интеграль- ных характеристик детерминированных и случайных сигналов, и может быть использовано в технике связи, в производстве и испытаниях различных радиоэлектронных приборов и систем, а также в процессе научных исследований.

Цель изобретения - расширение области применения путем увеличения частотного диапазона измеряемого сигнала при одновременном обеспечении надежности результата цреобразования .

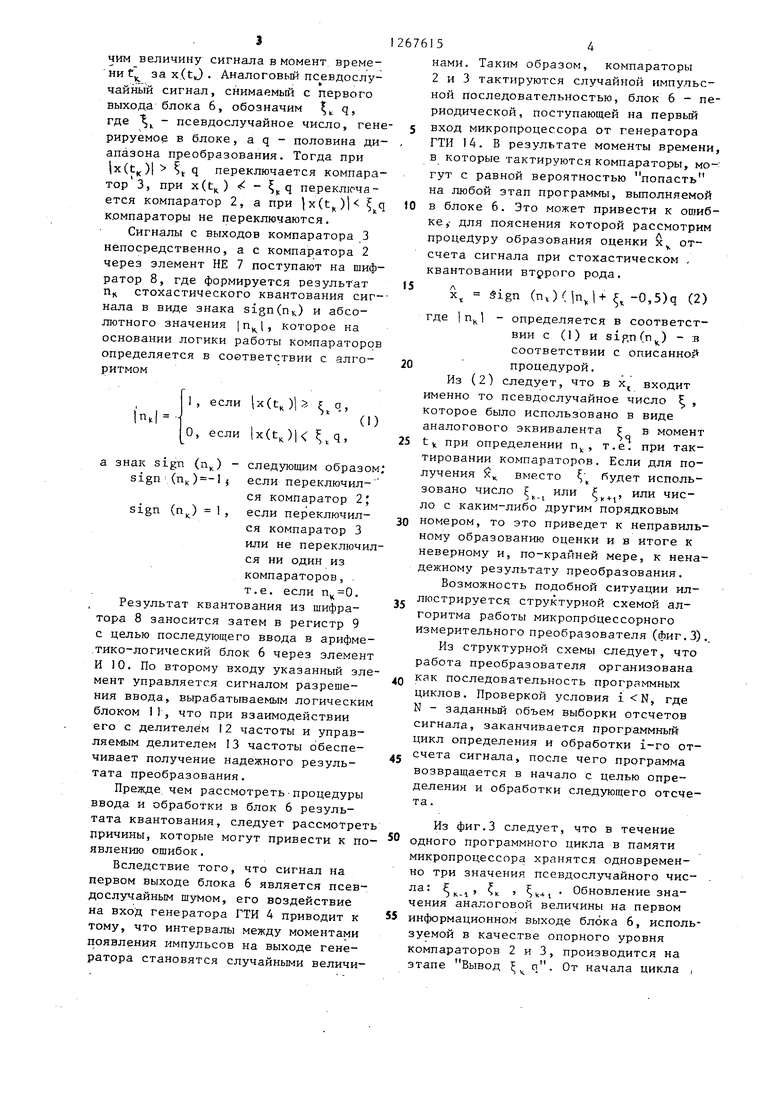

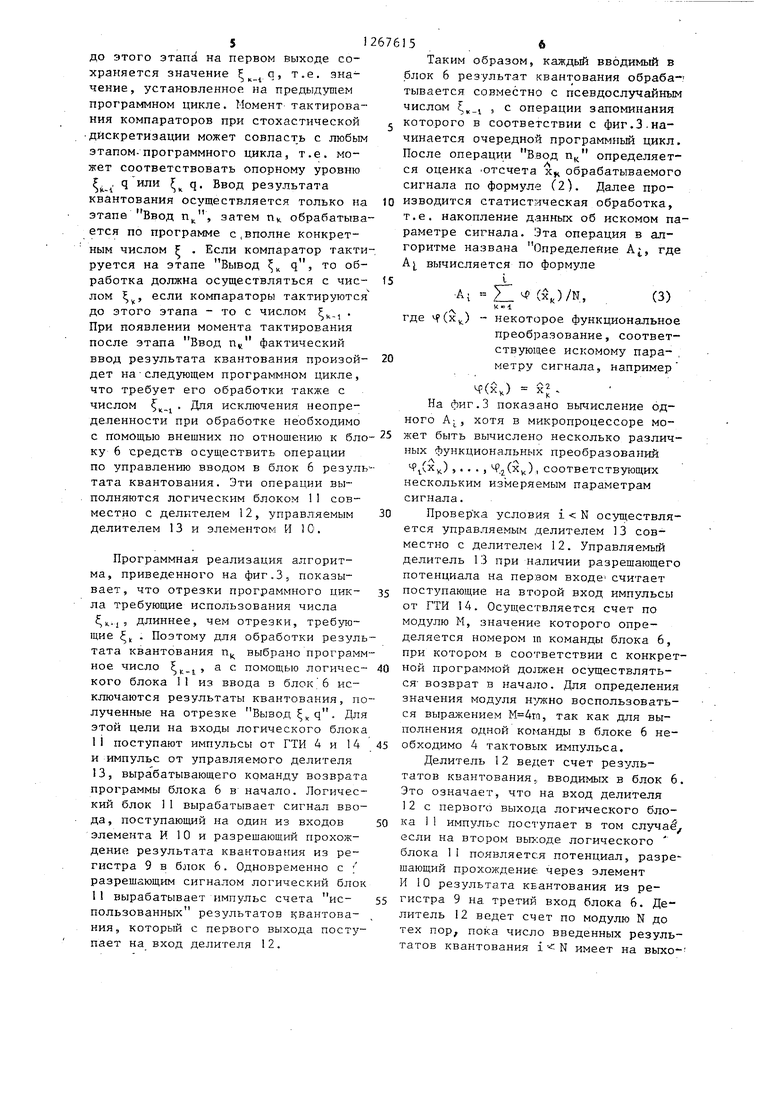

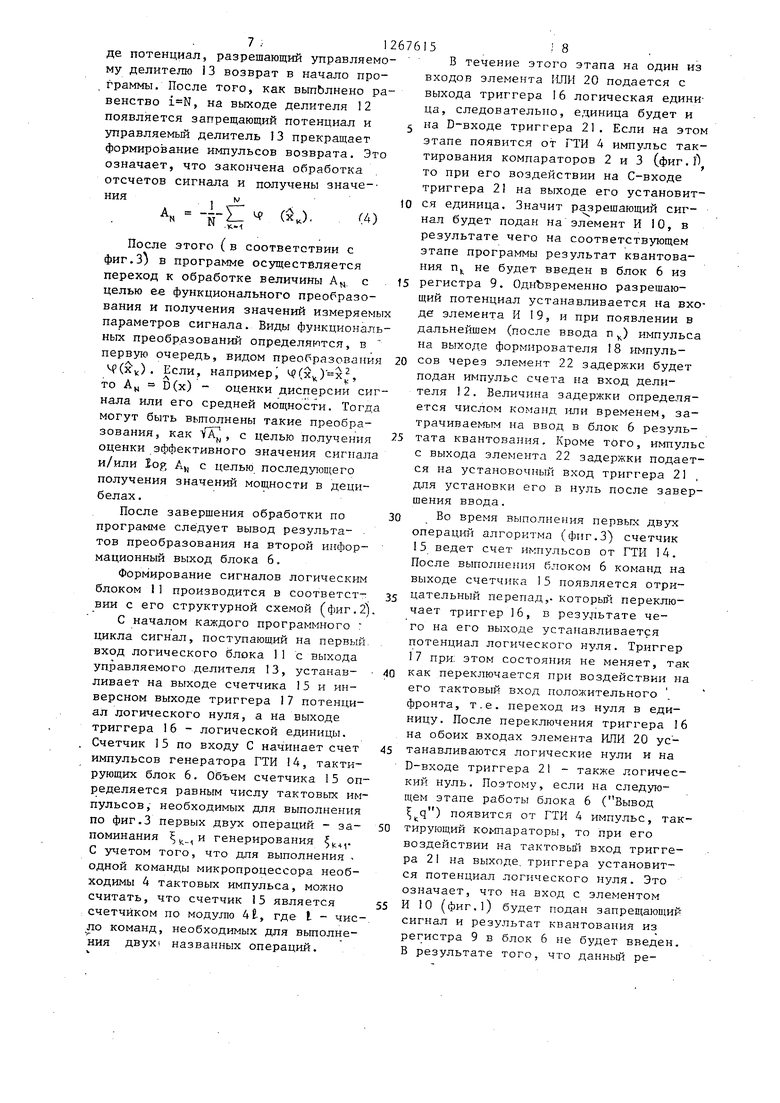

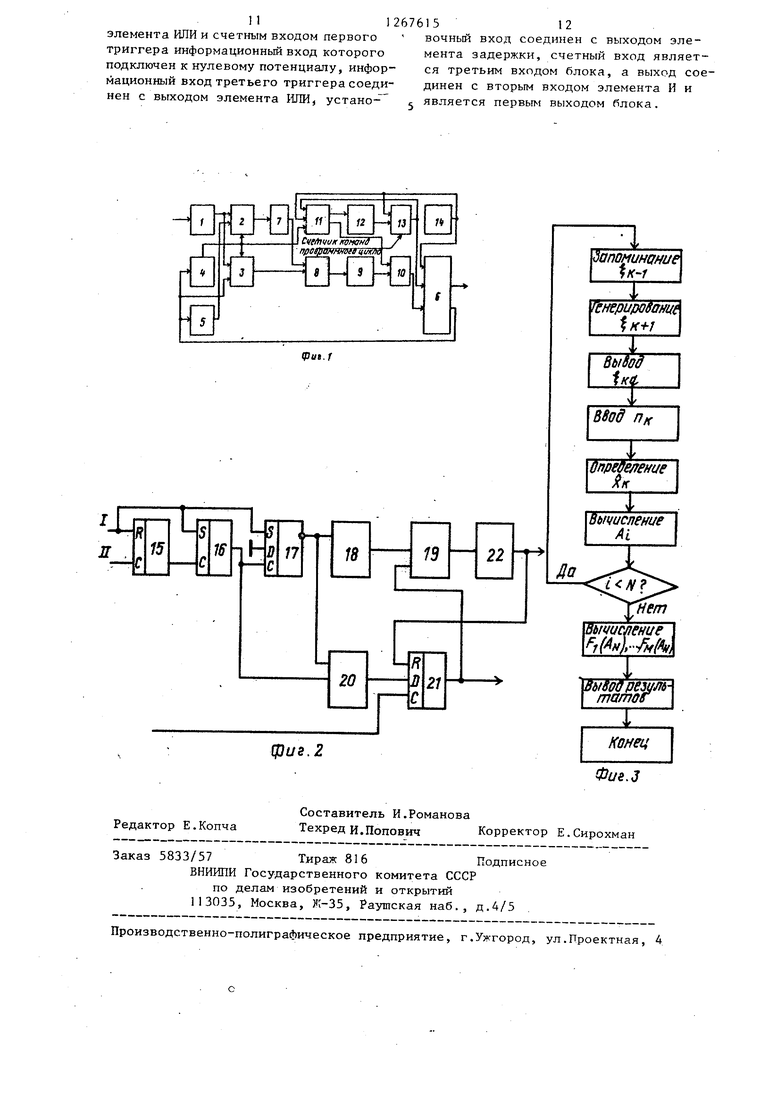

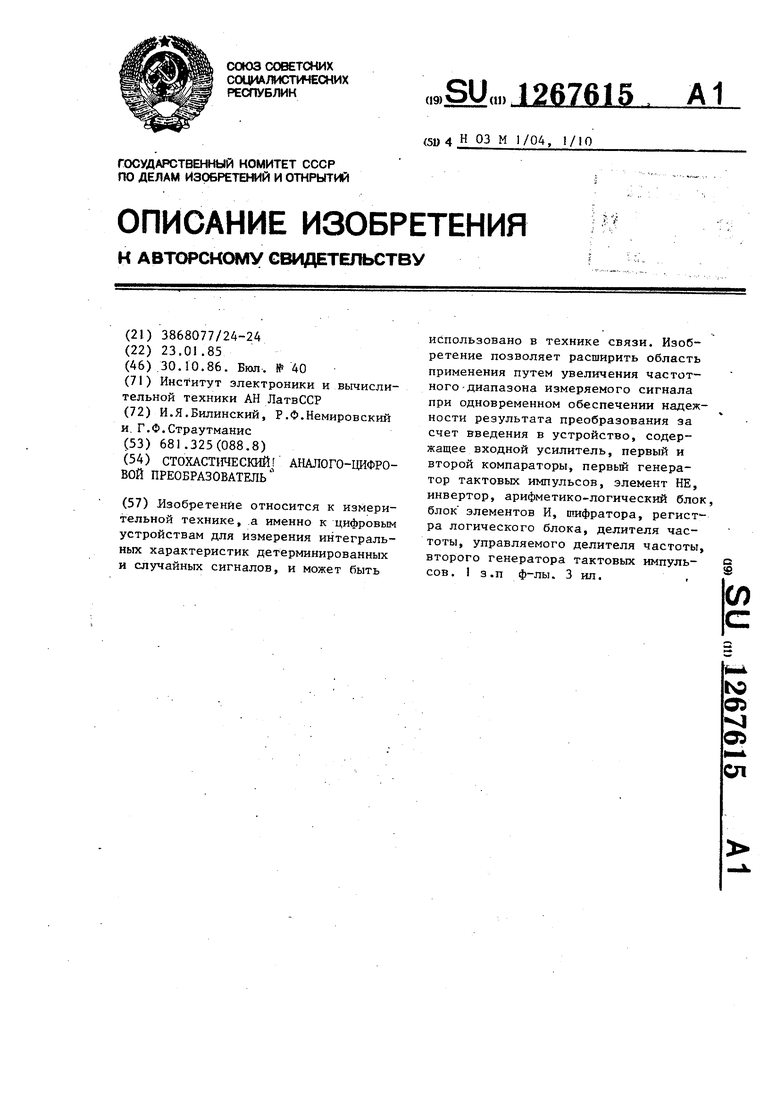

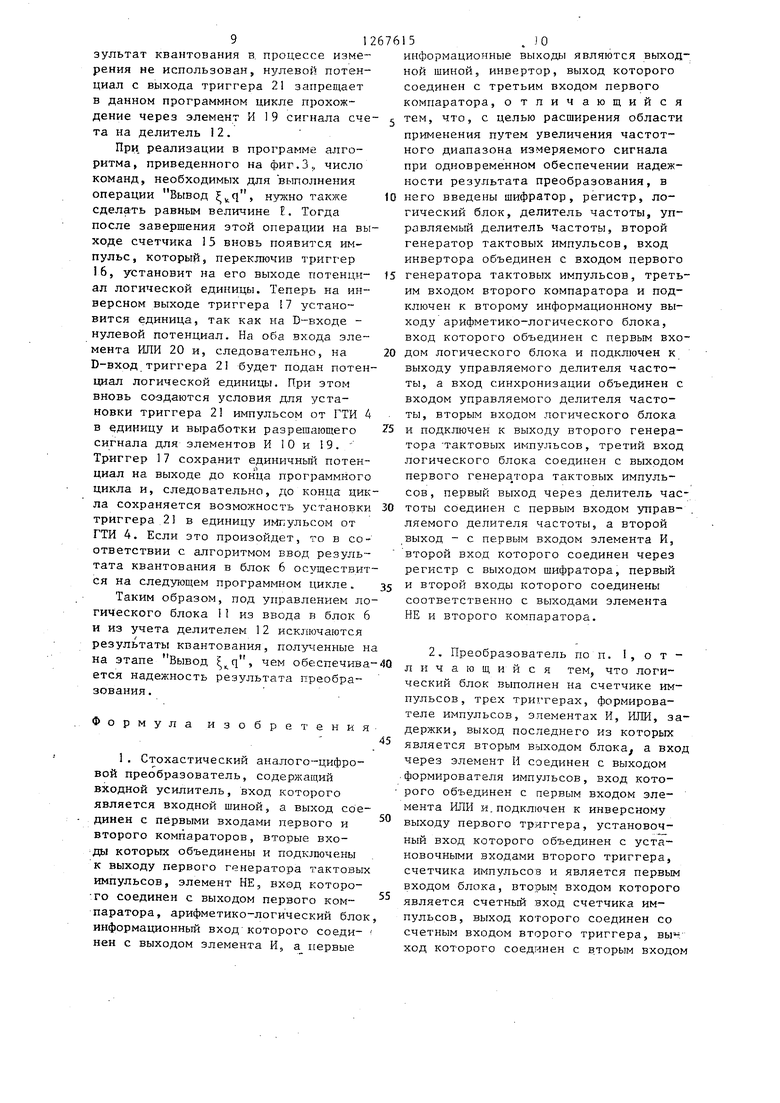

На фиг.1 изображена структурная схема стохастического анзлого-цифрового преобразователя; на фиг.2 структурная схема логического блока; на фиг.З - блок-схема алгоритма работы стохастического аналого-цифрового преобразователя.

Устройство содержит входной усилитель 15 первый 2 и второй 3 компараторЫ; первьп- генератор 4 тактовых импульсов, инвертор 5, арифметикологический блок 6, элемент НЕ 7, шифратор 8„ регистр 9, элемент И 10, логический блок 11, делитель i 2 частоты, управляемый делитель 13 частоты, второй генератор 14 тактозьк импульсов .

Стохастическое квантование в предлагаемом измерителе осуществляется путем сравнения входного сигнала с опорным сигналом, в качестве которого используется аналоговый псевдослучайный сигнал,, формируемый блоком 6. В то л;е время с помощью этого псевдослучайного сигнала осуществляется и управление генератором тактовых импульс.ов (ГТИ) 4 , В результате ГТИ 4 формирует импульс) в случайные моменты времени, что обеспечивает стох астическую дискретизацию, т.е. обеспечивается получение результатов квантования в указанные случайные моменты времени. Ввиду того, что арифметико-логический блок 6 тактируется периодической последовательностью от ГТИ 14, а результаты квантования получены в случайные моменты времени, в устройстве предусмотрены технические средства для синхяронизации процедур получения результатов квантования и их обработки в арифметико-логическом блозсе 6.

152

OcHOBFMMH задачами логического блока 11 являются выработка сигналов упргавления элементом И 10, через которьш осуществляется ввод результа тов квантования из регистра 9 в арифметико-логический блок 6, и формирование импульсов счета введенных результатов . Импульсы счета используются в качестве входной информации делителя 12 частоты. В связи с тем, что арифметико-логический блок 6 тактируется периодической последовательностью (от ГТИ )4), а компараторы 2 и 3 - случайной, импульсы обоих генераторов являются основной входной информацией, на основании которой вырабатываются выходные сигналы логического блока П. Логический блок 11 содержит счетчик 15 импульсов, триггеры 16 и 17, формирователь 18 импульсов, элемент И 19, элемент ИЛИ 20, триггер 21, элемент 22 задержки.

Основной функцией ГТИ 4 является генерирование последовательности импульсов со случайными интервалами между моментами .лх появления. Эта функция осуществляется за счет управления работой генератора от источника аналогового псевдослучайного сигнала. В качестве такого источника используется ари(| кетико-логический блок 6, с выхода которого псевдослучайный сигнал поступает на вход генератора.

Устройство работает следующим образом,

Обрабатываемьц сигнал через входной усилитель 1, в котором он приводится к требуемому масштабу измерения , поступает H,J первые входы компараторов 2 и 3. На вторые входы компараторов подается сигнал от ГТИ 4. На третьи входы компараторов поступает аналоговьй псевдослучайный опорный сигнал с первого выхода арифметико-логического блока 6, причем на третий вход компаратора 3 поступают положительные значения, а на третий вход компаратора 2 - отрицательные после инверсии, выполняемой в инверторе 5. В моменты времени определяемые ГТИ 4, происходит сравнение сигнала и опсфиого напряжения. В зависимости от полярности сигнала и соотношений ,цу сигналом и опорньм напряжением может переключиться компаратор 2 или ко: таратор 3, Обозна31

чим величину сигнала в момент времени t за x(t j . Аналоговый пс евдослучайньш сигнал, снимаемый с первого выхода блока 6, обозначим q, где - псевдослучайное число, генерируемое в блоке, а q - половина диапазона преобразования. Тогда при |x(t)| j q переключается компаратор3, при x(tn) q переключается компаратор 2, а при |x(t)| q компараторы не переключаются.

Сигналы с выходов компаратора 3 непосредственно, а с компаратора 2 через элемент НЕ 7 поступают на шифратор 8, где формируется результат

стохастического квантования сиг-п. нала в виде знака sign(n) и абсолютного значения , которое на основании логики работы компараторо определяется в соответствии с алгоритмом1 , если lx(t )1 . q, О, если x(t,)l q. а знак sign (п) - следующим образо sign(пк)-1J если переключился компаратор 2; sign (п) 1, если переключился компаратор 3 или не переключи ся ни один из компараторов, , т.е. если . Результат квантования из шифратора 8 заносится затем в регистр 9 с целью последующего ввода в арифме ,тико-логический блок 6 через элемен И 10. По второму входу указанный эл мент управляется сигналом разрешения ввода, вырабатываемым логически блоком 11, что при взаимодействии его с делителем 12 частоты и управляемым делителем I3 частоты обеспечивает получение надежного результата преобразования. Прежде чем рассмотреть-процедуры ввода и обработки в блок 6 результата квантования, следует рассмотре причины, которые могут привести к п явлению ошибок. Вследствие того, что сигнал на первом выходе блока 6 является псев дослучайным шумом, его воздействие на вход генератора ГТИ 4 приводит к тому, что интервалы между моментами появления импульсов на выходе генератора становятся случайными величи

676154

нами. Таким образом, компараторы 2 и 3 тактируются случайной импульсной последовательностью, блок 6 - периодической, поступающей на первый 5 вход микропроцессора от генератора ГТИ 14. В результате моменты времени, в которые тактируются компараторы, могут с равной вероятностью попасть на любой этап программы, выполняемой 10 в блоке 6. Это может привести к ошибке,- для пояснения которой рассмотрим процедуру образования оценки х отсчета сигнала при стохастическом квантовании второго рода.

15

л Х„

Sign (nj(lnj+ -0,5)q (2) где 1 п. - определяется в соответствии с (1) и sipn(n) - в соответствии с описанной процедурой. Из (2) следует, что в х входит именно то псевдослучайное число , которое было использовано в виде аналогового эквивалента в момент t у при определении п, , т.е. при тактировании компараторов. Если для повместо будет испольлучения 5 или чисзовано число )ло С каким-либо другим порядковым номером, то это приведет к неправильному образованию оценки и в итоге к неверному и, по-крайней мере, к ненадежному результату преобразования. Возможность подобной ситуации иллюстрируется структурной схемой алгоритма работы микропроцессорного измерительного преобразователя (фиг.З)., Из структурной схемы следует, что работа преобразователя организована как последовательность программных циклов. Проверкой условия i N, где N - заданньй объем выборки отсчетов сигнала, заканчивается программный цикл определения и обработки i-ro отсчета сигнала, после чего программа возвращается в начало с целью определения и обработки следующего отсчета . Из фиг.З следует, что в течение одного программного цикла в памяти микропроцессора хранятся одновременно три значения псевдослучайного числа: , к , к-и Обновление значения аналоговой величины на первом информационном выходе блока 6, используемой в качестве опорного уровня компараторов 2 и 3, производится на этапе Вывод q. От начала цикла i

до этого этапа на первом выходе сохраняется значение F а, т.е. знаJ К-1

чение, установленное на предыдущем программном цикле. Момент тактирования компараторов при стохастической

дискретизации может совпасть с любым этапом-программного цикла, т.е. может соответствовать опорному уровню f , q или q. Ввод результата квантования осуществляется только на этапе Ввод п,., затем Пу. обрабатывается по программе с,вполне конкретным числом F . Если компаратор тактируется на этапе Вывод q, то обработка должна осуществляться с числом , если компараторы тактируются до этого этапа - то с числом , . При появлении момента тактирования после этапа Ввод п,, фактический ввод результата квантования произойдет наследующем программном цикле, что требует его обработки также с числом j . Для исключения неопределенности при обработке необходимо с помощью внешних по отношению к блоку 6 средств осуществить операции по управлению вводом в блок 6 результата квантования. Эти операции вы. полняются логическим блоком 1 совместно с делителем 12, управляемым делителем 13 и элементом И 10.

Программная реализация алгоритма, приведенного на фиг.З, показывает, что отрезки программного цикла требующие использования числа ,., длиннее, чем отрезки, требующие . . Поэтому для обработки результата квантования п выбрано программное число .j, а с помощью логического блока 11 из ввода в блок 6 исключаются результаты квантования, полученные на отрезке Вывод q. Для этой цели на входы логического блока 1i поступают импульсы от ГТИ 4 и 14 и импульс от управляемого делителя 13, вырабатывающего команду возврата программы блока 6 в начало. Логический блок 11 вырабатывает сигнал ввода , поступающий на один из входов элемента И 10 и разрешающий прохождение результата квантования из регистра 9 в блок 6. Одновременно с ; разрешающим сигналом логический блок 11 вырабатывает импульс счета использованных результатов квантования, который с первого выхода поступает на вход делителя 12 .

Таким образом, каждый вводимый в блок 6 результат квантования обрабатывается совместно с псевдослучайным числам j , с операции запоминания которого в соответствии с фиг.3.начинается очередной программный цикл. После операции Ввод п определяется оценка отсчета х обрабатываемого сигнала по формуле (2). Далее производится статистическая обработка, т.е. накопление данных об искомом параметре сигнала. Эта операция в алгоритме названа Определение А, где Aj вычисляется по формуле

А. (x,)/N, (3) /ч к-1

где f(x) - некоторое функциональное преобразование, соответствующее искомому параметру сигнала, например

Ч(х,) х1.

На фиг.3 показано вычисление одного А, хотя в микропроцессоре может быть вычислено несколько различных функциональных преобразований ,) ,. . . , Ч.(Х)) I соответствующих нескольким измеряемым параметрам сигнала.

Проверка условия осуществляется управляемым делителем 13 совместно с делителем 12. Управляемый делитель 13 при наличии разрешающего потенциала на первом входе считает

поступающие на второй вход импульсы от ГТИ 14. Осуществляется счет по модулю М, значение которого определяется номером in команды блока 6, при котором в соответствии с конкретной программой должен осуществляться- возврат в начало. Для определения значения модуля воспользоваться выражением , так как для выполнения одной команды в блоке 6 необходимо 4 тактовых импульса.

Делитель 12 ведет счет результатов квантования, вводимых в блок 6. Это означает, что на вход делителя 12 с первого выхода логического блока 11 импульс поступает в том если на втором выходе логического блока 1I появляется потенциал, разре шающий прохождение через элемент И 10 результата квантования из регистра 9 на третий вход блока 6. Делитель 12 ведет счет по модулю N до тех пор, пока число введенных результатов квантования i S N имеет на выхо1:1

де потенциал, разрешающий управляемому делителю 13 возврат в начало программы. После того, как вьтЬлнено равенство , на выходе делителя 12 появляется запрещающий потенциал и управляемьш делитель 13 прекращает формирование импульсов возврата. Это означает, что закончена обработка отсчетов сигнала и получены значе-ния 1 -bL

А, -N- к). (4)

-ч-После этого (в соответствии с фиг.З) в программе осущестйляется переход к обработке величины А с целью ее функционального преобразования и получения значений измеряемы параметров сигнала. Виды функциональных преобразований определяются, в первую очередь, видом преобразования 4(xv;). Если, например (х,), то А„ D(х) - оценки дисперсии сигнала или его средней мощности. Тогда могут быть выполнены такие преобразования, как VA, с целью получения оценки эффективного значения сигнала и/или log А) с целью последу оп(его получения значений мощности в децибелах.

После завершения обработки по программе следует вывод результатов преобразования на второй информационный выход блока 6.

Формирование сигналов логическим блоком 11 производится в соответстВИИ с его структурной схемой (фиг. 2),

С началом каждого программного г цикла сигнал, поступающий на первыйвход логического блока 11 с выхода управляемого делителя 13, устанав- ливает на выходе счетчика 15 и инверсном выходе триггера 17 потенциал логического нуля, а на выходе триггера 16 - логической единицы. Счетчик 15 по входу С начинает счет импульсов генератора ГТИ 14, тактирующих блок 6. Объем счетчика 15 определяется равным числу тактовых импульсов, необходимых для выполне гия по фиг.З первых двух операций - запоминания , и генерирования г С учетом того, что для выполнения одной команды микропроцессора необходимы 4 тактовых импульса, можно считать, что счетчик 15 является ; счетчиком по модулю 4Ё-, где t - число команд, необходимых для вьтолнения двух: названных операций.

15 . i 8 ,

В течение этого этапа на один из входов элемента ШИ 20 подается с выхода триггера 16 логическая единица, следовательно, единица будет и на D-входе триггера 21. Если на этом этапе появится от ГТИ 4 импульс тактирования компараторов 2 и 3 (фиг.Л то при его воздействии на С-входе триггера 2 на выходе его установится единица. Значит разрешающий сигнал будет подан на элемент И 10, в результате чего на соответствующем этапе программы результат квантования п не будет введен в блок 6 из регистра 9. ОднЪвременно разрешающий потенциал устанавливается на входе элемента И 19, и при появлении в дальнейшем (после ввода п ) импульса на выходе формирователя 18 i-шпульсов через элемент 22 задержки будет подан импульс счета на вход делителя 12. Величина задержки определяется числом команд или временем, затpaчивae ым на ввод в блок 6 результата квантования. Кроме того, импуль с выхода элемента 22 задержки подается на установочный вход триггера 21 для установки его в нуль после завершения ввода.

Во время выполнения первых двух операций алгоритма (фиг.З) счетчик 15 ведет счет импульсов от ГТИ 14. После выполнения блоком 6 команд на выходе счетчика 15 появляется отрицательный перепад,- который переключает триггер 16, в результате чего на его выходе устанавливается потенциал логического нуля. Триггер 17 при: этом состояния не меняет, так как переключается при воздействии па его тактовый вход положительного фронта, т.е. переход из нуля в единицу. После переключения триггера 16 на обоих входах элемента ИЛИ 20 устанавливаются логические нули и на D-входе триггера 21 - также логический нуль. Поэтому, если на следующем этапе работы блока 6 (Вывод q) появится от ГТИ 4 импульс, тактирующий компараторы, то при его воздействии на тактовый вход триггера 2 I на выходе, триггера установится потенциал логического нуля. Это означает, что на вход с элементом И 10 (фиг.1) будет подан запрещающий сигнал и результат квантования из регистра 9 в блок 6 не будет введен. В результате того, что данный ре91эультат квантования в. процессе измерения не использован, нулевой потенциал с выхода триггера 21 запрещает в данном программном цикле прохождение через элемент И 19 сигнала сче та на делитель 12. При реализации в программе алгоритма, приведенного на фиг.З,, число команд, необходимых для выполнения операции Вывод q, нужно также сделаТь равным величине . Тогда после завершения этой операции на вы ходе счетчика 15 вновь появится импульс, который, переключив триггер 16, установит на его выходе потенциал логической единицы. Теперь на ин версном выходе триггера 17 установится единица, так как на D-входе нулевой потенциал. На оба входа эле мента ИЛИ 20 и, следовательно, на D-вход триггера 2 будет подан поте циал логической единицы. При этом вновь со-здаются условия для установки триггера 21 импульсом от ГТИ в единицу и выработки разрешающего сигнала для элементов И 10 и 19. Триггер 17 сохранит единичньш потен циал на выходе до конца программног цикла и, следовательно, до конца ци ла сохраняется возможность установк триггера.2 в единицу иь пульсом от ГТИ 4. Если это произойдет, то в со ответствии с алгоритмом ввод резуль тата квантования в блок 6 осуществи ся на следующем программном цикле. Таким образом, под управлением л гического блока 11 из ввода в блок и из учета делителем 12 исключаются результаты квантования, пол;у енные на этапе Вывод q, чем обеспечив ется надежность результата преобразования. Формула изобретени 1, Стохастический аналого-цифровой преобразователь, содержащий входной усилитель, вход которого является входной шиной, а выход сое динен с первыми входами первого и второго компараторов, вторые которых объединены и подключены к выходу первого генератора тактовы импульсов, элемент НЕ, вход icoTopo:го соединен с выходом первого компаратора, арифметико-логический бло информационный вход которого соединей с выходом элемента И, а первые 5,10 нформационные выходы являются выходой шиной, инвертор, выход которого оединен с третьим входом первого омпаратора, отличающийся ем, что, с целью расширения области применения путем увеличения частотного диапазона измеряемого сигнала при одновременном обеспечении надежности результата преобразования, в него введены шифратор, регистр, логический блок, делитель частоты, управляемьм делитель частоты, второй генератор тактовых импульсов, вход инвертора объединен с входом первого генератора тактовых импульсов, третьим входом второго компаратора и подключен к второму информационному выходу арифметико-логического блока, вход которого объединен с первым входом логического блока и подключен к выходу управляемого делителя частоты, а вход синхронизации объединен с входом управляемого делителя частоты, вторым входом логического блока и подключен к выходу второго генератора тактовых импульсов, третий вход логического блока соединен с выходом первого генера тора тактовых импульсов, первый выход через делитель частоты соединен с первым входом управляемого делителя частоты, а второй выход - с первым входом элемента И, второй вход которого соединен через регистр с выходом щифратора, первый и второй входы которого соединены соответственно с выходами элемента НЕ и второго компаратора. 2. Преобразователь по п. I, о т л и чающийся тем, что логический блок выполнен на счетчике импульсов, трех триггерах, формирователе импульсов, элементах И, ИЛИ, задержки, выход последнего из которых является вторым выходом блока а вход через элемент Н соединен с выходом формирователя импульсов, вход которого объединен с первым входом элемента ИЛИ и.подключен к инверсному выходу первого триггера, установочный вход которого объединен с установочными входами второго триггера, счетчика импульсов и является первым входом блока, вторым входом которого является счетный вход счетчика импульсов, выход которого соединен со счетным входом второго триггера, вы. ход которого соединен с вторым входом

элемента ИЛИ и счетным входом первого триггера информационный вход которого подключен к нулевому потенциалу, информационный вход третьего триггера соединен с выходом элемента ИЛИ устано-

вочный вход соединен с выходом элемента задержки, счетный вход является третьим входом блока, а выход соединен с вторым входом элемента И и является первым выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выполнения преобразования Фурье | 1987 |

|

SU1429125A1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| Устройство для регистрации информации | 1989 |

|

SU1698895A1 |

| Устройство поиска псевдослучайной последовательности | 1991 |

|

SU1788592A1 |

| Устройство для определения действующего значения сигнала | 1983 |

|

SU1141421A1 |

| УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО ВЫБОРА СИГНАЛОВ | 2012 |

|

RU2476923C1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ M-ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1989 |

|

RU2030103C1 |

| Стохастическое устройство для определения действующего значения сигнала | 1981 |

|

SU962940A1 |

| Дельта-кодер | 1986 |

|

SU1381715A1 |

| Дельта-кодер | 1987 |

|

SU1429321A1 |

изобретение относится к измерительной технике, .а именно к цифровым устройствам для измерения интегральных характеристик детерминированных и случайных сигналов, и может быть использовано в технике связи. Изобретение позволяет расширить область применения путем увеличения частотного -диапазона измеряемого сигнала при одновременном обеспечении надежности результата преобразования за счет введения в устройство, содержащее входной усилитель, первый и второй компараторы, первый генератор тактовых импульсов, элемент НЕ, инвертор, арифметико-логический блок, блок элементов И, шифратора, регистра логического блока, делителя частоты, управляемого делителя частоты, второго генератора тактовых импульI сов. 1 з.п ф-лы. 3 ил. , (Л с:

Авторы

Даты

1986-10-30—Публикация

1985-01-23—Подача