информационным входом схемы сравне- ния, первый выход которой подключен к первому входу четвертого элемента ИЛИ и управляющему входу счетчика подряд идущих приращений, первый выход которого соединен с информационными входами элем.ентов И пятой и шестой групп, второй выход схемы сравнения подключен к первому входу пятого элемента ИЛИ, выход которого подключен к управлякадим входам элементов И четвертой, пятой и седьмой групп и через первый формирователь импульсов - к второму входу четвертого элемента ИЛИ и управляющим входам элементов И второй группы и выходного регистра и входу сложения счетчика подряд идущих приращений, второй выход которого подключен к второму входу пятого элемента ИЛИ, выход четвертого элемента ИЛИ подключен череэ второй формирователь импульсов к управляющим входам элементов И первой , третьей и пятой групп, к входу сложения счетчика каналов и первому входу блока управления, второй вход которого подключен к третьему выходу счетчика каналов, второй выход которого соединен а управляющими входами элементов И седьмой группы, выходы элементов И шестой, четвертой и седьмой групп подключены соответственно к первому, второму и третьему информационным входам выходного регистра, выходы элементов И третьей и пятой групп, второй вход регистра и информационный вход счетчика подряд идущих приращений через кодовые шины соединены с информационным входом блока оперативной памяти, выход генератора тактирующих импульсов подключен к третьему входу блока управления, четвертый

и пятый входы которого являются соответственно входами пуска и останов устройства, причем блок управления содержит регистр сдвига, триггер синхронизации, пятый и шестой элементы И, шестой-девятый элементы ИЛИ и третий, четвертый и пятый формирователи импульсов, причем выход третьего формирователя импульсов соединен с вторым выходом блока и через четвертый формирователь импульсов с третьим выходом блока, первый вход пятого элемента И соединен через пятый формирователь импульсов с первым входом блока, второй вход - с нулевым выходом триггера синхронизации, а выход - с первым входом шестого элемента ИЛИ, .выходом соединенного с входом третьего формирователя импульсов, вторым входом - с четвертым входом блока, а третьим входом с первым выходом триггера сдвига, счетный и первый установочный входы которого подключены соответственно к выходам шестого элемента И и седьмого элемента ИЛИ, второй установочный вход - к четвертому входу блока и первым входам седьмого, восьмого и девятого элементов ИЛИ, а второй выход - к второму входу седьмого элемента ИЛИ, выход девятого элемента ИЛИ соединен с первым выходом , а второй вход - с пятым входом блока и вторым входом восьмого элемента ИЛИ, выход которого подключен к нулевому входу триггера синхронизации, единичный вход которого соединен с вторым входом блока, а единичный выход - с первым входом шестого элемента И, вторым входом подключенного к третьему входу блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для передачи сигналов приращений | 1982 |

|

SU1103276A1 |

| Многоканальный преобразователь напряжения в код | 1982 |

|

SU1109900A1 |

| Многоканальное устройство для передачи информации с дельта-модуляцией | 1982 |

|

SU1166330A1 |

| Устройство для передачи телеметрической информации | 1985 |

|

SU1262553A1 |

| Устройство для регистрации сейсмических сигналов на магнитную ленту | 1981 |

|

SU1030752A1 |

| Устройство для передачи и приема информации | 1982 |

|

SU1104571A1 |

| Многоканальное устройство дляпЕРЕдАчи иНфОРМАции C дЕльТА- МОдуляциЕй | 1979 |

|

SU849271A1 |

| Устройство для передачи и приема сигналов | 1985 |

|

SU1275510A1 |

| Устройство для регистрации информации | 1983 |

|

SU1115074A1 |

| Устройство для измерения и регистрации частоты вращения вала скважинного забойного двигателя | 1984 |

|

SU1265294A1 |

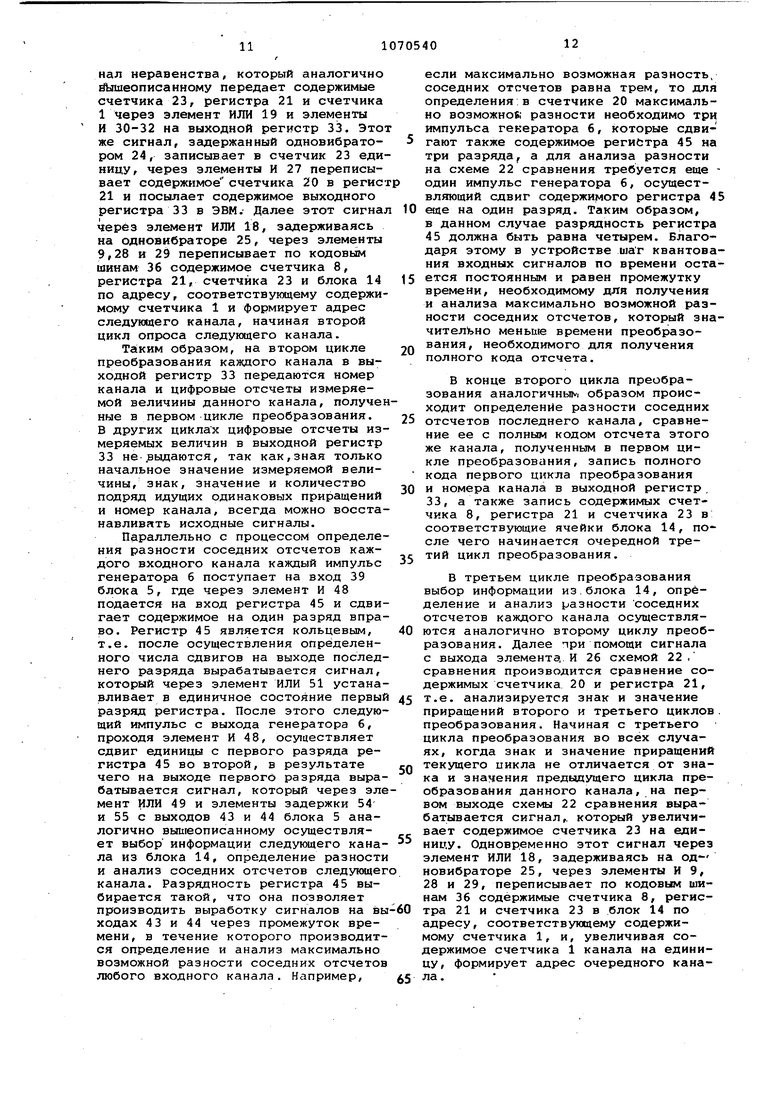

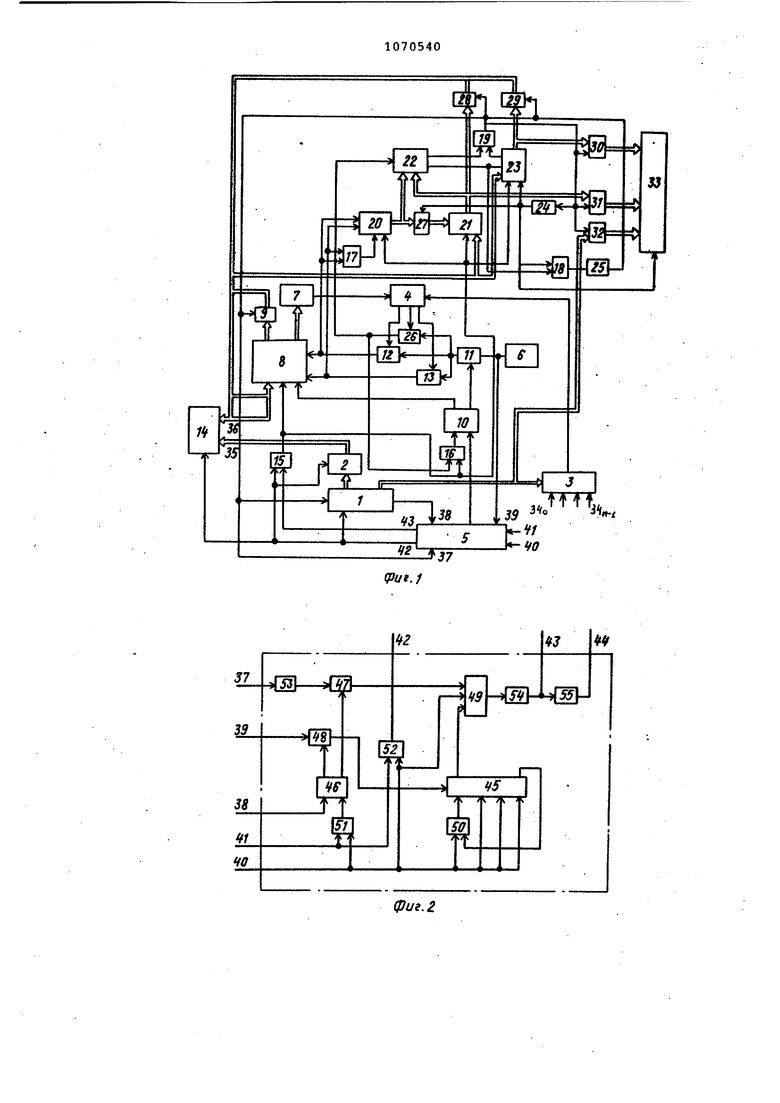

УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С ДАТЧИКАМИ, содержащее счетчик каналов, первый выход которого подключен к информапйонному входу узла усилителей адреса канала, выходом подключенного к адресному входу блока оперативной памяти, второй выход счетчика каналов соединен с входом коммутатора каналов, группа входов которого является группой входов устройства, а вьтход подключен к первому входу компаратора, второй вход которого через преобразователь кода в напряжение подключен к первому разрядному выходу реверсивного счетчика, второй разрядный выход которого подключен к информационным входам элементов И первой группы, выходы которых через кодовые шины соединены с инФормагионными входами реверсивного счетчика и блока оперативной памяти, выход генератора тактирующих импульсов подключен к первому входу первого элемента И, выход которого подключен к первым входам второго и третьего элементов К, выходы которых подключены соответственно к входам сложения и вычитания реверсивного счетчика, управляющий вход которого подключен к единичному входу триггера управления, нулевой выход которого подключен к второму входу первого элемента И, выход первого элемента ИЛИ соединен с входом сброса реверсивного счетчика, отличающееся тем, что, с 1елью повьадения пропускной способности устройства, в него введены счетчик разности, регистр, схема сравнения,счетчик подряд идущих приращейий, два формирователя импульсов, выходной регистр, месть групп элементов И, блок управления и пять элементов ИЛИ, причем первый выход блока -управления подключен к выходу сброса счетчика каналов, первому входу первого элемента ИЛИ и управляющему входу блока оперативной памяти, второй выход- к второму входу первого элемента ИЛИ и управляюгцему входу узла усилителей адреса каналов, а третий выход О в к нулевому входу триггера управления единичный вход которого подключен к СО выходу второго элемента ИЛИ, первый вход четвертого элемента И соединен с выходом первого элемента И, выход первого элемента ИЛИ соединен с первыми входами второго элемента ИЛИ, регистра и входами сброса счетчика подряд идущих приращений и счетчика разности, первый и второй знаковые входы которого подключены соответст-. венно к выходам второго и третьего элементов И и первому и второму входам третьего элемента ИЛИ, вторые входы второго, третьего и четы вертого элементов И подключены со4 ответственно к первому, второму и третьему выходам компаратора, выход четвертого элемента И подключен к второму входу второго элемента ИЛИ и управляющему входу схемы сравнения, выход третьего элемента ИЛИ подключен к счетному входу .счетчика разности, выход которого подключен к. первому информационному входу схемы сравнения и информационным входам элементов И второй группы, выходь которых подключены к рзторому входу регистра, ныход которого соединен с информапионными нходлми элементов И (третьей и четвортог; групп и вторым

1

Изобретение относится к вычислительной технике и может быть использовано в АСУ технологическими процессами для подключения аналоговых датчиков в вычислительной машине (ВМ). I .

Известно, устройство для сопряжения вычислительной машины с датчиками , содержащее узлы запуска преобразования, генераторы эталонного напряжения, нуль-органы, формирователи импульсов первой и второй группы, шифратор,.узел согласования, эле мент ИЛИ, выходной регистр, генератор импульсов времени, коммутатор, счетчик импульсов времени, элементы И и линию связи 11.

Однако длительность цикла преобразования для каждого канала в указанном устройстве равна максимальной длительности цикла преобразования,

что приводит к уменьшению общего быстродействия ввода информации в ЭВМ. Кроме того, отсчеты каждого канала таких устройств состоят из (8-15)разрядных кодов .и они обычно содержат большую избыточность информации.

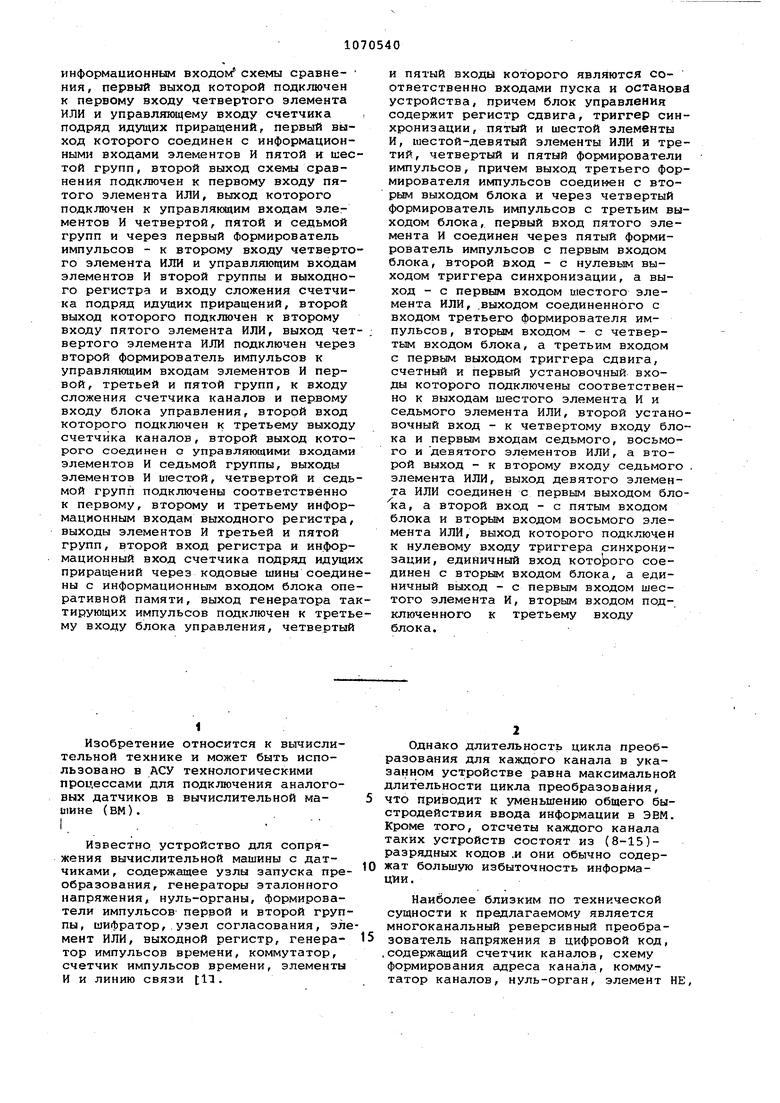

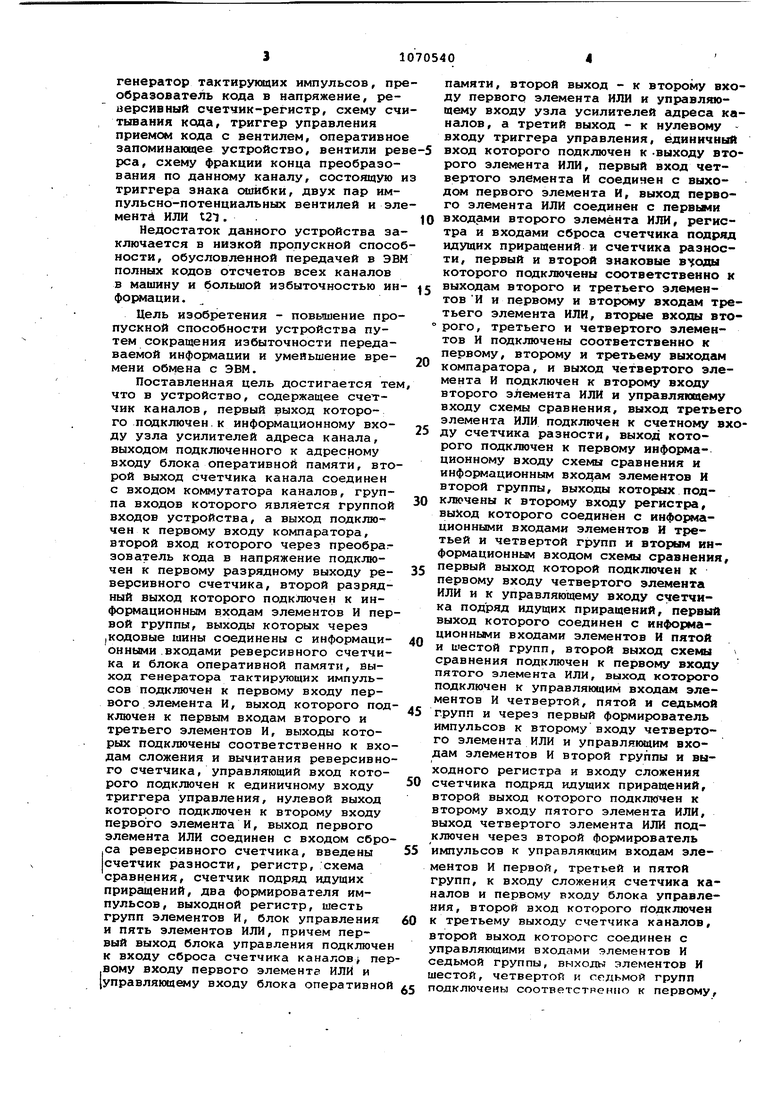

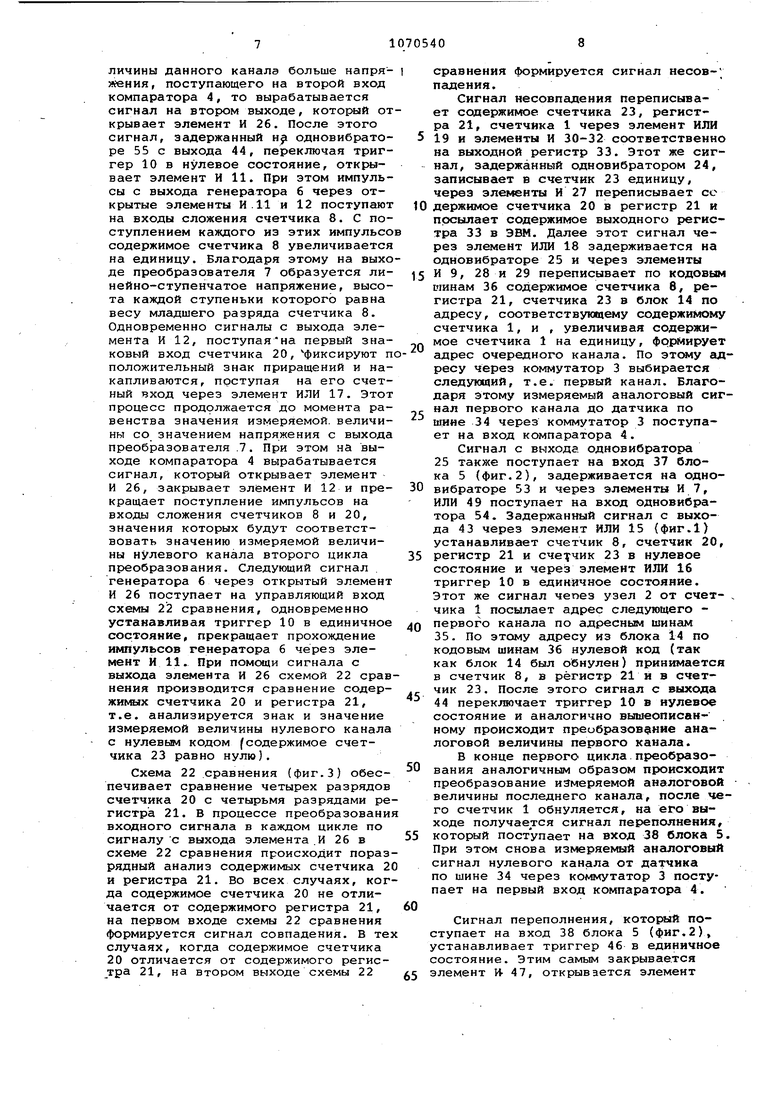

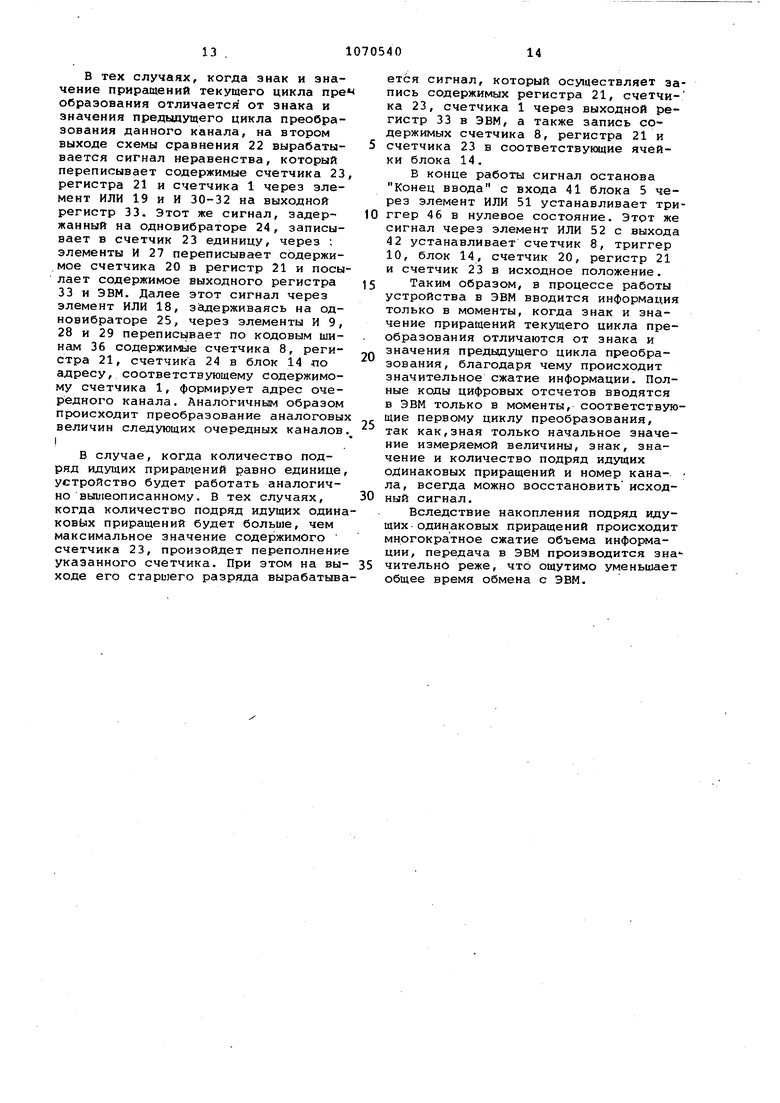

Наиболее близким по технической сущности к предлагаемому является многоканальный реверсивный преобразователь напряжения в цифровой код, .содержащий счетчик каналов, схему формирования адреса канала, коммутатор каналов, нуль-орган, элемент НЕ, генератор тактирукяцих импульсов, пр образователь кода в напряжение, реверсивный счетчик-регистр, схему сч тывания кода, триггер управления приемом кода с вентилем, оперативно запоминающее устройство, вентили ре рса, схему фракции конца преобразования по давнему каналу, состоящую триггера знака ошибки, двух пар импульсно-потенциальных вентилей и эл менте ИЛИ t21, Недостаток данного устройства за ключается в низкой пропускной спосо ности, обусловленной передачей в ЭВ полных кодов отсчетов всех каналов в машину и большой избыточностью ин формации. Цель изобретения - повышение про пускной способности устройства путем сокращения избыточности передаваемой информации и уменьшение времени обмена с ЭВМ, Поставленная цель достигается те что в устройство, содержащее счетчик каналов, первый выход которого подключен . к информационному входу узла усилителей адреса канала, выходом подключенного к адресному входу блока оперативной памяти, вто рой выход счетчика канала соединен с входом коммутатора каналов, группа входов которого является группой входов устройства, а выход подключен к первому входу компаратора, второй вход которого через преобраг зователь кода в напряжение подключен к первому разрядному выходу реверсивного счетчика, второй разрядный выход которого подключен к информационным входам элементов И пер вой группы, выходы которых через ,кодовые шины соединены с информационными входами реверсивного счетчика и блока оперативной памяти, выход генератора тактирующих импульсов подключен к первому входу первого . элемента И, выход которого под ключен к первым входам второго и третьего элементов И, выходы которых подключены соответственно к вхо дам сложения и вычитания реверсивно го счетчика/управляющий вход которого подключен к единичному входу триггера управления, нулевой выход которого подключен к второму входу первого элемента И, выход первого элемента ИЛИ соединен с входом сбро са реверсивного счетчика, введены счетчик разности, регистр, схема сравнения, счетчик подряд идущих приращений, два формирователя импульсов, выходной регистр, шесть групп элементов И, блок управления и пять элементов ИЛИ, причем первый выход блока управления подключе к входу сброса счетчика каналов пер вому входу первого элементе ИЛИ и управляющему входу блока оперативной памяти, второй выход - к второму входу первого элемента ИЛИ и управляющему входу узла усилителей адреса каналов, а третий выход - к нулевому входу триггера управления, единичный вход которого подключен к -выходу второго элемента ИЛИ, первый вход четвертого элемента И соединен с выходом первого элемента И, выход первого элемента ИЛИ соединен с первьми входами второго элемента ИЛИ, регистра и входами сброса счетчика подряд идущих приращений и счетчика разности, первый и второй знаковые которого подключены соответственно к выходам второго и третьего элементов И и первому и второму входгш третьего элемента ИЛИ, вторые входы второго, третьего и четвертого элементов И подключены соответственно к первому, второму и третьему выходам компаратора, и выход четвертого элемента И подключен к второму входу второго элемента ИЛИ и управляющему входу схемы сравнения, выход третьего элемента ИЛИ подключен к счетному входу счетчика разности, выход которого подключен к первому информационному входу схемы сравнения и информационным входам элементов И второй группы, выходы которых подключены к второму входу регистра, выход которого соединен с информационнЕлми входами элементов И третьей и четвертой групп и вторым информационным входом схемы сравнения, первый выход которой подключен к первому входу четвертого элемента ИЛИ и к управляющему входу счетчика подряд идущих приращений, первый выход которого соединен с информационными входами элементов И пятой и шестой групп, второй выход схемы сравнения подключен к первому входу пятого элемента ИЛИ, выход которого подключен к управляющим входам элементов И четвертой, пятой и седьмой групп и через первый формирователь импульсов к второму входу четвертого элемента ИЛИ и управляющим входам элементов И второй группы и выходного регистра и входу сложения счетчика подряд идущих приращений, второй выход которого подключен к второму входу пятого элемента ИЛИ, выход четвертого элемента ИЛИ подключен через второй формирователь импульсов к управляющим входам элементов И первой, третьей и пятой групп, к входу сложения счетчика каналов и первому входу блока управления, второй вход которого подключен к третьему выходу счетчика каналов, торой выход которого соединен с управляющими входами элементов И едьмой группы, выходьт элементов И естой, четвертой и седьмой групп одключены соответстменЕЮ к первому. второму и третьему инфог ационным входам выходного регистра, выходы элементов И третьей и пятой групп, второй вход и инфор«1ационный вход счетчика подряд идущих приращений через кодовые шины соединен с инфррмационным входом блока оперативной памяти, выход генератора тактирующих импульсов подключен к третьему входу блока управления, четвертый и пятый входы которого являются COOTветственно входами пуска и останова устройства, причем блок управления содержит регистр сдвига, триггер син хронизации, пятый и шестой элементы И, шеетой-девятый элементы ИЛИ и третий, четвертый и пятый формирова теля импульсов, причем выход третьего формирователя импульсов соединен с вторым выходом блока и через четвертый формирователь импульсов с третьим выходом блока, первый вход пятого элемента И соединен через пя тый формирователь импульсов с первым входом блока, второй вход - с нулевы выходом триггера синхронизации, а выход - с первым входом шестого элемента ИЛИ, выходом соединенного с входом третьего формирователя импуль сов, вторым входом - с четвертым входом блока, а третьим входом - с первым Выходом регистра сдвига, сче нь1й и первый установочный входы кото рого подключены соответственно к вы ходам шестого и седьмого элемента ИЖ второй установочный вхбд - к четвертому входу блока и первым входам седьмого, восьмого и девятого элементов ИЛИ, второй выход - к .второму входу седьмого элеьюнта ИЛИ выход девятого элемента ИЛИ соединен с первым выходом блока, а второй вход - с пятьал входом блока и вторым входом восьмого элемента ИЛИ, выход которого подключен к нулевому входу триггера синхронизации, единичный вход которого соединеи с вторым входом блока, а единичный выход - с первым входом шестого эле мента И, вторым входом подключенного к третьему входу блока. На фиг,1 представлена структурная схема устройства; на фиг.2 функциональная схема блока управления; на фиг.З - то же, схемы сравне ния. Устройство {фиг.1) содержит счет чики 1 каналов, узел 2 усилителей адреса каналов, коммутатор 3 каналов, компаратор 4, блок 5 управления, генератор б тактирующих импуль сов, преобразователь 7 кода в напря жение, реверсивный счетчик 8, элементы И 9 первой группы, триггер 10 управления, первый, второй и третий элементы и 11-13 соответственно, блок 14 оперативной памяти, первый, второй, третий, четвертый и пятый элементы ИЛИ 15-19 соответственно, счетчик 20 регистра, регистр 21, схе«му 22 сравнения, счетчик 23 количества подряд идущих приращений, формирователи 24 и 25 импульсов (одновибраторы), четвертый элемент И 26, элементы И 27-32 второй, трет-ьей, пятой шестой, четвертой и седьмой групп соответственно, выходной регистр 33 и шины 34 группы входов устройства. На фиг.1 обозначены адресные шины 35 и кодовые шины 36 блока 14 оперативной памяти, а также входы 37-41 и выходы 42-44 блока 5 управления. Блок 5 управления содержит (фиг.2) регистр 45 сдвига, триггер 46 синхро-. низации, пятый и шестой элементы И 47 и 48, шестой-девятый элементы ИЛИ- 49-52 и третий, четвертый и пятый формирователи импульсов 53-55 соответственно. Схема сравнения 22 (фиг.З) содержит элементы ИЛИ 56-64 и элементы И 65-80. Устройство работает следующим образом. В начале работы сигнал пуска (Начало ввода)с входа 40 (фиг.2) через элемент ИЛИ 51 устанавливает триггер 46 и все разряды регистра 45, кроме первого, в нулевое положение. Первый разряд регистра 45 через элемент ИЛИ 50 устанавливается в единичное положение. Этот же сигнал через элемент ИЛИ 52 с выхода 42 обнуляет все ячейки блока 14 и через элемент ИЛИ 15 устанавливает счетчик 8, счетчик 20, регистр 21 и счетчики 23 в нулевое (исходное) состояние, а через элемент ИЛИ 16 - триггер 10 в единичное состояние. С выхода счетчика 1 нулевой код номера канала поступает на вход коммутатора 3. При этом измеряелмй аналоговый сигнал нулевого канала от датчика 24 через коммутатор 3 поступает на первый вход компаратора 4. По сигналу Начало ввода через элемент ИЛИ 49, задерживаясь на одновибраторе 54, на выходе 43 формируется строб, разрешаквдий прохождение через узел 2 от счетчика 1 адреса канала по адресным шинам 35. По этому адресу из блока 14 по кодовым шинам 36 нулевой код (так как все ячейки бяока 14 были обнулены) принимается в счетчик В, в регистр 21 к в счетчик 23. При этом на выхЬде преобразователя 7 образуется нулевой уровень напряжения, который поступает на вход компаратора 4. В зависимости от результата сравнения этого напряжения с измеряемой величиной нулевого канала, которая через коммутатор 3 поступает на первый вход, на одном из трех выходов компаратора 4 вырабатывается сигнал. Если значение измеряемой ae-i личины данного канала больше напря5 еения, поступающего на второй вход компаратора 4, то вырабатывается сигнал на втором выходе, который от крывает элемент И 26. После этого сигнал, задержанный н одновибраторе 55 с выхода 44, переключая триггер 10 в нулевое состояние, открывает элемент И 11. При этом импульсы с выхода генератора 6 через открытые элементы И.11 и 12 поступают на входы сложения счетчика 8. С поступлением каждого из этих импульсо содержимое счетчика 8 увеличивается на единицу. Благодаря этому на выхо де преобразователя 7 образуется линейно-ступенчатое напряжение, высота каждой ступеньки которого равна весу младшего разряда счетчика 8. Одновременно сигналы с выхода элемента И 12, поступаяна первый знаковый вход счетчика 20, фиксируют п положительный знак приращений и накапливаются, поступая на его счетный вход через элемент ИЛИ 17. Этот процесс продолжается до момента равенства значения измеряемой, величины со значением напряжения с выхода преобразователя .7. При этом на выходе компаратора 4 вырабатывается сигнал, который открывает элемент И 26, закрывает элемент И 12 и прекращает поступление импульсов на входы сложения счетчиков 8 и 20, значения которых будут соответствовать значению измеряемой величины нулевого канала второго цикла преобразования. Следующий сигнал генератора 6 через открытый элемент И 26 поступает на управляющий вход схемы 22 сравнения, одновременно устанавливая триггер 10 в единичное состояние, прекращает прохождение импульсов генератора 6 через элемент И 11. При помощи сигнала с выхода элемента И 26 схемой 22 срав нения производится сравнение содеруккмах счетчика 20 и регистра 21, т.е. анализируется знак и значение измеряемой величины нулевого канала с нулевым кодом (содержимое счетчика 23 равно нулю). Схема 22 .сравнения (фиг.З) обеспечивает сравнение четырех разрядов счетчика 20 с четырьмя разрядами ре гистра 21. В процессе преобразовани входного сигнала в каждом цикле по сигналу С выхода элемента .И 26 в схеме 22 сравнения происходит пораз рядный анализ содержимых счетчика 2 и регистра 21. Во всех случаях, ког да содержимое счетчика 20 не отличается от содержимого регистра 21, на первом входе схемы 22 сравнения формируется сигнал совпадения. В тех случаях, когда содержимое счетчика 20 отличается от содержимого регистра 21, на втором выходе схемы 22 сравнения формируется сигнал несов-; падения. Сигнал несовпадения переписывает содержимое счетчика 23, регистра 21, счетчика 1 через элемент ИЛИ 19 и элементы И 30-32 соответственно на выходной регистр 33. Этот же сигнал, задержанный одновибратором 24, записывает в счетчик 23 единицу, через элементы И 27 переписывает се держимое счетчика 20 в регистр 21 и посылает содержимое выходного регистра 33 в ЭВМ. Далее этот сигнал через элемент ИЛИ 18 задерживается на одновибраторе 25 и через элементы И 9, 28 и 29 переписывает по кодовым минам 36 содержимое счетчика 8, регистра 21, счетчика 23 в блок 14 по адресу, соответствующему содержимому счетчика 1, и , увеличивая содержимое счетчика 1 на единицу, формирует адрес очередного канала. По этсму адресу через коммутатор 3 выбирается следующий, т.е. первый канал. Благодаря этому измеряемый аналоговый сигнал первого канала до датчика по шине 34 через коммутатор 3 поступает на вход компаратора 4. Сигнал с выхода одновибратора 25 также поступает на вход 37 блока 5 (фиг.2), задерживается на одновибраторе 53 и через элементы И 7, ИЛИ 49 поступает на вход одновибратора 54. Задержанный сигнал с выхода 43 через элемент ИЛИ 15 {фиг.1) устанавливает счетчик 8, счетчик 20, регистр 21 и сче-учик 23 в нулевое состояние и через элемент ИЖ 16 триггер 10 в единичное состояние. Этот же сигнал чепез узел 2 от счетчика 1 посылает адрес следующего первого канала по адресным шинам 35. По этому адресу из блока 14 по кодовым шинам 36 нулевой код (так как блок 14 был обнулен) принимается в счетчик 8, в регистр 21 и в счетчик 23. После этого сигнал с выхода 44 перек ночает триггер 10 в нулевое состояние и аналогично вышеописанному происходит преобразование аналоговой величины первого канала. В конце первого цикла преобразования аналогичным образом происходит преобразование измеряемой аналоговой величины последнего канала, после чего счетчик 1 обнуляется, на его выходе получается сигнал переполнения, который поступает на вход 38 блока 5. При этом снова измеряелолй аналоговый сигнал нулевого канала от датчика по шине 34 через коммутатор 3 поступает на первый вход компаратора 4. Сигнал переполнения, который потупает на вход 38 блока 5 (фиг.2), станавливает триггер 46 в единичное остояние. Этим самым закрывается лемент И- 47, открывается элемент И 48 и начинаются основные циклы пре образования всех каналов. Первый цикл преобразования всех каналов является подготовительным., В конце этого цикла в соответствующих адресах блока 14 будут находиться полные коды цифровых отсчетов всех входных каналов. Начиная с второго цикла преобразования импульсы с входа 39 блока 5 проходят открытый элемент И 48 и поступают на вход регистра 45. Первым импульсом содержимое регистра 45 сдвигается на один разряд вправо, и на выходе первого разряда получается сигнал, который через элемент ИЛИ 49 задерживаясь на одновибраторе ОВ1, с выхода 43 блока 5 управления через логический элемент ИЛИ 54 устанавливает счетчики 8,20 и 23, регистр 21 в нулевое состояние, а через элемент ИЛИ 16 - триггер 10 в единичное состояние и через узел 2 от счетчика 1 посылает адрес нулевого канала по адресным шинам 35. По этому .адресу из блока 14 по кодовым шинам 36 в счетчик 8 принимается полный код цифрового отсчета, соответствующий значению измеряемой аналоговой величины нулевого канала первого цикла преобразования, в регистр 21 - знак и значение полного кода, а в счетчик 23 - единица. При этом на выходе преобразователя 7 образуется уровень напряжения, соответствующий значению отсчета нулевого канала первого цикла преобразования, который поступает на второй вход компаратора 4. В.зависимости от результата сравнения этого напряжения с измеряемой величи ной нулевого канала, которая через коммутатор 3 поступает на другой вхо компаратора 4, на одном из.трех выходов которого вырабатывается сигнал Если текущее значение измеряемой вел чины данного канала больше предыдуще го, то сигналом на первом- выходе открывается элемент И 12. Если текущее значение измеряемой величины данного канала равно предыдущему, то вырабатывается сигнал на втором выходе компаратора и открывается элемент И 26. Если текущее значение измеряемой величины данного канала меньше предьщущего, сигнал на третьем выходе открывает элемент И 13. После это ,го сигнал с выхода 44 блока 5, переключая триггер 10 в нулевое состояни открывает элемент И II.При этом,если значение измеряемой величины нулевог канала второго цикла преобразования больше значения первого цикла преобразования, то импульсы с выхода гене ратора 6 через открытые элементы И 1 и 12 поступают на входы сложения счетчика 8. Благодаря этому на выход преобразователя 7 от уровня напряжеиия, соответствующего предьщущему значению данного канала, образуется линейно-ступенчатое возрастающее напряжение, высота каждой ступеньки которого равна весу младшего разряда счетчика 8. Одновременно сигналы с выхода элемента И 12, поступая на первый знаковый вход счетчика 20, фиксируют положительный знак приращений и накапливаются через элемент ИЛИ 17, поступая на его счетный вход. Если значение измеряемой величины нулевого канала второго цикла преобразования меньше значения первого цикла преобразования, то импульсы с выхода генератора 6 через открытые элементы И 11 и 13 поступают на входы вычитания счетчика 8. Благодаря этому на выходе преобразователя 7 от уровня напряжения,соответствующего предыдущему значению канала, образуется линейно-ступенчатое уменьшающееся напряжение. При этом сигналы с выхода элемента И 13, поступая на второй знаковый вход счетчика 20, фиксируют отрицательный знак и через элемент ИЛИ 17, поступая на его счетный вход, накапливаются. Этот процесс продолжается до момента равенства значения измеряемой величины значению напряжения с выхода преобразователя кода в напряжение. При этом на выходе компаратора 4 вырабатывается сигнал, который открывает элемент И 26, за-, крывает элементы И 12 и 13 и прекращает поступление импульсов на входы сложения или вычитания счетчика 8, содержимое которого соответствует значению измеряемой величины нулевого канала второго цикла преобразования, а в счетчике 20 находятся знак и значение разности отсчетов второго и первого циклов преобразования. Начиная с этого цикла в счетчике 20 получается разность значений измеряемой величины соседних циклов данного канала. Следующий сигнал генератора б через открытый элемент И 26 поступает на управляющий вход схемы 22 сравнения, одновременно устанавливая триггер 10 в единичное состояние , и прекращает прохождение импульсов генератора 6 через элемент И 11. При помощи сигнала с выхода элемента И 26 схемой 22 сравнения производится сравнение содержимых счетчика 20 и регистра 21, т.е. анализируется знак и значение приращений второго и первого циклов преобразований. При сравнении знака и значения разности, находящейся в счетчике 20, с отсчетом, пропорциональным значению измеряемой величины данного канала, полученным в первом цикле и находящимся в регистре 21, на втором выходе схемы 22 сравнения получается сигнал неравенства, который аналогично йУшеописаиному передает содержимые счетчика 23, регистра 21 и счетчика 1 через элемент ИЛИ 19 и элементы И 30-32 на выходной регистр 33. Это же сигнал, задержанный одновибратором 24, записывает в счетчик 23 единицу, через элементы И 27 переписывает содержимое счетчика 20 в регист 21 и посылает содержимое выходного регистра 33 в ЭВМ. Далее этот сигнал через элемент ИЛИ 18, задерживаясь на одновибраторе 25, через элементы 9,28 и 29 переписывает по кодовым шинам 36 содержимое счетчика 8, регистра 21, счетчика 23 и блока 14 по адресу, соответствующему содержимому счетчика 1 и формирует адрес следующего канала, начиная второй цикл опроса следующего канала.

Та;ким образом, на втором цикле преобразования каждого канала в выходной регистр 33 передаются номер канала и цифровые отсчеты измеряемой величины данного канала, полученные в первом -цикле преобразования. В других циклах цифровые отсчеты измеряемых величин в выходной регистр 33 не вьадаются, так как,зная только начальное значение измеряемой величины, знак, значение и количество подряд идущих одинаковых приращений и номер канала, всегда можно восстанавливать исходные сигналы.

Параллельно с процессом определения разности соседних отсчетов каждого входного канала каждый импульс генератора 6 поступает на вход 39 блока 5, где через элемент И 48 подается на вход регистра 45 и сдвигает содержимое на один разряд вправо. Регистр 45 является кольцевым, т.е. после осуществления определенного числа сдвигов на выходе последнего разряда вырабатывается сигнал, который через элемент ИЛИ 51 устанавливает в единичное состояние первый разряд регистра. После этого следующий импульс с выхода генератора 6, проходя элемент И 48, осуществляет сдвиг единицы с первого разряда регистра 45 во второй, в результате чего на выходе первого разряда вырабатывается сигнал, который через элемент ИЛИ 49 и элементы задержки 54 и 55 с выходов 43 и 44 блока 5 аналогично вышеописанному осуществляет выбор информации следующего канала из блока 14, определение разности и анализ соседних отсчетов следующег канала. Разрядность регистра 45 выбирается такой, что она позволяет производить выработку сигналов на вы ходах 43 и 44 через Промежуток времени, в течение которого производится определение и анализ максимально возможной разности соседних отсчетов любого входного канала. Например,

если максимально возможная разность, соседних отсчетов равна трем, то для определения в счетчике 20 максимально возможное; разности необходимо три импульса генератора 6, которые сдвигают также содержимое регистра 45 на три разряда, а для анализа разности на схеме 22 сравнения требуется еще один импульс генератора 6, осуществляющий сдвиг содержимого регистра 4 еще на один разряд. Таким образом, в данном случае разрядность регистра 45 должна быть равна четырем. Благодаря этому в устройстве шаг квантования входных сигналов по времени остается постоянным и равен промежутку времени, необходимому для получения и анализа максимально возможной разности соседних отсчетов, который значител но меньше времени преобразования, необходимого для получения полного кода отсчета.

В конце второго цикла преобразования аналогичньл , образом происходит определение разности соседних отсчетов последнего канала, сравнение ее с полным кодом отсчета этого же канала, полученным в первом цикле преобразовгжия, запись полного кода первого цикла преобразования и номера канала в выходной регистр , 33, а также запись содержимых счетчика 8, регистра 21 и счетчика 23 в соответствующие ячейки блока 14, после чего начинается очередной третий цикл преобразования.

В третьем цикле преобразования выбор информации из.блока 14, определение и анализ разности соседних отсчетов каждого канала осуществляются аналогично второму циклу преобразования. Далее при помощи сигнала с выхода элемента, И 26 схемой 22/ сравнения производится сравнение содержимых счетчика 20 и регистра 21, т.е. анализируется знак и значение приращений второго и третьего циклов преобразования. Начиная с третьего цикла преобразования во всех случаях, когда знак и значение приращений текущего иикла не отличается от знака и значения предыдущего цикла преобразования данного канала, на первом выходе схемы 22 сравнения вырабатывается сигнал, который увеличивает содержимое счетчика 23 на единицу. Одновременно этот сигнал через элемент ИЛИ 18, задерживаясь на одновибраторе 25, через элементы И 9, 28 и 29, переписывает по кодовым шинам 36 содержимые счетчика 8, регистра 21 и счетчика 23 в .блок 14 по адресу, соответствующему содержимому счетчика 1, и, увеличивая содержимое счетчика 1 канала на единицу, формирует адрес очередного канала.

В тех случаях, когда знак и значение приращений текущего цикла преч образования отличается от знака и значения предыдущего цикла преобразования данного канала, на втором выходе схемы сравнения 22 вырабатывается сигнал неравенства, который переписывает содержимые счетчика 23, регистра 21 и счетчика 1 через элемент ИЛИ 19 и И 30-32 на выходной регистр 33. Этот же сигнал, задержанный на одновибраторе 24, записывает в счетчик 23 единицу, через i элементы И 27 переписывает содержимое счетчика 20 в регистр 21 и посылает содержимое выходного регистра 33 и ЭВМ. Далее этот сигнал через элемент ИЛИ 18, задерживаясь на одновибраторе 25, через элементы И 9, 28 и 29 переписывает по кодовым шинам 36 содержимые счетчика 8, регистра 21, счетчика 24 в блок 14 по адресу, соответствующему содержимому счетчика 1, формирует адрес очередного канала. Аналогичным образом происходит преобразование аналоговых величин следующих очередных каналов. I

В случае, когда количество подряд идущих приращений равно единице, устройство будет работать аналогично вышеописанному. В тех случаях, когда количество подряд идущих одинаKOBbix приращений будет больше, чем максимальное значение содержимого счетчика 23, произойдет переполнение указанного счетчика. При этом на выходе его старшего разряда вырабатывается сигнал, который осуществляет запись содержимых регистра 21, счетчика 23, счетчика 1 через выходной регистр 33 в ЭВМ, а также запись содержимых счетчика 8, регистра 21 и

счетчика 23 в соответствующие ячейки блока 14.

В конце работы сигнал останова Конец ввода с входа 41 блока 5 через элемент ИЛИ 51 устанавливает три0 ггер 46 в нулевое состояние. Этот же сигнал через элемент ИЛИ 52 с выхода 42 устанавливает счетчик 8, триггер 10, блок 14, счетчик 20, регистр 21 и счетчик 23 в исходное положение.

5 Таким образом, в процессе работы устройства в ЭВМ вводится информация только в моменты, когда знак и значение приращений текущего цикла преобразования отличаются от знака и

значения предыдущего цикла преобразования, благодаря чему происходит значительное сжатие информации. Полные коды цифровых отсчетов вводятся в ЭВМ только в моменты, соответствующие первому циклу преобразования, так как,зная только начальное значение измеряемой величины, знак, значение и количество подряд идущих одинаковых приращений и номер канала, всегда можно восстановить исход0 ный сигнал.

Вследствие накопления подряд идущих- одинаковых приращений происходит многократное сжатие объема информации, передача в ЭВМ производится зна5 чительно реже, что ощутимо уменьшает общее время обмена с ЭВМ.

§5 1$

.

Cue мал cffk/x.f ycmpot/cfTfio

фиг.З

СЮ

ых. г

Bux.f

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для сопряжения вычислительной машины с датчиками | 1978 |

|

SU765798A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| В. И. Ульянова ^Ленина)" | 0 |

|

SU188757A1 |

Авторы

Даты

1984-01-30—Публикация

1982-09-29—Подача