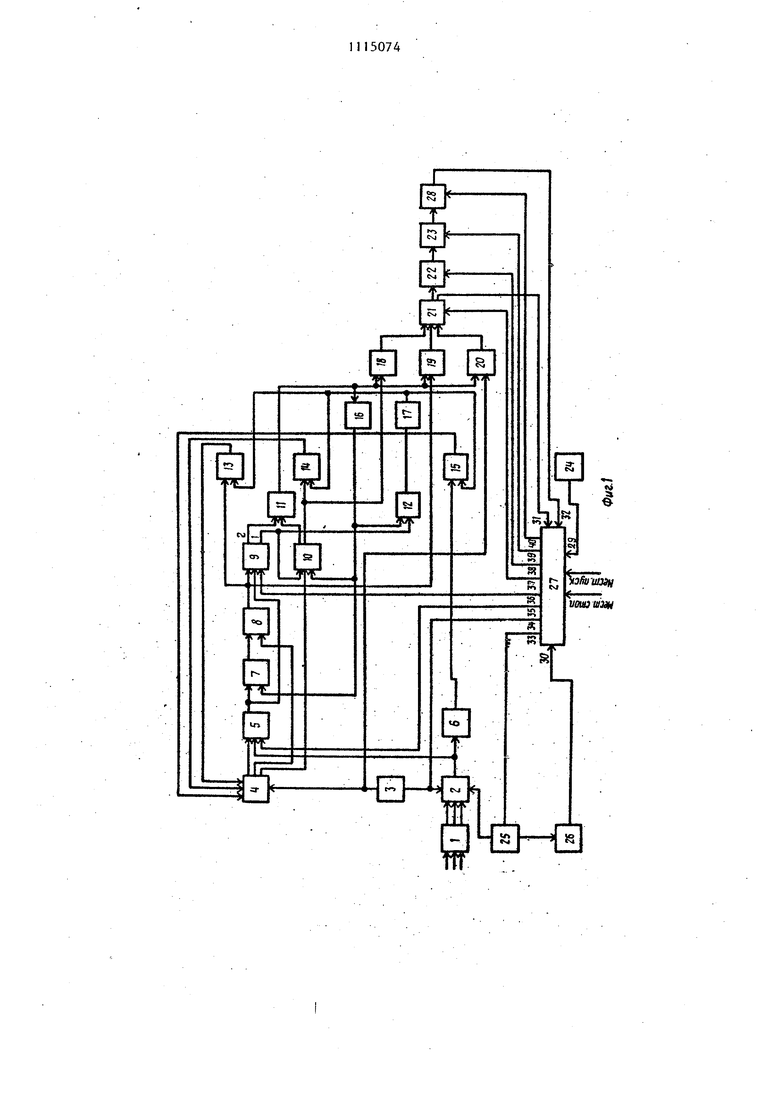

1 Изобретение относится к автомати ке и вычислительной технике и может .быть использовано для цифровой регистрации измерительной информации перфоленту с целью последующего вво да ее в цифровую вычислительную машину. Известно устройство для управления регистрацией информации, со держащее блок согласования, коммута тор, преобразователь кода, блок уси лителей, перфоратор, блок выбора числа каналов, счетчик, блок управления и генератор синхросигналов, выход которого подключен к входу бл ка управления, к другому входу кото рого подключен выход счетчика, -другой выход которого подключен к входу коммутатора, к другим входам которого подключены выходы блока согласования, выход преобразователя кодов подключен R входу блока усилителей, выход которого подключен к входу перфоратора, выходы блока управления подключены к входам блока выбора числа каналов, преобразовате ля кодов, блока усилителей и перфоратораНедостатком этого устройства является то, что регистрируемая измерительная информация содержит зна чительную избыточность, что Ьгра.ничивает его функциональные возможности. Наиболее близким к изобретению является устройство для управления регистрацией информации, содержащее первьй блок памяти, соединенньй с первым счетчиком, распределитель импульсов, подключенньй к второму счетчику, к датчику сигналов числа накалов, соединенному с вторым счет чиком и с коммутатором, входы которого подключены к блоку сопряжения, а выгод соединен с первым регистром и с сумматором, другие входы которого подключены к первому блоку па(Мяти и распределителю импульсов, соединенному с генератором синхро-, сигналов, вторым блоком памяти, преобразователем кода и усилителями подключенными к преобразователю код .вход которого соединен с вторым бло ком памяти, первьй элемент И, соединенньй с сумматором и вторым регистром, выход которого подключен к второму элементу И и блоку сравнени соединенному с сумматором и распред 42 лителем импульсов, первьй элемент ИЛИ, соединенный с первым элементом задержки, и второй элемент задержки С2. Однако известное устройство характер.изуется недостаточно высокой надежностью. Цель изобретения - повышение надежности устройства. Поставленная цель достигается тем, что в устройство, содержа щее коммутатор, входы которого соединены с блоком сопряжения и датчиком сигналов числа каналов, подключенным к распределителю импульсов, а выходы с первым регистром и одним входом сумматора, другие входы которого подключены к первому блоку памяти и распределителю импульсов, а выходы соединены с одним входом первого элемента И и блоком сравнения, первьй счетчик, вход которого подключен к распределителю импульсов, а выход соединен с первым блоком памяти, второй счетчик, вход которого подключен к датчику сигналов числа каналов, а выход соединен с распределителем импульсов, подключенным к генератору синхросигналов, к одному входу усилителей и преобразователю кода, выход которого соединен с другим входом усилителей, выходы которых подключены .к перфоратору, соединенному с распределителем импульсов, второй регистр, одни входы которого соединены с первым блоком памяти и выходом первого элемента И, а выход подключен к одному входу второго элемента И и блоку сравнения соединенному с распределителем импульсов, второй блок памяти, подклгоченньй к преобразователю кода и распределителю импульсов, первьй элемент ИЛИ, выход которого соединен с первым элементом задержки, и второй элемент задержки, введены третий счетчик, одни входы которого соединены с блоком сравнения и первым блоком памяти, а выход подключен к одному входу первого элемента ИЛИ, другой вход которого соединен с выходом блока сравнения, вторрй элемент ИЛИ, один вход которого подключен к первому элементу задержкиJ соединенному с другими входами первого элемента И и третьего счетчика, другой - к блоку сравнения, а выход соединен с вторым элементом задержки, соединенным с другим входом второго элемента И, выход которого подключен к первому блоку памяти, третий элемент И, входы которого соединены с третьим счет чиком и вторым элементом задержки, а выход подключен к первому блоку памяти, четбертый элемент И, входы которого соединены с первым регистром и вторым элементом задержки, а выход подключен к первому блоку памяти, и группу элементов И, одни , входы которых соединены с выходом первого элемента ИЛИ, другие подключены к третьему счетчику, второму регистру и первому счетчику соответс венно, а в 1ходы соединены с вторым блоком памяти, На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 конкретное конструктивное выполнелие распределителя импульсов. Устройство содержит блок 1 сопряжения, коммутатор 2, первьш счетчик 3, первый блок 4 памяти, сумматор 5, первый регистр 6, первый элемент И 7 второй регистр 8, блок 9 сравнения, третий счетчик 10, первый 11 и второй 12 элементы ИЛИ, второй 13, третий 14 и четвертый 15 элементы И, первый 16 и второй 17 элементы эадержки, группу элементов И 18 - 20, второй блок 21 памяти, преобразователь 22 кода, усилители 23, генера тор 24 синхросигналов, датчик 25 сигналов числа каналов, второй счетчик 26 и распределитель 27 импул сов. На фиг. 1 также показан перфора тор 28 и обозначены входы 29 - 32 и выходы 33-40 распределителя импуль сов. Распределитель импульсов (фиг.2) содержит элементы ИЛИ 41 и 42, триггер 43, элементы И 44 и 45, регистр 46 сдвига и формирователи 47. Устройство работает следующим образом.. В начале работы в счетчике 26 устанавливается необходимое число измерений, а в датчике 25 - необходимое число регистрируемых каналов. При подаче сигнала Местный пуск распределитель 27 вырабатывает необходимые управляющие сигналы, поступающие на триггер 43 и через элемент ИЛИ 41 - на первый разряд регистра 46, устанавливая их в единичное положение, а остальные разряды регистра 46 устанавливаются в нулевое со тояние. Импульсы с выхода генератора 1 4 4 . 24 синхросигналов череэ вход 29 распределителя 27 и элемент И 44 поступают на вход регистра 46. Первым импульсом содержимое регистра 46 сдвигается на один разряд вправо и на выходе его первого разряда получается сигнал, который с выхода 33 распределителя 27 поступает на датчик 25. При этом на входе коммутатора 2 появляется сигнал, по которому через коммутатор 2 и блок 1 на вход устройства подключается выход первого цифрового измерительного прибора. Показания первого измерительного прибора заносятся в регистр 6 и подаются на вход сумматора 5. Затем второй импульс с выхода генератора 24, проходя через элемент И 44 сдвигает содержимое регистра 46 еще на один разряд вправо, и на выходе второго разряда регистра 46 получается сигнал, который с выхода 34 рас пределителя 27 записывает единицу в счетчик 3. Так как в начале работы устройства во всех адресах блока 4 находятся нули, то по сигналу от счетчика 3 из первого адреса блока 4 на сумматор 5, регистр 6 и счетчик 10 принимаются нули. Третий импульс с выхода генератора 24, проходя через элемент И 44, сдвигает содержимое регистра 46 еще на один разряд вправо и на выходе его третьего разряда получается сигнал, который с выхода 35 распределителя 27 поступает на вход сумматора 5, и на сумматоре 5 производится вычитание нуля из показания первого измерительного прибо Р этом содержимое сумматора 5 не изменяется. h С выхода сумматора 5 показание первого измерительного прибора подается на информационный вход блока 9. На другой информационный вход блока 9 поступает содержимое регистра 8 (в данном случае нуль). Четвертый импульс с выхода генератора 24 синхросигналов, проходя через элемент И 44, сдвигает содержимое регистра 46 еще на один разряд вправо, и на выходе его четвертого разряда получается сигнал, который устанавливает первый разряд этого регистра в единицу и с выхода 36 распределителя 27 поступает на управляющий вход блока 9. По этому сигналу в блоке 9 производится сравнение содержимого сумматора 5 и регистра 8, т.е анализируется показание первого измерительного прибора с нулевым кодом (содержимое регистра 8 в данном случае равно нулю). Во всех случаях когда содержимое сумматора 5 не отли чается от содерткймого регистра 8, на выходе блока 9 получается сигнал равенства. В тех случаях, когда содержимое сумматора 5 отличается от содержимого регистра 8, на вькоде блока 9 получается сигнал неравенства. Сигнал неравенства с выхода блока 9, проходя через элемент ИЛИ 11, открывает элементы И 18 - 20 и записывает в блок 21 со счетчика 10 и регистра 8 нули, а со счетчика 3 единицу т.е. код номера первого ци фового прибора. Этот же сигнал записи задерживаясь на элементе 16 задержки, записывает единицу в счет чик 10, открывает элемент И 7 и переписывает показание первого прибора с выхода сумматора 5 в регистр 8. Сигнал с выхода элемента 16 задержки, проходя через элемент ИЛИ 1 задерживается на элементе 17 задерж ки, открывает элементы И 13 - 15 и записывает показания первого цифро.вого прибора, поступающие с регистров 8 и 6, и единицу, поступающую С.О счетчика 10, в блок 4 памяти по первому адресу. Следующий импуль с выхода генератора 24 синхроимпуль сов, проходя через элемент И 44, сдвигает содержимое регистра 46 на один разряд вправо, и на выходе 33 распределителя 27 получается сиг нал, который поступает в датчик 25. При этом на входе коммутатора 6 появляется сигнал, по которому чере комйутатор 2 и блок 1 на вход уст:ройства подключается выход второго цифрового измерительного прибора. По окончании первого цикла преоб зования всех каналов на выходе датчика 25 появляется сигнал, по которому заносится единица в счетчик 26 после чего начинается второй цикл преобразования. Далее устройство работает аналогично описанному. Блок 21 памяти содержит несколько регистров для запоминания знака, значения, количества подряд идущих одинаковых разностей и номера канал элемент задержки и входную логику для каждого регистра. По сигналу с выхода элемента ИЛИ 11 информация о знаке, значении, количестве подряд идущих одинаковых разностей и номере канала принимается в соответствующие разряды первого регистра блока 21 памяти, а в контрольный разряд записывается единица. Таким образом, единичное состояние контрольного разряда соответствует наличию информации в дру- гих разрядах первого регистра блока 21. По сигналу с выхода 37 распределителя 27 содержимое первого регистра блока 21 параллельно переписывается во второй, а задержанный на элементе задержки сигнал обнуляет его, т.е. этим самым освобождается первый регистр для приема следующей информации. Второй сигнал с выхода 37 распределителя 27 аналогичным образом переписывает информацию с второго регистра на третий и т.д. Наконец информация о знаке, значении, количестве подряд идущих одинаковых разностей и номере канала поступает на выходной регистр блока 21 памяти. В течение всех циклов регистрации I на вход элемента И 45 распределителя 27 поступают с блока 21 сигналы р.наличии информации в этом блоке. При подаче на другой вход элемента И 45 сигнала от перфоратора 28 о готовности последнего к регистрации, очередной импульс с генератора 24 синхросигналов проходит через элемент И 45, и на выходе этого элемента появляется сигнал, который формирует на выходах формирователей 47 управляющие сигналы, подаваемые на входы блока 21 памяти, преобразователя 22 кодов, усилителей 23 и перфоратора 28. Преобразователь 22 кода по сигналам с выхода 38 распределителя 27 подает сформированные коды из блока 21 памяти через усилители 23 в перфоратор 28, пробивающий поочередно на перфоленте знаки и значения разностей соседних показаний цифровых приборов, количество подряд идущих одинаковых разностей и номера приборов. Если до поступления сигнала готовности от перфоратора 28 на выходе элемента ИЛИ 11 еще раз появляется сигнал, в первый регистр блока 21 заносится информация о знаке, значении, количестве

подряд идущих одинаковых разностей и номере прибора, и аналогично описанному происходит перепись этой информации в свободньА регистр, ближайший к выходному. Таким образом, блок 21 памяти осуществляет согласование частоты поступления информации о подряд идущих одинаковых разностях с частотой регистрации этой информации.

По окончании цикла регистрации данного числа каналов на выходе датчика 25 числа каналов появляется сигнал, по которому заносится единица в счетчик 26, после чего цикл регистрации повторяется до тех пор.

пока не произойдет столько циклов регистрации, столько задано счетчиком 26, который после отсчета заданно1о числа измерений подает сигнал

на вход 30 распределителя 27, который через элемент ИЛИ 42 устанавливает триггер 43 в нулевое состояние, и устройство выключается. Работа устройства прекращается также при подаче на вход элемента ИЛИ 42 сигнала Местный стоп.

Введение новых узлов и элементов, а также новых конструктивных связей позволило существенно повысить надежность устройства.

r

«S4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема информации | 1982 |

|

SU1104571A1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1691841A1 |

| Многоканальное устройство дляпЕРЕдАчи иНфОРМАции C дЕльТА- МОдуляциЕй | 1979 |

|

SU849271A1 |

| Устройство для диагностики заболеваний | 1981 |

|

SU999064A1 |

| Устройство для голосования | 1980 |

|

SU928383A1 |

| Вычислительная система "Антикон" для предотвращения столкновения судов | 1983 |

|

SU1136178A1 |

| Устройство для вычисления массы нефте-пРОдуКТОВ B РЕзЕРВуАРАХ | 1979 |

|

SU845159A1 |

| Устройство для селекции изображений объектов | 1989 |

|

SU1777651A3 |

| Устройство для обработки телемеханической информации | 1975 |

|

SU534780A1 |

| Устройство для преобразования изображений объектов | 1984 |

|

SU1234859A1 |

УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ИНФОРМАЦИИ, содержащее коммутатор, входы которого соединены с блоком сопряжения и датчиком сигналов числа каналов, подключенным к распределителю импульсов, а выходы - с первым регистром и одним входом сумматора, другие входы которого подключены к первому блоку памяти и распределителю импульсов, а выходы соединены с одним входом первого элемента И и блоком сравнения, первый счетчик, вход которого подключен к распределителю импульсов, а выход соединен с первым блоком памяти, второй счетчик, вход которого подключен к датчику сигналов числа каналов, а выход соединен с распределителем импульсов, подключенном к генератору синхросигналов, к одному входу усилителей и преобразователю кода, выход которого соединен с другим входом усилителей, выходы которых подключены к перфоратору, соединенному с распределителем импульсов, второй регистр, одни входы которого соединены с первым блоком памяти и выходом первого элемента И, а выход подключен к одному входу второго элемента И и блоку сравнения, соединенному с распределителем импульсов, второй блок памяти, подключенньй к преобразователю кода и распределителю импульсов, первьш элемент ИЛИ, выход которого соединен с первым элементом задержки, и второй элемент задержки, о т л и ч а ющ е е с я тем, что, с целью повышения надежности устройства, оно содержит третий счетчик, одни входы которого соединены с блоком сравнения и первым блоком памяти, а выход подключен к одному входу первого элемента ИЛИ, другой вход кото рого соединен с выходом блока (Л сравнения, второй элемент ИЛИ, один вход которого подключен к первому элeмeнтV задержки, соединенному с другими входами первого элемента И и третьего счетчика, другой - к блоку сравнения, а выход соединен с вторым элементом задержки, соединенньм с другим входом второго элемента И, выход ко.торого подключен ел к первому блоку памяти, третий о элемент И, входы которого соединены с третьим счетчиком и вторым 4 элементом задержки, а выход подключен к первому блоку памяти, четвертый элемент И, входы которого соединены с первьм регистром и вторым элементом задержки, а выход подключен к первому блоку памяти., и группу элементов И, одни входы которых соединены с выходом первого элемента ИЖ, другие подключены к третьему счетчику, второму регистру и пер.вому счетчику соответственно, а выходы соединены с вторым блоком памяти.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для регистрации информации | 1974 |

|

SU522508A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 3873769, кл | |||

| Способ получения кодеина | 1922 |

|

SU178A1 |

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

Авторы

Даты

1984-09-23—Публикация

1983-03-03—Подача