(54) МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ С ДЕЛЬТА-МОДУЛЯЩШЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для передачи сигналов приращений | 1982 |

|

SU1103276A1 |

| Устройство для сопряжения вычислительной машины с датчиками | 1982 |

|

SU1070540A1 |

| Многоканальное устройство для передачи информации с дельта-модуляцией | 1982 |

|

SU1166330A1 |

| Устройство для передачи и приема информации | 1982 |

|

SU1104571A1 |

| Многоканальный следящий преобразовательАНАлОг-КОд | 1979 |

|

SU836792A1 |

| Устройство для регистрации информации | 1983 |

|

SU1115074A1 |

| Многоканальный коррелятор | 1974 |

|

SU552613A1 |

| Устройство для голосования | 1980 |

|

SU928383A1 |

| Многоканальное устройство для регистрации сейсмических сигналов на магнитную ленту | 1980 |

|

SU989501A1 |

| Устройство для считывания графической информации | 1980 |

|

SU934511A1 |

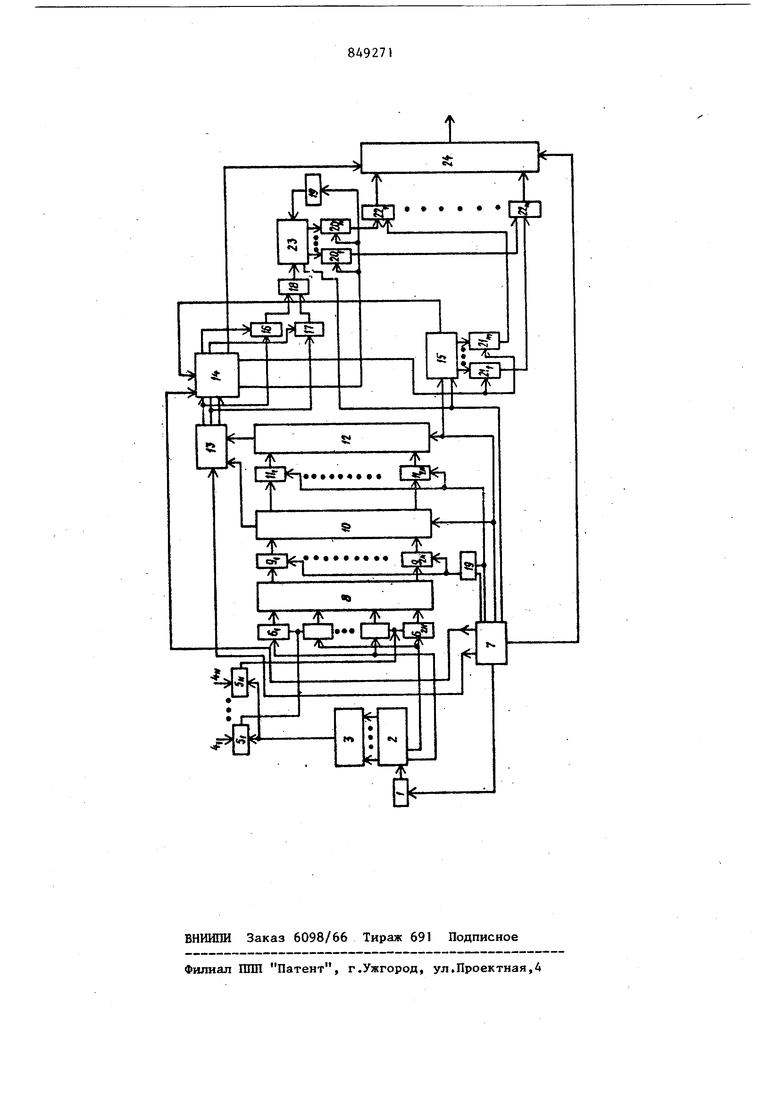

Изобретение относится к измерительной технике и технике связи и может использоваться в системах телеметрии, автоматизированных си-стемах коитроля и управления, фотографии и телевидении. Известно устройство для передачи сигналов с дельта-модуляцней, содер жащее вычитающий блок, выход которо го соединен с входом двоичного модулятора, подключенного через интегратор к первому входу вычитающего блока, и последовательно соединенные синхронизатор, делитель частоты и блок стробирования, первы . выход которого через соответствующи вентили подключен ко второму и трет му входам вычитающего блока и ко второму входу интегратора, при этом выход первого вентиля соединен с другим входом второго вентиля, а выход интегратора подключен к другому входу третьего вентиля 1 . Однако это устройство имеет узкий диапазон практического применения, так как не позволяет произвести сжатие и кодирование многоканальных сигналов . Известно многоканальное устройство для передачи информации с дель-. та-модуляцией,, содержащее в каждом из N каналов первый элемент И и второй элемент И, которых подключены ко входам элемента ИЛИ, и вычитающий элемент, выход которого подключен к одному из входов троичного модулятора, выход которого через интегратор подключен к одному из входов вычитающего элемента I а также общее для всех каналов блок памяти, синхронизатор, блок формирования адресов, сумматор и двоичный модулятор, выход которого подключен к первому входу сумматора, ко второму входу которого подключен первый выход блока формирования адресов, второй и третий выходы которого подключены к соответствукицим входам двоичного модулятора, причем второй выход блока формирования адресов подключен к первому входу первого эле мента И каждого из N каналов, второй выход которого и первый вход второго элемента И соединены с соответству ющим выходом блока памяти, ко входам которого подключены выходы троичных модуляторов соответствукяцих каналов, первый выход синхронизатора подключен к другому входу вычитакидего элемента из N каналов и к дополнительному входу блока памяти, второй выход синхронизатора подключен к другому входу троичного модулятора каладого из каналов и первому дополнительному входу блока фо1)мирования адресов, второй дополнительный вход которого соединен с третьим выходом синхронизатора, соединенным с другим входом второго элемента И каждого из N каналов 2. Однако в известном устройстве имеет место малая степень уплотнения информации. Наиболее близким по технической сущности к предлагаемому является многоканальное устройство для передачи информации с дельта-модуляцией, содержащее в каждом из N каналов первый элемент И н второй элемент И, выходы которых подключены ко входам элемента ИЛИ, и вычитаниций элемент, выход которого подключен к одному из входов троичного модулятора, выход которого через интегратор подключен к одному из входов вычитакщего элемента, а также общие для всех каналов блок памяти, синхронизатор, блок формирования адресов, сумматор и двоичный модулятор, выход которого подключен к первому входу сумматора, ко второму входу которого подключен первый выход блока формирования адресов, второй и третий выходы которого подключены к соответствующим входам дво ичного модулятора, причем второй выход блока формирования адресов подключен к первому входу первого элемента И каждого из N каналов, второй вход ко торого и первый вход второго элемента И соединены с соответствукицим выходом блока памяти, ко входам кото рого подключены выходы троичных модуляторрв соответствующих каналов, первый выход синхронизатора подключе к другому входу вычитающего элемен та каждого из N каналов и к дополнительному входу блока памяти, второй выход синхронизатора подключен к другому входу троичного модулятора каждого из N каналов и к первому дополнительному входу блока формирования адресов, второй дополнительный вход которого объединен с третьим выходом синхронизатора, соединенным с другим входом второго элемента И каждого из N каналов, кроме первого, введены последовательно соединенные элементы НЕТ, элемент НЕ и третий элемент И, а также введены обшсие для всех каналов последовательно соединенные регистр сдвига, .счетчик и блок формирования кода числа каналов, элемент задержки, дополнительный элемент НЕ и блок формирования маркера кадра, при этом в каждом из N каналов, кроме первого, один из входов элемента НЕТ и другой вход третьего элемента И подключены к выходу элемента ИЛИ, выход каждого из элементов НЕТ и выход элемента ИЛИ первого канала подключены к соответЬтвующим входам блока формирования адресов; другой вход элемента НЕТ каждого из N-1 каналов подключен к выходу элемента ИЛИ предьщущего канала, выходы третьих элементбв И каждого из N-1 каналов подключены к соответствующим взводам регистра сдвига, к дополнительному входу которого подключен четвертый выход синхронизатора, выход блока формирования кода числа каналов подключен к третьему входу сумматора, и к четвертому входу которого подключен первый выход синхронизатора через блок формирования маркера кадра, выход регистра сдвига через последовательно соединенные дополнительный элемент НЕ и элемент задержки подклю-чей ко второму входу счетчика, к третьему входу которого и ко входу синхронизатора подключен выход дополнительного элемента НЕ З. Однако известное устройство содержит в каядцом из N каналов троичный модулятор и интегратор, что значительно усложняет аппаратуру в це-, лом и после каждого шага требуется определенное время для уплотнения и передачи информации, что уменьшает частоту преобразования. Цель изобретения - упрощение устройства, повышение быстродействия и 58А927 улучшение технологичности изготовления, Поставленная цель достигается тем, что в многоканальное устройство для передачи информации с дельта-мо- дуляцией, содержащее элементы сравнения, первые входы которых подключены к N аналоговым входам устройства, блок памяти, выходал которого через соответствующие элементы И подключены к входам регистра сдвига, счетчик количества единиц в коде, блок формирования адресов и кодов числа, синхронизатор, выходы которого подключены к входам регистра сдвига, блока памяти, счетчика количества единиц в коде, блока формирования адресов и кодов числа введены счетчик отсчетов; преобразователь кода в напряжение, группы элементов И, дополнительный регистр сдвига, блок определения приращения, счетчик адресов, элементы И, элемент ИЛИ, элементы задержки, группа элементов ИЛИ, выходной блок, генератор импульсов,вы- ход которого подключен к счетчику отсчетов, первый выход которого подключей к входу преобразователя кода в напряжение, выход которого соединен со вторьми входами элементов срав- нения, выходы элементов сравнения подключены к соответствующим объединенным попарно первым входам элементов И первой группы 2 N элементов И, выходы которых подключены к блоку памяти, 2 N выходов которых подключены к блоку памяти, 2 N выходов которых подключенык соответствующим 2 N первым выходам второй группы элементов N выходы которых подключены к соответствующим входам регистра сдвига, первый выход которого подключен к блоку определения приращения, 2 N других выходов подключены к соответствуюицм 2 N первым входам элементов И третьей группы элементов И, выходы которых подключены к соответствующим входам дополнительного регистра сдвига, выход последнего подключен к второму „ входу блока определения приращений, первый, второй и третьий выходы которого соединены с первым , вторым и третьим входами блока формирования адресов и кодов числа, первый выход блока определения приращения соединен с первым входом первого элемента И, второй вход которого соединен с первым выходом блока форми16рования адресов и кодов числа, аторой выход которого соединен со вто второго элемента И, пер« ° которого со вторым выхоЯ блока определения приращений. выхода первого и второго э 1ементов И соединены с соответствующими входами элемента ИЛИ, выход которого сое динен с первым входом счетчика количестна единиц кода, m выходов которого подключены к соответствующим первым входам элементов И четвертой группы элементов-И, вторые входы которых объединены и соединены с третьим выходом блока формирования адресов и кодов числа и входов первого элемента задержки, выход которого подключен к второму входу счетчика количества единиц кода, выходы .элементов И четвертой группы элементов И подключены к соответствую Дим первым входам элементов ИЛИ группы m элементов ИЛИ, выходы которых подключены к выходному блоку, второй вход которого соединен с четвертьм выходом блока формирования адресов и кодов числа, соответствующие выходы синхронизатора подключены к входу генератора импульсов и к синхронизирующим входам блока определения приращений, блока формирования адресов и кодов числа, к объединенньм вторым входам элементов И третьей группы элементов И, через второй элемент задержки к объединенным вторым входам элементов И второй группы элементов «« выходному блоку, к второму вхоДУ регистра сдвига, к второму входу дополнительного регистра сдвига и к первому входу счетчика адресов, к третьему входу счетчика количества единиц кода, к второму входу счетчика адресов, первый выход счетчика адресов подключен к четвертому входу блока формирования адресов и кодов числа, другие m выходов подключены к соответствующим первьм входам элементов И пятой группы элементов И, объединенные вторые входы которых соедииены с пятым входом блока формирования адресов и кодов числа, а выходы соединены с соответствующими вторыми входами элементов ИЛИ группы элементов ИЛИ, втброй выход счетчика отсчетов соединен с объеда ненными вторыми входами четных элементов И первой группы элементов И, третий выход соединен с объединенными вторыми Bxoflahm нечетных элементов И первой группы элементов И. На чертеже представлена блок-схема предлагаемого устройства. Многоканальное устройство для передачи информации с дельта-модуляцией содержит генератор 1 импульсов, счетчик 2 отсчетов, преобразова тель 3 кода в напряжение-, аналоговые входы устройства о элементы 5v-5ig сравнения, элементы И ,, синхронизатор 7, блок 8 памяти, элементы И 9 -Элцт регистр 10 сдвига, элементы И -,2,}1,опол«кгепътай регистр.12 сдвига, блок 13 опрёделения приращения, блок 14 формирования адресов и кодов числа, счетчик 15 адресов, элементы И 16, 17, логический элемент 18, элемент 19 задерж ки, элементы И 20,-20(элементы И 21 -2 lyy, элементы ИЛИ 22 -22 счетчик 23 количества единиц в коде, выходной блок 24. Устройство работает следующим образом. В начале работы на выходе синхро низатора 7 формируется разрешающий уровень напряжения, который запускает генератор 1. Импульсы с генератора 1 поступаю на вход счетчика 2 отсчетов. С поступлением каждого из этих импульсов содержимое счетчика 2 уве личивается на единицу. В связи с этим на выходе преобразователя 3 кода в напряжение образуется линейно-ступенчатое напряжение, высота каждой ступеньки которого равна весу младшего разряда счетчика 2. С возрастанием содержимого счетчика 2 на элементах сравнения 5j-5j производится сравнение указанного ступен чатого напряжения со всеми входными аналоговь&ш сигналами, которые подаются через входные каналы (. момент равенства аналогового сигнала I-го входного канала со ступенчатым напряжением на выходе I-го эл мента 5 сравнения, вырабатывается сигнал. В этот момент содержимое сче чика 2 соответствует двоичному коду цифрового значения аналогового сигн ла {-го канала, и указанный импульс через группы входных вентилей 6/|-б осуществляют передачу содержимого двух младших разрядов счетчика 2 в те разряды блока 8 памяти, входы ко 18 -ого элеторых подключены к выходу ента сравнения. В результате ЭТОГО в соответствуиидих разрядах блока 8 памяти заполняется два младших разряда двоичного кода аналогового сигнала i-го канала 4i. До переполнения разрядной сетки счетчика 2 на выходах всех элементов 5;. -5 j сравнения в моменты равенства входных сигналов соответствующих каналов с линейно-ступенчатым напряжением вырабатываются сигналы, которые через соответствующие группы ключей 6i-б | осуществляют передачу содержимого двух младших разрядов счетчика 2 в соответствующие разряды блока 8 памяти. При одновременном совпадении двух или нескольких входных аналоговых сигналов со ступенчатым напряжением выходы элементов , сравнения этих каналов через соответствующие группы элементов 6 -б2 |осуществляют параллельную передачу содержимого младших, разрядов счетчиком 2 в соответствующие разряды блока 8 памяти. В момент переполнения разрядной сетки счетчика 2 завершается текущий шаг преобразования входных сигналов в цифровой код, и счетчик 2 сбрасьшается в нулевое состояние. После этого на выходе синхронизатора 7 получается сигнал, который через элементы 11 -11.осуществляет передачу содержимого регистра 10 сдвига в дополнительный регистр 12 сдвига. Затем очередной сигнал с другого выхода синхронизатора 7 через элементы 9 -92|,(Осуществляет параллельную передачу содержимого блока 8 памяти на регистр 10 сдвига. Таким образом, в соответствуияцих разрядах регистров lOjH. 2 сдвига запоминаются два младших разряда цифровых кодов данного и предыдущего шагов преобразования входных каналов. Причем коды 1-го канала располагаются в старших разрядах, а коды N-ro канала находятся в младших разрядах регистров 10 и 12. В начале каждого цикла преобразования сигналом от блока 14 формирования адресов и кодов числа устанавливается в исходное состояние счетчик 23 количества единиц в коде, а сигналом от синхронизатора 7 - счетчик

15 адресов. После этого начинается очередной цикл преобразования входных аналоговых сигналов, и параллельно с этим в блоке 13 определения приращений происходит определение значения и знака приращений предыдущего шага. При этом на вход блока 13 определения приращений поступают два младших разряда цифрового кода текущего и предыдущего шага 1-го канала, и этим самым, начиная с 1-го канала, в нарастающем порядке производится определение знака и значения приращений. После определения в блок 13 приращений знака и значения разности соседних ординат для 1-го канала синхронизатором 7 вырабатываются импульсы сдвига , по которым содержимое регистров 10 и 12 сдвигаются на два разряда. При этом на вход блока 13 определения приращений поступают два младших разряда цифрового кода текущего и предыдущего шага второго канала, и на выходе блока 14 формирования адресов и кодов числа формируетс знак разности второго канала. Далее аналогичным образом по импульсам от синхронизатора 7 сдвигаются содержи.мые регистров 10 и 12 по два разряда, и в блоке 13 определения приращений последовательно определяется знак разности остальных каналов. Таким образом, до окончания следующего цикла преобразования на выходе блока 13 определения приращений последовательно выдается знак разности

сигналов всех входных каналов Ai-Ai., , IN

В счетчик 15 адресов при каждом сдвиге содержимых регистров 10 и 12 поступает импульс, и его содержимое соответствует номеру каналов, для которого в блоке 13 определения приращений в данный момент определяется приращение. В устройстве передача полученных приращений в линии связи в каждом цикле разбита на два такта. В первом такте в линии связи передается количество подрядиду- щих положительных приращений и их адреса, а во втором такте передается количество подрядидущих отриц тельных приращений и их адреса. Приращения, равные нулю, в линии связи не передаются.

И момент появления первого приращения с положительным значением на первом выходе блока 13 определения появляется сигнал, который воздействует на 1-ый вход блока 14 формирователя адресов и кодов числа, и в результате на его 3-ем выходе вырабатывается сигнал, который через логические элементы И 2Ц-21у(,и элементы ИЛИ 22 -22уу, передается содержимое счетчика 15 адреса, представляющее собой адрес первого положительного приращения, в выходной блок 24. Одновременно с этим на первом выходе блока 14 формирования адресов и кодов числа вырабатывается сигнал, который через элементы И 16 и ИЛИ 18 обеспечивает прохождение положительных приращений на входе счетчика количества единиц в коде 23. Этот процесс продолжается до момента появления приращения, равного нулю, или отрицательного приращения. При этом если приращение имеет отрицат тельный знак, то на втором выходе блока 13 определения приращений вырабатывается сигнал, который воздествует на второй вход блока 14 формирования адресов и кодов числа, В результате на четвертом выходе блока 14 формирования адресов и кодов числа вырабатывается сигнал, который через логические элементы И и ИЛИ 22 -22yj, передает содержимое счетчика количества единиц 23 на выходной блок 24. Если на выходе блока 13 определения приращения появилось приращение, значение которого равно нулю, то на третьем выходе блока 13 определения приращения вырабатывается сигиал, который воздействует на третий вход блока 14 фомирования адресов и кодов числа.

В результате на четвертом выходе блока формирования адресов и кодов чсла появляется сигнал, который через элементы И и ШШ записывает содержимое счетчика количества единиц в коде счетчика 23 в выходной блок 24. Как видно передача в выходной блок 24 количества подрядидущих единиц производится в момент когда значение приращений очередного канала оказывается равным нулю или имеет отрицательное значение. После этого до момента появления приращения с положительным знаком в счетчик количества единиц в коде 23 сигналы не поступают, и на выходной блок 24 ничего не подается. В момент появления очередного положительного приращения сигнап с первого выхода блока 13 определения приращения опять воздействует на блок 14 формирования адресов и кодов числа, и на его третьем выходе вырабатьюается сигнал, который через элементы И 21(|21у и ИЛИ .у передает содержимое счетчика-15 на выходной блок 24 Начинав с этого момента, сигнал с первого выхода блока 13 определения приращен через элементы И 16 и ИЛИ 18 поступают на вход счетчика количества единиц в коде 23, где сно ва вышеуказанным образом определяется количество подрядидувщх единиц При появлении приращения с отрицател ным знаком или нуля опять аналогично вьтеуказанному содержимое счетчика количества единиц 23 передается на выходной блок 24, Таким образом, в период первого такта через выходной блок 24 в линии связи передаются адреса и количество всех подрядидущих положительных приращений. Коэффициент пересчета счетчика 15 адресов берется равньш количеству каналов. В связи с этим в конце пер вого такта количество импульсов, J посТупакмцих на вход счетчика 15 адресов, оказывается равным коэффициенту пересчета, на выходе счетчика 15 адресов появляется сигнал, которьй воздействует на четвертый вход блока 14 формирования адресов и кодов числа, и сигнал, полученный с его 5-го выхода, передается на выходной блок 24. Сигнал с выход ного блока 24 представляет собой код положительных приращений, переданных на линии связи в первом такт В результате в первом такте на лишш связи передаются начальные адре са положительных подрядидущих приращений и их количество. Во втором такте, как и в первом, по сигналам от синхронизатора 7 содержзлмое регистров 10 и 12 сдвига сдаигается на два разряда. Аналогично первому такту в счетчике 15 адресов при каждом сдвиге содержимых регистров 10 и 12 поступает юшульс, и его содержимое соот ветствует номеру канала, для которого на блоке 13 определения приращений в данный момент определяется приращение. В момент появления отрицательного приращения на втором выходе блока 1 3 определения приращений появля ется сигнал, который воздействует на второй вход блока 14 формирования адресов и кодов числа. При зтом на третьем выходе блока 14 вырабатывается сигнал, который через элементы И ,и ИЛИ 22( .передается содержимое счетчика 15 адресов на выходной блок 24. Одновременно с этим сигналы-со второго выхода блока 13 определения приращений через элементы И 17 и ИЛИ 18 поступают на вход счетчика 23 количества единиц в коде.Это продолжается до момента появления положительного приращения или приращения, равного нулю. При этом процесс суммирования единиц на счетчике 23 количества единиц в коде прекращается. При появлении очередного приращения с положительным знаком сигнал с первого выхода блока 13 определения приращений воздействует на блок V4 формирования адресов и кодов числа, и иа его четвертом выходе получается сигнал, который через элементы И 20-20 и ИЛИ 22-22 передает содержи мое счетчика 23 количества единиц в коде в выходной блок 24. Если очередное приращение имеет значение, равное нулю, то сигнал с третьего выхода блока 13 определения приращений действует иа блок 14 формирования адресов и кодов числа. Сигнал с его четвертого выхода через элементы И элементы ИЛИ передает содержимое счетчика количества единиц в коде 23 в выходной блок 24. Процесс передачи адресов и количества приращений с отрицательным знаком продолжается до истечения второго такта, в конце ;этого такта опять с выхода счетчика 15 получается сигнал, который воздействует на вход блока 14 формирования адресов и кодов числа, и на его шестом выходе вырабатывается сигнал, который представляет собой код отрицательных приращений, переданных на линии связи. Таким образом, в каждом текущем цикле работы устройства параллельно . с преобразованием и определением младших разрядов отсчетов всех входных сигналов данного шага также производится определение и передача в линии связи Количества и адресов подрядидущих приращений предьодущего шага. При этом по сравнению с известным устройством В два -раза повьштается быстродействие, и вместо N интегр торов и N троичных модуляторов используется всего один счетчик отсчетов и один преобразователь кода в напряжение. В связи с этим значитель но упрощается устройство и улучшается технологичность его изготовления. Формула изобретения Многоканальное устройства для пер дачи информации с дельта-модуляцией содержащее элементы сравнения, первые входы которых подключены к N аналоговым входам устройства, блок памяти, выходь: которого через соотв ствующие элементы И подключены к вхо дам регистра сдвига, счетчик количества единиц в коде, блок формиров ния адресов и кодов числа, синхрони тор, вьпсоды которого подключены к вх дам регистра сдвига, блока памяти, счетчика количества единиц в коде, блока формирования адресов и кодов числа, отличающееся тем что, с целью повьшения быстродейств и упрощения устройства в него введе ны счетчик отсчетов, преобразовател кода в напряжение, группы элементов дополнительный регистр сдвига, блок определения приращения, счетчик адр сов, элементы И, элементы ИЛИ, элементы задержки, группа элементов ИЛИ выходной блок, генератор импульсов, выход которого подключен к счетчику отсчетов, первый выход которого подключен к входу преобразователя кода в напряжение, выход которого соединен со вторыми входами элементов сравнения, выходы элементов сравнени подключены к соответствующим объединенным попарно первым входам элементов И первой группы 2 N элементов. И, выходы которых подключены к блоку памяти, 2 N выходов которых подключены к блоку памяти, 2 N выходов которых подключены к соответствующим 2 N первым выходам второй группы элементов И, выходы которых подключены к соответствующим входам регистра сдвига, первый выход которого подключен к блоку определения приращения, 2 N других выходов подключены к соответствующим 2 N первым входам элементов И третьей группы элементов И, выходы которых подключены к соответствующим входам дополнительного регистра сдвига, выход последнего подключен к второму входу блока определения приращений, первый, второй и третий выхоф которого соединены с первым, вторым и третьим входами блока формирования адресов и кодов числа, первый выход блока определения приращения соединен с первым входом первого элемента И, второй вход которого соединен с первьо4 выходом блока формирования адресов и кодов числа, второй выход которого соединен со вторым входом второго элемента И, первый вход которого соединен со вторым выходом блока определения приращений, выходы первого и второго элементов И сое динены с соответствующими входами элемента ИЛИ, выход которого соединен с первым входом счетчика количества единиц кода, m выходов которого подключены к соответствующим первым входам элементов И четвертой группы элементов И, вторые входы которых объединены и соединены с третьим выходом блока формирования адресов и кодов числа и входом первого элемента задержки, выход которого подключен к второму входу счетчика количества единиц кода, выходы элементов И четвертой группы элементов И подключены к соответствующим первым входам элементов ИЛИ группы m элементов ИЛИ, выходы ко - торых подключены к выходному блоку, второй вход которого соединен с четвертым выходом блока формирования адресов и кодов числа, соответству- ющие выходы синхронизатора подключены к входу генератора импульсов и к синхронизирующим входам блока определения приращений, блока формирования адресов и кодов числа, к объединенШ) вторым входам элементов И третьей группы элементов И, через второй элемент задержки к объединенным вторым входам элементов И второй группы-элеентов И, к выходному блоку, к второму входу регистра сдвига, к второму входу дополнительного регистра сдвига и к первому входу счетчика адре - ов, к третьему входу счетчика колиества единиц кода, к второму входу четчика адресов, первый выход счетика адресов подключен к четвертому ходу блока формирования адресов и одов числа, другие m выходов подключекы к соответствующим первым входам элементов И пятой группы: элементов И, объединенные вторые входы которых соединены с пятым входом блока формирования адресов и кодов числа, а выходы соединены с соответствующими вторыми входами элементов ИЛИ, группы элементов ИЛИ второй выход счетчика отсчетов соединен с объединенными вторыми входами четных элементов И первой групгад элементов И, третий выход соединен с объединенными вторыми входами нечетных элементов И первой группы элементов И.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-07-23—Публикация

1979-10-22—Подача