О).

о

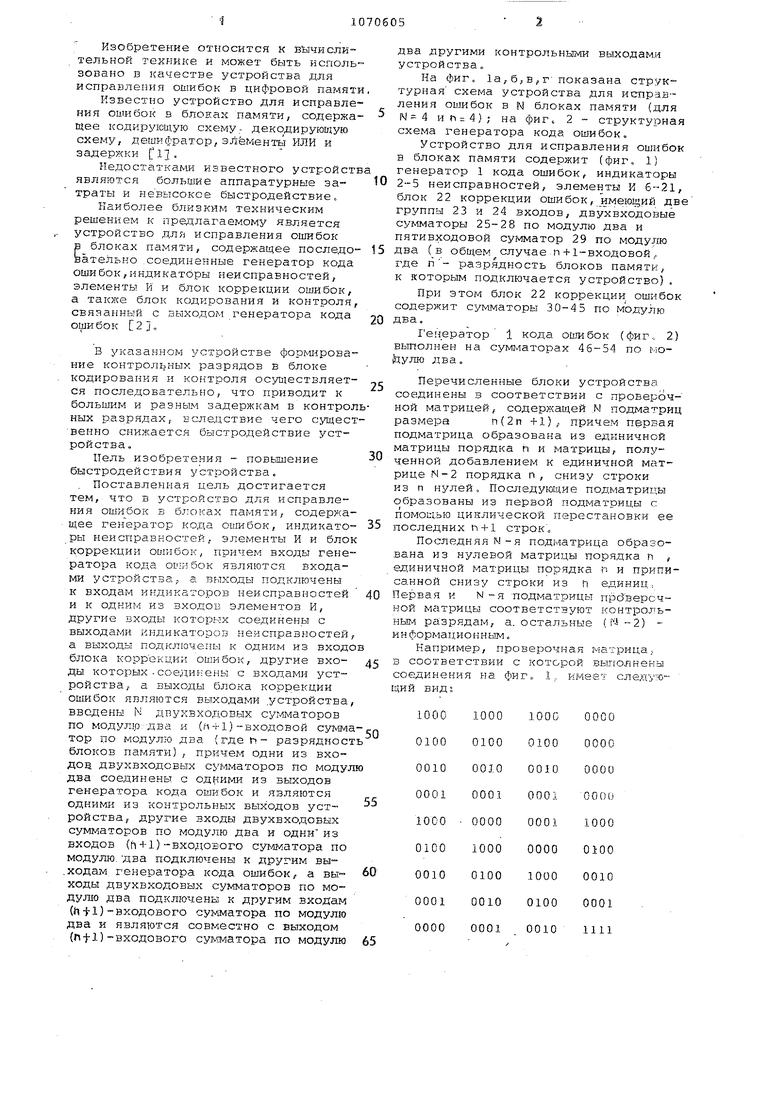

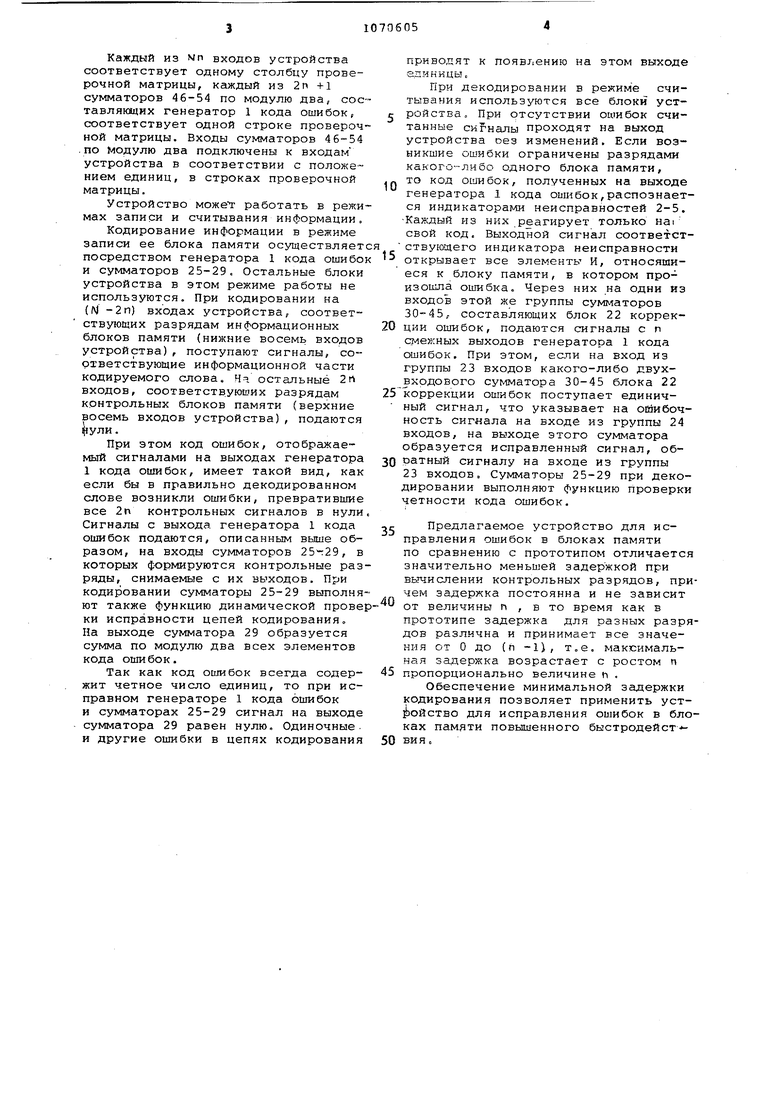

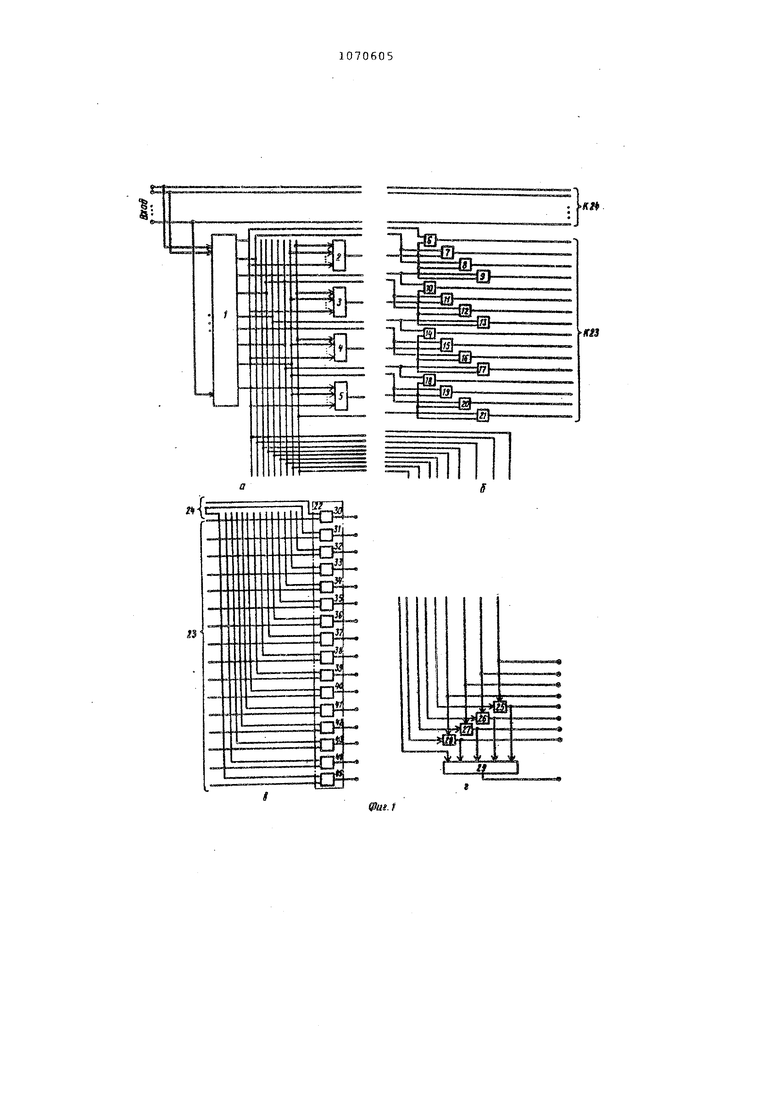

СП Изобретение относится к Вычислительной технике и может быть исполь зовано в качестве устройства для исправления ошибок в цифровой парлят Известно устройство для исправле ния ошибок в блоках памяти, содержа щее кодирующую схему- декодирующую схему, дешифратор,злёменты ИЛИ и задержки Ij. Недостатками известного устройст являются большие аппаратурные затраты и невысокое быстродействие с Наиболее близким техническим решением к предлагаемому является устройство для исправления ошибок в блоках памяти, содержащее последо вательно соединенные генератор кода ошибок,индикаторы нейснравностей, элементы И и блок коррекции ошибок, а также блок кодирования и контроля связанный с выходом генератора кода ошибок 2 J„ В указанном устройстве фop шpoвaние контрольных разрядов в блоке кодирования и контроля осуществляется последовательно, что приводит к большим и разным задержкам в контрол ных разрядах, вследствие чего сущест венно снилсается быстродействие устройства. Цель изобретения - повышение быстродействия устройства« Поставленная цель достигается тем, что в устройство для исправления ошибок в блоках памяти, содержащее генератор кода ошибок, индикаторы неисправностей, элементы И и блок коррекции ошибоз :, причем входы генератора кода oL i;6oK ЯБляготся входами устройства, а выходы подключены к входам индикаторов неисправностей и к одним из входов элементов И, другие входы которых соединены с выходами индикаторов неисправностей а выходы подгслючепы к одним из входо блока коррекции ошибок, другие входы которых . соединены с входами устройства, а выходы блока коррекции ошибок являются выходами .устройства введены N двухвходовых суг-вдаторов по модул IP два и (п + 1)-входовой сумма тор оо модулю два (где п разряднос блоков памяти), причем одни из входоц двухвходовых сумматоров по модул два соединены с одними из выходов генератора кода ошибок и являются одними из контрольных выходов устройства, другие входы двухвходовых сумматоров по модулю два и одни из входов {h+ 1)-входового сутлматора по модулю, два подключены к другим вы.ходам генератора кода ошибок, а выходы двухвходовых сумматоров по модулю два подключены к другим входам (hi 1)-входового сууматора по модулю два и являк тся совместно с выходом (nfl)-входового cyw iaxopa по модулю два другими контрольнь&ли выходам.и устройства о На фиг. 1а,б,в,г показана структурная схема устройства для исправления ошибок в N блоках памяти (для W- 4 и п 4); на фиг 2 - структурная схема генератора кода ошибок. Устройство для исправления ошибок в блоках памяти содержит (фиг. 1) генератор 1 кода ошибок, индикаторы 2-5 неисправностей, элементы И б-21, блок 22 коррекции ошибок, имеющий две группы 23 и 24 входов, двухвходовые сумматоры 25-28 по модулю два и пятивходовой сумматор 29 по модулю два (в общем случае n + 1-входовой,, где ii- разрядность блоков памяти, к которым подключается устройство). При этом блок 22 коррекции ошибок содержит сумматоры 30-45 по модулю два, Генератор 1 кода ошибок (фиг, 2) выполнен на сумматорах 46-54 по i4OЙулю два. Перечисленные блоки устройства соединены в соответствии с проверС1Чной матрицей, содержащей .N подматриц размера п(2п +1), причем первая подматрица образована из единичной матрицы порядка п и матрицы, полученной добавлением к единичной матрице М-2 порядка п, снизу строки из п нулей. Последующие подматрицы образованы из первой подматрицы с помощью циклической перестановки ее последних Г1+1 строк Последняяы-я подматрица образована из нулевой матрицы порядка п , единичной матрицы порядка п и приписанной снизу строки из п единиц, Первая и N-я -подматрицы п рбверсчной матрицы соответствуют контрольНЬ1М разрядам, а. остальные (i -2) информационным. Например, проверочная ма1-рни.а, в соответствии с которой выгголнены соединения на фиг. 1. имеет следу-вщий вид; 100С 1000 1000 ООСО 0100 0000 0100 0100 0010 0000 0010 0010 Каждый из Nn входов устройства соответствует одному столбцу проверочной матрицы, каждый из 2п +1 сумматоров 46-54 по модулю два, составляющих генератор 1 кода ошибок, соответствует одной строке проверочной матрицы. Входы сумматоров 46-54 .по модулю два подключены к входам устройства в соответствии с положением единиц, в строках проверочной матрицы. Устройство может работать в режи мах записи и считывания информации. Кодирование информации в режиме записи ее блока памяти осуществляет посредством генератора 1 кода ошибо и сумматоров 25-29. Остальные блоки устройства в этом режиме работы не используются. При кодировании на {W -2п) входах устройства, соответствующих разрядам информационных блоков памяти (нижние восемь входов устройства), поступают сигналы, соответствующие информационной части кодируемого слова. Н. остальные 2п входов, соответств.уюших разрядам контрольных блоков памяти (верхние восемь входов устройства), подаются ули. При этом код ошибок, отображаемый сигналами на выходах генератора 1 кода ошибок, имеет такой вид, как если бы в правильно декодированном слове возникли ошибки, превратившие все 2п контрольных сигналов в нули Сигналы с выхода генератора 1 кода ошибок подсцотся, описанным выше образом, на входы сумматоров 25-т29, в которых формируются контрольные раз ряды, снимаемые с их выходов. При кодировании сумматоры 25-29 выполня ют также функцию динамической прове ки исправности цепей кодирования На выходе сумматора 29 образуется сумма по модулю два всех элементов кода ошибок. Так как код ошибок всегда содержит четное число единиц, то при исправном генераторе 1 кода ошибок и сумматорах 25-29 сигнал на выходе сумматора 29 равен нулю. Одиночные. и другие ошибки в цепях кодирования приводят к появлению на этом выходе единицы. При декодировании в режиме считывания используются все блоки устройства. При отсутствии ошибок считанные сигналы проходят на выход устройства оез изменений. Если возникшие ошибки ограничены разрядами какого-либо одного блока памяти, то код ошибок, полученных на выходе генератора 1 кода ошибок,распознается индикаторами неисправностей 2-5. Каждый из них реагирует только Hai свой код. Выходной сигнал соответстствующего индикатора неисправности открывает все элементь И, относящиеся к блоку памяти, в котором произошла ошибка. Через них на одни из входов этой же группы сумматоров 30-45, составляющих блок 22 коррекции ошибок, подаются сигналы с п стиежных выходов генератора 1 кода ошибок. При этом, если на вход из группы 23 входов какого-либо двухвходового сумматора 30-45 блока 22 коррекции ошибок поступает единичный сигнал, что указывает на ойзибочность сигнала на входе из группы 24 входов, на выходе этого сумматора образуется исправленный сигнал, обратный сигналу на входе из группы 23 входов. Сумматоры 25-29 при декодировании выполняют функцию проверки четности кода ошибок. Предлагаемое устройство для исправления ошибок в блоках памяти по сравнению с прототипом отличается значительно меньшей задержкой при вычислении контрольных разрядов, причем задержка постоянна и не зависит от величины п , в то время как в прототипе задержка для разных разрядов различна и принимает все значения от О до {п -li, т.е. максимальная задержка возрастает с ростом п пропорционально величине п . Обеспечение минимальной задержки кодирования позволяет применить уст |зойство для исправления ошибок в блоках памяти повышенного быстродейстфиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и исправления ошибок | 1990 |

|

SU1785041A1 |

| Устройство для контроля блоков памяти | 1978 |

|

SU765883A1 |

| Устройство для исправления ошибок в блоке памяти | 1978 |

|

SU868841A1 |

| Устройство для обнаружения и исправления ошибок в блоках памяти | 1989 |

|

SU1649615A1 |

| Запоминающее устройство с исправлением ошибок | 1984 |

|

SU1226536A1 |

| Устройство для обнаружения и исправления ошибок в блоках памяти | 1988 |

|

SU1525746A1 |

| Устройство для исправления ошибок | 1986 |

|

SU1383509A1 |

| Запоминающее устройство с коррекцией однократных ошибок | 1982 |

|

SU1073799A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Устройство для исправления пакета ошибок длины два | 1988 |

|

SU1578812A1 |

УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК В БЛОКАХ ПАМЯТИ, содержащее генератор кода ошибок, индикаторы неисправностей, элементы И и блок коррекции ошибок, причем входы генератора кода ошибок являются входами устройства, а выходы подключены к входам индикаторов неисправностей и к одним из входов элементов И, другие входы которых соединены с выходами индикаторов неисправностей, а выходы подключены к одним из входов блока коррекции ошибок, другие входы которых соединены с входами устройства, а выходы блока коррекции ошибок являются выходами устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены ы двухвходовых суммато-ров по модулю Два и (Ь+1) -входовой сумматор по модулю два (где п - разрядность блоков памяти), причем одни из входов двухвходовых с тчматоров по модулю два соединены с одними из выходов генератора кода ошибок и являются одними из контрольных выходов устройства, другие, входы двухвходовых сумг аторов по модулю два и одни из входов (п+1)-входового Q Сумматора по модулю два подключены к другим выходам генератора кода ошибок, а выходы двухвходовых сумматоров по модулю два подключены к (| другим входам ( п + 1 гвходового сумма- тора по модулю два и являются сов- В местно с выходом ( п + 1)-входового сумматора по мод,лю два другими контрольньами выходами устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Обнаружение и исправление ошибок в дискретных устройствах | |||

| Под ред | |||

| В.С.Толстякова | |||

| М., Советское, радио, 1972, с.11 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля блоков памяти | 1978 |

|

SU765883A1 |

Авторы

Даты

1984-01-30—Публикация

1981-10-19—Подача