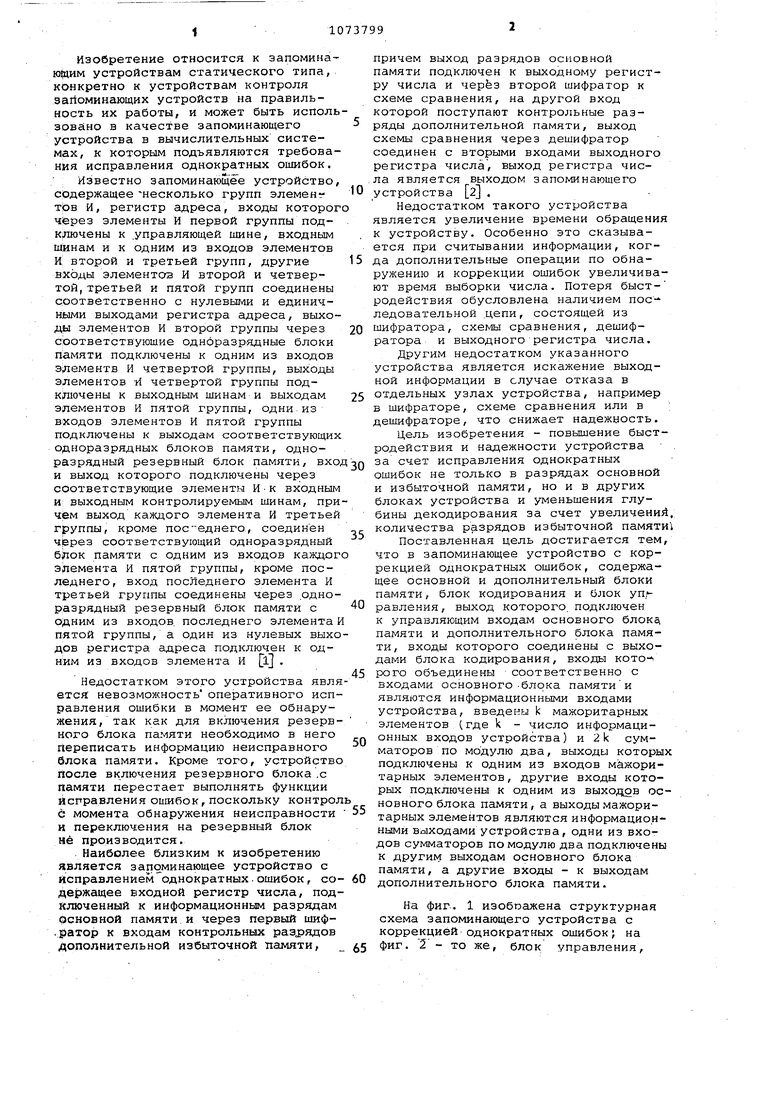

О5 Изобретение относится к запоминающим устройствам статического типа, конкретно к устройствам контроля зайоминающих устройств на правильность их работы, и может быть исполь зовано в качестве запоминающего устройства в вычислительных системах, к которым подъявляются требования исправления однократных ошибок. Известно запоминающё е устройство содержащее несколько групп элемент тов И, регистр адреса, входы которог через элементы И первой группы подключены к .управляющей шине, входным шинам и к одним из входов элементов И второй и третьей групп, другие входы элементов И второй и четвертой, третьей и пятой групп соединены соответственно с нулевыми и единичными выходами регистра адреса, выхо да элементов И второй группы через соответствующие одноразрядные блоки памяти подключены к одним из входов элемента И четвертой группы, выходы элементов -И четвертой группы подключены к выходным шинам и выходам элементов И пятой группы, одни из входов элементов И пятой группы подключены к выходам соответствующих одноразрядных блоков памяти, одноразрядный резервный блок памяти, вхо и выход которого подключены через соответствующие элементы Ик входным И; выходным контролируемым шинам, при чем выход каждого элемента И третьей группы, кроме пос еднего, соединен ч|ерез соответствующий одноразрядный 6JIOK памяти с одним из входов каждог элемента и пятой группы, кроме последнего, вход последнего элемента И третьей группы соединены через .одноразрядный резервный блок памяти с одним из входов, последнего элемента пятой группы, а один из нулевых выхо дов регистра адреса подключен к одним из входов элемента И l . Недостатком этого устройства явл ется невозможность оперативного исп равления ошибки в момент ее обнаружения, так как для включения резерв него блока памяти необходимо в него переписать информацию неисправного блока памяти. Кроме того, устройств после включения резервного блока .с памяти перестает выполнять функции Исправления ошибок,поскольку контро С момента обнаружения неисправности Н переключения на резервный блок не производится, . Наиболее близким к изобретению является запоминающее устройство с исправлением однократных.ошибок, со держащее входной регистр числа, под ключенный к информационным разрядам Основной памяти и через первый шиф.ратор к входам контрольных разрядов дополнительной избыточной памяти, причем выход разрядов основной памяти подключен к выходному регистру числа и через второй шифратор к схеме сравнения, на другой вход которой поступают контрольные разряды дополнительной памяти, выход схемы сравнения через дешифратор соединен с вторыми входами выходного регистра числа, выход регистра числа является выходом запоминающего устройства 2 . Недостатком такого устройства является увеличение времени обращения к устройству. Особенно это сказывается при считывании информации, когда дополнительные операции по обнаружению и коррекции ошибок увеличивают время выборки числа. Потеря быстродействия обусловлена наличием пос- ледовательной .цепи, состоящей из шифратора, схемы сравнения, дешифратора и выходного регистра числа. Другим недостатком указанного устройства является искажение выходной информации в случае отказа в отдельных узлах устройства, например в шифраторе, схеме сравнения или в дешифраторе, что снижает надежность. Цель изобретения - повышение быстродействия и надежности устройства за счет исправления однократных ошибок не только в разрядах основной и избыточной памяти, но и в других блоках устройства и уменьшения глубины декодирования за счет увеличений,; количества разрядов избыточной памяти Поставленная цель достигается тем, что в запоминающее устройство с коррекцией однократных ошибок, содержащее основной и дополнительный блоки памяти, блок кодирования и блок уп,-равления, выход которого, подключен к управляющим входам основного блока. памяти и дополнительного блока памяти , входы которого соединены с выходами блока кодирования, входы KOTO--I рого объединены соответственно с входами основного-блока памятии являются информационными входами устройства, введены k мажоритарных элементов (где k - число информацион}1ых входов устройства) и 2k сумматоров по модулю два, выходы которых подключены к одним из входов мажоритарных элементов, другие входы которых подключены к одним из выходов основного блока памяти, а выходы мажоритарных элементов являются информационными выходами устройства, одни из входов сумматоров по модулю два подключены к другим выходам основного блока памяти, а другие входы - к выходам дополнительного блока памяти. На фиг. 1 изображена структурная схема запоминающего устройства с коррекцией однократных ошибок; на фиг. 2 - то же, блок управления.

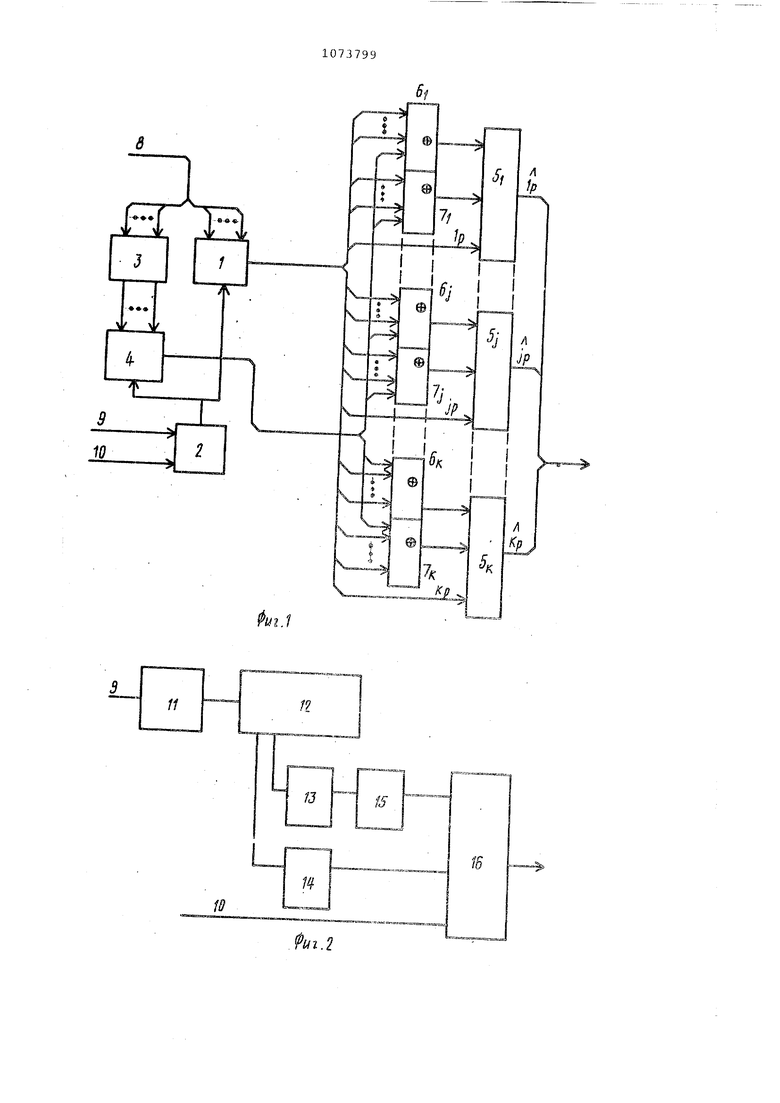

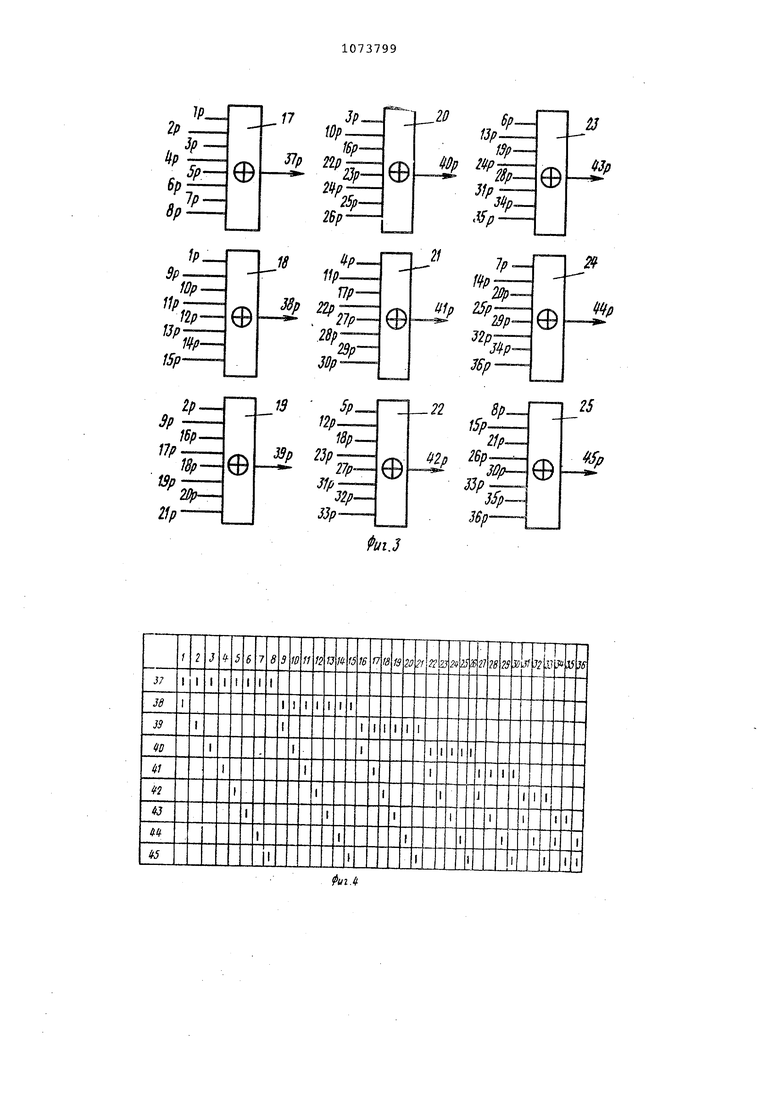

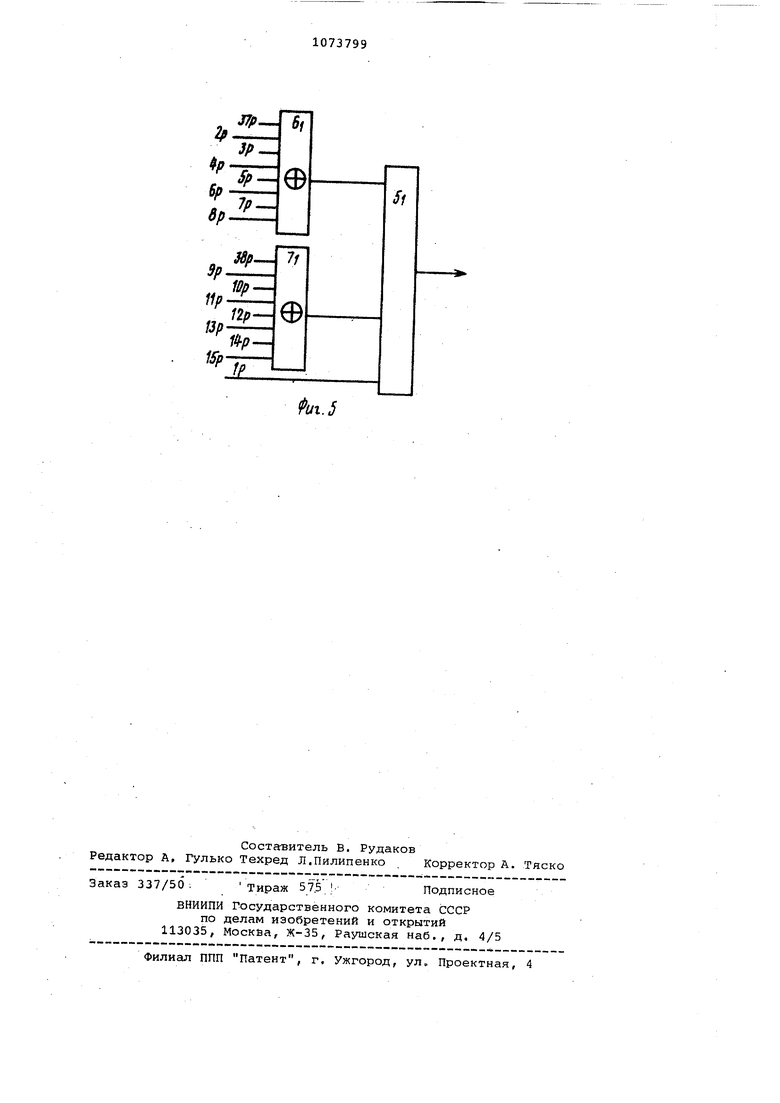

на фиг. 3 - то же,блок кодирования, например для корректирующего (45 и 36) - кода; на фиг. 4 - порождакидая (проверочная) Н - матрица соответственно для (45 и 36) - кода; на. фиг. 5 - соединение мажоритарного элемента и сумматоров по модулю два, соответствющее первому разряду устройства для (45 и 36J - кода.

Запоминающее устройство с коррекг ций однократных ошибок содержит .(фиг. 1) основной блок 1 памяти, бло 2 управления, блок 3 кодирования, дополйительный блок 4 памяти,k мажоритарных элементов 5 - 5ц и 2k сумматоров 6 6 и 7 k слухсащи для вычисления контрольных проверок. Устройство имеет информационные 8 и управляющие 9 и 10 входы.

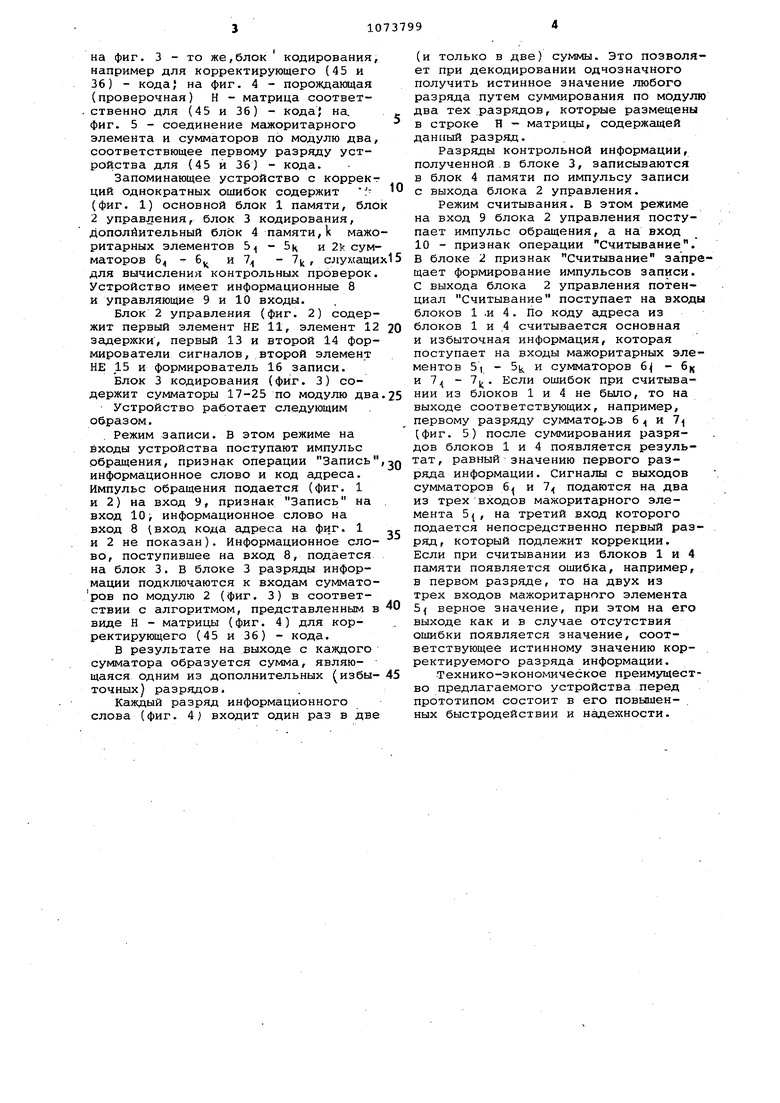

Блок 2 управления (фиг. 2) содержит первый элемент НЕ 11, элемент 12 задержки, первый 13 и второй 14 формирователи сигналов, второй элемент НЕ 15 и формирователь 16 записи.

Блок 3 кодирования (фиг. 3) содержит сумматоры 17-25 по модулю два

Устройство работает следующим образом.

, Режим записи. В этом режиме на входы устройства поступают импульс обращения, признак операции Запись информационное слово и код адреса. Импульс обращения подается (фиг. 1 и 2) на вход 9, признак Запись на вход 10 информационное слово на вход 8 (вход кода адреса на фиг. 1 и 2 не показан). Информационное слово, поступившее на вход 8, подается на блок 3. В блоке 3 разряды информации подключаются к входам сумматоров по модулю 2 (фиг. 3) в соответствии с алгоритмом, представленным в виде Н - матрицы (фиг. 4) для корректирующего (45 и 36) - кода.

В результате на выходе с каждого сумматора образуется сумма, являю- щаяся одним из дополнительных (избыточных) разрядов.

Каждый разряд информационного слова (фиг. 4; входит один раз в две

(и только в две) суммы. Это позволяет при декодировании однозначного получить истинное значение любого разряда путем суммирования по модул два тех разрядов, которые размещены в строке Н - матрицы, содержащей данный разряд.

Разряды контрольной информации, полученной.в блоке 3, записываются в блок 4 памяти по импульсу записи с выхода блока 2 управления.

Режим считывания. В этом режиме на вход 9 блока 2 управления поступает импульс обращения, а на вход 10 - признак операции Считывание. В блоке 2 признак Считывание запрщает формирование импульсов записи. С выхода блока 2 управления потенциал Считывание поступает на вход блоков 1 .и 4. По коду адреса из блоков 1 и .4 считывается основная и избыточная информация, которая поступает на входы мажоритарных элементов Б - Б,;, и сумматоров 6 - 6ц и l - 7j, . Если ошибок при считывании из блоков 1 и 4 не было, то на выходе соответствующих, например, первому разряду сумматоров 6 и 7.| (фиг. 5) после суммирования разрядов блоков 1 и 4 появляется результат, равный значению первого разряда информации . Сигналы с выходов сумматоров 6 и 7 подаются на два из трех входов мажоритарного элемента 5, на третий вход которого подается непосредственно первый разряд , который подлежит коррекции. Если при считывании из блоков 1 и 4 памяти появляется ошибка, например, в первом разряде, то на двух из трех входов мажоритарного элемента 5 верное значение, при этом на его выходе как и в случае отсутствия ошибки появляется значение, соответствующее истинному значению корректируемого разряда информации.

Технико-экономическое преимущество предлагаемого устройства перед прототипом состоит в его повышенных быстродействии и надехшости.

л ffl

Si

®

7/

iL

,

Sj

Л

JP

-J.

/™$

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с коррекцией однократных ошибок | 1983 |

|

SU1137540A2 |

| Запоминающее устройство с коррекцией однократных ошибок | 1987 |

|

SU1531174A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

| Устройство для дешифрации команд | 1987 |

|

SU1532932A1 |

| Запоминающее устройство с исправлением ошибок | 1989 |

|

SU1667156A1 |

| Устройство для кодирования | 1985 |

|

SU1287294A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1539844A1 |

| Резервированное оперативное запоминающее устройство | 1982 |

|

SU1137538A1 |

| Трехканальная резервированная микропроцессорная система | 1985 |

|

SU1378287A1 |

| Логическое запоминающее устройство | 1977 |

|

SU733024A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С КОРРЕКЦИЕЙ ОДНОКРАТНЫХ ОШИБОК, содержащее основной и дополнительный блоки памяти, блок кодирования и блок управления, выход которого подключен к управляющим входам основного блока памяти и дополнительного блока памяти, входы которого соединены с выходами блока кодирования, входы которого объединены соответственно с входами основного блока па- чти и являются информационными входами устройства, отличающееся тем, что, с целью повышения быстродействия и надежности устройства, в введены мажоритарных элементов (где k - число информационных входов устройства) и 2 k cyNTviaTopoB по модулю два, выходы которых подключены к одим из входов мажоритарных элементов , другие входы которых подключены к одним из выходов основного блока памяти, а выходы мажоритарных элементов являются информационными выходами устройства, одни из входов g сумматоров по модулю два подключены к другим выходам основного блока С/ памяти, а другие входы - к выходам дополнительного блока памяти.

v

X.™™fe

19

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающее устройство | 1978 |

|

SU781973A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Полупроводниковые запоминающие устройства и их применение | |||

| Под ред | |||

| .Гордонова | |||

| М | |||

| , Радио и связь, 1981, с | |||

| Обогреваемый отработавшими газами карбюратор для двигателей внутреннего горения | 1921 |

|

SU321A1 |

Авторы

Даты

1984-02-15—Публикация

1982-09-28—Подача