1

Изобретение относится к запоминающим устройствам.

Известно устройство для контроля блоков памяти, содержащее два контрольных блока памяти ji. Оно отличается низкой чадежностью работы.

Наиболее близким, техническим решениМ к изобретению является устройство для контроля блоков памяти, содержащее сумматоры по модулю два, индикаторы неисправностей, элементы И, двухвходовые сумматоры, причем входы сумматоров по модулю два подключены к входам устройства, а выходы - к соответствующим входам индикаторов неисправностей, выход каждого индикатора неисправностей соединен с управляющими входами соответствующих элементов И, другие входы которых подключены к выходам соответствующих сумматоров по модулю два, первый вход каждого двухвходоБого сумматора соединен с одним из входов устройства, а второй вход - с выходом одного из элементов И 12). Однако невозможность использований его для кодирования информации при записи ее в память и отсутствие средств динамической проверки исправности аппаратуры устройства снижает его надежность.

Целью изобретения является повышение надежности устройства и обеспечение кодирования информации при записи ее в память.

Достигается это тем, что устройство содержит трехвходовый сумматор и две группы последовательно соединенных двухвходовых сумматоров, причем выход каждого двухвходового сумматора, кроме последнего, сое10динен с первым входом последующего двухвходового сумматора, первые и вторые входы первых и вторые входы двухвходовых сумматоров обеих групп подключены к выходам сумматоров по модулю два, выходы последних двухвходовых сумматоров обеих групп

15 соединены соответственно с первым и вторым входами трехвходового сумматора, третий вход которого подключен к выходу одного из сумматоров по модулю два, первые вхо ды первых и выходы двухвходовых сумматоров групп и выходы трехвходового сумматора соединены с контрольными выходами устройства.

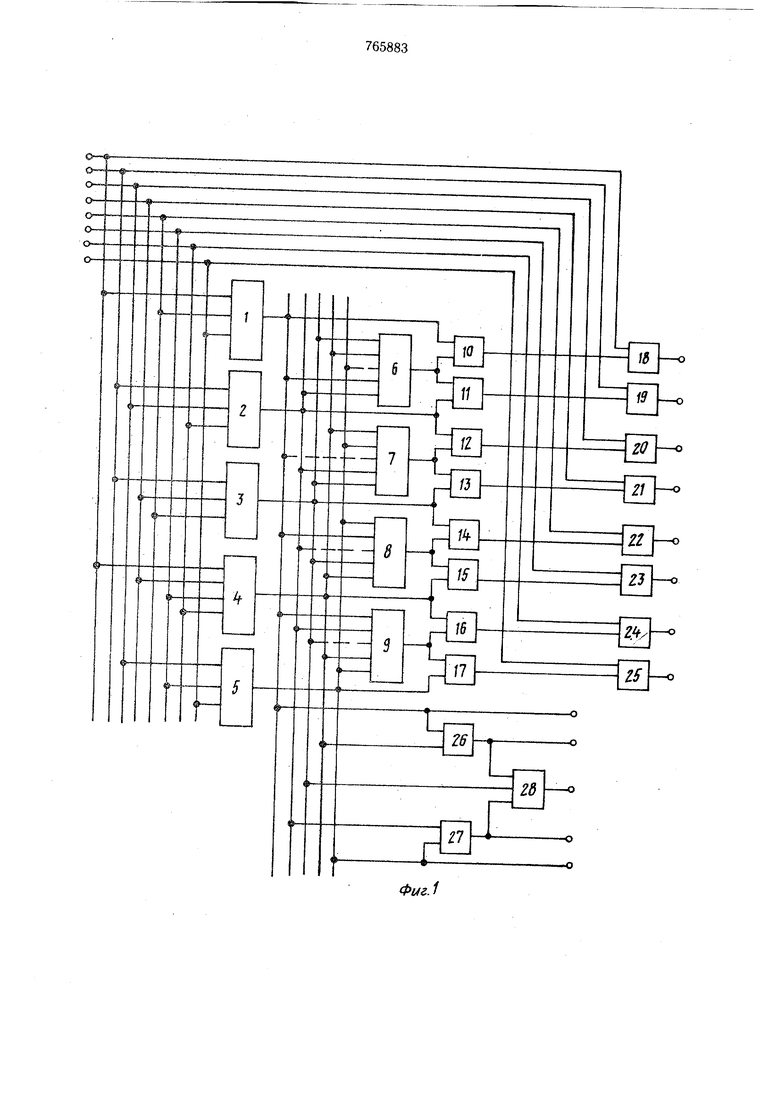

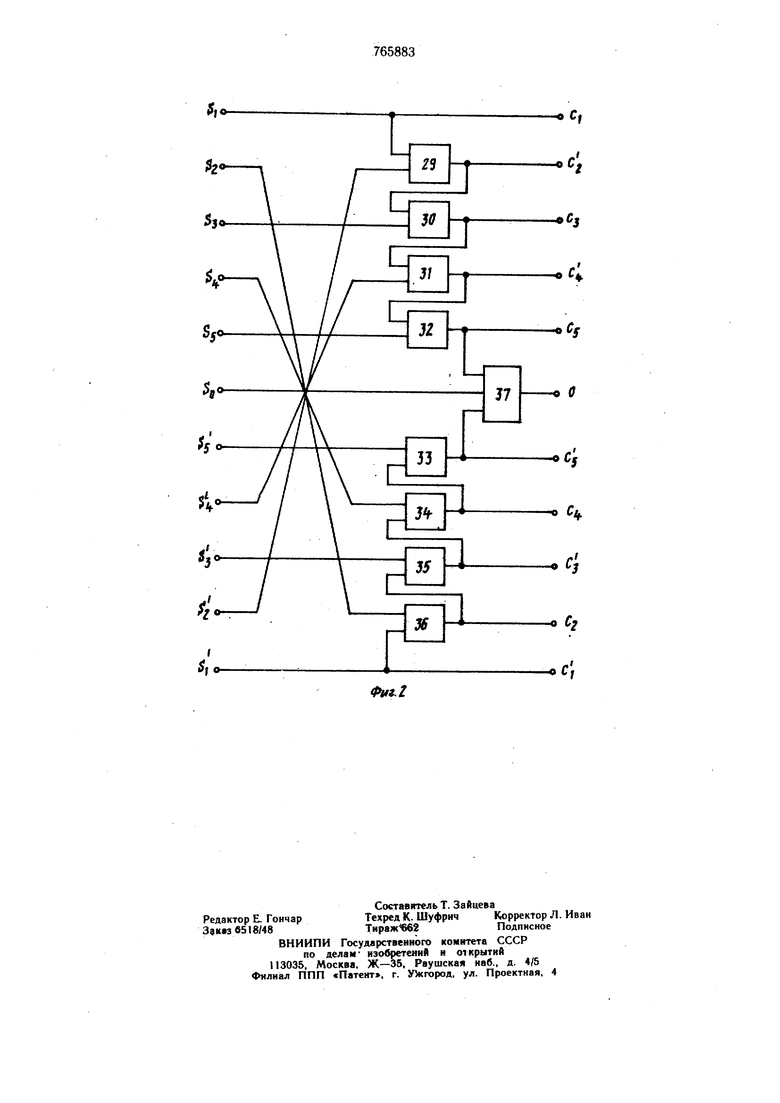

На фиг. 1 изображена блок-схема устройства, содержащая 4 двухразрядных блока

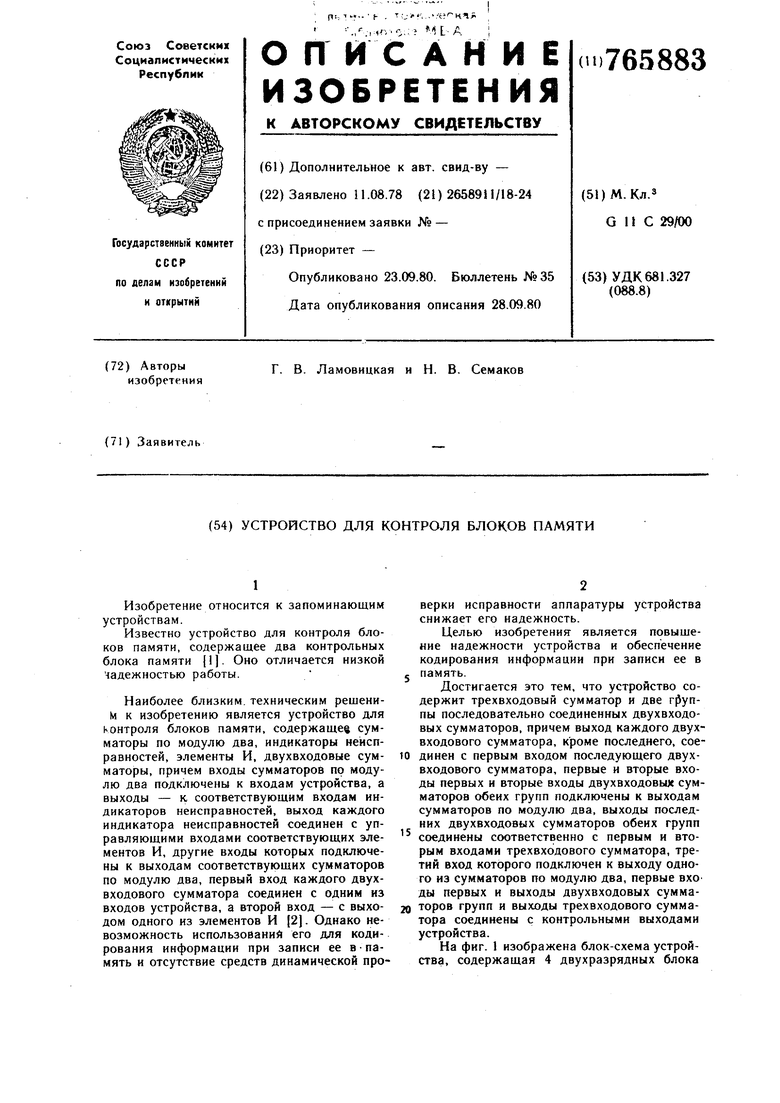

памяти; на фиг. 2 -- изображена схема соединения трехвходового сумматора и двух групп последовательно соединенных двухвходовых сумматоров с .выходами сумматоров по модулю два для разрядов блоког памяти b 5.

Устройство {см. фиг. 1) содержит сумматоры по модулю два 1-5, составляющие генератор кода ошибок, индикаторы неис правиостей 6-9 и элементы И 10-17, составляющие двухступенчатый преобразователь кода ошибок, двухвходовые сумматоры 18-25, составляющие блок коррекции ошибок, первую 26 и вторую 27 группы последовательно соединенных двухвходовых сумматоров и трехвходовый сумматор 28, составляющие блок кодирования и контроля.

Входы сумматоров по модулю два t-5 подключены к входам устройства, а выходы-х к соответствующим входам индикаторов ненсправностей . Выход каждого индикатора неиспра0но ;тей б-9 соединен с управляющимн входами соответствующих эл ментов И , другие входы которых подключены к выходам соответствующнх сумматоров по модулю два -5. Первый вход каждого двухвходового сумматора 18-25 соединен с одним из входов устройства, а второй вход - с выходом одного из элементов И 10-17. Выходы сумматоров 18-25 являются выходами устройства. Первые входы первых и вторые/ входы всех из двух групп 26 и 27 последовательно соединенных деухвходовых сумматоров подключены к выходам сумматоров по модулю два 1-5, выход каждого из последовательно соединенных двухвходовых сумматоров, кроме последне го, соединен с первым входом последующего двухвходового сумматора, а выходы последннх двухвходовых сумматоров 26, 27 соедннены соответственно с первым н вторым входами сумматора 28, третий вход которого подключен к выходу одного из сумматоров по модулю два -5. Первые входы первых и выходы двухвходовых сумматоров групп 26 и 27 и выход трехвходового сумматора 28 соединены с контрольными выходами устройства.

На фиг. 2 показаны последовательно соединенные двухвходовые сумматоры первой 29-32 и второй 33-36 групп н трехвходовый сумматор 37, составляющие блок кодирования н контроля, а также схема соединения этих сумматоров с выходами So, (Si- Ss), () сумматоров по модулю два, составляющих генератор кода ошибок, через So обозначен средний выход, а через (Si-Ss) и (St-55) - смежные выходы сумматоров по модулю два. Через (С i-С s) и (Cl-С 5) обозначены сигналы на контроль ных выходах устройства.

Устройство работает следующим образом.

Это устройство предназначено для исправления ошибок в N параллельных Ь-раз рядных блоках памяти (где N 2Ь -ь I Р

а Р - простое число). Генератор кода ошибок в общем случае содержит (2Ь + 1) сумматоров по модулю два 1-5 (см. фиг. 1), из которых N имеют по (N-1), а остальные по N входов. Первая степень преобразователя кода ошибок содержит N индикаторов неисправностей 6-9, а вторая ступень состоит из N групп По Ь-элементов И 10-17. Блок коррекции ошибок составлен из N групп по Ь-двухвходовых сумматоров 18-

25. Блок коднровання и контроля содержит

Ь-двухвходовых сумматора, составляющих две группы 26 и 27 по (Ь-1) последовательно соединенных двухвходовых сумматоров,. Блоки устройства соединены в соответствии с проверочной матрицей, N подматриц кото)эой образованы циклической перестановкой {2Ь -f 1) строк исходной подматрицы, составленной из двух перестановочных матриц порядка b с единицами на разных диагоналях и разряделяющей их строки из b нулей. Каждый из Nb входов устройства соот15етстаует одному столбцу проверочной матрицы, каждый из (2Ь -f 1) сумматоров по модулю два I-5, составляющих генератор кода ошибок, соответствует одной строке ттроверочной матрицы. Входы сумматоров по модулю два подключены к входам устройства в соответстветствии с положением единиц в строках проверочной матрицы. Входы каждой группы последовательно соединенных двухвходовых сумматоров 29-32, 33-36 (см. фиг. 2), отсчитываемые с первого входа первого сумматора группы, подключены к выходам сумматоров по модулю два с соответствующими порядковыми номерами, отсчитываемыми попеременно от начала одних и других смежных выходов по направлению к среднему выходу. Кодирование HtiJ формации в режиме записи ее в память осуществляется посредством генератора кода ошибок и блока кодирования н контроля. Остальные блоки устройства в этом режиме .работы не используются. При кодировании на (N - 2Ь) входов устройства, соответст® вующих разрядам информационных блоков памяти (нижние 4 входа устройства (см. фиг. I), поступают сигналы, соответствующие информационной части кодируемого слова. На остальные 2Ь входов, соответствующие разрядам контрольных блоков памяти (верхнне 4 входа устройства), подаются нули. При этом код ошибок, отображаемый сигналами на выходах генератора кода ошибок, имеет такой же вид, как если бы в правильно закодированном слове возникли

o ошибки, превратившие все 2Ь контрольных сигнала в нули. Сигналы с выхода генератора кода ошибок подаются описанным выше образом на входы блока кодирования и контроля и вычисленные их значения снима1отся с выходов последовательных днухвходовых сумматоров групп. При кодировании блок кодирования н контроля выполняет также функцию динамической проверки исправности цепей кодирования. На выходе

fpexBxo.aoBoro сумматора (28 на фиг. 1 и VJ на фиг.2) образуется сумма по модулю Цва всех элементов кода ошибок. Так как код ошибок всегда содержит четное число единиц, то при исправном генераторе кода ошибок и блоке кодирования и контроля сигнал на выходе трехвходового сумматора равен нулю. Одиночные и другие ошибки в цепях кодирования приводят к появлению на этом выходе единицы.

При декодировании в режиме считывания используются все блоки устройства. При отсутствии ошибок считанные сигналы проходят на выход устройства без изменений. Если возникшие ошибки ограничены разрядами какого-либо одного блока памяти, то код ошибок симметричен относительно центра, соответствующего нулевой строке проверочной подматрицы этого блока памяти. Положение центра симметрии кода ошибок, полученного на выходе генератора кода ошибок, распознается индикаторами неисправностей блоков памяти. Каждый из них реагирует только на «свой код, т. е. код с одним определенным положением центра симметрии. (Выходной сигнал индикатора неисправности блока памяти открывает все элементы И относящейся к этому блоку памяти группы. Через них на вторые входы этой же группы сумматоров, составляющих блок коррекции ошибок, подаются сигналы с b смежных выходов генератора кода ошибок, отсчитываемых от выхода, соответствующего центру кода ошибок. При этом, если на второй вход какого-либо двухвходового сумматора (18- 25) блока коррекции ошибок поступает единичный сигнал, что указывает на ошибочность сигнала на его первом входе, на выходе ЭТОГО сумматора образуется исправленный сигнал, обратный сигналу на первом Bxo де. Блок кодирования и контроля при декодировании выполняет функцию проверки четности кода ошибок.

Технико-экономическое преимущество описываемого устройства заключается в том, что применение в нем блока кодирования и контроля, содержащего 2Ь двухвходовых сумматора, позволяет совмещать выполнение-грех функций: вычисление контрольных сигналов, динамической проверки, исправное ти цепей кодирования информации при записи и динамической проверки, ксправиости генератора кода ошибок при считывании тогда как для раздельной реализации этих

трех функций требуется второе больше число сумматоров.

За счет сокращения числа сумматоров в предлагаемом устройстве существенно повышается его надежность при обеспечении наибольшего возможного при минимуме аппаратуры быстродействия кодирования.

Формула изобретения

Устройство для контроля блоков памяти, содержащее сумматоры по модулю два, индикаторы неисправностей, элементы И, двухвходовые сумматоры, причем входы сумматоров по модулю два подключены ко входам устройства, а выходы --- к соответствующим входам индикаторов неисправностей, выход каждого индикатора неисправностей соединен с управляющими входами соответствующих элементов И, другие входы которых подключены к выходам соответствующих Сумматоров по модулю два, первый вход каждого двухвходового сумматора соединен с одИим из входов устройства, а второй вход - с выходом одного из элементов И, отличающееся тем, что, с целью повышения надежности, оно содержит трехвходовой сумматор и две группы последовательно соединенных двухвходовых сумматоров, причем выход каждого двухвходового сумматора, кроме последиего, соединен с первым входом последующего двухвходового сумматора, первые и вторые входы первых и вторые входы последующих двухвходовых сумматоров обеих групп подключены к выходам сумматоров по модулю два, выходы последних двухвходовых сумматоров обеих групп соединены соответственно с первым и вторым входами трехвходового сумматора, третий вход которого подключен к в ыходу одного из сумматоров по модулю два, первые входы первых и выходы двухвходовых сумматоров групп и выход трехвходового сумматора соединены с контрольными выходами устройства.

Источники информации,

принятые во внимание при экспертизе

1.Bossen D. С., «b-A0jacent error correction 3BIKI Journal of Research and Development, 1970, 14, № 4, pp. 402-408.

2.Авторское свидетельство СССР по заявке № , кл. G II С 29/00, 15.05.78 {прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления ошибок в блоке памяти | 1978 |

|

SU868841A1 |

| Устройство для исправления ошибок в блоках памяти | 1981 |

|

SU1070605A1 |

| Устройство для обнаружения и исправления ошибок | 1990 |

|

SU1785041A1 |

| Устройство для исправления ошибок в блоках памяти | 1979 |

|

SU868842A1 |

| Устройство для определения местоположения ошибок в строке матричного накопителя | 1980 |

|

SU896691A1 |

| Устройство для обнаружения и исправления ошибок в блоках памяти | 1989 |

|

SU1649615A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с исправлением ошибок | 1984 |

|

SU1226536A1 |

| Генератор псевдослучайных кодов | 1983 |

|

SU1167710A1 |

| Устройство кодирования информации для оперативной памяти | 1983 |

|

SU1160474A1 |

Авторы

Даты

1980-09-23—Публикация

1978-08-11—Подача