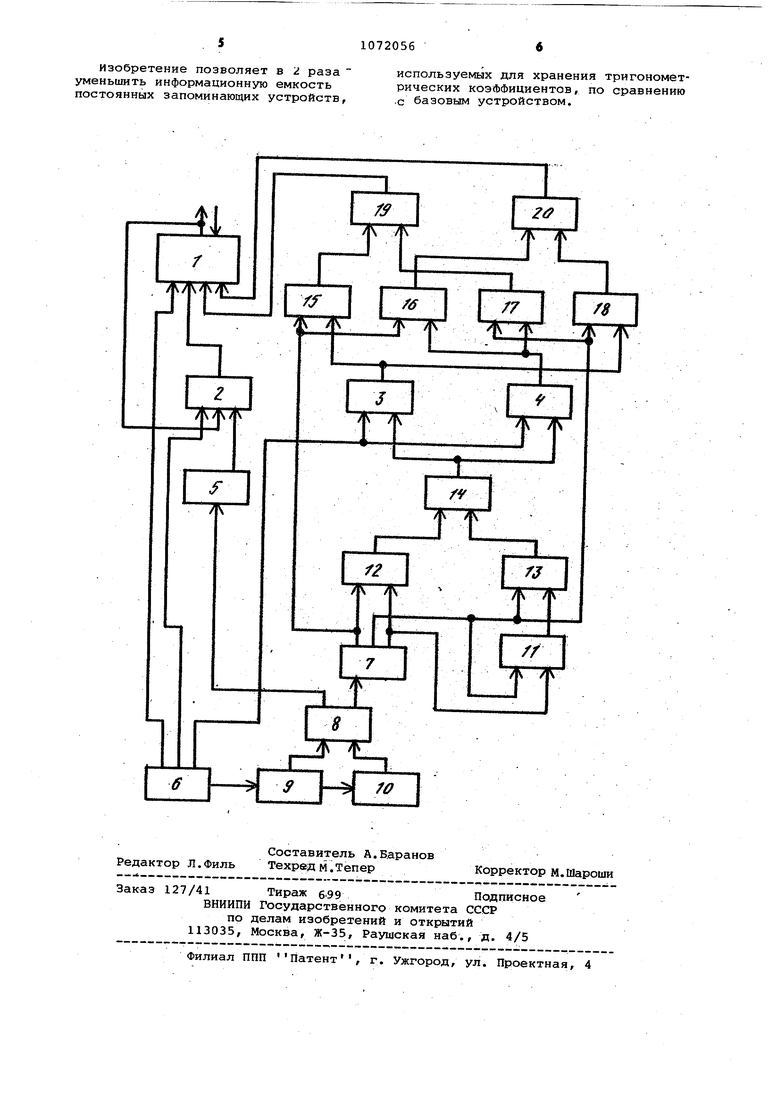

Изобретение относится к вычислительной технике и может быть использовано для решения задач спектрального анализа и цифровой фильтрации, Известны формирователи коэффициентов процессоров БПФ, состоящих из арифметического устройства, памяти для хранения входных данных промежуточных и конечных результато постоянных запоминающих устройств для хранения таблиц тригонометричес ких коэффициентов и устройства управления f . Недостатком блоков формирования коэффициентов является избыточная емкость постоянных запоминающих устройств. Наиболее близким к преддагаемому по технической сущности является блок БПФ, состоящий из арифметического устройства, оперативного запоминающего устройства, постоянных запоминающих устройств, регистра адреса и оперативного запоминающего устройства, регистра гьдреса постоянных запоминающих устройств, формирователя приращения адреса запоминающих устройств, счетчика циклов, счетчика итераций и устрцйства управления, Выходы оперативного Запоминающего устройства и постоянных запоми нающих устройств соединены с входами арифметического устройства, выход которого соединен с входсмл оперативного запоминающего устройства, выходы регистра адреса опера тивного запоминающего устройства и регистра адреса постоянных запоминающих устройств со.единены соответственно с входами оперативного запоминающего устройства и постоянных запоминающих устройстн., а входы регистров адреса соединены с выходами формирователя сигналов приращения регистров адреса запоминшо щих устройств, выходы счетчика циклов и счетчика итераций соединены с входами формирования сигнатлов приращения регистров адреса зййся-шнающих устройств, .вход ечетчи ка итераций соединен с-выходом сче циклов, выходы устройства управления соединены соответственно с входами арифметического устройст ва, оперативного и постоянных запо минающих устройств, формирователя сигналов приращения регистров адре са запоминающих УСТРОЙСТВ и счетчи ка циклов 2J . Недостаток известного устройства заключается в избыточной емкоети постоянных запоминающих устройст В этих устройствах хранятся табличн значения косинусов и., синусов в диа. . -jj пазоне значений углов О-( - -jj) с дискретизацией по углу, равной ( /ч- 2;7« Однако известно, что значения синусов и косинусов симметричны относительно угла ii /4. Поэтому в принципе в постоянных запоминающих устройствах достаточно хранить значения косинусов и синусов для значений углов в диапазоне 0-S/4,. т ,е, половину табличных значений, используемых в прототипе. Хранение полных таблиц приводит к двукратному увеличению емкости постоянных запоминающих устройств, Цель Изобретения - сокращение объема оборудова.ния, Поставленная цель достигается, темj что блок формирования тригонометрических коэффициентов для прог цессора дискретного преобразования Фурье, содержащий два узла, постоянной памяти, регистр адреса, формирователь приращений адреса, счетчик циклов и счетчик итерахий, информационный выход которого подключен к первому входу формирователя приращений адреса, выход которого подключен к информационному входу ре1истра адреса, тактовый вход счетчика итераций соединен с выходом последнего разряда счетчика циклов, информационный выход которого подключен к второму входу формирователя приращений адреса, причем тактовЕлй вход счетчика циклов является первым тактовЕзй входом блока, тактовые входы первого и второго узлов постоянной памяти объединены и являются вторым такTOBfcOd входом блока, содержит формирователь дополнительного кода, шесть эл« 1ентов И и три элемента ИЛИ, инверсный выход старшего разряда регистра адреса соединен с первьзми входами первого, второго и третьего элементов И, прямой выход старшего разряда дзегистра адреса подключен к первыкГ .входам четвертого, пятого и шестого элементов И и входу старшего разряда фор- миров ателя дополнительного кода, выход Которого подключен к второму входу четвертого элемента И, выход которого соединен с первым входом первого элемента ИЛИ, выход которого соединен с адресными входами первого и второго узлов постоянной памяти, информационный выход первого узла постоянной памяти подключен к вторым -. входам второго и шестого элементов И, выходы которых соединены с первыми (входами соответственно второго и третьего элементов ИЛИ, выходы которых являются выходами соответственно реальной и мнимой частей блока, информационный выход второго узла постоянной памяти соединен с вторыми входами третьего и пятого эле ментов И, выходы, которых подключены к вторым входам соответственно третьего и второго элементовчИЛИ, выход i -го (i ,№-) разряда регистра адреса подключен к входу д-го разряда формирователя дополнительного кода и .(«).-му входу первого элемента И, выход которого соединен с вторьш входом первого элемента ИЛИ. На чертеже изображен блок формирования тригонометрических коэффициентов для процессора дискретного преобразования Фурье, БЛОК содержит- арифметическое устройство 1, оперативное запоминающее устройство 2, узлы 3 и 4 по стоянной памяти, регистр 5 адреса оперативного запоминающего устройству гУстройство 6 управления, регистр 7 адреса, формирователь 8 пр ращения адреса, счетчик 9 циклов, счетчик 10 итераций, формирователь 11 дополнительного-кода, элементы И 12 и 13/ элемент, ИЛИ 14, элементы И 15-18 и элементы ИЛИ 19 и 20. В узлах 3 и 4 постоянной памяти хранятся значения тригонометрических коэффициентов coset+jsinflt для углов 0-if/4 с дискретизацией по X , равной 2it/N, причем в узле 3 храни ся реальная или косинусная состав-ляюшая упомянутых коэффициентов, а в узле 4 - мнимая составляющая. Об количество дискретных значений три гонометрических коэффициентов, а слё цоватеяьно, к информационная ил кость узлов 3 и 4 постоянной памяти, измеряемая в количестве адrf N ресЬву равна g + 1, т.е. фактическ в 2 раза меньше, чем в устройствепрототипе . Блок формирования тригонометрических йоэффицйентов работает следующим образом. Устройство б управления вырабатывает сигналы, переключающие счетчик 9 циклов и счетчик 10 итераций. В зависимости oi; кодов на выходе этих счетчиков в начале каж го цикла вычислений формирователь приращения адреса формирует адреса .обращения к оперативному запоминаю щему устройству и блокам пос/гоянно памяти и засылает их в регистр 7 а ,реса. Количество разрядов у регист ра 7 адреса в данном ycтpoйciвe такое же, как в прототипе, и равно ogoN/4, что обеспечивает присвоен углу с значений, изменяющихся в интервале О-(в/2-27/N). Вес старшего разряда регистра 7 адреса равен / и этот разряд в адресации узлов 3 и 4 непосредственно не участвует. Если угол х в регистре 7 адреса меньше li /4 (старший разряд регистра 7 адреса цаходится в состоянии О). то инверсный выход старшего разряда вшцеупомянутого регистра разрешает передачу содержимого остальных разрядов того же самого регистра к узлам 3 и 4 через элемент И 12 и элемент ИЛИ 14. Одновременно инверсный выход старшего разряда регистра 7 адреса разрешает передачу считанного из узла 3 значения cpsx, а из узла 4 - значения sink jj через элементы И 15 и 16 и элементы ИЛИ 19 и 20 в арифметическое устройство 1. Если же в регистре 7 адреса содержится угол (старший разряд вышеупомянутого регистра Находится в состоянии )/ то инверсный выход старшего разряда этого регистра приобретает значение О и отключает элемент И 12, запрещая тем самым передачу кода адреса из регистра 7 адреса к узлам 3 и 4. В то же .время прямой выход старшего разряда регистра 7 адреса приобретает значение и разрешает передачу через элемент И 13 и элемент ИЛИ 14 дополнительного кода адреса от формирователя 11 дополнительного кода к узлам 3 и 4. Одновременно происходит запрет передачи информации с выходов узлов 3 и 4 через элементы И 15, 16 и разрешение на передачу через элементы И 17 и 18. В этом случае значение cosxg будет поступать в арифметическое устройство 1 из. узла 4, в значение sinx из узла 3,при угле , из узла 4 - з1йх. Для любого угла X х %н/4 можно указать такой угол , сиьадетрйчный с xg ртносительНо , что будет выполняться равенство cosx2+jsirix inxa+icosx , угол X2 является дополнительным по отношению к углу х. Для нахождения требуемого значения тригонометрического коэффициента согласно приведенному выражению надо поменять местами реальную и мнимую-части, т,е. значение косинуса я синуса угла Хп: cosx..slnxi, jsinx- jcosxL. / . , . . Аппаратно это реализуется элементами И 15-18 и элементами КЛЯ 19 и 20, ос}пцествляющими коммутацию. ВЁИХОДОВ узлов 3 и 4 при передаче тригонометрического коэффициента и арифметическое устройство 1, управляемую старшим разрядом регистра 7 адреса. В арифметйче(ком устройстве 1 осуществляется умножение комплексного тригонсинётрического коэффициента, поступившего из узлов 3 и 4 на один из двух комплексных отсчетов, выбранных иа оперативного , запоминаяяцего устройства 2.

Изобретение позволяет в раза уменьшить информационную емкость постоянных запоминающих устройств,

используемых для хранения тригонометрических коэффициентов, по сравнению .с базовым устройством.

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1247891A1 |

| Процессор быстрого преобразования Фурье | 1986 |

|

SU1388892A1 |

| Устройство для формирования адресов операндов процессора быстрого преобразования Фурье | 1982 |

|

SU1056207A1 |

| Процессор быстрого преобразования фурье | 1979 |

|

SU788114A1 |

| Процессор быстрого преобразования Фурье | 1983 |

|

SU1119027A1 |

| Устройство для реализации двумерного быстрого преобразования фурье | 1983 |

|

SU1142845A1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

| Устройство для реализации двухмерного быстрого преобразования Фурье | 1982 |

|

SU1164730A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

БЛОК ФОРМИРОВАНИЯ ТРИГОНОМЕТРИЧЕСКИХ КйЭФФИЦИ БНТОВ ДЛЯ ПРОЦЕССОРА .ЦИСКРЕТНрГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ, содержащий два узла постоянной памяти, регистр аот)еса, формирователь приращений адреса, счетчик циклов и счетчик итераций, информационный выход которого подключен к первому входу формирователя при эащенйй адреса, выход которого подключен к информационному входу регистра адреса, тактовый вход счетчика итераций соединен с выходом последнего разряда счетчика Ц1рслов, информационный выход которого подключен к второму входу формирователя приращений адреса, причем тактовый вход счетчика циклов, является первым тактовым входом блока, тактовые входы первого и второго узлов постоянной памяти объединены и являются вторым тактрвБГМ входом блока, отличающийс я тем, что, с целью сокращения , объеила оборудования, он содержит формирователь дополнительного кода, шесть элементов И и три элемента ИЛИ, инверсный выход старшего разряда регистра адреса соединен с первыми-йходами первого, второго и третьего элементов И, прямой выход старшего разряда регистра адреса подключен к первым входам четвертого, пятого и шестого элементов И и входу старшего разряда Формирователя дополнительного кода, выход которого подключен к второму входу четвертого элемента И, выход которого соединен с первьзм входом первого элемента ИЛИ, выход котог. рргр соединен с адресными входами, первого и второго узлов постоянной памяти, информационный выход первого узла постоянной памяти подключен к вторым входам второго и шестого элементов И, выходы кото рых соединены с первыми входами соответственно второго и третьего элементов ИЛИ, выходы которых яв.ляются выходами соответственно реальной и мнимой частей блока, ин;формационный выход второго уэла по сТоянной памяти соединен с вт.ооыми входами третьего и пятого элементов И, выходы которых подключены к вторым входам соответственно третьего и второго элементов ИЛИ, выход -го (i l,m-l) разряда регистра адреса подключен к входу i-го разряда формирователя Дополг ительного кода и

7WIV7V

f

1

П

/

/7

/

A 7V

/

1

/Л /

/

Jt

/J

7

V

J

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Рабинер Л., Гоулд Б | |||

| Теория и применение цифровой обработки сигналов | |||

| М., Мир, 1978 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Клан Р | |||

| Специализированный процессор для быстрого решения за,дач гармонического анализа | |||

| Электроника, 1968, т.41, № 13 (ПРОТОТИП). | |||

Авторы

Даты

1984-02-07—Публикация

1982-09-16—Подача