подключен к выходу триггера, входы установки в 1 и О которого соединены с выходами старших разрядов соответственно второго и третьего счетчиков, выход генератора тактовых импульсов подключен к тактовому вход второго делителя частоты, четвертому входу элемента И,старшие разряды управляющего входа второго коммутатора объединены с входом разрешения записи четвертого счетчика, с младшими разрядами управляющего входа второго коммутатора и тактовым входом пятого счетчика, информационный выход которого подключен к первому входу второго узла сравнения, первьй выход которого соединен с адресным входом второго блока памяти, тактовый вход четвертого счетчика объединен с тактовьм входом шестого счетчика, информационный выход которого объединен с третьим выходом узла формирования управляющих импульсов, выходом первого узла сравнения и подключен к входу синхронизации второго арифметического блока,выход второго коммутатора подключен к информационному входу регистра,информационный выход которого соединен с первым входом умножителя, вторым входом первого узла сравнения и информационным входом четвертого счетчика, первый вход второго коммутатора подключен к выходу умножителя, второй вход которого объединен с вторым входом второго коммутатора, вторым входом второго узла сравнения, управляющими входами первого и второго делител1ей частоты и является входом задания параметров устройства, тактовый вход пятого счетчика объединен с установочным входом шестого счетчика и соединен с выходом окончания вычислений второго арифметического блока, выход генератора тактовых импульсов объединен с выходом элемента И, выходом триггера и подключен к входу синхронизации процессора быстрого преобразования Фурье, причем узел формирования управл;1ющих импульсов содержит два элемента И, элемент НЕ, элемент ИЛИ, две дифференцирующие цепочки, формирователь импульсов и триггер, выход которого соединен с первым входом формирователя импульсов и установочным входом четвертого

счетчика, второй вход формирователя импульсов соединен с первым выходом второго узла сравнения, первый выход формирователя импульсов- с первым входом первого элемента И, выход которого объединен с информационным выходом четвертого счетчика

и подключен к управляющему входу второго блока памяти и первому входу первого узла сравнения, вход установки в О триггера соединен с выходом окончания вычислений процессора быстрого преобразования Фурье, вход установки в триггера объединен с входом первой дифференцирующей цепочки, третьим входом формирователя импульсов, вторым входом первого элемента И, установочным входом пятого счетчика и соединен с вторым выходом второго узла сравнения, первый и второй входы второго элемента И соединены соответственно с выходом первого угл-а сравнения и выходом окончания вычислений второго арифметического блока, выход второго элемента И соединен с тактовым входом четвертого счетчика, выход эле- мента ИЛИ - с входом разрешения записи четвертого счетчика, первый вход элемента ИЛИ - с выходом элемента НЕ, вход которого подключен

к выходу первой дифференцирующей цепочки, второй вход элемента ИЛИ соединен с выходом второй дифференцирующей цепочки,вход которой соединен с выходом генератора тактовых импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор быстрого преобразования Фурье | 1987 |

|

SU1425709A1 |

| Устройство для реализации двухмерного быстрого преобразования Фурье | 1982 |

|

SU1164730A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1989 |

|

SU1697086A1 |

| Процессор для быстрого преобразования Фурье | 1989 |

|

SU1633426A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Устройство управления для процессора быстрого преобразования Фурье | 1984 |

|

SU1270775A1 |

| Устройство для формирования адресов операндов процессора быстрого преобразования Фурье | 1982 |

|

SU1056207A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

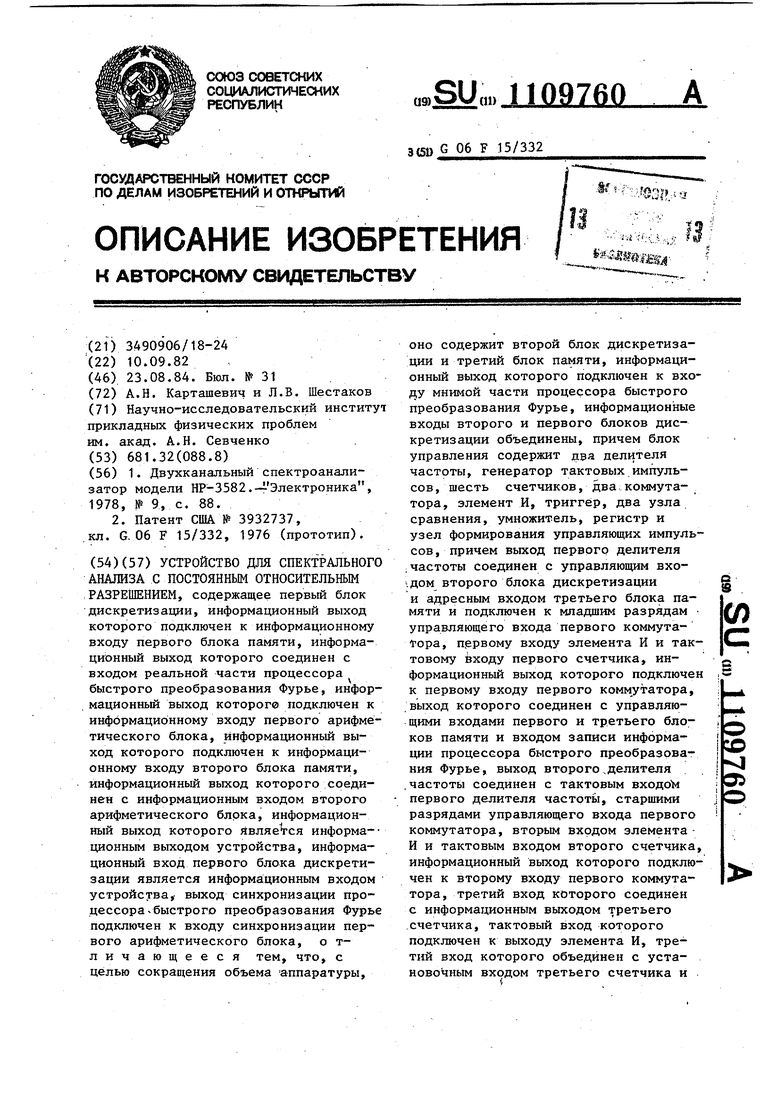

УСТРОЙСТВО ДЛЯ СПЕКТРАЛЬНОГО АНАЛИЗА С ПОСТОЯННЬМ ОТНОСИТЕЛЬНЫМ .РАЗРЕШЕНИЕМ, содержащее первый блок дискретизации, информационный выход которого подключен к информационному входу первого блока памяти, информационный выход которого соединен с входом реальной части процессора быстрого преобразования Фурье, информационный выход которого подключен к информационному входу первого арифметического блока, информационный выход которого подключен к информационному входу второго блока памяти, информационный выход которого соединен с информационным входом второго арифметического блока, информационный выход которого являемся информа-ционным выходом устройства, информационный вход первого блока дискретизации является информационным входом устройства, выход синхронизации процессора быстрого преобразования Фурье подключен к входу синхронизации первого арифметического блока, о тличающееся тем, что, с целью сокращения объема аппаратуры. оно содержит второй блок дискретизации и третий блок памяти, информационный выход которого подключен к вхоцу мнимой части процессора быстрого преобразования Фурье, информационные входы второго и первого блоков дискретизации объединены, причем блок управления содержит два делителя частоты, генератор тактовых импульсов , шесть счетчиков, ;а;ва коммутатора, элемент И, триггер, два узла сравнения, умножитель, регистр и узел формирования управляющих импульсов , причем выход первого делителя ;частоты соединен с управляющим вхо.дом второго блока дискретизации и адресным входом третьего блока па(/} мяти и подключен к младшим разрядам управляющего входа первого коммутаС тора, пэрвому входу элемента И и тактовому входу первого счетчика, информационный выход которого подключен к первому входу первого коммутатора, выход которого соединен с управляющими входами первого и третьего блоков памяти и входом записи информа;о ции процессора быстрого преобразования Фурье, выход второго,делителя 05 . частоты соединен с тактовым входом первого делителя частоты, старшими разрядами управляющего входа первого коммутатора, вторым входом элемента И и тактовым входом второго счетчика, информационный выход которого подключен к второму входу первого коммутатора, третий вход которого соединен с информационным выходом третьего счетчика, тактовый вход которого подключен к выходу элемента И, третий вход которого объединен с установочным входом третьего счетчика и

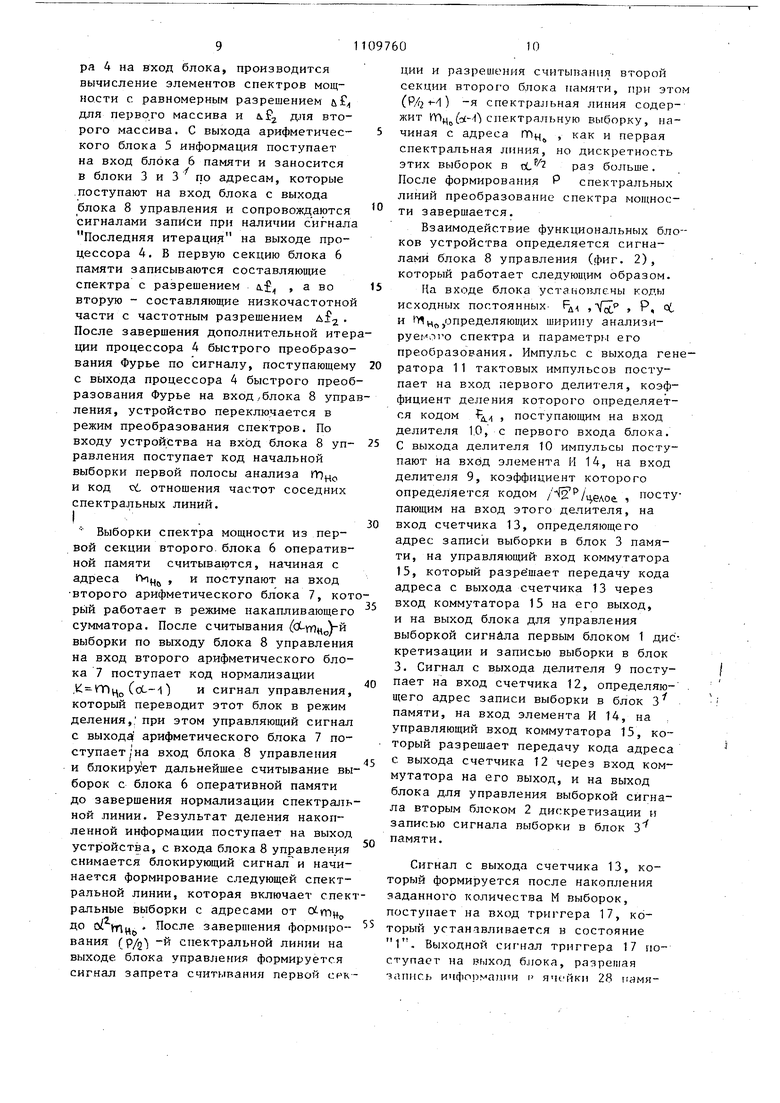

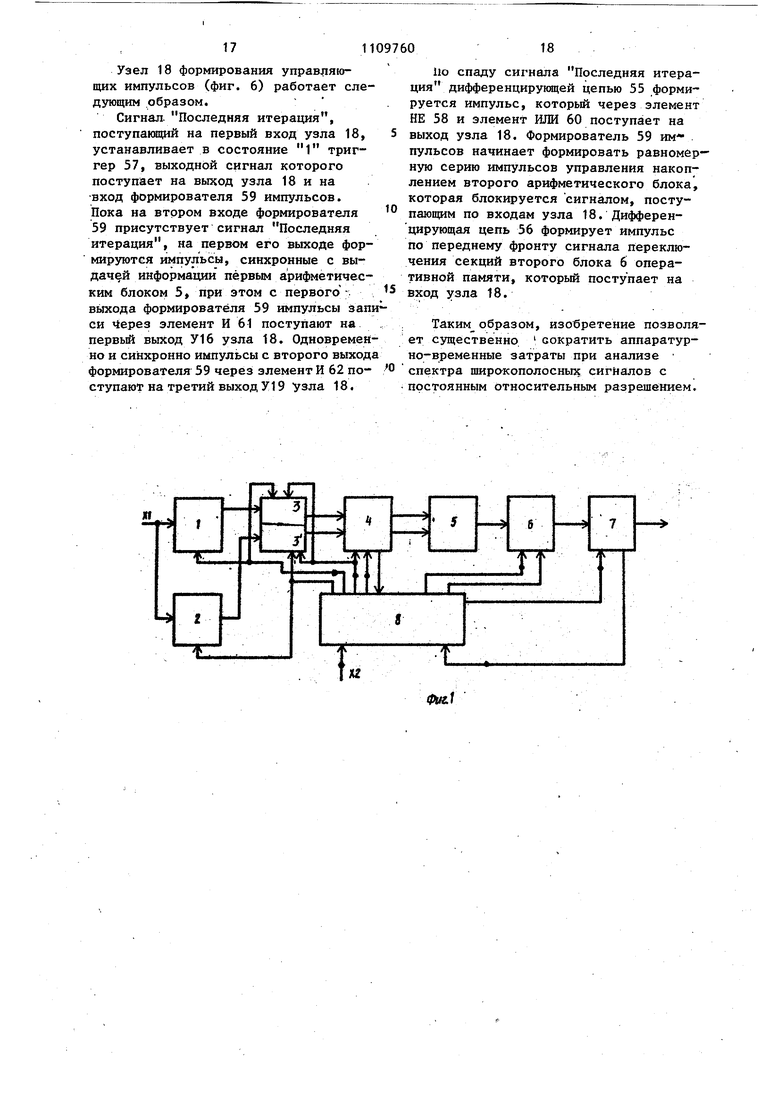

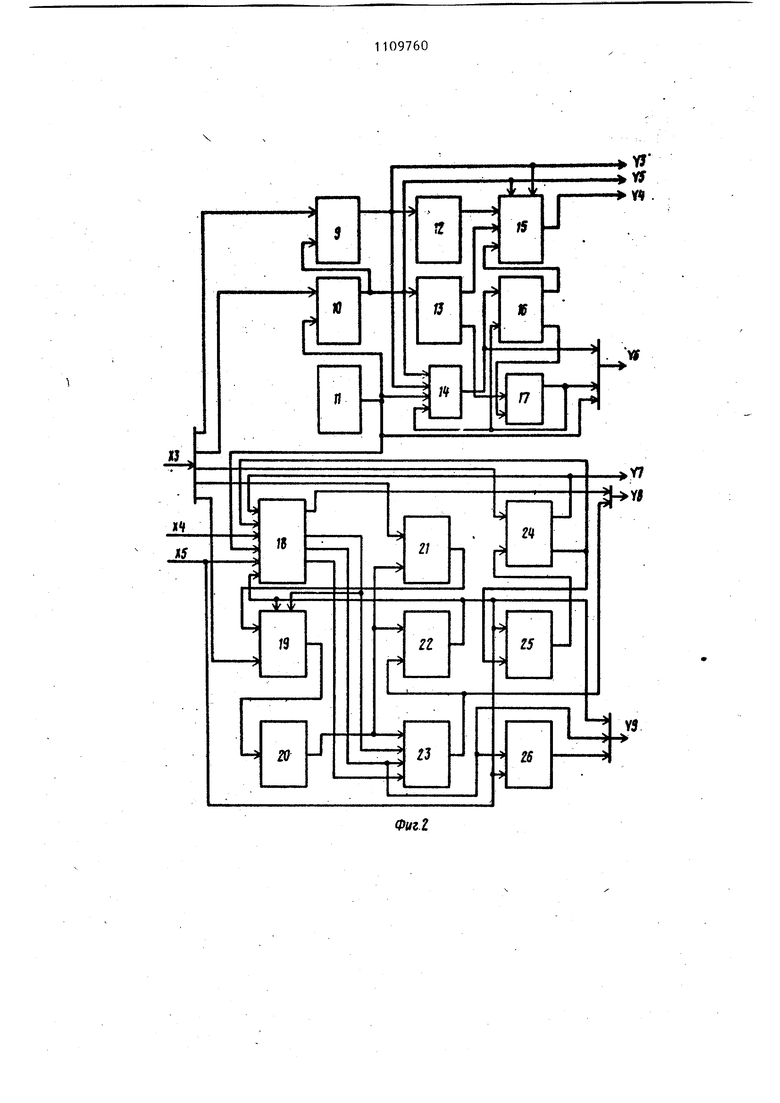

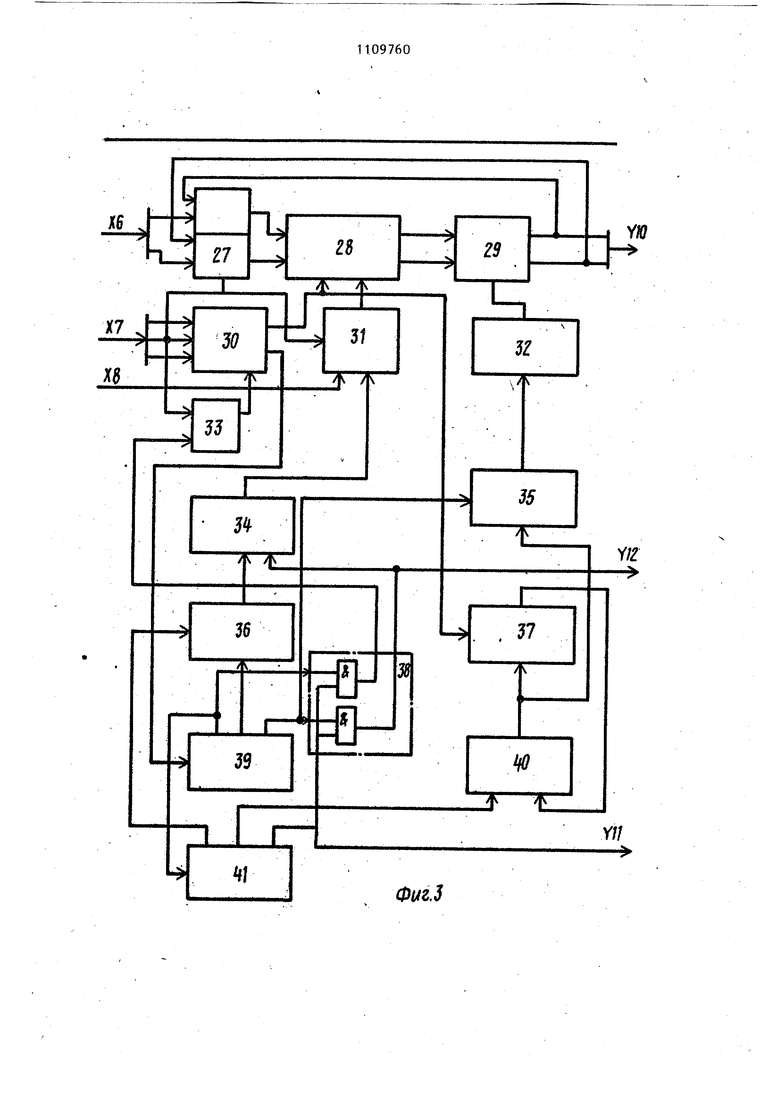

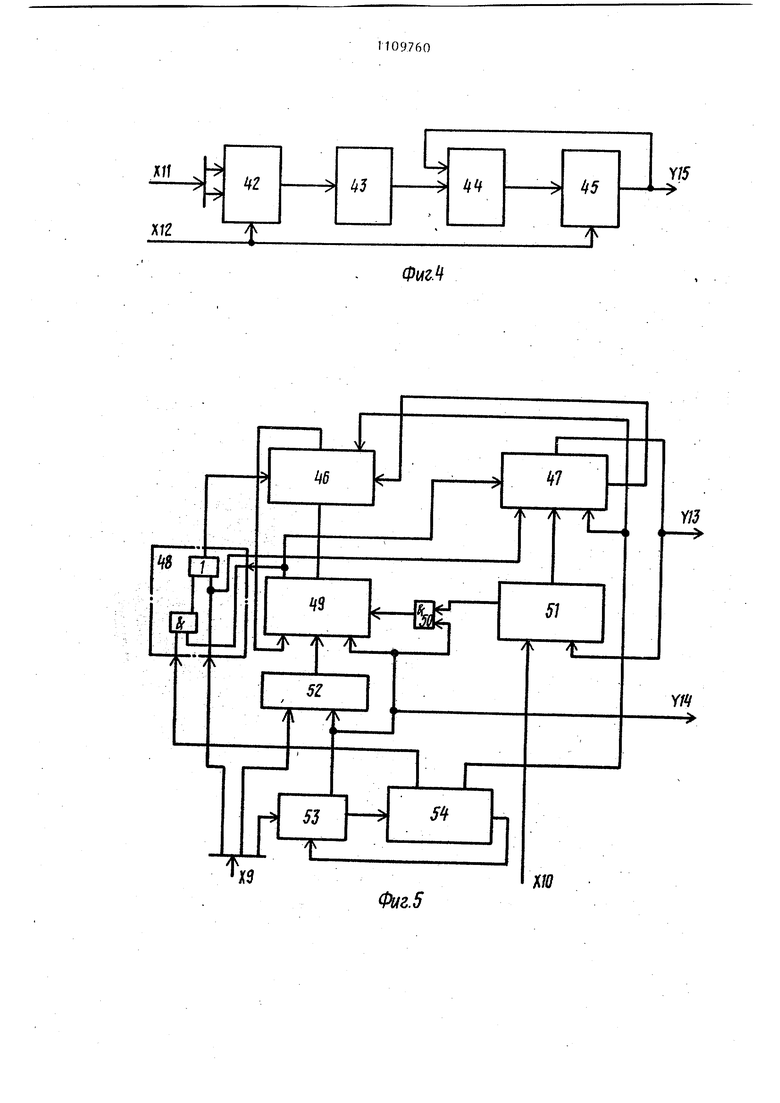

Изобретение относится к вычислительной технике, а именно к устройствам спектрального анализа, и предназначено для измерения спектров широкополосных сигнадов с частотным

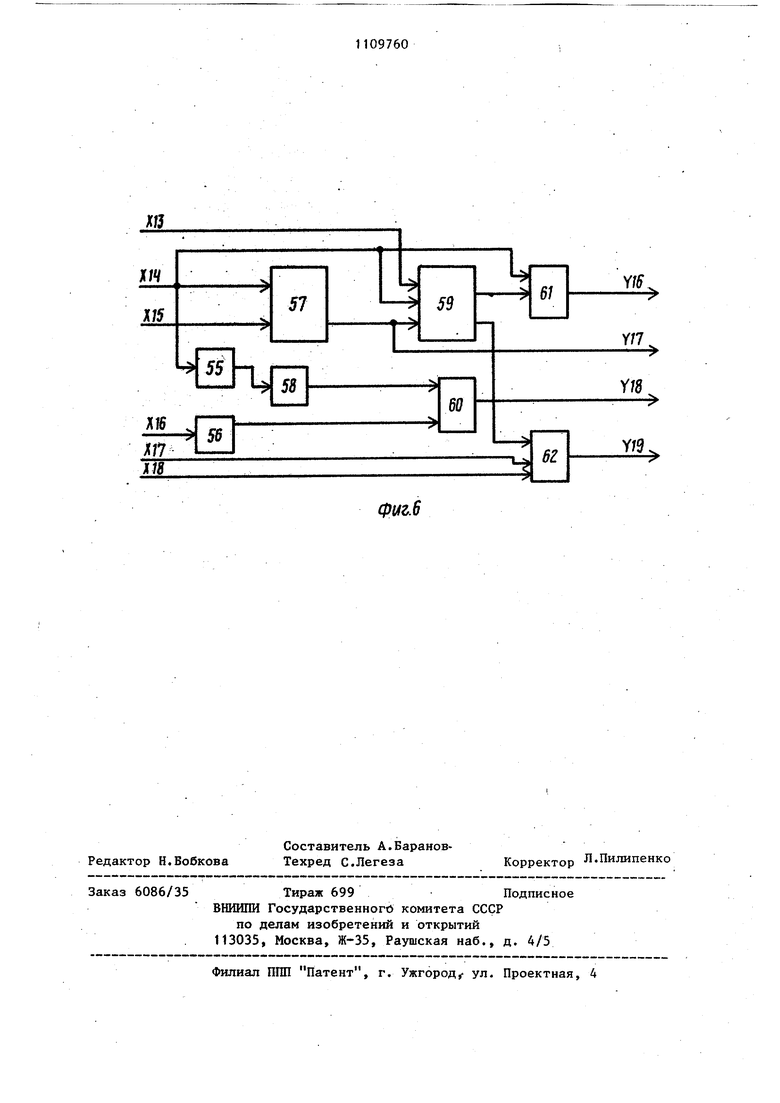

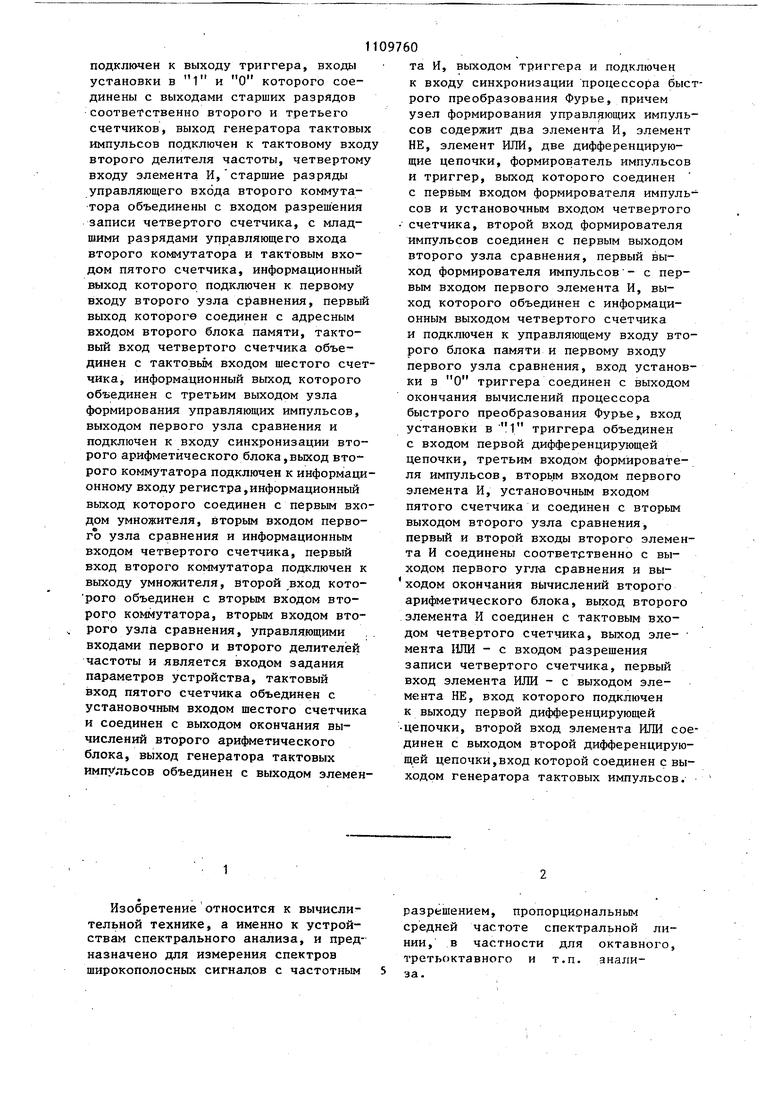

разрешением, пропорциональным средней частоте спектральной линии, в частности для октавного, третьоктавного и т.п. анализа. Известно устройство цифрового спектрального анализа, состоящее из блока дискретизации, процессора быстрого преобразования Фурье, выходного арифметического блока Щ. Недостаток дднного устройства получение спектров только с равномерным разрешением. Наиболее близким к изобретению по технической сущности является устройство, позволяющее формировать спектры с постоянным относительным разрешением, содержащее процессор быстрого преобразования Фурье, блок оперативной памяти, блок постоянной памяти, арифметический блок, блок формирования адресов, накапливающий сумматору блок деления, блок синхрони ции и управления, причем входом устрой ства является вход процессора быстрого преобразования Фурье, выход ко торого соединен с входом блока опер тивной памяти, выход которой соединен с первым входом блока умножения второй вход которого соединен с выходом блока постоянной памяти, а выход -,с входом накапливающего сум матора, выход которого соединен с первым входом блока деления, второй вход которого соединен с третьи выходом блока формирования адресов, а выход является выходом устройства и, кроме того, выходы блока синхронизации соединены с управляющими входами оперативной и постоянной памяти, блока формирования адресов, накапливающего сумматора и блока деления 12. Недостатком известного устройств являются значительные аппаратурновременные затраты при выполнении быстрого,преобразования Фурье при спектральном анализе с постоянным относительным разрешением широкополосных сигналов из-за большой избыточности по разрешению в области ве них частот спектра при удовлетворяющей стандартам, точности и разреша щей способности в области нижних частот Цель изобретения - сокращение объема аппаратуры. Поставленная цель достигается те что устройство для спектрального анализа с постоянным относительным разрешением, содержащее первый блок дискретизации, информационный выход которого подключен к информационному входу первого блока памяти, ин формационнмй выход которого соединен С входом реальной части процессора быстрого преобразования Фурье, информационный выход которого подклю-. . чен к информационному входу первого арифметического блока, информационный выход которого подключен к информационному входу второго блока памяти, информационный выход которого соединен с информационным входом второго арифметического блока, информационный выход которого является информационным выходом устройства, информационный вход первого блока дискретизации является информационHbiM входом устройства, выход синхронизации процессора быстрого преобразования Фурье подключен к входу синхронизации первого арифметического блока, содержит второй блок дискретизации и третий блок памяти, информационный выход которого подключен к входу мнимой части процессора быстрого преобразования Фурье, информационные входы второго и первого блоков дискретизации объединв ны, причем блок управления содержит два делителя частоты, генератор тактовых импульсов, шесть счетчиков, два коммутатора, элемент И, триггер, два узла сравнения, умножитель, регистр и узел формирования управляющих импульсов, причем выход первого делителя частоты соединен с управляющим входом второго блока дискретизации и адресным входом третьего блока памяти и подключен к младшим разрядам управляющего входа первого коммутатора, первому входу элемента И. и тактовому входу первого счетчика, информационный выход которого подключен к первому входу первого коммутатора, выход которого соединен с управляющими входами первого и третьего блоков памяти,и входом записи информации процессора быстрого преобразования Фурье, выход второго делителя частоты соединен с тактовым входом первого делителя частоты, старшими разрядами управляющего входа первогр коммутатора, вторым вхором элемента И и тактовым входом второго счетчика, информационный выход которого подключен к второму входу первого коммутатора, третий вход которого соединен с информационным выходом третьего счетчика, тактовый вход которого подключён к выходу элемента И, третий вход кото. рого объединен с установочным входом третьего счетчика и подключен к выходу триггера, входы установки в 1 и О которого соединены с выходами старших разрядов соответствен но второго и третьего счетчиков, выход генератора тактовых импульсов подключен к тактовому входу второго делителя частоты, четвертому входу элемента И, старшие разряды управляющего входа второго коммутатора объединены с входом разрешения записи четвертого счетчика, с младшими разрядами управляющего входа второго коммутатора и тактовым входом пятого счетчика, информационный выход которого подключен к первому входу BixJ рого узла сравнения, первый выход которого соединен с адресным входом второго блока памяти, тактовый вход четвертого счетчика объединен с тактовым входом шестого счетчика, информационный выход которого объединен с третьим выходом узла формирова НИН управляющих импульсов, выходом первого узла сравнения и подключен к входу синхронизации второго арифметического блока, выход второго коммутатора подключен к информационному входу регистра, информационный выход которого соединен с первым входом умножителя, вторым входом пер вого узла сравнения и информационным входом четвертого счетчика, первый вход второго коммутатора подклю чен к выходу умножителя, второй вход которого объединен с вторым входом второго коммутатора, вторым входом второго узла сравнения, управ ляющими входами первого и второго делителей частоты и является входом .задания параметров устройства, такто вый вход пятого счетчика объединен с установочным входом шестого счетчика и соединен с выходом окончания вычислений второго арифметического блока, выход генератора тактовых импульсов объединен с выходом элемента И, выходом триггера и подключен к входу синхронизации процессора быстрого преобразования Фурье, при,чем узел формирования управляющих импульсов содержит два элемента И, элемент НЕ, элемент ИЛИ, две дифференцирующие цепочки, формирователь i, импульсов и триггер, выход которого соединен с первым входом формироват ля импульсов и установочным входом четвертого счетчика, второй вход формирователя импульсов соединен с первым выходом второго узла сравнения, первый выход формирователя импульсов - с первым входом первого элемента И, выход которого объединен с информационным выходом четвертого счетчика и подключен к управляющему входу второго блока памяти и первому входу первого узла сравнения, вход установки в О триггера соединен с выходом окончания вычислений процессора быстрого преобразования Фурье, вход установки в 1 триггера объединен с входом первой дифференцирующей цепочки, третьим входом формирователя импульсов, вторым входом первого элемента И, установочным входом пятого счетчика и соединен с вторым выходом второго узла сравнения, первый и второй входы второго элемента И соединены соответственно с выходомпервого узла сравнения и выходом окончания вычислений второго арифметического блока, выход второго элемента И соединен с тактовым входом четвертого счетчика, выход элемента ИЛИ - с входом разрешения записи четвертого счетчика, первый вход элемента ИЛИ - с выходом элемента НЕ, вход которого подключен к выходу первой дифференцирующей цепочки, второй вход элемента ИЛИ соединен с выходом второй дифференцирующей цепочки, вход которой соединен с выходом генератора тактовых импульсов. На фиг. 1 представлена схема устройства для спектрального анализа с постоянным относительным разрешением, на фиг. 2 - блок управления; на фиг, 3 - процессор быстрого преобразования Фурье, на фиг. 4 - первый арифметический блок на фиг. 5 второй арифметический блок; на фиг. 6 - узел формирования управляющих импульсов Устройство спектрального анализа (фиг. 1) содержит первый 1 и второй 2блоки дискретизации, блоки 3 и 3 памяти, процессор А быстрого преобразования Фурье, арифметический блок 5, блок 6 памяти, арифметический блок 7 и блок 8 управления. Блок управления (фиг, 2) содержит первый 9 и второй 10 делители частоты (с переменным коэффициентом). генератор 11 тактовых импульсов, счё чики 12 и 13, элемент И 14, коммутатор 15, счетчик 16, триггер 17, узел 18 формирования управляющих импульсо коммутатор 19, регистр 20, умножитель 21, узел 22 сравнения, счетчик 23, узел 2А сравнения и счетчики 25 и 26. . , Процессор быстрого преобразования Фурье (фиг. 3) содержит коммутатор 27, оперативную память 28, арифметическое устройство 29, генератор 30 управляющих импульсов, коммутатор 31 постоянную память 32, триггер 33, первый 34 и второй 35 блоки инверсии кода, блок 36 коммутатора, регистр 37, блок 38 управления инверсией, счетчик 39, сумматор 40 и регистр 41 сдвига. Первый арифметический блок (фиг. 4 содержит коммутатор 42, квадратор 43, сумматор 44 и регистр 45, а второй арифметический блок (фиг. 5) состоит из первого 46 и второго 47 регистров сдвига, узла 48 управления занесением, сзгмматора-вычитателя 49, элемента И 50, сумматора 51, группы элементов И 52, триггера 53, генератора 54 серий импульсов. Узел формирования управляющих импульсов (фиг. 6) содержит дифференцирующие цепочки 55 и 56, триггер 57, элемент НЕ 58, формирователь 59 импульсов, элемент ИЛИ 60, элементы И 61 и 62. Устройство спектрального анализа с постоянным относительным разрешением работает следующим образом. Входной широкополосный сигнал поступает на входы блоков 1 и 2 дискретизации, где фильтруется, квантуется и преобразуется в цифровые коды причем частота квантования первого блока дискриминации устанавливается в соответствии с выражением с ixPoo ГРГ Д 00 средняя частота первой спектральной линии; oi/%Г частот соседних спектральных линий количество спектральных линий в полосе анализа, а. частота квантования второго блока дискретизации определяется соотношением Д . Выборки сигналов с выхода первого. 1 и второго 2 блоков дискратизации поступают на вход блоков-3 и 3 памяти, в которых накапливаются первый Ml и второй М2 массивы выборок, размер которых определяется соотношением K-Ma-Z Ll,..-,. где u-ifj Jbfoo/f V - диск15етизации частоты второго канала процессора быстрого преобразования Фурь.е, - относительная ширина спектральной линии. При этом шаг дискретизации часто ты первого ;канала процессора быстрого преобразования Фурье if -ifj/ci /u /V/q целая часть . При полном обновлении выборок массива Ml блоков 3 и 3 памяти, массивы Ml и М2 по сигналам с выхода блока 8 управления .заносятся в оперативную память 28 процессора 4 быстрого преобразования Фурье, как действительная и мнимая части комплексного массива. Процессор 4 переключается на режим выполнения преобразования и начинает выполнять итерации быстрого преобразования Фурье над полученным комплексным массивом. После завершения итераций быстрого преобразования Фурье выполняется специальная итерация распаковки полученного комплексного массива, при которой формируются две комплексные последовательности YfviJu ZCM) соответствующие массивам частотны } коэффициентов входного сигнала с различным частотным резрешением. Элементы последовательностей формаруются в соответствии с соотношениями,)Mx ±Vi:MM,}l. Яг: СгСйЯ Jv XCvxUX M-NH. 2 .tY( беЛУЫ-ут-и Т :). По мере формирования элементы последовательности с первого выхода процессора 4 быстрого преобразования Фурье поступают на вход арифметического блока 5, где по тактовым сигналам, поступаюнщм с выхода процессоpa 4 на вход блока, производится вычисление элементов спектров мощности с равномерным разрешением л для первого массива и .fj второго массива. С выхода арифметического блока 5 информация поступает на вход блока 6 памяти и заносится в блоки 3 и 3 по адресам, которые поступают на вход блока с выхода блока 8 управления и сопровождаются сигналами записи при наличии сигнала Последняя итерация на выходе процессора 4. В первую секцию блока 6 памяти записываются составляющие спектра с разрешением л. , а во вторую - составляющие низкочастотной части с частотным разрешением S- . После завершения дополнительной итер ции процессора 4 быстрого преобразования Фурье по сигналу, поступающему с выхода процессора 4 быстрого преоб разования Фурье на вход/блока 8 упра ления, устройство переключается в режим преобразования спектров. По входу устройства на вход блока 8 управления поступает код начальной выборки первой полосы анализа , и код об отношения частот соседних спектральных линий. I Выборки спектра мощности из первой секции второго, блока 6 оперативной памяти считываются, начиная с адреса , и поступают на вход -второго арифметического блока 7, кот рый работает в режиме накапливающего сумматора. После считывания ( выборки по выходу блока 8 управления на вход второго арифметического блока 7 поступает код нормализации (, (оС-1) и сигнал управления, который переводит этот блок в режим деления,; при этом управляющий сигнал с выходу арифметического блока 7 поступает /на вход блока 8 управления и блокиругет дальнейшее считывание вы борок с блока 6 оперативной памяти до завершения нормализации спектраль ной линии. Результат деления накопленной информации поступает на выход устройства, с входа блока 8 управления снимается блокирующий сигнал и начинается формирование следующей спектральной линии, которая включает спек ральные выборки с адресами от до После завершения формирования (р/з й спектральной линии на выходе блока управления формируется сигнал запрета считывания первой СРК ции и разрешения считывания второй секции второго блока памяти, при этом (Р/2-) я спектральная линия содержит ) спектральную выборку, начиная с адреса iTi , как и первая спектральная линия, но дискретность этих выборок в сс раз больше. После формирования Р спектральных линий преобразование спектра мощности завершается. Взаимодействие функциональных блоков устройства определяется сигналами блока 8 управления (фиг. 2), который работает следующим образом. Ни входе блока устано)шечы коды исходных постоянных- Рд YoC РЧ °i и ЧУ :1пре.р,епяю1цих ширину анализируемого спектра и параметры его преобразования. Импульс с выхода генератора 11 тактовых импульсов поступает на вход первого дели7еля, коэффициент деления которого определяется кодом ff , поступающим на вход делителя 1.0, с первого входа блока. С выхода делителя 10 импульсы поступают на вход элемента И 14, на вход делителя 9, коэффициент которого определяется кодом / /иелое. i поступающим на вход этого делителя, на вход счетчика 13, определяющего адрес записи выборки в блок 3 памяти, на управляющий- вход коммутатора 15, который разрешает передачу кода адреса с выхода счетчика 13 через вход коммутатора 15 на его выход, и на выход блока для управления выборкой сигнАла первым блоком 1 дискретизации и записью выборки в блок 3. Сигнал с выхода делителя 9 поступает на вход счетчика 12, определяющего адрес записи выборки в блок 3 памяти, на вход элемента И 14, на управляющий вход коммутатора 15, который разрешает передачу кода адреса с выхода счетчика 12 через вход коммутатора на его выход, и на выход блока для управления выборкой сигнала вторым блоком 2 дискретизации и записью сигнала выборки в блок 3 памяти. Сигнал с выхода счетчика 13, коорый формируется после накопления аданного количества М выборок, оступает на вход триггера 17, коорый устанавливается н состояние 1. Выходной сигнал триггера 17 потупает на рыход блока, разрешая апись ичформамии г ячейки 28 намити процессора 4 быстрого преобразования Фурье, на вход элемента И 14, на ныходе которого формируется серия тактовых импульсов управления записью, которая передается на выход блока 8 управления и на вход счетчика 16, на выходе которого формируется код адреса, поступающий на вход коммутатора 15, с выхода которого этот код передается на выход блока 8 управления. Импульсы на выходе элемента И 14 блокируются си налами, поступающими на входы этого элемента в циклах формирования выборок сигнала первым 1 или вторым 2 бл ками дискретизации. Сигнал с выхода счетчика 16, который формируется после перезаписи заданного количеств выборок М, устанавливает триггер 17 в состояние О и прекращает режим перезаписи массивов. При появлении сигнала последней итерации выполнения быстрого преобр.азования Фурье на входе блока 8 управления, на выходе узла 18 формирования управляющих импульсов формируется серия импульсов управления записью, которая поступает на выход блока 8. Одновременно на третьем выходе узла 18 формируется серия импульсов, которая поступает на выход блока 8 управления и на вход счетчика 23 адреса, код с выхода которого поступает на второй вход узла 22 сравнения и выход блока, и на вход счетчика 26. По заднему фронту сигнала Последняя итерация, который поступает на вход блока, узел 18 формирует на выходе импульс, который поступает на управляющий вход коммутатора 19 и разреша ет поступлен-о кода адреса начальной выборки т спектра с входа управления через вход коммутат.бра 19 на его вы ход и запись этого кода в регистр 2 Одновременно сигнал с выхода узла 18 поступает на вход счетчика 23 и разрешает запись кода tn, , которы поступает с выхода регистра 20 на вход счетчика 23 адреса. При этом на выходе узла 22 сравнения формиру ется импульс, который поступает на выход блока 8 управления и переводи второй арифметический блок 7 в режи деления, при этом сигнал с выхода этого блока через вход блока управления поступает на вход счетчика 26 и на вход узла 18, блокируя его работу, на вход счетчика 25 числа сформированных спектральных линий и на управляющий вход коммутатора 19, соединяя его вход с выходом. Произведение кода начальной выборки ГПц , который поступает с выхода «регистра 20 на вход умножителя 21, с кодом Q(отношения соседних частот, который поступает с входа блока на первый вход умножителя 21, с выхода умножителя через коммутатор 19 записывается в регистр 20. На этом завершается цикл подготовки. При снятии запрещающего сигнала , с входа блока управления узел 18 начинает цикл преобразования спеКтра. При этом на выходе узла 18 формируется серия тактовых импульсов, которая пос;гупает на выход блока управления, на вход счетчика 26 количества усредняемых выборок, выход которого соединен с выходом блока, и на вход счетчика 23 адреса, код с выхода iCOToporo поступает на вход узла 22 сравнения и на выход блока, определяя адрес ячейки первой секции второго блока 6 оперативной памяти, с которой производится считывание выборки спектра мощности первого массива. При равенстве текущего кода адреса на входе узла 22 сравнения с конечным адресом усредняемой группы выборок, который поступает на вход узла 22 сравнения с выхода регистра 20, на выходе узла формируется импульс, к оторый поступает на выход блока управления и переводит второй арифметический блок 7 в режим деления (при этом сигнал с выхода второго арифметического блока 7 через вход блока управления поступает на вход счетчика 26, на вход узла 18, блокируя его работу), на вход счетчика-25 числа сформированных спектральных линий и на управляющий вход коммутатора 19, соединяя его вход .с выходом. Произведение кода выборки, поступающей на вход умножителя 21, с множителем oL отношения частот, который поступает на его вход с входа блока, через коммутатор 19 записывается в регистр 20. На этом цикл формирования первой спектральной линии завершается. После выполнения деления вторым арифметическим блоком 7 он переходит в режим накопления и снимает запрещающий сигнал с. входа блока управления, при этом начинает формироваться следующая спектральная линия. На узле 24 сравнения сравнивается код числа сформированных спектральных линий, поступающий с выхода счетчика 25 на второй вход узла, с кодом Р заданного числа спектральных линий, который поступает с входа блока управления на вход узла 24. После сформирования Р/2 спектрапьных линий на первом выходе узла 24 сравнения появляется сигнал, который поступает на выход блока управления, где используется для переключения секций второго блока 6 памяти, и на вход узла 18, По переднему фронту сигнала, поступающего на вход узла 18, на вькоде этого узла формируется импульс, который поступает на управляющий вход коммутатора 19 и разрешает поступление кода адреса начальной выборки г с входа блока управления через вход коммутатора 19 на выход коммутатора и занесение его в регистр 20, Одновременно сигнал с выхода узла 18 поступает на вход счетчика 23 адреса и разрешает запись кода тц„ , который поступает с выхода регистра 20 на вход счетчика 23 адреса. На выходе узла 22 сравнения формируется импульс который поступает на выход блока управления и на вход коммутатора 19, Далее работа блока продолжается, как .описано. После сформирования F полос на втЪром выходе узла 24 сравнения формируется сигнал Конец преобразования-, который поступает на вход узла 18, переводя ее в режим ожидания сигнала Последняя итерация, посту-: пающего на вход блока управления,

Процессор быстрого преобразования Фурье (фиг. 3), в котором-реализован безызбыточный алгоритм с замещением, работает следующим образом.

Сигнал Режим перезаписи с входа процессора поступает на управляющий вход двухканального коммутатора 27 (при этом входы оперативной памяти 28 процессора подключаются к его первому входу), на управляющий вход коммутатора 31. адресов, который под-. ключает к адресным входам оперативной памяти 28 коды адреса, поступающие по входу процессора, на генератор 30 управляющих импульсов и на первый вход триггера 33, При этом генератор 30 управляющих импульсов формирует сигналы управления записью оперативной памяти 28, которые синхронизируются аналогичными сигналами, поступающими на вход процессора. Задним фронтом сигнала Режим перезаписи триггер 33 устанавливается в состояние 1 и переводит процессор на выполнение итераций вычисления быстрого преобразования Фурье, Входы оперативной памяти 28 коммутатором 27 подключаются к выходам арифметического устройства 29,

) К адресным входам оперативной памяти 28 через второй вход адресного коммутатора 31 подключается выход первого блока 34 инверсии кода, и начинаются итерации .вычисления быстрого преобразования Фурье, заключающиеся в последовательном выполнении элементарных операций преобразования вида , где А - первый, В второй операнды, выбираемые из ячеек оперативной памяти 28 и поступающие на первый и второй вход арифметического блока 29, а 4:V - значение экспоненциального множителя, поступающего с выхода постоянной памяти 32 и на третий, вход этого же арифметического блока. Элементарная операция выполняется за четыре такта и каждый импульс такта, поступая с второго выхода генератора 30 управляющих импульсов, изменяет состояние счетчика 39, Во время выполнения двух первых тактов на вентиль, отделяющий младший разряд счетчика, с второго выхода генер.атора 30 управляющих импульсов поступает потенциал, блокирующий прохождение сигнала переноса с младшего разряда счетчика на следующий разряд.

Одновременно этот сигнал с первого выхода генератора 30 управляющих импульсов поступает на вход управления оперативной памяти 28 и разрешает считывание двух операндов из ячеек памяти. На первом йыходе счетчика 39 пда этом формируются два значения кода, которые преобразуются в адреса операндов, считываемых с ячеек оперативной памяти 28 с помощь блока 36 коммутаторов, управляемого сигналами, поступающими с первого выхода итерационного регистра 41, Считываемые операнды заносятся в арифметический блок 29, где выполняется элементарная операция преобразования и во время последующих двух тактов результаты преобразования заносятся через коммутатор 27 в оперативную память 28 по адресам, совпадающим с адресами считывания. Потенциал, блокирующий младший разряд счетчика 39, при этом снимается и на вход управления оперативной памятью 28 поступает сигнал занесения информации. Во время ввода информации в оперативную память 28 на выходе второго блока 35 инверсии кода формиру ются адреса обращения к постоянной памяти 32 для следующей элементарной операции. Значение экспоненциал15ного множителя считывается с выхода постоя ной памяти 32 и заносится по третьему входу в арифметический блок 29. После выполнения M/j элементарных операций сигнал перехода из 1 в О со с.таршего разряда счетчика 39, являющийся вторым выходом этого счетчика, поступает на вход итерационного регистра 41 и сдвигает влево на один разряд информацию в регистре, что приводит к выполнению следующей итерации быстрого преобразования Фурье. Коды, поступающие с первого входа счетчика 39 на вход блока 36 коммутаторов, преобразуются в адресные коды обращения к оперативной памяти 28. Первьш арифметический блок 5 (фиг. 4) работает следующим образом. Действительная и мнимая части комплексного спектрального коэффициента поступают соответственно на пер вый и второй входы коммутатора 42, которые являются первым входом блока 5, и по тактовым импульсам, поступающим на управляющий вход коммутато ра с второго входа блока 5, последовательно передаются чер§з квадратор 43 на первый вход сумматора 44, а с его выхода на вход накапливающего регистра 45, выход которого соединен с вторым входом сумматора 44 и с выходом блока 5, куда передается сумма квадратов действительной и мнимой со тавляющих спектрального коэффициента Второй арифметический блок 7 (фиг. 5) работает в двух режимах. В первом режиме триггер 53 сигналом с выхода подключает через элемен И 50 выход переноса старшего разряда сумматора 51 к входу переноса младшего разряда сумматора-вычитателя 49 блокирует прохождение информации с входа второго арифметического блока через блок ключей и устанавливает в режим суммирования сумматор76016вычитатель 49. В первом режиме второй арифметический блок работает в режиме накапливающего сумматора. Информация, поступающая с входа арифметического блока, суммируется с содержимым регистров 46 и 47 и вновь за-, носится в эти регистры. Импульсы занесения информации в регистры 46 и 47 формируются на выходе узла 48 управления занесением под воздействием сигналов, поступающих с входа арифметического блока на первый вход узла управления занесением. Сиг-, нал, поступающий на первый вход . триггера 53 с первого входа арифметического блока, устанавливает его в 1. Сигнал с выхода триггера разрешает прохождение кода множителя нопмализации через элемент И 52 на вход сумматора-вычитателя 49, переводит его в режим вычитания и разрешают работу генератора 54 серий импульсов. После этого второй арифметический блок начинает работать в режиме деления. При наличии низкого потенциала на втором выходе сумматора-вычи- тателя 49 (выход переноса старшего разряда), поступающего на второй вход узла управления занесением, на выходе этого узла под воздействием импульса, поступающего с второго . выхода генератора тактовых импульсов, формируется импульс занесения результата вычитания содержимого регистра 46 и множителя нормализации в регистр 46. После этого на первом выходе генератора 54 серий импульсов формируются импульсы, поступающие на входы сдвига регистров 46 и 47, по которым информация в них сдвигается влево на один разряд, причем информация со старшего разряда регистра 47 заносится в младший /разряд регистра 46, а в Младший разряд регистра 47 записывается 1, если на втором выходе сумматора-вычитателя 49 потенциал О. и сигнал О при наличии потенциала 1 на этом выходе. Описанные циклы занесения и сдвига повторяются до получения требуемой разрядности результата, триггер 53 сигналом с третьего выхода генератора 54 серий импульсов устанавливается в О и второй арифметический блок переходит в режим накопления. Узел 18 формирования управляю1ЦИХ импульсов (фиг. 6) работает следующим образом. Сигнал. Последняя итерация, поступакмций на первый вход узла 18, устанавливает в состояние 1 триггер 57, выходной сигнал которого поступает на выход узла 18 и на вход формирователя 59 импульсов. Пока на втором входе формирователя 59 присутствует сигнал Последняя итерация, на первом его выходе формируются импульсы, синхронные с выдачей информации первым арифметическим блоком 5, при этом с первого; выхода формирователя 59 импульсы зап си ерез элемент И 61 поступают на первый выход У16 узла 18. Одновремен но и синхронно импульсы с второго выход формирователя 59 через элемент И 62 поступают на третий выход У19 узла 18. Но спаду сигнала Последняя итерация дифференцирукяцей цепью 55 формируется импульс, который через элемент НЕ 58 и элемент ИЛИ 60 поступает на выход узла 18. Формирователь 59 импульсов начинает формировать равномерную серию импульсов управления накоплением второго арифметического блока, которая блокируется сигналом, поступающим по входам узла 18. Дифференцирующая цепь 56 формирует импульс по переднему фронту сигнала переключения секций второго блока 6 оперативной памяти, который поступает на вход узла 18. Таким образом, изобретение позволяет существенно сократить аппаратурно-временные затраты при анализе спектра широкополосных сигналов с постоянным относительным разрешением.

VJ

,3

Фмг.

Фиг.5

фиг.6

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ТЕЛЕФОННАЯ ТРАНСЛЯЦИЯ ДЛЯ ПОСЛЕДОВАТЕЛЬНОГО ВКЛЮЧЕНИЯ В ЛИНИЮ | 1921 |

|

SU3582A1 |

| Шланговое соединение | 0 |

|

SU88A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 3932737, кл | |||

| G | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-08-23—Публикация

1982-09-10—Подача