Изобретение относится к вычисли тельной технике, а именно к преобразователям аналоговой величины сигнала в код, и предназначено преимущественно для компенсации нелинейности измерительных датчиков.

Известен функциональный аналогоцифровой преобразователь, содержащий первый интегратор, вход которого через первый ключ соединен с .первой входной клеммой устройства, выхо первого интегратора через второй ключ соединен с входом второго интегратора, соединенным также -через третий ключ с второй входной клеммой устройства, причем управляющие входы ключей подключены соответственно к выходу Схемы сравнения, к инверсному выходу триггера и его неинверсному выходу, выход второго интегратора соединен с входом блока сравнения, выход которого подключен к блоку определения начальных условий первого интегратора, первому входу схемы совпадений и управляющему входу блока задания и измерения интервалов времени, управляющий выход которого подключен к тактовому входу триггера, инверсный выход которого подключен к второму входу схемы сравнения, выходы блока задания и из мерения интервалов времени являются кодовыми выходами устройства ij .

Недостатками устройства являются невозможность прямого программирования функции линеаризации по Известным значениям входной функции, узкий класс реализуемых.функций, ограниченный чисто степенной зависимостью второго порядка, а также низкая точность, связанная с сдвигом и дрейфом обоих интеграторов и особенно входного блока сравнения.

Наиболее близким по технической сущности к предлагаемому является функциональный аналого-цифровой преобразователб, содержащий интегратор, вход которого соединен с выходами первого и второго ключей, информационный вход первого ключа через первый масштабный резистор соединен с входом преобразователя, а информационный вход второго ключа через второй масштабный резистор соединен с выходом источника опорного сигнала, управляющие входы первого и второго ключей подключены к соответствующим ныходам триггера, вход синхронизации которого соединен с шлходом старшего разряда счетчика, подключенного счетным входом к выходу тактового генератора 2 .

Недостатком известного преобразователя является сложность регулировки коэффициентов деления, при этом точность.преобразователя ограничена

кусочно-линейной аппроксимацией и дискретностью установки коэффициентов деления соответствующих счетчиков.

Цель изобретения - повышение точности.

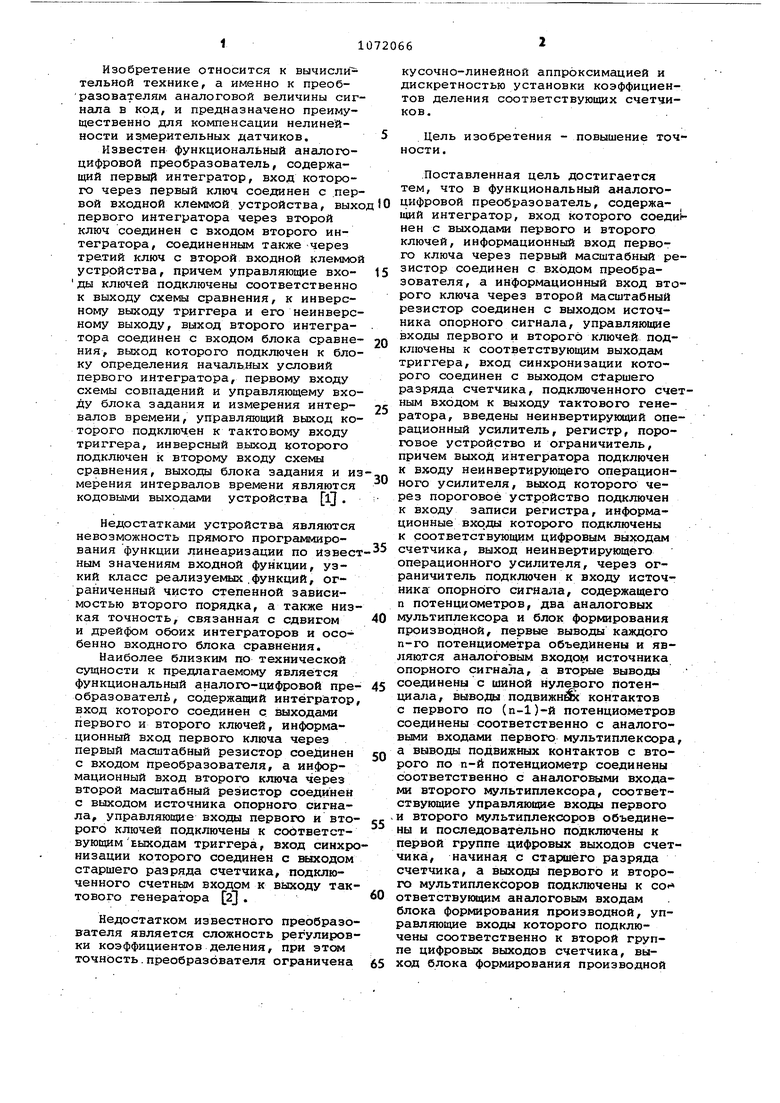

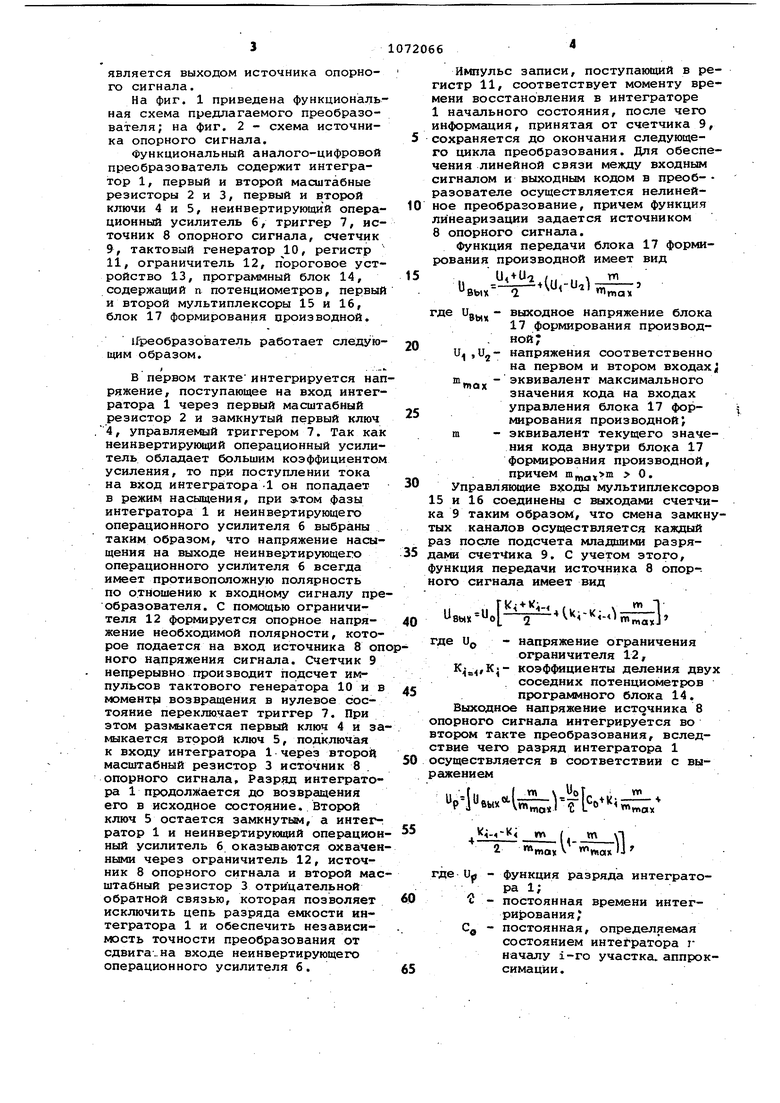

.Поставленная цель достигается тем, что в функциональный аналогоцифровой преобразователь, содержащий интегратор, вход которого соеди нен с выходами первого и второго ключей, информационный вход первого ключа через первый масштабный резистор соединен с входом преобразователя, а информационный вход второго ключа через второй масштабный резистор соединен с выходом источника опорного сигнала, управляющие входы первого и второго ключей подключены к соответствующим выходам триггера, вход синхронизации которого соединен с выходом старшего разряда счетчика, подключенного сченым входом к выходу тактового генератора, введены неинвертирующий операционный усилитель, регистр, порогхэвое устройство и ограничитель, причем выход интегратора подключен к входу неинвертирующего операционного усилителя, выход которого через пороговое устройство подключен к входу записи регистра, информационные входы которого подключены к соответствующим цифровым выходам счетчика, выход неинвертирующего операционного усилителя, через ограничитель подключен к входу источника опорного сигнала, содержащего п потенциометров, два аналоговых мультиплексора и блок формирования производной, первые выводы каждого п-го потенциометра объединены и являются аналоговым входом источника опорного сигнала, а вторые вывода) соединены с шиной нулевого потенциала, выводы подвижник контактов с первого по (п-1)-й потенциометров соединены соответственно с аналоговыми входами первого мультиплексора а выводы подвижных контактов с второго по п-й потенциометр соединены соответственно с аналоговыми входами второго мультиплексора, соответствующие управляющие входы первого и второго мультиплексоров объединены и последовательно подключены к первой группе цифровых выходов счетчика;, начиная с старшего разряда счетчика, а выходы первого и второго мультиплексоров подключены к со ответствукицим аналоговым входам блока формирования производной, управляющие входы которого подключены соответственно к второй группе цифровых выходов счетчика, выход блока формирования производной является выходом источника опорного сигнала. На фиг. 1 приведена функциональ ная схема предлагаемого преобразователя; на фиг. 2 - схема источника опорного сигнала. функциональный аналого-цифровой преобразователь содержит интегратор 1, первый и второй масштабные резисторы 2 и 3, первый и второй ключи 4 и 5, неинвертирующий операционный усилитель 6, триггер 7, источник 8 опорного сигнала, счетчик 9, тактовый генератор 10, регистр 11, ограничитель 12, пЪроговое устройство 13, программный блок 14, содержащий п потенциометров, первый и второй мультиплексоры 15 и 16, блок 17 фop шpoвaния ароизводной, 1Греобразователь работает следую щим образом. В первом такте интегрируется нап ряжение, поступающее на вход интег ратора 1 через первый масштабный резистор 2 и замкнутый первый ключ 4, управляемый триггером 7. Так как неинвертирующий операционный усилитель обладает большим коэффициентом усиления, то при поступлении тока на вход интегратора -1 он попадает в режим насыщения, при э-том фазы интегратора 1 и неинвертирующего операционного усилителя 6 выбраны таким образом, что напряжение насыщения на выходе неинвертирующего операционного усилителя 6 всегда имеет противоположную полярность по отношению к входному сигналу пре образователя. С помощью ограничителя 12 формируется опорное напряжение необходимой полярности, которое подается на вход источника 8 оп ного напряжения сигнала. Счетчик 9 непрерывно производит подсчет импульсов тактового генератора 10 и в моменту возвращения в нулевое состояние переключает триггер 7. При этом размыкается первый ключ 4 и за мыкается второй ключ 5, подключая К входу интегратора 1 через второй масштабный резистор 3 источник 8 опорного сигнсша. Разряд интегратора 1 продолжается до возвращения его в исходное состояние. Второй ключ 5 остается замкнутым, а интегратор 1 и неинвертирующий операцион ный усилитель 6 оказываются охвачен ными через ограничитель 12, источник 8 опорного сигнала и второй мас штабный резистор 3 отрицательной обратной связью, которая позволяет исключить цепь разряда емкости интегратора 1 и обеспечить независимость точности преобразования от сдвига-на входе неинвертирующего операционного усилителя 6. Импульс записи, поступающий в регистр 11, соответствует моменту времени восстановления в интеграторе 1 начального состояния, после чего информсщия, принятая от счетчика 9, сохраняется до окончания следующего цикла преобразования. Для обеспечения линейной связи между входным сигналом и выходным кодом в преоб- разователе осуществляется нелинейное преобразование, причем функция линеаризации задается источником 8 опорного сигнала. Функция передачи блока 17 формирования производной имеет вид tlUrM где Ujy - выходное напряжение блока 17 формирования производ. ной; U;, jUj- напряжения соответственно на первом и втором входах; тах Эквивалент максимального значения кода на входах управления блока 17 фор- мирования производной) m - эквивалент текущего значения кода внутри блока 17 формирования производной, причем ,т 0. Управляющие входы мультиплексоров 15 и 16 соединены с выходами счетчика 9 таким образом, что смена замкнутых каналов осуществляется каждый аз посхпе подсчета младшими разряами счетчика 9. С учетом этого, ункция передачи источника 8 опор-, ого сигнала имеет вид где Up - напряжение ограничения ограничителя 12, коэффициенты деления двух соседних потенциометров программного блока 14, Выходное напряжение источника 8 опорного сигнсша интегрируется во втором такте преобразования, вследствие чего разряд интегратора 1 осуществляется в соответствии с выражением.1-гК-, , 4-5 m 2 «maxV ««,ах М где Up - функция разряда интегратора 1; постоянная времени интегрирования, Сд - постоянная, определяемая состоянием интегратора т началу i-ro участка, аппроксимации .

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный аналого-цифровой преобразователь | 1983 |

|

SU1113813A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛЫ ВРЕМЕНИ | 2014 |

|

RU2552605C1 |

| Интегрирующий преобразователь напряжения в код | 1986 |

|

SU1410275A1 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1101848A1 |

| Интегратор с автокоррекциейКОэффициЕНТА пЕРЕдАчи | 1978 |

|

SU805346A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СРЕДНЕКВАДРАТИЧЕСКОГО ЗНАЧЕНИЯ НАПРЯЖЕНИЯ | 2000 |

|

RU2198410C2 |

| Цифровой частотомер | 2019 |

|

RU2730047C1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1132357A1 |

| Функциональный аналого-цифровой преобразователь | 1986 |

|

SU1310855A1 |

| Устройство для контроля деградации МДП-структур | 1990 |

|

SU1783454A1 |

ФУНКЦИОНАЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий интегратор, вход которого соединен с выходами первого и второго ключей, информационный вход первого ключа через первый, масштабный резистор соединен с входом преобразователя, а информационный вход второго кл1рча через второй масштабный резистор - с выходом источника о.порного сигнала, управляющие входы первого и второго ключей подключены к соотвещ-ствующим выходам триггера, вход синхронизации которого соединен с выходом старшего разряда счетчика, подключенного счетным входом к выходу тактового генератора, отличающийся тем, что, с целью повышения,точности, в него введены неинвертирующий операционный усилитель, регистр, пороговое устройство , и ограничитель, причем вход интегратора подключен к входу неинвертирующего операционного усилит1вля, .выход которого через пороговое устройство подключен к входу записи регистра, информационные входы кототрого подключены к соответствующим цифровым выходам счетчика, выход неинвертирующего операционного усилителя через ограничитель подключен к входу источника опорного сигнат ла, содержащего п потенциометров, два аналоговых мультиплексора и блок формирования прЬизводной, -первые выводы каждого п-го потенциометра объединены и являются аналоговым входом источника опорного , а вторые вывода соединены с шиной нулевого потенциала, выводы подвижных контактов с первого по (п-1)-й потенциометров соединены соответственно с аналоговыми входами первого мультиплексора, а выводы подвижных контактов с второго по п-й потенциометр соединены соответственно с аналоговыми входами второго мультиплексора, соответствующие управляющие входы первого и второго мультиплексоров объединены и последовательно подключены к первой группе цифровых выходов счетчика, начиная с старшего -разряда счетчика, а выходы первого и второго мультиплексоров подключены к соответствующим аналоговым входам блока формирования производной, управляющие входы которого подключены соответст- венно к второй группе цифровых выходов счетчика, выход блока формирования производной является выходом источника опорного сигнала.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аналого-цифровой функциональный преобразователь | 1978 |

|

SU746582A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США 4110746, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

Авторы

Даты

1984-02-07—Публикация

1982-09-27—Подача