фае.}

2. Устройство по П.1, отличающееся тем, 4to. преобразователь напряжения в частоту содержит операционный усилитель, конденсатор, аналоговый ключ, компаратор, тактируемый D-триггер, резистор, разрядный ключ, источник разрядного тока, шину отрицательного источника питания, причем параллельно соединенные конденсатор и аналоговый ключ подключены между инвертирующим входом и выходом операционного усилителя, выход которого подключен к инвертирующему входу компаратора, неинвертирующий вход которого соединен с неинвертирукндим входом операционного усилителя и общей щиной устройства, выход компаратора соединен с D-иходом тактируемого В-триггера, прямой выход которого соединен с управляющим входом разрядного ключа и является выходом преобразователя напряжения в частоту, первый, второй и третий управляющие входы которого подключены к С-входу тактируемого 3)-триггера, управляющему входу аналогового ключа и R -входу тактируемого D-триггера- соответственно, вход преобразователя напряжения в частоту через резистор соединен с инвертирующим входом операционного усилителя и входом разрядного ключа, выход которого через источник разрядного тока соединен с шиной отрицательного источника питания ..

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1984 |

|

SU1239867A1 |

| Аналогово-цифровое делительное устройство | 1981 |

|

SU1049927A1 |

| Устройство для формирования последовательностей импульсов | 1989 |

|

SU1653140A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1106013A1 |

| Измерительный преобразователь для тензорезисторных весоизмерительных устройств | 1990 |

|

SU1830463A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 1997 |

|

RU2121754C1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1277396A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1462482A1 |

| Преобразователь напряжение-код | 1988 |

|

SU1508343A1 |

| Устройство для передачи информации | 1986 |

|

SU1381571A1 |

Изобретение относится-к устройствам импульсной техники и предназначено для использования в системах сбора и обработки информации различного назначения, системах автоматического управления и регулирования. Известен аналого-цифровой преобра зователь последовательного приближения, содержащий цифроаналоговый преобразователь, регистр, источник опорного напряжения и компаратор l, Недостатком известного устройства является наличие большого числа прецизионных узлов и блоков, что затрудняет их изготовлейие в виде боль ших интегральных схем. Известен также аналого-цифровой преобразователь с промежуточным преобразователем в частоту, содержащий преобразователь напряжения в частоту, вход которого является входом устройства, а выход соединен с тактовым входом блока счетчиков импульсов, блок фор1«а1рования временных интервалов, первый выход которого соединен с первым управляющим входом блока счетчиков импульсов 2j . Недостатком известного устройства является то, что в течение всего . интервала преобразования устройства состояние ни одного из {)азрядов выходного счетчика импульсов не опре делено, т.е. последний импульс в из-) меряемой пачке, поступающий с выхода преобразователя напряжения в частоту, может изменить состояние всех разрядов Iсчетчика. Это приводит к тому, что, например, процессор системы сбора и обработки информации простаивает в течение всего интервала преобразования аналого-цифрового преобразователя. Кроме того, многие цифровые процессоры начинают обработку информации, начиная со старших разрядов кода, получения которых . в процессе преобразования известный аналого-цифровой преобразователь не обеспечивает, что существенно снижает эффективность и область его применения. Цель изобретения - расширение функциональных возможностей устройства путем обеспечения последовательного формирования значений выходного кода, начиная со старших разрядов, в процессе преобразования, а также формирование выхддного кода в виде, не. требующем выходного согласующего устройства. Поставленная цель достигается тем, что в аналого-цифровой преобразователь, содержапщй преобразователь напряжения в частоту, вход которого является входом устройства, а выход

соединен с тактовым входом блока счетчиков импульсов, блок формирования временных интервалов, первый выход которого соединен с первым управляющим входом блока счетчиков импульсов, введены блок управления и генератор тактоввк импульсов, причем первый вход блока управления является входом запуска устройства, второй вход соединен с выходом генератора тактовых импульсов, первым управляклцим входом преобразователя напряжения в частоту и первым входом блока формирования временных интервалов, первый выход блока управления соединен со вторым управляющим входом преобразователя напряжения в частоту, а второй выход - со входами сброса блоков счетчиков импульсов и формирования временных интервалов и с третьим управляющим входом преобразователя напряжения в частоту, группа выходов со второго по N-и блока формирования временных интервалов соединена с соответствующей груп пой управляющих входов блока счетчиков импульсов, а N4 1-й выход - с третьим входом блока управления, где N - число разрядов выходного кода устройства.

При этом преобразователь напряжения в частоту содержит операционный усилитель, конденсатор, аналоговыйключ, компаратор, тактируемый } -триггер, резистор, разрядный ключ, источник разрядного тока, шину отрицательного источника питания, причем параллельно соединенные конденсатор и аналоговь-й ключ подключены между инвертирующим входом и выходом oneрационного усилителя, выход которого подключен к инвертирующему входу компаратора, неинвертирующий вход которого соединен с неинвертирующим входом операционного усилителя и общей шиной устройства, выход компаратора соединен, сD-входом тактируемого 3)-триггера, прямой выход которого соединен с управляющим входом разрядного ключа и является выходом преобразователя напряжения в частоту, первый, второй.и третий управлягацие входы которого подключены к С-входу тактируемого Г- риггера, управляющему входу аналогового ключа и R -входу тактируемого) -триггера соответственно, вход преоб1 азователя напряжения в частоту через резистор соединен с инвертирующим входом операционного усилителя и входом разрядного ключа, выход которого ЧРрез источник разрядного тока.соединен с шиной отрицательного источника питания.

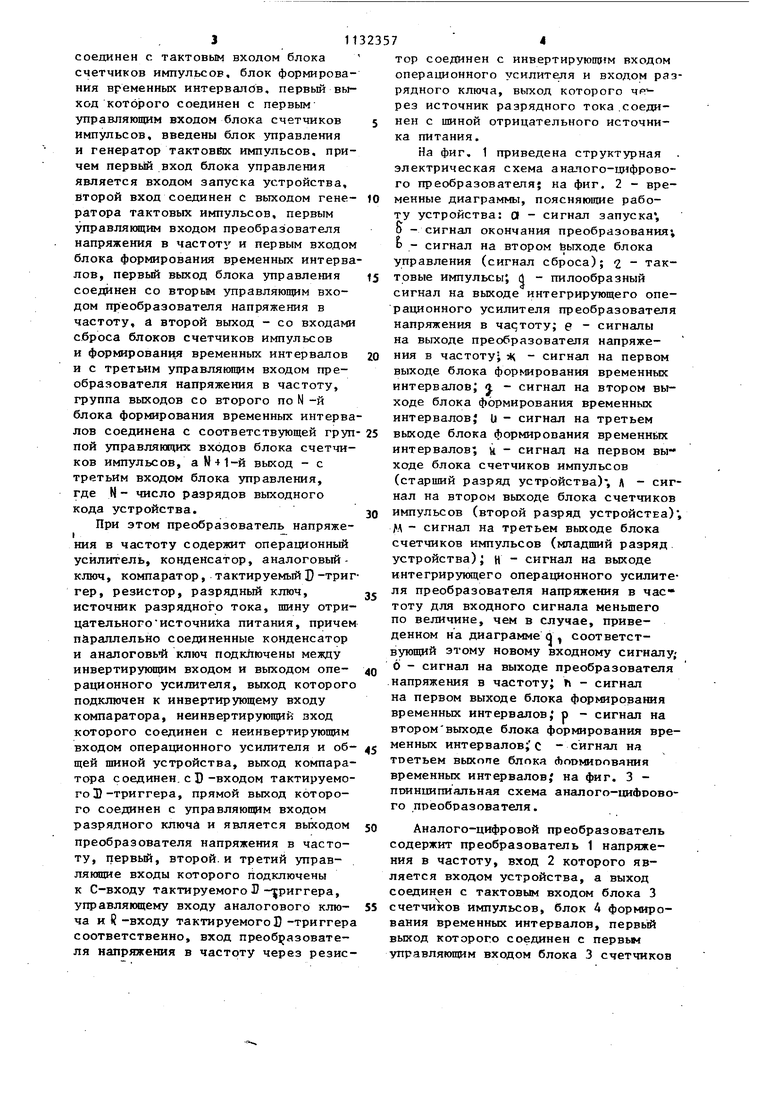

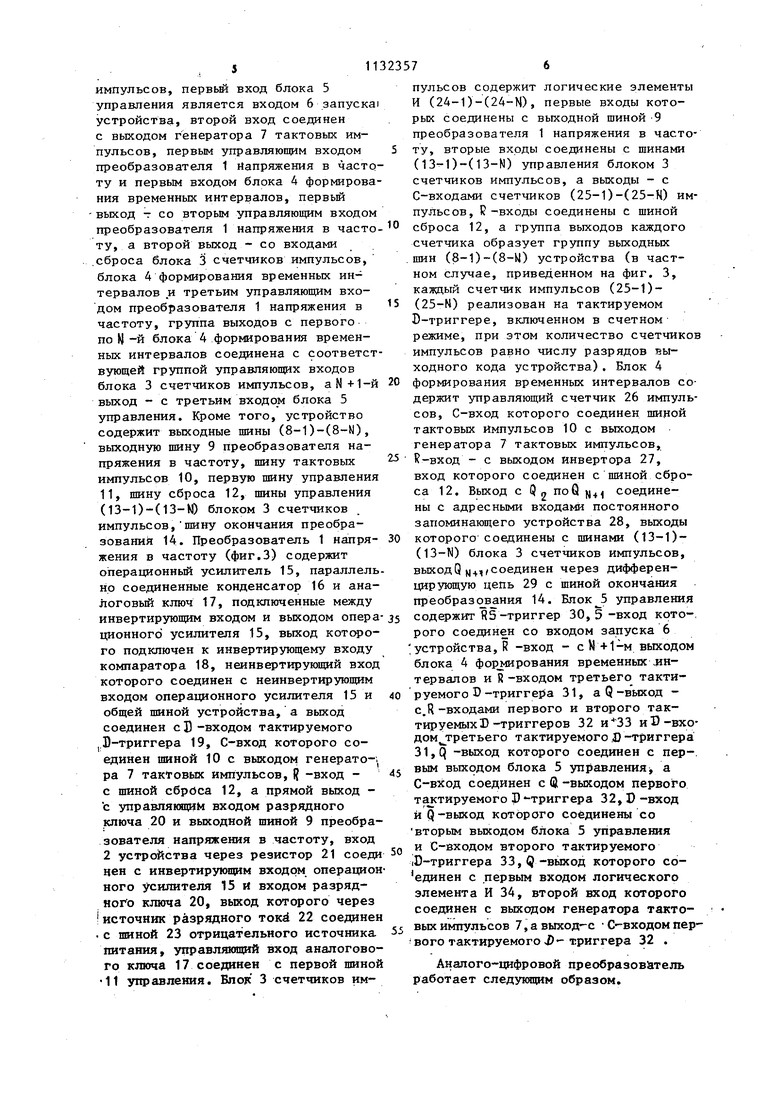

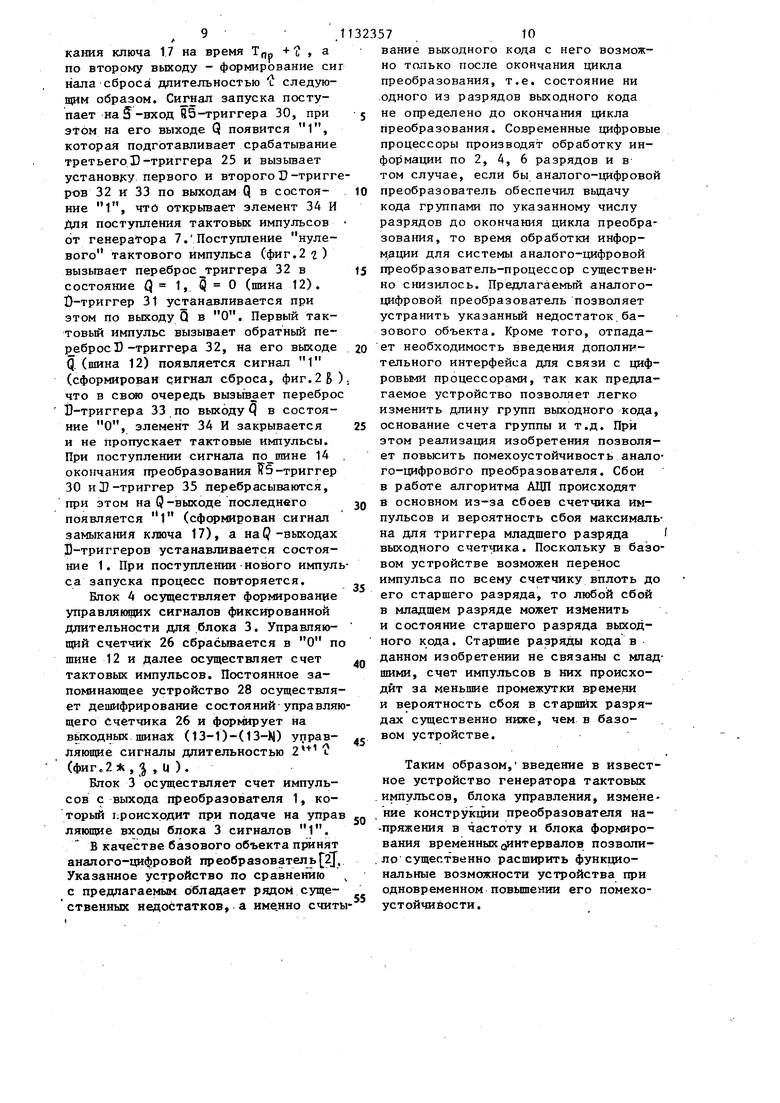

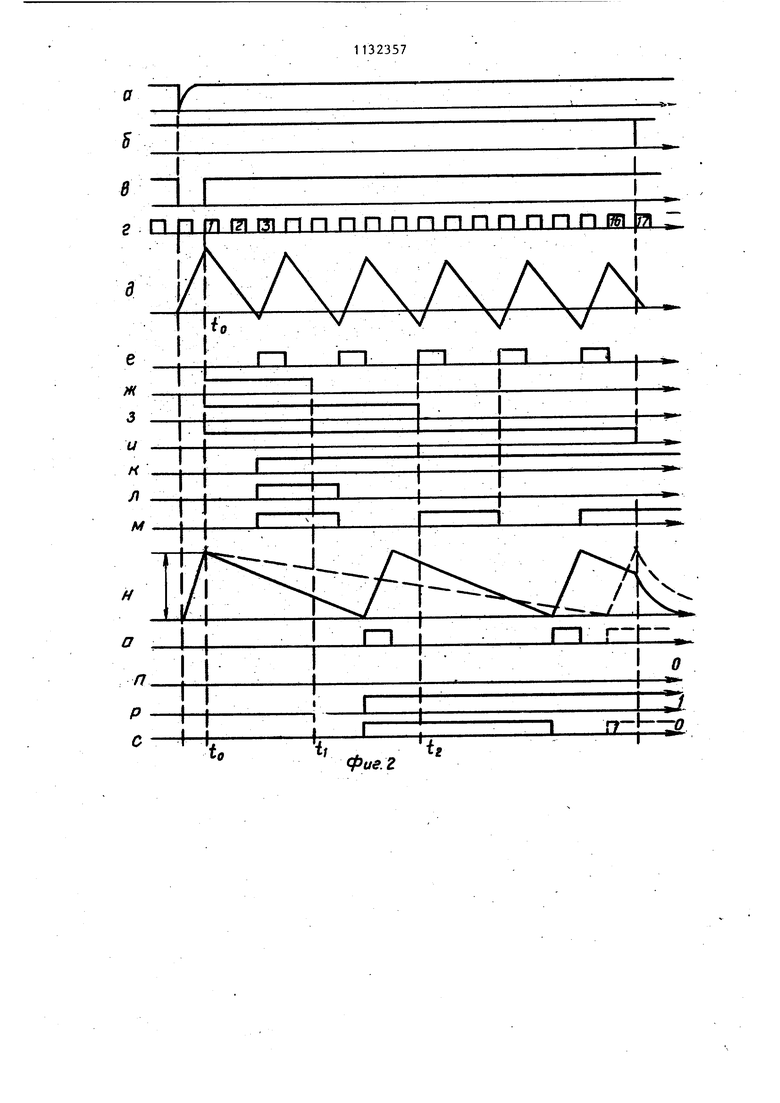

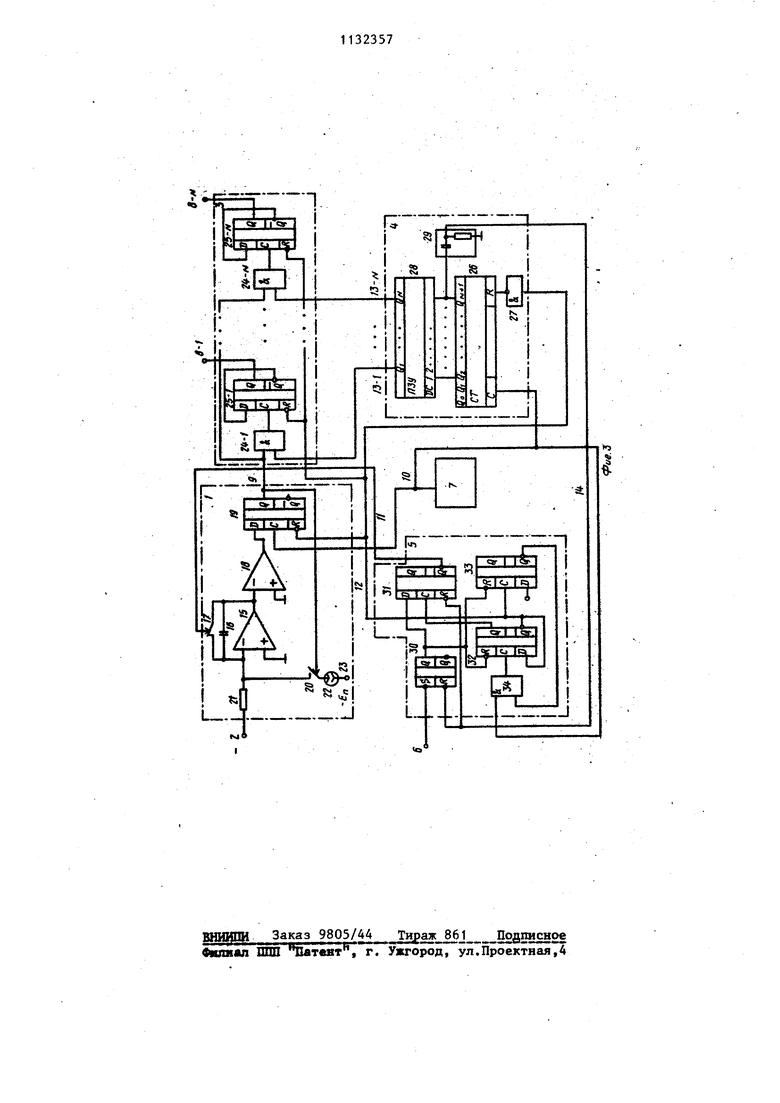

На фиг. 1 приведена структурная злектрическая схема аналого-цифрового преобразователя; на фиг. 2 - временные диаграммы, поясняющие работу устройства: О - сигнал запуска, О - сигнал окончания преобразования; b - сигнал на втором йыходе блока управления (сигнал сброса); 2 тактовые импульсы и - пилообразный сигнал на выходе интегрирующего операционного уси.лителя преобразователя напряжения в частоту; е - сигналы на выходе преобразователя напряжения в частоту - сигнал на первом выходе блока формирования временных интервалов; « - сигнал на втором выходе блока формирования временных интервалов} О - сигнал на третьем выходе блока формирования временньпс интервалов; ц - сигнал на первом выходе блока счетчиков импульсов (старший разряд устройства), Л - сигнал на втором выходе блока счетчиков импульсов (второй разряд устройства) М - сигнал на третьем выходе блока счетчиков импульсов (мпадщий разряд устройства); Н - сигнал на выходе интегрирующего операционного усилителя преобразователя напряжения в час тоту для входного сигнала меньшего по величине, чем в случае, приведенном на диаграмме d, соответствующий этому новому входному сигналу 6 - сигнал на выходе преобразователя напряжения в частоту; Л - сигнал на первом выходе блока формирования временных интервалов, р - сигнал на второмвыходе блока формирования временных интервалов;с - сигнал на тоетьем выхогте блока Аоомиопвяния временных интервалов; на фиг. 3 принципиальная схема аналого-цифрового преобразователя.

Аналого-цифровой преобразователь содержит преобразователь 1 напряжения в частоту, вход 2 которого является входом устройства, а выход соединен с тактовым входом блока 3 счетчиков импульсов, блок А формирования временных интервалов, первый выход которого соединен с первьм управляющим входом блока 3 счетчиков импульсов, первьй вход блока 5 управления является входом 6 запуска устройства, второй вход соединен с выходом генератора 7 тактовых импульсов, первым управляющим входом преобразователя 1 Напряжения в частоту и первьм входом блока 4 формирования временных интервалов, первьй - выход -г со вторым управляющим входом преобразователя 1 напряжения в частоту, а второй выход - со входами .сброса блока 3 счетчиков импульсов, блока 4 формирования временных интервалов и третьим управляющим входом преобразователя 1 напряжения в частоту, группа выходов с первого по И-и блока 4 формирования временных интервалов соединена с соответствующей группой управляющих входов блока 3 счетчиков импульсов, aN+1-й выход - с третьим входом блока 5 управления. Кроме того, устройство содержит выходные шины (8-1)-(8-N), выходную шину 9 преобразователя напряжения в частоту, шину тактовых импульсов 10, первую шину управления 11, шину сброса 12, шины управления (13-1)-(13-КО блоком 3 счетчиков импульсов,шину окончания преобразований 14. Преобразователь 1 напряжения в частоту (фиг.З) содержит операционный усилитель 15, параллель нр соединенные конденсатор 16 и аналоговый ключ 17, подключенные между инвертирующим входом и выходом опера ционного усилителя 15, выход котсч ого подключен к инвертирующему входу компаратора 18, неинвертирукмций вход которого соединен с неинвертирующим входом операционного усилителя 15 и общей шиной устройства, а выход соединен с D -входом тактируемого D-триггера 19, С-вход которого соединен шиной 10 с выходом генерато-. ра 7 тактовых импульсов,R -вход с шиной сброса 12, а прямой выход с управляющим входом разрядного .ключа 20 и выходной шиной 9 преобразователя напряжения в частоту, вход Vл, 2 устройства через резистор 21 соеди нен с инвертирующим входом операцион ного усилителя 15 и входом разрядного ключа 20, выход которого через источник разрядного токе 22 соединен -с шиной 23 отрицательного источника питания, управляющий вход аналогового ключа 17 соединен с первой шиной 11 управления. Блок 3 счетчиков имАнапого-цифровой преобразователь работает следующим образом. пульсов содержит логические элементы И (24-1)-(24-Ю , первые входы которых соединены с выходной шиной 9 преобразователя 1 напряжения в частоту, вторые входы соединены с шинами ()-( 13-N) управления блоком 3 счетчиков импульсов, а выходы - с С-входами счетчиков (25-1)-(25-Ю импульсов, R-входы соединены с шиной сброса 12, а группа выходов каждого счетчика образует группу выходных шин (8-1)-(8-К|) устройства (в частном случае, приведенном на фиг. 3, каждый счетчик импульсов (25-1)(25-N) реализован на тактируемом D-триггере, включенном в счетном режиме, при этом количество счетчиков импульсов равно числу разрядов выходного кода устройства). Блок 4 формирования временных интервалов содержит управляющий счетчик 26 импульсов, С-вход которого соединен шиной тактовьк Импульсов 10 с выходом генератора 7 тактовых импульсов, R-вход - с выходом инвертора 27, вход которого соединен с шиной сброса 12. Выход с Qo noQ f) соединены с адресными входами постоянного запоминающего устройства 28, выходы которого соединены с шинами (13-1)(13-N) блока 3 счетчиков импульсов, вькодО соединен через дифференцирующую цепь 29 с шиной окончания преобразования 14. управления содержит Я5 -триггер 30,5 -вход которого соединен со входом запуска 6 устройства, -вход - с N+1-м выходом блока 4 фор мирования временных-интервалов и R-входом третьего тактируемого D -тригге1 а 31, а Q -выход с,R-входами первого и второго тактщ уемых1)-триггеров 32 и1)-входом гретьего тактируемого .0 -триггера 31,Q -выход которого соединен с пер-. « выходом блока 5 управления, а -вход соединен сЩ-выходом первого та стируемого J) -триггера 32, D -вход и Q-выход которого соединены со вторым выходом блока 5 управления и С-входом второго тактируемого ,-, ,Hj-cnui. iiJ-триггера 33, О-выход которого соединен с первым входом логического элемента И 34, второй вход которого соединен с выходом генератора тактовькимпульсов 7,авыход-с С- входомпервого тактируемого )-триггера 32 .

На входе 2 преобразователя 1 установлен аналоговый сигнал. При поступлении на вход 6 блока 5 сигнала запуска (фиг,2а) и первого тактового импульса от генератора 7 на вто ром входе блока 5 формируется сигнал сброса (фиг.2)), :длительность которого равна периоду тактовых импульсов. По сигналу сброса устанавливаются в О счетчики блоков 3 и 4 и D-триггер преобразователя 1. В течение длительности импульса сброса интегратор преобразователя 1 устанавливается в исходное состояние выумо,.2д и К). С выхода преобразователя 1 в блок 3 по шине 9 поступают тактовые импульсы (фиг.2е), которые проходят на тактовые входы всех)-триггеров (25-1)-(25-М) через элементы И (24-1)-(24-N)j на вторые входы которых по первому тактовому импульсу поступают сигналы управления из блока 4 (фиг.2Ж, , U ,шины (13-1)(13-N). Длительность сигналов управления для 1 -го триггера составляет Tnpi , где С - период следрвания тактовых импульсов, 1-N. Выходные сигналы триггеров приведены на ,фиг. 2 If , Л к .М- При поступлении с выхода преобразователя 1 импульса в течение интервала tQ-t( триггер 25-1 блока 3 установится в состояние 1 (фиг.2Л;), а при меньшем входном сигнале (фиг.2 «) триггер 25-1 останется в состоянии О (фиг.2 л), Таким образом, оказывается сформированным старший разряд выходного крда устройства. Триггер 25-2 осуществляет счет импульсов с выхода преобразователя 1 в ; ечение интервала ifl-tj. Далее процесс формирования выходного кода происходит аналогично.до фop шpoвaния мпадшего разряда выходного кода. По завершеНИИ интервала преобразования (фиг.2 блок 4 вьфабатываёт сигнал окончания интервала преобразования Тфиг.28) который поступает по шине 14 на блок 5, на первом выходе которого появляется сигнал обнуления интегра тбра преобразователя 1. Поступление импульсов по шине 9 прекращается, на шинах (13-1)-() устанавлива тся нулевые сигналы, а на выходах блок 3 присутствует код входного сигнала .

Код старших разрядов при этом фopмиpJrвтcя до окончания цикла npeoразования и может быть сразу же отправлен на обработку, причем автоматически организуется последовательный вывод информации, чем и достигается расширение функциональных возможностей устройства. В известном устройстве 2J информация может быть получена только по окончании полного цикла преобразования.

Преобразователь 1 (фиг.З) работает следуняцим образом.

При поступлении логического О со второго выхода блока 5 на R -вход D-триггера 19 появляется сигнал 1 на его выходе Q. Одновременно с первого выхода блока 5 поступает О,осуществляющий размыкание ключа 17. Интегратор, построенный на усилителе 15, конденсаторе 16 и резисторе 21, натинает интегрирование разности разрядного и входного токов в течение длительности периода тактовых импульсов Z (фиг.2д, момент 0-4: ). При этом напряжений на выходе усилителя 13 становится равным

IP-I

вх

и

вых так

- значение разрядного

где тока источника 22,

/R - входной ток,

U g -.входное напряжение, R - сопротивление резистора 21.

При поступлении первого тактового импульса на выходе Q триггера 19 устанавливается О, разрядный ключ 20 размыкается, генератор 22 отключается от входа усилителя 15, напряжение на выходе которого начинает уменьшаться. При достижении этим напряжением О на выходе компаратора 18 появляется 1 и при поступлении на С-вход триггера 19 тактового импульса на его выходе CJ появляется 1, замыкается ключ 20 -и начинается интегрирование величины 1 - Г . По сл.едукийему тактовому импульсу состояние триггера 19 изменяется на О, и тем самым на выходе преобразовател 1 формируется импульс длительностью С- .

Далее процесс повторяется. Вход-ное напряженке преобразователя ока- зывается пропорционально средней час тоте следования импульсов по шине 9 .

Блок 5 осуществляет по первому выходу формирование сигнала размы, 9. кзния ключа 17 на время Трр +D , а по второму выходу - формирование си нала-сброса длительностью L следующим образом. запуска поступает на 5-вход йб-триггера 30, при этом на его выходе Q появится 1, которая подготавливает срабатывание третьегоD-триггера 25 и вызьшает установку первого и второго D-тригг ров 32 и 33 по выходам Q в состояние 1, чти открьгоает элемент 34 И Для поступления тактовьк импульсов от генератора 7.Поступление нулевого тактового импульса (фиг.22) вызьгаает переброс триггера 32 в состояние Q 1 5 О (шина 12). О-триггер 31 устанавливается при этом по выходу 9 в О. Первый тактовый импульс вызывает обратный переброс Г -триггера 32, на его выходе q, (шина 12) появляется сигнал 1 (сформирован сигнал сброса, фиг.2В что в свсяо очередь вызьтвает перебро Й-триггера 33 по выходуQ в состояние О, элемент ЗА И закрывается и не пропускает тактовые импульсы. При поступлении сигнала 14 окончания преобразования 5-триггер 30 и 3 -триггер 35 перебрасываются, при этрм на Q-выходе последнего появляется l (сформирован сигнал замыкания ключа 17), а наQ -выходах ЗЗ-триггеров устанавливается состояние 1. При поступлении нового импул са запуска процесс повторяется. Блок 4 осуществляет формирование управляющих сигналов фиксированной дпительности для :блока 3. Управляющий счетчик 26 сбрасывается в О п шине 12 и Далее осуществляет счет тактовых импульсов. Постоянное запоминающее устройство 28 осуществля ет дешифрирование состояний управля щего Счетчика 26 и формирует на вьпсодных шинах (13-1 )-() управляющие сигналы длительностью 2 L (фиг.2 , J , U ). Блок 3 осуществляет счет импульсов с выхода преобразователя 1, который гфоисхрдит при подаче на упра ляющие входы блока 3 сигналов 1. В качестве базового объекта принят анал ого-цифровой пр еобр аз овател ь 2j Указанное устройство по сравнению с предлагаемым обладает рядом суще ственных недостатков, а именно счит 5710 вание выходного кода с него возможно только после окончания цикла преобразования, т.е. состояние ни .одного из разрядов выходного кода не определено до окончания цикла преобразования. Современные цифровые процессоры производят обработку информации по 2, 4, 6 разрядов и в том случае, если бы аналого-цифровой преобразователь обеспечил вьщачу кода группами по указанному числу разрядов до окончания цикла преобразования, то время обработки информдции для системы аналого-цифровой преобразователь-процессор существенно снизилось. Предлагаемый аналогоцифровой преобразователь позволяет устранить указанный недостаток.базового объекта. Кроме того, отпада- ет необходимость введения дополнительного интерфейса для связи с цифровыми процессорами, так как предлагаемое устройство позволяет легко изменить длину групп выходного кода, основание счета группы и т.д. При этом реализагщя изобретения позволяет повысить помехоустойчивость аналого-цифрового преобразователя. Сбои в работе алгоритма АЦП происходят в основном из-за сбоев счетчика импульсов и вероятность сбоя максимальна для триггера младшего разряда i выходного счетчика. Поскольку в базовом устройстве возможен перенос импульса по всему счетчику вплоть до его старшего разряда, то любой сбой в младшем разряде может изменить и состояние старшего разряда вькодного кода. Старшие разряды кода в данном изобретении не связаны с младшими, счет импульсов в них происходит за меныше промежутки времени и вероятность сбоя в старших разрядах существенно ниже, чем в базовом устройстве. Таким образом, введение в известное устройство генератора тактовых импульсов, блока управления, изменение конструкдаи преобразователя на-пряжения в частоту и блока формирования временных динтервалов позволило существенно расширить функциональные возможности устройства при одновременном повышении его помехоустойчивости.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Бахтияров Г.Д | |||

| и др | |||

| Аналого-цифровые преобразователи | |||

| М., Советское радио, 1980, с | |||

| Система механической тяги | 1919 |

|

SU158A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Там же, с | |||

| Аппарат для передачи изображений на расстояние | 1920 |

|

SU171A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1984-12-30—Публикация

1983-05-30—Подача