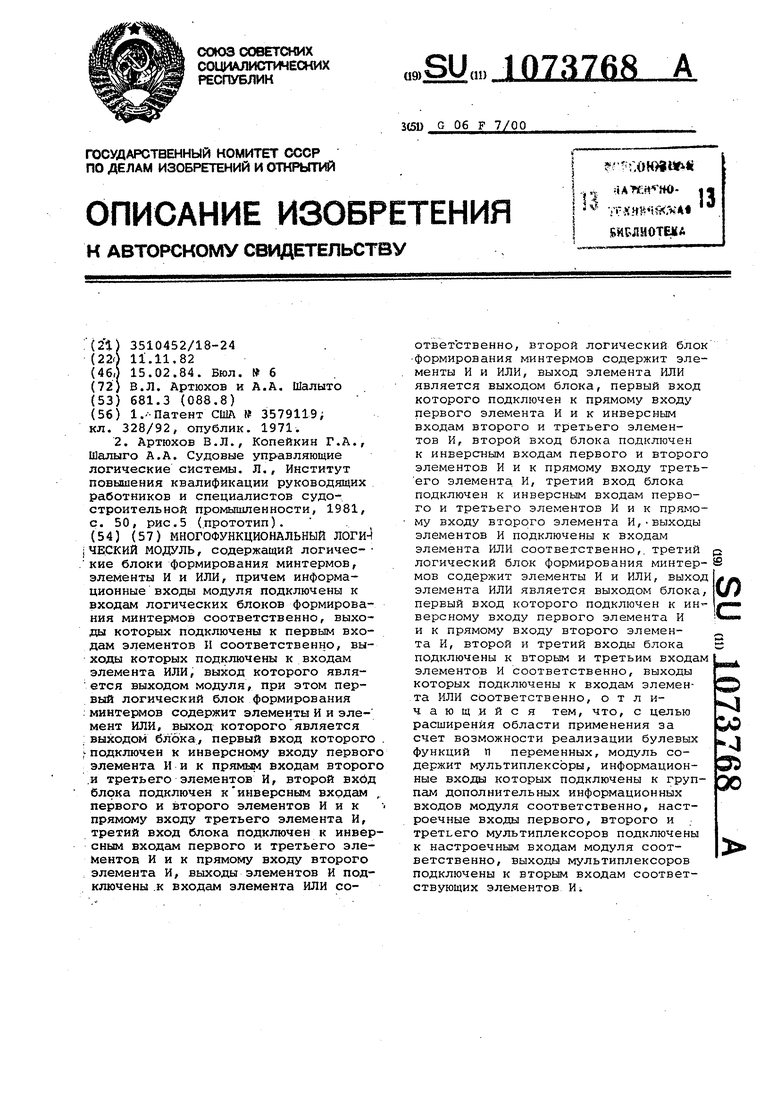

Изобретение относится к области автоматики и вычислительной техники и предназначено для реализации путем настройки произвольных булевых функций п переменных.

Известен многофункциональный логический модуль, содержащий логические элементы и пред ваз наченнь: для реализации произвольных булевых функций п переменных ij .

Недостатком этого модуля является большое число его входов, определяемое соотношениями:

М(п) п + 2

при подаче констант О и 1 на настроечные входы;

М,(п) п - 1 +

при подаче констант О и 1, а также переменной Ху, и ее инверсии на настроечные входы.

Наиболее близким к предложенному по технической сущности- является многофункциональный логический модуль, содержащий три информационных и три настроечных входа, один выход три блока для реализации дизъюнкций минтермов, удовлетворяющих условию избирательности, трех переменных с тремя входами и одним выходом каждый, три двухвходовых элемента И и один трехвходовой элемент ИЛИ, причем i-й информационный вход (i - 1, 2,3) соединен с 1-м входом каждого из блоков, выход i-ro блока и i-й настроечный вход соединены соответственно с первым и вторым входами i-ro элемента И, выходы элементов И соединены с i-M входом элемента ИЛИ, выход которого соединен с выходом модуля 2 ,

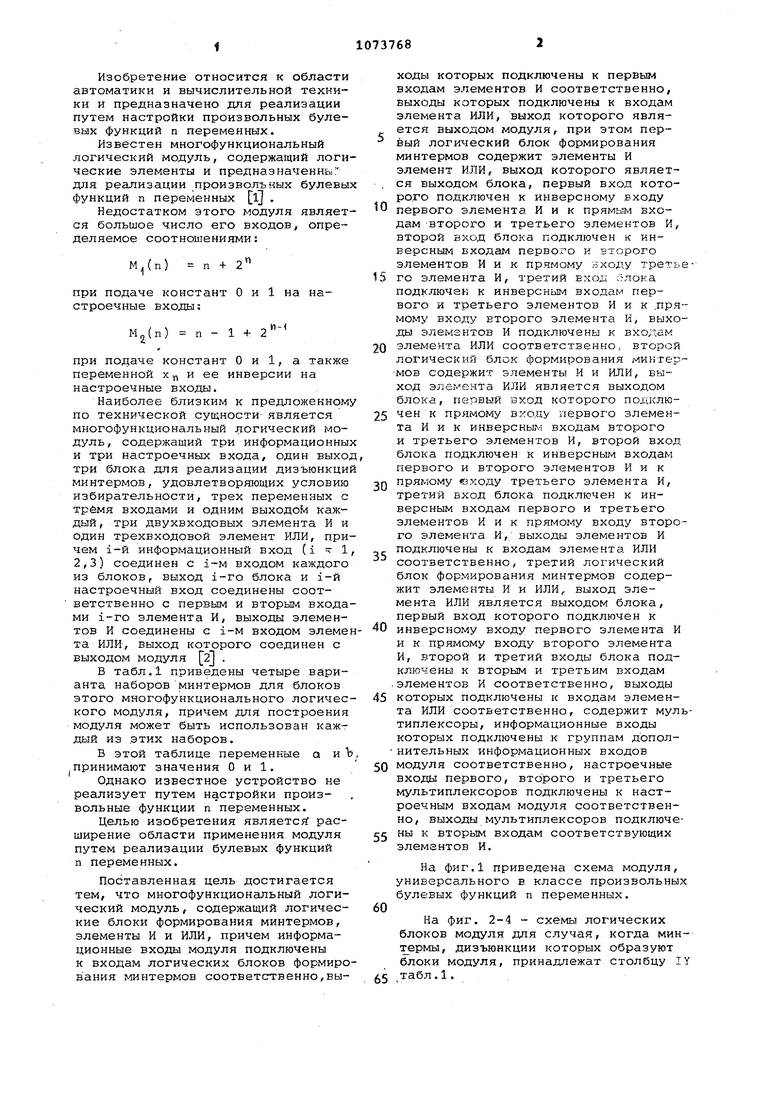

В табл.1 приведены четыре варианта наборовминтермов для блоков этого многофункционального логического модуля, причем для построения модуля может быть использован каждый из .этих наборов.

В этой таблице переменные а и Ъ принимают значения О и 1.

Однако известное устройство не реализует путем настройки произвольные функции п переменных.

Целью изобретения являетс5 расширение области применения модуля путем реализации булевых функций п переменных.

Поставленная цель достигается тем, что многофункциональный логический модуль, содержащий логические блоки формирования минтермов, элементы И и ИЛИ, причем информационные входы модуля подключены к входам логических блоков формирования минтермов соответственно,выходы которых подключены к первым входам элементов И соответственно, выходы которых подключены к входам элемента ИЛИ, выход которого является выходом модуля, при этом первый логический блок формирования минтермов содержит элементы И элемент ИЛИ, выход которого является выходом блока, первый вход которого подключен к инверсному входу первого элемента И и к прямьэд входам второго и третьего элементов И, вторюй вход бпока подключен к инверсным входам первого и второго элементов И и к прямому входу третьго элемента И, третий вход блока подключен к инверсным входам первого и третьего элементов И и к .прямому входу второго элемента И, выходы элементов И подключены к входам элемента ИЛИ соответственно, второй логический блок формирования минтермов содержит элементы И и ИЛИ, выход элегиента ИЛИ является выходом блока, первый вход которого подключен к прямому Б;-ГОДУ первого элемента И и к инверснььм входам второго и третьего .элементов И, второй вход блока подключен к инверсным входам первого и второго элементов И и к прямому «зходу третьего элемента И, третий вход блока подключен к инверсным входам первого и третьего элементов И и к прямому входу второго элемента И,; выходы элементов И подключены к входам элемента. ИЛИ соответственно, третий логический блок формирования минтермов содержит элементы И и ИЛИ, выход элемента ИЛИ является выходом блока, первый вход которого подключен к инверсному входу первого элемента И и к прямому входу второго элемента И, второй и третий входы блока подключены к вторым и третьим входам

.элементов И соответственно, выходы которых подключены к входам элемента ИЛИ соответственно, содержит мултиплексоры, информационные входы которых подключены к группам дополнительных информационных входов модуля соответственно, настроечные входы первого, второго и третьего мультиплексоров подключены к настроечным входам модуля соответственно, выходы мультиплексоров подключены к вторым входам соответствующих элементов И,

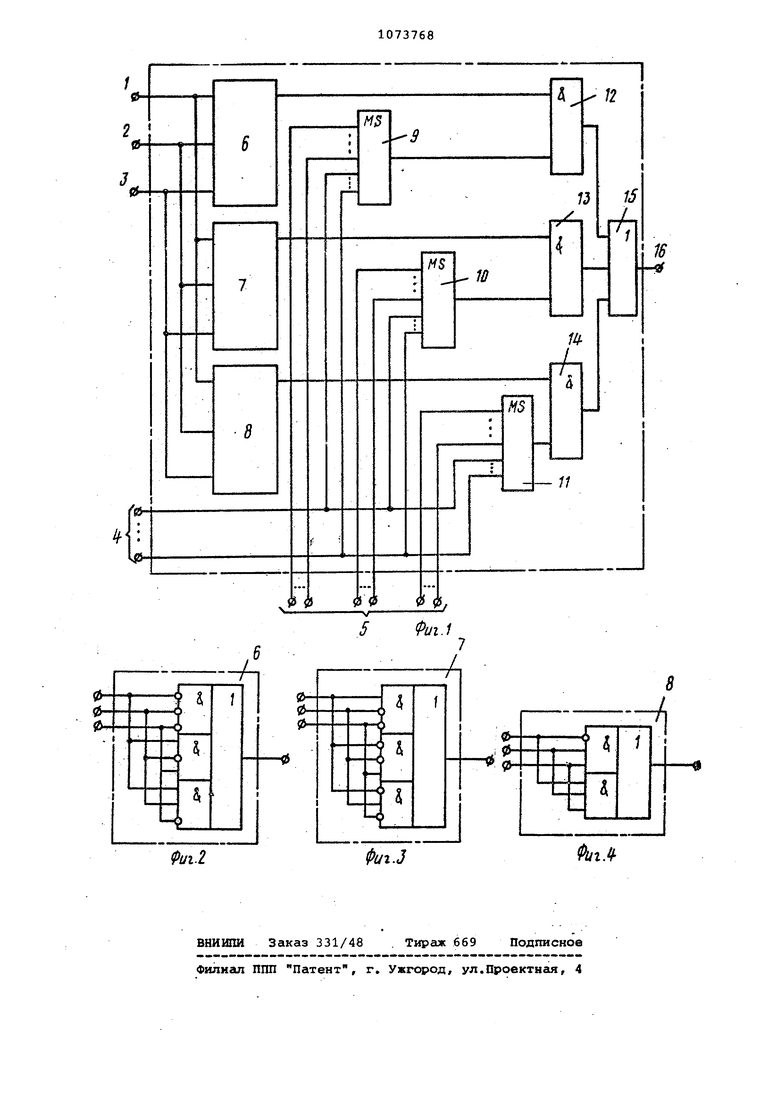

На фиг.1 приведена схема модуля, универсального в классе произвольны булевых функций п переменных.

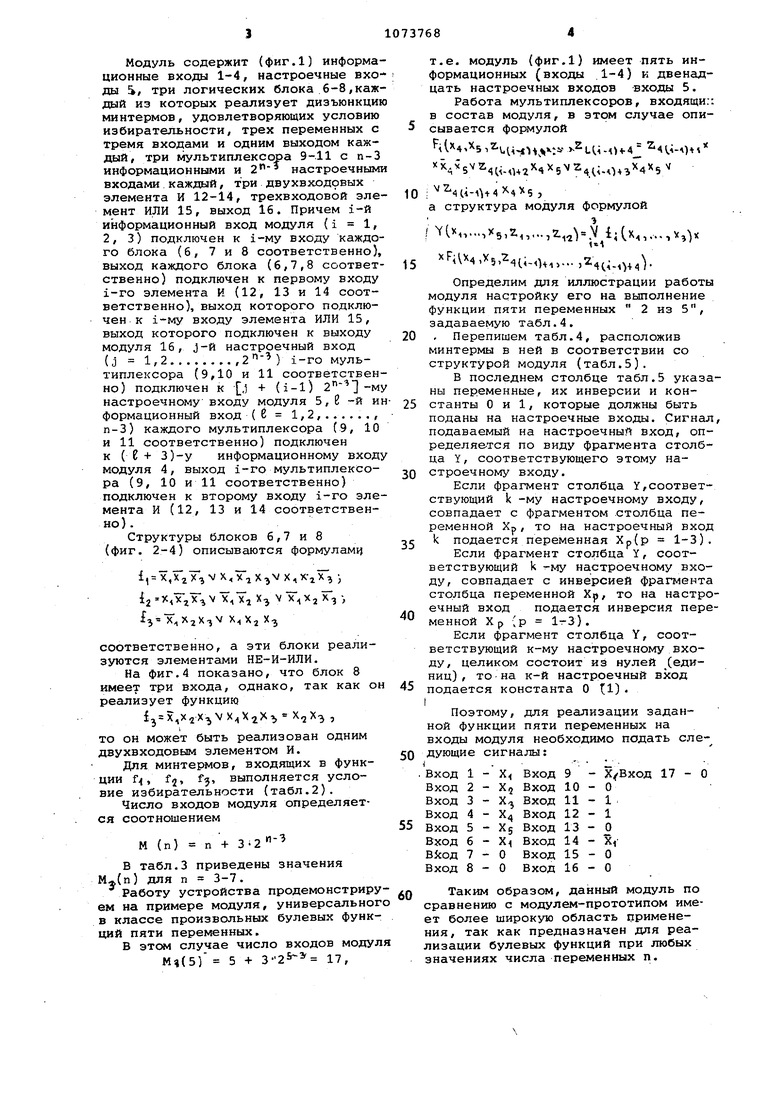

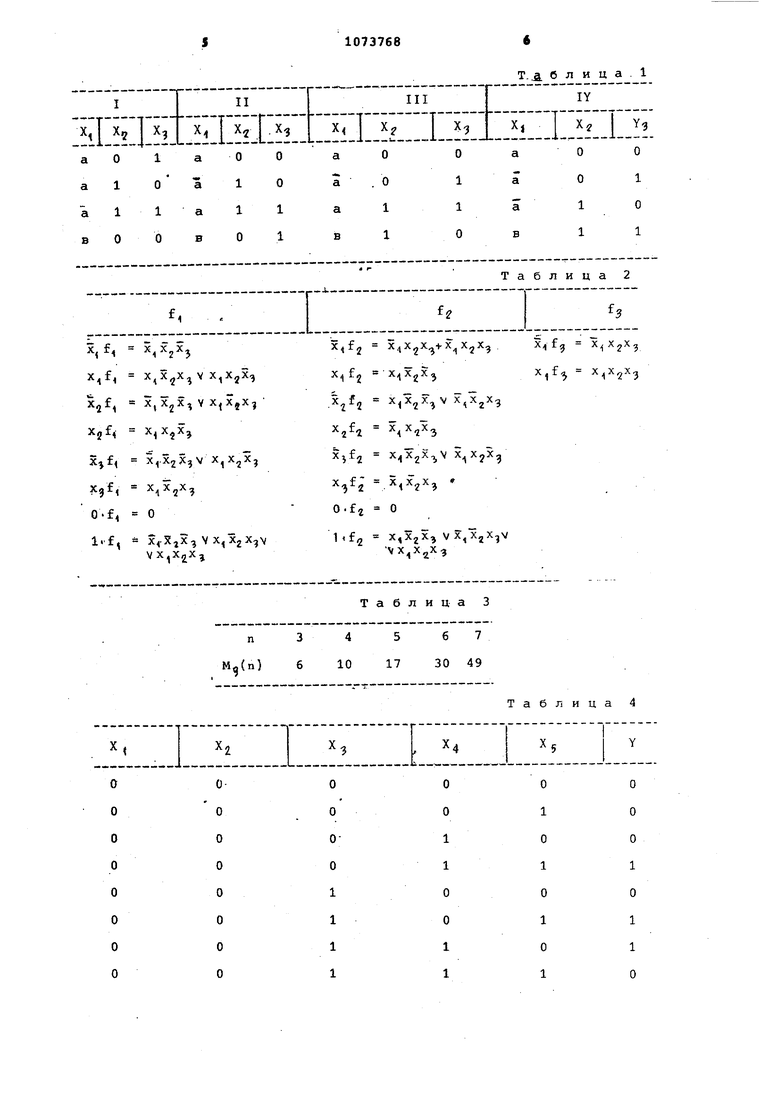

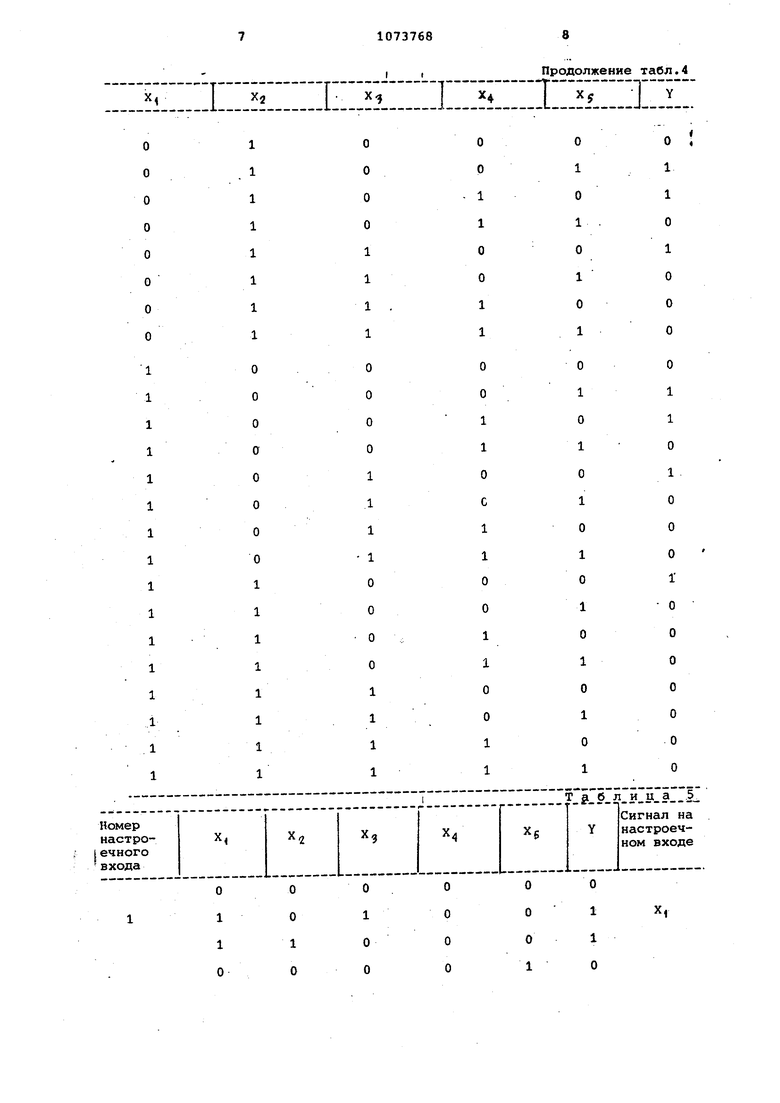

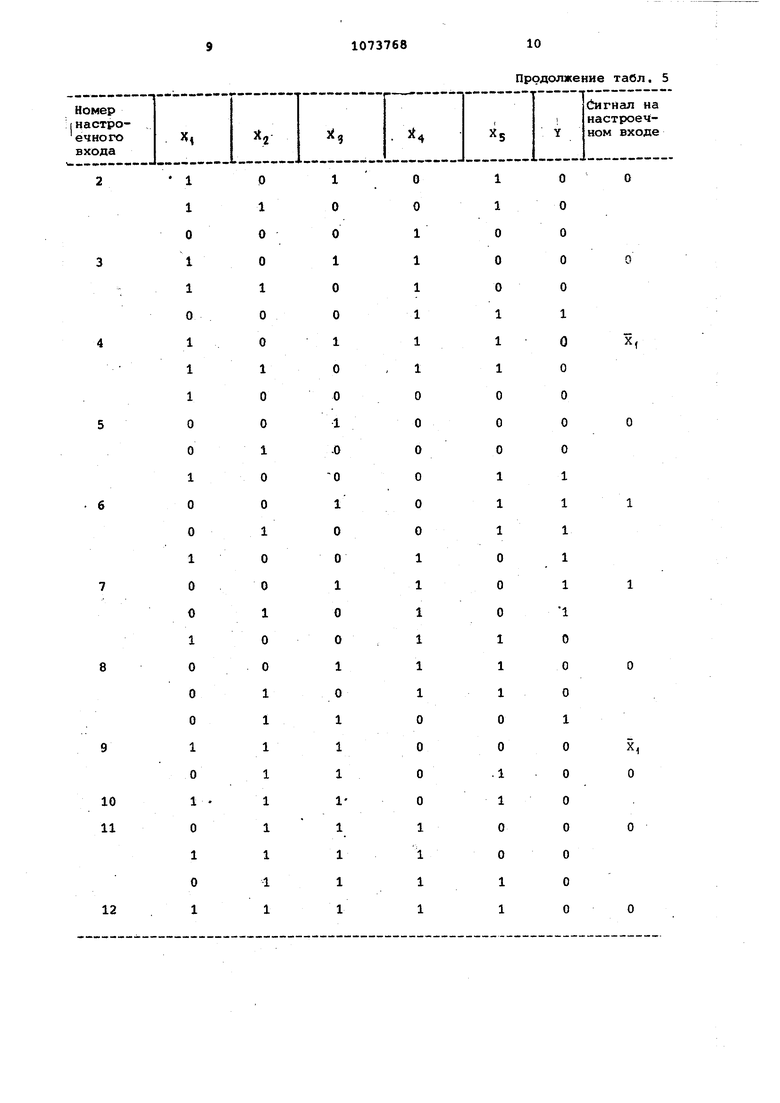

На фиг. 2-4 - схемы логических блоков модуля для случая, когда минтермы, дизъюнкции которых образуют блоки модуля, принадлежат столбцу I табл. 1. Модуль содержит (фиг.1) информационные входы 1-4, настроечные вхо ды S, три логических блока 6-8,каж дый из которых реализует дизъюнкцию минтермов, удовлетворяющих условию избирательности, трех переменных с тремя входами и одним выходом каждый, три мультиплексора 9-11 с п-3 информационными и настроечным входами каждый, три двухвходовых элемента И 12-14, трехвходовой эле мент ИЛИ 15, выход 16. Причем i-й информационный вход модуля (, 2, 3) подключен к i-му входу каждого блока (б, 7 и 8 соответственно), выход каждого блока (6,7,8 соответственно) подключен к первому входу i-ro элемента И (12, 13 и 14 соответственно), выход которого подключен к i-му входу элемента ИЛИ 15, выход которого подключен к выходу модуля 16, j-й настроечный вход (j 1,2,) i-ro мультиплексора (9,10 и 11 соответственно) подключен к , + (i-l) настроечному входу модуля 5,6 -и ин формационный вход (6 1,2,...,.., п-3) каждого мультиплексора (9, 10 и 11 соответственно) подключен к (6+ 3)-у информационному входу модуля 4, выход i-ro мультиплексора (9, 10 и 11 соответственно) подключен к второму входу i-ro элемента И (12, 13 и 14 соответственно). Структуры блоков 6,7 и 8 (фиг. 2-4) описываются формулами , х,хгТ, V x,,v , ; ij V Х V х, -, соответственно, а эти блоки реализуются элементами НЕ-И-ИЛИ. На фиг.4 показано, что блок 8 имеет три входа, однако, так как он реализует функцию f, X,, , то он может быть реализован одним двухвходовым элементом И. Для минтермов, входящих в функции f, fj, f-}, выполняется условие избирательности (табл.2). Число входов модуля определяется соотношением М (п) п + табл.3 приведены значения М(п) для п 3-7. Работу устройства продемонстрируем на примере модуля, универсального в классе произвольных булевых функций пяти переменных. В этом случае число входов модуля М«(5) 5 + 3-2 17, т.е. модуль (фиг.1) имеет пять информационных (входы .1-4) и двенадцать настроечных входов входы 5. Работа мультиплексоров, входящи;: в состав модуля, в этом случае описывается формулой .l,(, ,i-iK4 4(,;-) .. ; J a структура модуля формулой Y(x,,...,X5,z,,...,z,) i(x,,...,v,)x ,,24(.;MH4V Определим для иллюстрации работы модуля настройку его на выполнение функции пяти переменных 2 из 5, задаваемую табл.4. , Перепишем табл.4, расположив минтермы в ней в соответствии со структурой модуля (табл.5). В последнем столбце табл.5 указаны переменные, их инверсии и константы О и 1, которые должны быть поданы на настроечные входы. Сигнал, подаваемый на настроечный вход, определяется по виду фрагмента столбца Y, соответствующего этому настроечному входу. Если фрагмент столбца Y,соответствующий k -му настроечному входу, совпадает с фрагментом столбца переменной Хр, то на настроечный вход подается переменная Хр(р 1-3). Если фрагмент столбца Y, соответствующий k му настроечному входу, совпадает с инверсией фрагмента столбца переменной Хр, то на настроечный вход подается инверсия переманной Хр (р 1-3). Если фрагмент столбца Y, соответствующий к-му настроечному входу, целиком состоит из нулей (единиц), тона к-й настроечный вход подается константа О tl) Поэтому, для реализации заданной функции пяти переменных на входы модуля необходимо подать слеующие сигналы: . -. ход 1 - Х Вход 9 - Х -Вход 17-0 ход 2 - Xj Вход 10-0 ход 3 - Х Вход 11-1 ход 4 - Х Вход 12-1 ход 5 - Xj Вход 13 - О ход 6 - Х Вход 14 - X, 5сод 7-0 Вход 15-0 ход 8-0 Вход 16-0 Таким образом, данный модуль по равнению с модулем-прототипом имет более широкую область применеия, так как предназначен для реаизации булевых функций при любых начениях числа переменных п.

Т.блица.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный логический модуль | 1980 |

|

SU924697A1 |

| Многофункциональный модуль | 1983 |

|

SU1096636A1 |

| Многофункциональный логический модуль | 1982 |

|

SU1149244A1 |

| Ячейка однородной структуры | 1987 |

|

SU1418695A1 |

| Ячейка однородной структуры | 1988 |

|

SU1573456A1 |

| Ячейка однородной структуры | 1983 |

|

SU1092492A1 |

| Ячейка однородной структуры | 1988 |

|

SU1501035A2 |

| МНОГОФУНКЦИОНАЛЬНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2015 |

|

RU2610247C1 |

| Программируемое устройство | 1991 |

|

SU1789979A1 |

| Устройство для реализации логических функций | 1981 |

|

SU1001080A1 |

МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧ i ЧЕСКИЙ МОДУЛЬ, содержащий логичес- .кие блоки формирования минтермов, элементы И и ИЛИ, причем информационные входы модуля подключены к входам логических блоков формирования минтермов соответственно, выходы которых подключены к первым входам элементов И соответственно, выходы которых подключены к входам элемента ИЛИ, выход которого явля ется выходом модуля, при этом первый логический блок формирования минтермов содержит элементы И и элемент ИЛИ, выход которого является : выходом блока, первый вход которого . Подключен к инверсному входу первого элемента И и к прямым входам второго и третьего элементов И, второй вхбд блока подключен кинверсным входам первого и второго элементов И и к прямому входу третьего элемента И, третий вход блока подключен к инверсным входам первого и третьего элементов И и к прямому входу второго : элемента И, выходы элементов И подключены .к входам элемента ИЛИ соответственно, второй логический блок формирования минтермов содержит элементы И и ИЛИ, выход элемента ИЛИ является выходом блока, первый вход которого подключен к прямому входу первого элемента И и к инверсным входам второго и третьего элементов И, второй вход блока подключен к инверсным входг1м первого и второго элементов И и к прямому входу третьего элемента. И, третий вход блока подключен к инверсным входам первого и третьего элементов Инк прямому входу второго элемента И,-выходы элементов И подключены к входам элемента ИЛИ соответственно,, третий логический блок формирования минтермов содержит элементы И и ИЛИ, выход (Л элемента ИЛИ является выходом блока, первый вход которого подключен к инверсному входу первого элемента И и к прямому входу второго элемента И, второй и третий входы блока подключены к вторым и третьим входам элементов И соответственно, выходы которых подключены к входам элемента ИЛИ соответственно, отли -4 чающийся тем, что, с целью со расширения области применения за счет возможности реализации булевых | функций п переменных, модуль со держит мультиплексоры, информационные входал которых подключены к груп00 пам дополнительных информационных входов модуля соответственно, настроечные входы первого, второго и третьего мультиплексоров подключены к настроечным входам модуля соответственно, выходы мультиплексоров подключены к вторым входам соответствующих элементов И

.

,

Х V

X In - ХцХлХ

Х.

, V ,

X XjX

2 4 3

- - .-

АгТл

x.

x O.fj 0

0

x,X2X,

x X,x V X,

VX,X,jX

Xjl-a -

,jX

X,

X2

1 1 1 1 1 1 1 1

0 0 0 0 0 0 0 0

1 1 1 1 1 1 a 1

Продолжение табл.4

I I

:I:E::::I XyI Y

0

0 Q

0

1

1 1

1 1

0

1

0

1

0

0

1

0

0 0 0

0

1 1

1

0

0 0

0

1

1

1 1

0

1

1

0

0

1

0

1

с 1 1

0 0 0

0

1

1

0

0 0

1 0

0 0 0 0 0 0

0

1

1

1

0

0 0

1

0

1 1

1

1 о о 1 о о 1 о о 1

1 1 О 1 1 О 1 1 1 О

о 1 о о 1 о о 1 о о 1 о о 1 о о 1 о о 1 1 1 1 1 1 1 1 1

-О

о 1 о о 1 о о 1 о о о 1 о 1 о 1 о 1 Q

1

о

о

1

о

о

1

о

1

1

1

0 11

1

1

1

1

2

1

Продолжение табл. 5

1 1 о о о 1 1 1 о о о 1 1 1 о о о 1 1 1 о о

о о о о о 1 о

о о о о 1 1 1 1 1 1 о о о 1 о о о о о о о .1 1 о о 1 1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ переработки сплавов меди и цинка (латуни) | 1922 |

|

SU328A1 |

| Устройство станционной централизации и блокировочной сигнализации | 1915 |

|

SU1971A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Артюхов В.Л., Копейкин Г.А., Шалыго А.А | |||

| Судовые упр-авляющие логические системы | |||

| Л., Институт повьаиения квалификации руководящих работников и специалистов судостроительной промышленности, 1981, с | |||

| Устройство для выпрямления многофазного тока | 1923 |

|

SU50A1 |

Авторы

Даты

1984-02-15—Публикация

1982-11-11—Подача