Ьп

:о со

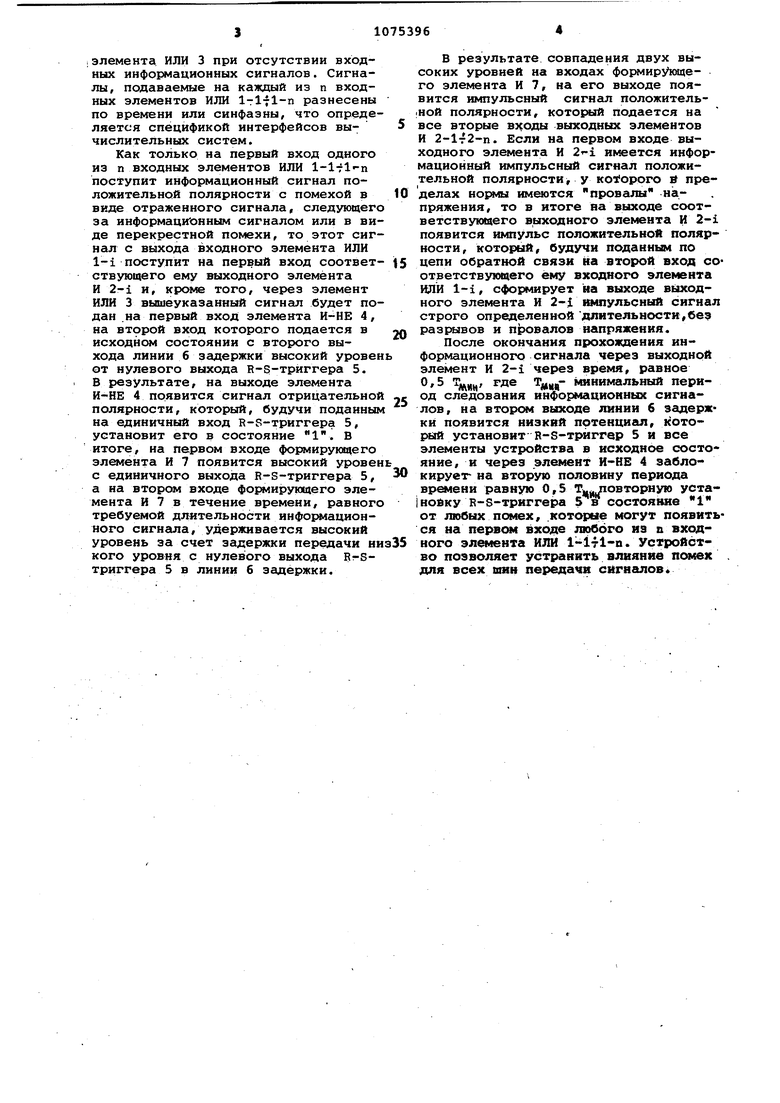

СП Изобретение относится к импульсной технике и может быть использовано, в частности, в аппаратуре приема информации для защиты от импульсных помех. Известно устройство подавления узкополосных .помех, содержащее последовательно соединенный фильтр, перемножитель и вычислитель, другой вход которого является входом устройства Г1 . Однако это устройство вносит искажение в сигнал и имеет низкую эф|фективность работы, так как не обеспечи вает защиту от импульсных помех, длительность которых меньше длительности информационных сигналов. Наиболее близким к изобретению по технической сущности является устройство для защиты от импульсных помех, содержащее подключенный к шине входного сигнала вентиль управления (эле мент и), к одному из входов управления которого подключен выход R-S-триг гера блокировки, на другой вход управ ления которого поданы тактовые импул сы, а выход вентиля управления через линию задержки подключен к одному из входов выходного вентиля, и последова тельно соединенные инвертор и вентил сброса, при этом информационный вход вентиля управления соединен с входом инвертора, выход которого подключен другому входу выходного вентиля, на вход управления которого поданы такто вые импульсы, а выход вентиля сброс подключен к установочным входам элемента задержки и триггера блокировки к входу которого подключен дополнительный выход линии задержки 2 . Недостатком таких устройств является низкая помехозащищенность. Цель изобретения - повышение помехозащищенности . Поставленная цель достигается тем, что в устройство для защиты от импульсных ncJMex, содержащее элемент И, линию задержки, R-S-триггер, шины входных сигналов, введены п входных элементов ИЛИ, элемент И-НЕ, п выходных элементов И и элемент ИЛИ, вхо ды которого подключены к п шинам входных сигналов и первым входам п входных элементов ИЛИ, а выход - к первому входу элемента И-НЕ, подключенного своим выходом к единичному входу R-S-триггера, нулевой вход которого соединен с вторым входом элемента И-НЕ и вторым выходом линии задержки прямой выход F-S-триггера соединен с первым входом элемейта И, а инверсный выхбд - .с входом линии задержки, первый выход которой соединен с вторым входом элемента И, выход которого под ключен к вторым входам п выходных эле ментов И, при этом выход и первый вхо п элементов И подключены соответствен но к второму входу и выходу п элементов ИЛИ, На чертеже приведена принципиальная электрическая схема устройства для защиты от импульсных помех. Устройство для защиты от импульсных помех содержит п входных элементов ИЛИ l-lfln,n выходных элементов И 2-lj-2-n, элемент ИЛИ 3, элемент И-НЕ 4, R-S-триггер 5, линию 6 задержки и элемент И 7. Выходы п.входных элементов ИЛИ1-171-П подключены к первым входам п выходных элементов И 2-172-п , а выход элемента ИЛИ 3 через элемент И-НЕ 4, R-S-триггер 5, линию б задержки и элемент И 7 соединен с вторыми входами п выходных элементов И 2-1-72-П , выходы КОТО1ЯДХ соединены соответственно с первыми входами п входных элементов ИЛИ l-1-fl-n. Устройство для защиты от импульсных помех работает следующим образом. В исходном состоянии при отсутствии информационных сигналов на всех первых входах каждого из входных элементов ИЛИ установлен низкий уровень, и на выходе каждого из них устанавливается также низкий уро(вень, который подается на первые вхо-. ды соотв етствующих выходных элементов И 2-1т2-п, вторые входы которых закрыты низким уровнем. Тот же низкий уровень подается с выхода элемента ИЛИ 3 на первый вход элемента И-НЕ 4, на второй вход которого и на нулевой вход R-S-триггера 5 подается через второй выход линии 6 задержки высокий уровень с нулевого выхода R-S-триггера 5. I В результате на выходе элемента И-НЕ 4 устанавливается высокий уровень, который и подается на единичный вход триггера 5. Низкий же уровень с единичного выхода R-S-триггера 5. подается на первый вход формирующего элемента И 7, на второй вход которого с первого выхода линии 6 задержки подается высокий уровень, поступающий с нулевого выхода R-S-триггера 5. В результате, низкий уровень с выхода элемента И 7 закрывает вторые входы выходных элементов И , Если же, при включении питания и при отсутствии информационных сигналов на первых |ходах входных элементов ИЛИ й-1т1-п R-S-триггер 5 окажется..в состоянии 1, то низкий уровень с его нулевого выхода через второй выход линии 6 задержки поступит на нулевой вход R-S-триггера 5 и установит его в исходное состояние О, не изменив высокого уровня на выходе элемента И-НЕ 4, а значит и на единичном входе R-s-триггера 5, так как на первом входе элемента И-НЕ 4 поддерживается в исходном состоянии низкий уровень, подаваемый с выхода I элемента ИЛИ 3 при отсутствии входных информационных сигналов. Сигналы, подаваемые на каждый из п входных элементов ИЛИ 1т171 п разнесены по времени или синфазны, что определяется спецификой интерфейсов вычислительных систем. Как только на первый вход одного из п входных элементов ИЛИ l-l-rl-n поступит информационный сигнал положительной полярности с помехой в виде отраженного сигнала, следующего за информационным сигналом или в виде перекрестной помехи, то этот сигнал с выхода входного элемента ИЛИ 1-i поступит на первый вход соответствующего ему выходного элемента И 2-i и, кроме того, через элемент ИЛИ 3 вышеуказанный сигнал будет подан .на первый вход элемента И-НЕ 4, на второй вход которого подается в исходном состоянии с второго выхода линии б задержки высокий уровен от нулевого выхода R-s-триггера 5. В результате, на выходе элемента И-НБ 4 появится сигнал отрицательной полярности, который, будучи поданным на единичный вход R-s-триггера 5, установит его в состояние итоге, на первом входе формирующего элемента И 7 появится высокий уровен с единичного выхода R-s-триггера 5, а на втором входе формирующего элемента И 7 в течение времени, равного требуемой длительности инфО1 ационного сигнала, удерживается высокий уровень за счет задержки передачи ни кого уровня с нулевого выхода Rr-sтриггера 5 в линии 6 задержки. В результате совпгшения двух высоких уровней на входах формирующего элемента И 7, на его выходе появится импульсный сигнал положительной полярности, который подается на все вторые входы выходных элементов И 2-1т2-п. Если на первом входе выходного элемента И 2-i имеется информационный импульсный сигнал положительной полярности у которого и пределах нормы имеются провалы напряжения , то в итоге на выходе соответствующего выходного И 2-i появится импульс положительной полярности, который, будучи поданным по цепи обратной связи на второй вход соответствь ощего ему входного элемента ИЛИ 1-i, сформирует на выходе вьисодного элемента И 2- импульсный сигнал строго определенной длительности,бе разрывов и провалов напряжения. После окончания прохождения информационного сигнала че(ез выходной элемент И 2-i через время, равное 0,5 где Тдад- минимальный период следования информационных сигналов, на втором выходе линии б задержки появится НИЗКИЙ потенциал, который установит R-S-трйггвр 5 и все элементы устройства в исходное состояние, и через элемент И-НБ 4 заблокирует- на вторую половину периода времени равную 0,5 Т овторную устанойку R-s-триггера 5 в состояние 1 от любых помех, которые могут появиться на первом входе любого иа п входного элемента ИЛИ 1-1т1-п. Устройство позволяет устранить влияние псжех для всех шин передачи сигнгиюв

/Т/

24/

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство задержки сигналов | 1983 |

|

SU1091306A2 |

| Аналого-цифровой преобразователь в кодах с естественной избыточностью | 1986 |

|

SU1381698A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| Входное устройство для электронных часов | 1990 |

|

SU1774471A1 |

| Устройство для задержки импульсных сигналов | 1986 |

|

SU1387183A1 |

| Система экстремального регулирования квадрупольного масс-спектрометра | 1989 |

|

SU1795419A1 |

| Устройство для вычитания импульсов | 1987 |

|

SU1432755A1 |

| Устройство для суммирования @ импульсных последовательностей | 1980 |

|

SU955050A1 |

| Устройство для устранения влияния дребезга сигнала | 1989 |

|

SU1725371A1 |

| Селектор импульсов по длительности | 1982 |

|

SU1092718A1 |

УСТРОЙСТВО ДЛЯ ЗАВШОИ ОТ . ЮШУЛЬСНЫХ ПОМЕХ, содержащее элемент И, линию задержки, R-S-триггер, шины входных сигналов, отличающееся тем, что, с целью повышения помехозащищенности, в него введены п входных элементов ИЛИ, элемент И-НЕ, п выходных элементов И/ и элемент ИЛИ, входы которого подключены к п шинам входных сигналов и первым входам п входных элементов ИЛИ, а выход - к первому входу элемента И-НЕ, подключенного своим выхсщом к единичному входу R-S-триггера, нулевой вход которого соединен с вторымвходом элемента И-НЕ и вторым выходом линии задержки, прямой выход R-S-триггера соединен с первым входом элемента И, а инверсный выход - с входом линии задержки, первый выход которой соединен с ВТОР1Л4 входом элемента И, выход которого подключен к вторам входам h выходных элементов И, при .выход и первый вход п элементов И подключены соответственно к второму входу и выходу п элементов ИЛИ.

fr2

Сп

/

IrV

М 5

1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент QIA 3979684, кл.328-167, 1976, 2 | |||

| Устройство для защиты от импульсных помех | 1977 |

|

SU652711A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-02-23—Публикация

1981-07-10—Подача