х|

VI

последовательно соединенные источник 1 входных сигналов в виде переключателя, схему 2 защиты от пробоя, входной нагрузочный элемент б, выполненный в виде n-канального МОП-транзистора, инвертор-усилитель 7 и формирователь 8

двоичных логических сигналов, В устройство введены согласующий элемент 5, выполненный в пиде р-канального МОП-транзистора, детектор 12 изменения входного сигнала, таймерное устройство 13. 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты | 1984 |

|

SU1239858A1 |

| Цифровые электронные часы | 1978 |

|

SU779967A1 |

| ЭНЕРГОНЕЗАВИСИМЫЙ МНОГОПОРОГОВЫЙ ТРИГГЕР КМОП С УПРАВЛЕНИЕМ УТЕЧКОЙ | 2003 |

|

RU2321944C2 |

| УСТРОЙСТВО КОРРЕКЦИИ СКВАЖНОСТИ ВХОДНОГО СИГНАЛА | 2011 |

|

RU2467473C1 |

| Устройство управления процессом горения | 1989 |

|

SU1620777A1 |

| Стабилизатор напряжения питания часовой интегральной схемы | 1985 |

|

SU1345165A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРОЦЕССОМ ДУГОВОЙ СВАРКИ НЕПЛАВЯЩИМСЯ ЭЛЕКТРОДОМ В СРЕДЕ ЗАЩИТНЫХ ГАЗОВ | 1988 |

|

SU1683244A1 |

| Устройство для ввертывания сердечников в катушки | 1987 |

|

SU1642531A1 |

| БАЗОВЫЙ УСИЛИТЕЛЬНЫЙ ЭЛЕМЕНТ ДИФФЕРЕНЦИАЛЬНОЙ ДИНАМИЧЕСКОЙ ЛОГИКИ (ВАРИАНТЫ) | 1999 |

|

RU2154338C1 |

| РЕВЕРСИВНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО ДИНАМИЧЕСКОГО ТИПА НА ПОЛЕВЫХ ТРАНЗИСТОРАХ С ИЗОЛИРОВАННЫМ ЗАТВОРОМ | 2001 |

|

RU2184418C1 |

Изобретение относится к электронной технике, в частности к цифровым электронным часам, в том числе к наручным часам, электронным секундомерам, калькуляторам, имеющим низковольтное батарейное питание. Целью изобретения является повышение устойчивости функционирования электронных часов к воздействию одиночных электромагнитных импульсов разряда статического электричества путем регулирования входного импульса инвертора усилителя и подавления импульсных помех, а также повышение достоверности контроля тока потребления при рассогласовании уровней напряжения источника питания и выходных сигналов измерителя путем расширения диапазона низкого уровня входного сигнала. Входное устройство содержит

Изобретение относится к электронной технике, в частности к цифровым электронным часам, в том числе наручным часам, электронным секундомерам, имеющим низковольтное батарейное питание.

Широко известно, что для изменения показаний времени в электронных часах используются переключатели. При замыкании переключателя на общий вывод источника тока, которым, как правило, является положительная клемма источника питания электронных часов, на управляющий вход микросхемы часов подается нулевой потенциал. При размыкании переключателя на управляющем входе устанавливается отрицательный потенциал с помощью высоко- импедансного входного нагрузочного элемента, при этом должна обеспечиваться устойчивая работоспособность электронных часов, т.е. минимальное значение тока утечки по управляющему входу.

Однако вследствие высокоимпедансно- го характера управляющего входа и использования новых пластических материалов корпуса часов на первый план выдвигаются две основные проблемы: обеспечение устойчивости функционирования электронных часов к воздействию статического электричества и повышенной влажности окружающей среды.

Известно входное устройство (технический отчет по ОКР Секунда 1, гос. № У07069, с. 28), включающее источник входных сигналов управления, представляющий собой механический переключатель, схему защиты от пробоя, включающей защитный диод, формирователь двоичных логических сигналов, содержащий триггер анти- дребезга контакта, формирующий инвертор и n-канальный входной нагрузочный МОП-транзистор, служащий для фиксации потенциала входа формирующего инвертора при разомкнутом переключателе.

В данном входном устройстве управляющий вход переключателя соединен со стоковым электродом n-канального входного

нагрузочного МОП-транзистора и входом формирующего инвертора, истоковый электрод входного нагрузочного МОП-транэи- стйра подключен к отрицательной клемме

источника питания, а электрод затвора - к положительной клемме источника питания. Выход формирующего инвертора подключем к D-вхду триггера антидребезга, а тактирующие входы триггера антидребезга через

два последовательно включенных тактирующих инвертора связаны с выходом схемы синхронизации часов, выход триггера антидребезга подключается к блоку управления часов. В качестве диода, служаа его для защиты схемы от воздействия статического электричества отрицательного знака, используется п+-область стока п-канального транзистора.

При замыкании переключателя на его

управляющий вход подается нулевой потенциал и через n-канальный входной нагрузочный МОП-транзистор начинает течь ток, величина которого определяется параметрами транзистора.

С другой стороны, параметры транзистора должны быть выбраны такими, чтобы обеспечить перезаряд емкости контактной площадки микросхемы после размыкания переключателя. Таким образом, при замыкании переключателей в схеме часов начинает течь входной ток и схема потребляет энергию от источника питания, величина которой прямо пропорциональна времени замыкания переключателя.

В электронных наручных часах (ЭНЧ) с целью уменьшения потребляемой мощности используются два уровня напряжения питания, при этом низкий уровень напряжения питания подключается к той части схемы часов, которая работает на высокой частоте, высокий уровень напряжения питания - к схемам, формирующим сигналы управления сегментами индикатора, сигналы, управляющие звуковыми устройствами, и

т.д.

При использовании часовой БИС в составе ЭНЧ, выполняющих, например, функции калькулятора или будильника с музыкальным устройством, БИС, имеющие различные уровни напряжения питания, могут быть подключены к одним и тем же переключателям. При этом в случае использования описанной схемы при отпущенной кнопке к входу схемы с более низким напряжением питания приложен более высокий отрицательный потенциал, который обеспечивает аналогичный n-канальный транзистор схемы с более высоким напряжением питания. Из-за разности напряжений питания в схеме с более низким напряжением питания через смещенный в прямом направлении диод, которым является сток п- канального транзистора, протекает значительный ток. Кроме того, более низкий потенциал на входе схемы с высоким уровнем напряжения питания может восприниматься этой схемой как замыкание переключателя, что приводит к ложному срабатыванию.

Таким образом, при использовании описанного входного устройства в электронных часах при использовании интегральных схем с различными уровнями напряжения питания требуются дополнительные согласующие элементы,. Использование данного устройства не обеспечивает достоверный контроль тока потребления микросхем для электронных часов на измерителях, когда на управляющий вход входного устройства подаются как нулевые, так и отрицательные потенциалы, и рассогласование их уровней напряжения питания приводит к забракованию схем по току потребления. Наличие высокоимпедансно- го входного n-канального транзистора приводит к нестабильности работы в условиях повышенной влажности, что сказывается на точности электронных часов, а также приводит к сбою функционирования при воздействии электромагнитных импульсов разряда статического электричества.

Известен твердотельный источник двоичных логических сигналов для электронных часов или аналогичных устройств (патент США № 4045692. кл. Н 03 К 3/353, 3/286, 17/04,1, G 04 С 3/00, опублик. 30.08.77), включающий первый и второй источники напряжения. К первому источнику напряжения подключен входной резистор. С вторым источником напряжения соединен выключенный переключатель. К первому и второму источникам напряжения подключен вход первого инвертирующего усилителя соответственно через входной резистор и выключенный переключатель. На выходе первого усилителя появляется первое напряжение, равное напряжению

второго источника напряжения, когда переключатель выключен. На выходе первого усилителя появляется второй уровень напряжения, равный напряжению первого ис- 5 точника напряжения, когда переключатель включен. Выход второго инвертирующего усилителя подключен к выходу первого инвертирующего усилителя. Между входом первого инвертирующего усилителя и выхо- 10 дом второго инвертирующего усилителя включен МОП-транзистор, электрод затвора которого соединен с выходом первого инвертирующего усилителя, МОП-транзистор, включенный при появлении первого 15 напряжения на выходе первого усилителя, создает цепь с низким импедансом между входом первого усилителя и выходом второго усилителя. При включенном переключателе и появлении второго напряжения на 0 выходе первого усилителя МОП-транзистор выключается при создании цепи с высоким импедансом между входом первого усилителя и выходом второго усилителя. Описанный выше источник двоичных логических 5 сигналов для электронных часов позволяет стабилизировать функционирование часов при открытом переключателе в условиях повышенной влажности.

Однако наличие на управляющем входе 0 высокоимпедансного нагрузочного реаи- стора снижает надежность работы источника двоичных логических сигналов в условиях сильных электромагнитных помех, возникающих в результате разряда статического 5 электричества, а также не обеспечивает достоверный контроль параметров, в частности тока потребления микросхемы, на измерительных системах при рассогласовании уровней первого и второго источников 0 напряжения.

Известно входное устройство для электронных часов (патент Японии № 57-59689, кл. Н 03 К 17/687, 19/00, опублик. 16.12.82), включающее источник входных сигналов, 5 представленный в виде переключателя, схему защиты от пробоя, входной нагрузочный резистор, формирователь двоичных логических сигналов, между входом и выходом которого включен п-канальный 0 МОП-транзистор. Формирователь .двоичных логических сигналов включает два последовательно соединенных инвертора, при этом выход второго инвертора подключен к электроду стока n-канального транзи- 5 стора, электрод затвора которого подключен к выходу первого инвертора и входу второго инвертора, а электрод истока - к входу первого инвертора, формируя замкнутый контур. К входу первого инвертора подключены переключатель, связанный с

высоким электрическим потенциалом, и резистор, второй вывод которого соединен с шиной низкого электрического потенциала. Когда переключатель замыкается на шину высокого потенциала, на входе первого и входе второго инверторов устанавливается высокий уровень. В это время на электроде затвора n-канального транзистора появляется низкий логический уровень и он закрывается. Когда переключатель размыкается, то на входе первого инвертора и выходе второго инвертора устанавливается низкий уровень напряжения относительно резистора, а на выходе инвертора первого - высокий уровень.На затворный электрод n-канального транзистора поступает высокий уровень, и на входе первого инвертора устанавливается стабильно низкий уровень выходного импенданса второго инвертора, что обеспечивает устойчивость схемы к воздействию влаги или единичной помехи. Однако наличие на входе высоко- импендансного резистора смещения снижает устойчивость работы переключателя в условиях сильных электромагнитных помех при разряде статического электричества и не обеспечивает достоверный контроль параметров изделия в целом, в частности тока потребления микросхемы, на измерительных системах при рассогласовании уровней питающего и управляющего напряжений, что приводит к ложному забракованию годных изделий.

Целью изобретения является повышение устойчивости функционирования электронных часов к воздействию электромагнитных импульсов разряда статического электричества путем регулирования входного импенданса инвертора-усилителя и подавления (фильтрации) импульсных помех, а также повышение достоверности контроля тока потребления при рассогласовании уровней напряжения источника питания и выходных сигналов измерителя путем расширения диапазона низкого уровня входного сигнала. Цель достигается тем, что в предлагаемое входное устройство для электронных часов введены согласующий элемент, выполненный в виде р-канального МОП-транзистора, истоковый электрод которого подключен к стоковому электроду входного нагрузочного элемента и входу инвертора- усилителя, а стоковый электрод - к выходу схемы защиты от пробоя, при этом электрод затвора соединен с положительной клеммой источника питания, детектор изменения входного сигнала, представляющий собой двухвходовой логический вентиль, реализующий функцию Y хш + Х1Х2, при этом первый вход детектора изменения

входного сигнала соединен с первым выходом формирователя двоичных логических сигналов, а второй вход подключен к второму выходу формирователя двоичных логических сигналов, таймерное устройство, состоящее из двоичного счетчика и двух вентилей 2И-НЕ, причем информационные выходы двоичного счетчика соединены с соответствующими входами первого венти0 ля 2И-НЕ, тактовый вход двоичного счетчика подключен к выходу второго вентиля 2И-НЕ, первый вход которого служит тактовым входом входного устройства, а второй вход подключен к выходу первого вентиля

5 21/1-НЕ, управляющий вход двоичного счетчика подключен к выходу детектора изменения входного сигнала, регистр входного сигнала, представляющий собой D-триггер, информационный вход которого подключен

0 к второму выходу формирователя двоичных логических сигналов, тактовый вход - к выходу таймерного устройства, а его выход служит информационным выходом входного устройства. Признак детектора измене5 иия входного сигнала, сходный с признаком детектора изменения входного сигнала заявляемого решения, не обнаружен. Наличие таймерного устройства и соответствующие связи известны из описания к авт.св. №

0 1205272, опублик. 15.01.86, бюл. № 2.

Однако сравнение свойства заявляемого и известного решений, обусловленное наличием данного признака, показало, что в заявляемом решении таймерное устройство

5 кроме расширения диапазона работоспособности часов, т.е. повышения помехоустойчивости, порождает избыточный эффект- возможность реализации дополнительной функции часов по входу типа нажа0 тие кнопки с задержкой, где в качестве линии задержки используется таймерное устройство.

Наличие указанных выше отличительных признаков и их связей обеспечивает

5 повышение устойчивости к воздействию внешних электромагнитных импульсов, возникающих при разряде статического электричества, за счет введения согласующего элемента, детектора изменения входного

0 сигнала, таймерного устройства, обеспечивающих двухступенчатый контроль истинности входного сигнала; повышение устойчивости к воздействию повышенной влажности за счет снижения входного им5 пенданса путем введения входного нагрузочного элемента, выполненного в виде открытого n-канального МОП-транзистора; повышение устойчивости входного устройства к рассогласованию уровней напряже- ния источника питания и выходных

сигналов измерителя или другого электронного устройства за счет введения согласующего элемента, выполненного о виде открытого р-канального МОП-транзистора, при этом обеспечиваются повышение достоверности контроля параметров, в частности тока потребления, а также возможность использования для управления электронными часами различных типов переключателей: как электронных, так и механических без дополнительных внешних согласующих элементов; расширение функциональной возможности входного устройства за счет наличия таймерного устройства, что обеспечивает в часах новую функцию нажатие кнопки с задержкой.

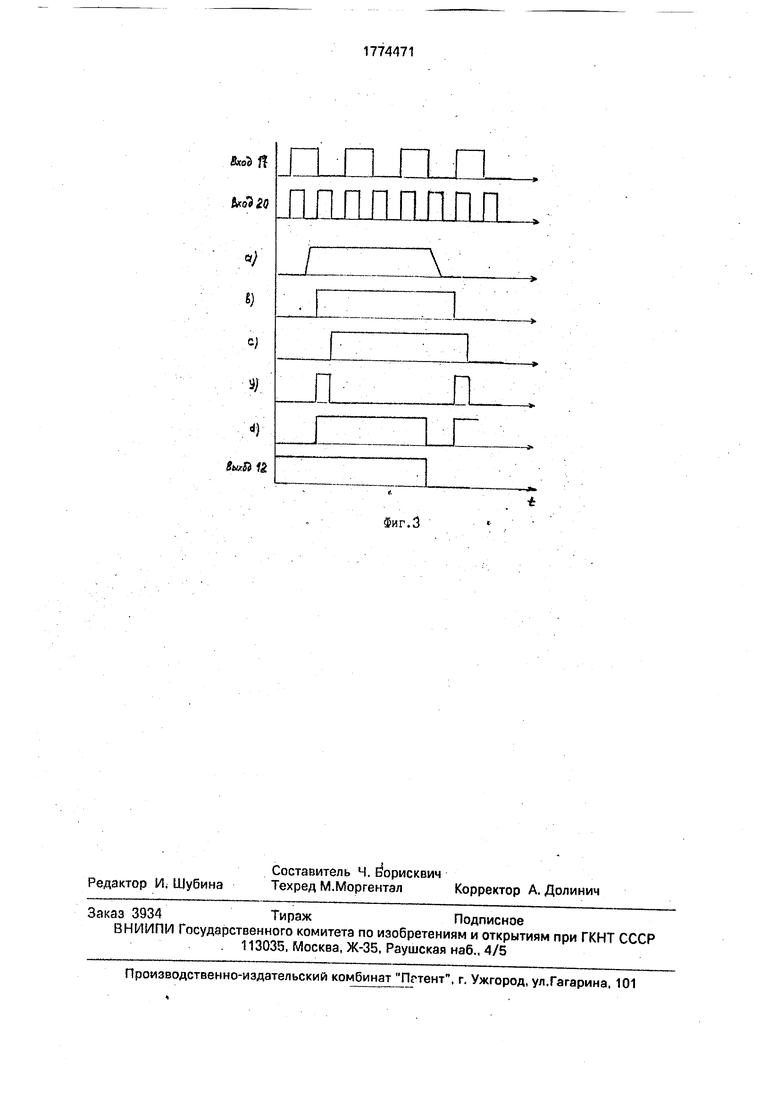

На фиг. 1 изображена структурная схема входного устройства для электронных часов; на фиг. 2 - функциональная схема входного устройства; на фиг. 3 - временная диаграмма функционирования устройства.

Входное устройство для электронных часов (фиг. 4) содержит источник 1 входных сигналов, представленный в виде переключателя, управляющий вход которого соединен с положительной клеммой источника питания, схему 2 защиты от пробоя, содержащую последовательно включенный интегральный резистор 3 и защитный диод 4, базовый электрод которого подключен к отрицательной клемме источника питания, согласующий элемент 5, выполненный в виде р-канального МОП-транзистора, стоковый электрод которого подключен к выходу схемы 2 защиты от пробоя, а электрод затвора - к отрицательной клемме источника питания, входной нагрузочный элемент 6, выполненный в виде n-канального МОП- транзистора, истоковый электрод которого подключен к отрицательной клемме источника питания, стоковый электрод - к исто- ковому электроду согласующего элемента 5, а электрод затвора - к положительной клемме источника питания, инвертор-усилитель 7, вход которого подключен к стоковому электроду входного нагрузочного элемента 6, формирователь 8 двоичных логических сигналов (фиг. 2), включакщий тактируемый RS-триггер 9, формирующий инвертор 10 и 0-триггер 11, детектор 12 входного сигнала, представляющий собой двухуровневый ло- гический вентиль, реализующий функцию у хш + Х1Х2, таймерное устройство 13, включающее два логических вентиля 2И-НЕ 14, 15 и двоичный счетчик 16, при этом первый вход вентиля 2И-НЕ 14 является тактовым входом 17 входного устройства, на который подается тактовая частота из делителя частоты электронных часов, и регистр входного сигнала, представленный в виде

D-триггера 18, информационный вход которого подключен к выходу вентиля 2И-НЕ 15, тактовый вход - к выходу RS-триггера 9, а его выход служит информационным выхо- 5 дом 19 входного устройств.

Один из электродов интегрального резистора 3, включенного последовательно, соединен с выходом переключателя 1, а другой - с электродом защитного диода 4 и стоковым 10 электродом р-канального МОП-транзистора, являющегося входом согласующего элемента 5. Выход инвертора-усилителя 7 подключен к информационному входу D-триггера 11, тактовый вход которого соединен с соотает- 15 ствующим тактовым входом RS-триггера 9 и подключен к выходу формирующего инвертора 10. Вход формирующего инвертора 10 является дополнительным тактовым входом 20 формирователя 8 двоичных логических 0 сигналов. Выходы D-триггера 11, прямой и инверсный, подключены к входам R и S RS- триггера 9 соответственно, при этом прямой выход D-триггера 11 подключен к первому входу двухвходового логического вентиля 5 12. Выход RS-триггера 9 подключен к второму входу двухвходового логического вентиля 12, выход которого подключен к управляющему входу двоичного счетчика 16. Тактовый вход двоичного счетчика 16 0 соединен с выходом вентиля 2И-НЕ 14, первый вход которого подключен к выходу 2И- НЕ 15.

Входное устройство для электронных часов работает следующим образом. 5 Рассмотрим работу входного устройства при замыкании и при размыкании переключателя 1. В начальный момент на выходах формирователя 8 двоичных логических сигналов устанавливаются потенциа- 0 лы, соответствующие значению логического О, переключатель 1 разомкнут, и на его выходе с помощью входного нагрузочного элемента 6 устанавливается также значение логического О, на выходе детектора 12 из- 5 менения входного сигнала также устанавливается уровень логического О, содержимое двоичного счетчика 16 максимально, при этом на выходе вентиля 2И-НЕ 15 логический О, который запрещает про- 0 хождение сигналов, поступающих по тактовому входу 17, на тактовый вход двоичного счетчика 16. Сигнал с выхода таймерного устройства 13. соответствующий уровню логического О, поступает на тактовый вход 5 D-триггера 18 регистра входного сигнала, на выходе 19 которого устанавливается уровень логической 1, соответствующий условию отсутствия воздействия на переключатель 1. При замыкании переключателя на его выход подается потенциал,

соответствующий уровню логической 1, что соответствует переднему фронту сигнала в точке а, изображенному на фиг. 3, По первому фронту из О в 1 сигнала, поступающего на дополнительный тактовый вход 20, временная диаграмма которого приведена на фиг. 3, D-триггер 11 переключается, и на прямом выходе устанавливается уровень логической 1, а следующим фронтом из 1 в О сигнала по входу 20 переключается RS-триггер 9 в состояние логической 1, при этом на выходе детектора 12 изменения входного сигнала короткий импульс, изображенный на фиг. 3, который сбрасывает двоичный счетчик 16 в исходное состояние и разрешает прохождение сигналов с входа 17 на тактовый вход двоичного счетчика 16 через вентиль 2И-НЕ 14 и запуск счетатаймерногоустройства 13. Временная диаграмма в точке d, соответствующая выходу таймерного устройства 13,изображена на фиг. 3.

Длительность отсчета времени определяется разрядностью двоичного счетчика 16, а также периодом тактовых импульсов, поступающих на вход 17. Как правило, длительность времени задержки определяется минимальной длительностью цикла обработки информации в электронных часах.

По заполнении двоичного счетчика 16 на выходе вентиля 2И-НЕ 15 устанавливается уровень логического О, который обеспечивает через вентиль 2И-НЕ 4 останов счета таймерного устройства 13 и записывается в D-триггер 18 регистра входного сигнала, на выходе 19 которого устанавливается уровень логического О, что соответствует условию, при котором переключатель 1 замкнут. При размыкании переключателя 1 по фронту из О в 1 сигнала по входу 20 в точке b устанавливается потенциал логического О, а по следующему фронту из 1 в О сигнала по входу 20 на выходе RS-триггера 9 устанавливается уровень логического О, при этом детектор 12 изменения входного сигнала вырабатывает короткий импульс, который обеспечивает сброс таймерного устройства 13 и последующий запуск отсчета задержки. По достиже- нии заданной длительности происходит останов таймерного устройства 13 и па выходе его формируется уровень логического О, который поступает на информационный вход D-триггера 18 регистра входного сигнала, при этом D-триггер регистра входною сигнала сохраняет предыдущую информацию о состоянии переключателя 1.

Описанная выше работа входного устройства для электронных часов обеспечивает подавление помех, возникающих при

дребезге переключателя или разряде статического электричества за счет реакции устройства на изменение входного сигнала и управления запуском и остановом таймерного устройства 13 по сигналам детектора 12 изменения входного сигнала.

При подаче на вход отрицательного импульса, амплитуда которого больше напряжения питания схемы р-канальный

0 МОП-транзистор 5 находится в области отсечки и величина входного тока схемы определяется токами утечки канала МОП-транзистора 5, величиной которого можно пренебречь. Применение данного

5 входного устройства в электронных часах позволяет повысить надежность электронных часов, обеспечивает устойчивость их функционирования в условиях высокой влажности и сильных электромагнитных по0 мех, позволяет расширить номенклатуру электронных часов в пластмассовых корпусах.

Использование заявляемого входного устройства для электронных часов позволя5 ет расширить диапазон напряжений, подаваемых на вход схемы с пределов от нуля до минус 1,5В до пределов от нуля до более чем минус 6В, при этом исключаются ложные срабатывания схемы, ток потребления уст0 ройства при этом снижается от 15 до 2,5 мкА при замкнутом переключателе.

Расширение диапазона уровня входного сигнала позволяет исключить брак в серийном производстве на операции

5 контроль тока потребления при рассогласовании сигналов измерителя и напряжения питания часов, обеспечивает использование таких микросхем в различных Системах питания часов, например 1,5

0 В система питания и 3 В система питания, что расширяет применение данной элементной базы. Кроме того, при измерениях часовых микросхем на АИС Виадук 1 на 10% уменьшается количество брака

5 микросхемы по току потребления из-за рассогласования уровней отрицательного напряжения, подаваемого на вход микросхемы измерителем и напряжением питания микросхемы.

0 Использование изобретения позволит повысить процент выхода годных на операции контроль функционирования примерно на 10%, это обеспечит снижение стоимости микросхемы часов в 1,1 раза.

5 Народнохозяйственное значение изобретения состоит в снижении себестоимости цифровых электронных часов, повышении их надежности, что способствует расширению номенклатуры изделий и повышению их качества.

Форму л а изобретения

Входное устройство для электронных часов, включающее последовательно соединенные источник входных сигналов в виде переключателя управляющий вход которого соединен с положительной клеммой источника питания, а выход подключен через интегральный резистор к электроду защитного диода, базовый электрод которого соединен с отрицательной клеммой источника питания, входной нагрузочный п-канальный МОП-транзистор, истоковый электрод которого подключен к отрицательной клемме источника питания, а электрод затвора - к положительной клемме источника питания, инвертор - усилитель и тактируемую двух- триггерную схему формирователя двоичных логических сигналов, отличающееся тем, что, с целью повышения устойчивости функционирования электронных часов к воздействию одиночных электромагнитных импульсов разряда статического электричества путем регулирования входного импеданса инвертора-усилителя и подавления (фильтрации) импульсных помех дребезга кнопки, а также повышения достоверности контроля тока потребления при рассогласовании уровней напряжения источника питания и выходных сигналов измерителя путем расширения диапазона низкого уровня входного сигнала, в устройство введены р- канальный МОП-транзистор, истоковый

#20

0

5

0

5

0

электрод которого подключен к стоковому электроду n-канального МОП-транзистора и входу инвертора-усилителя, а стоковый электрод- к выходу источника входных сигналов, при этом электрод затвора соединен с отрицательной клеммой источника питания, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, при этом первый вход элемента ИСКЛЮЧА- , ЮЩЕЕ ИЛИ-НЕ соединен с Q-выхоДом первого триггера тактируемой двухтриггер- ной схемы формирования двоичных логических сигналов, второй вход - с Q-выходом второго триггера тактируемой двухтриггер- ной схемы формирования двоичных логических сигналов, двоичный счетчик и два вентиля 2И-НЕ, информационные выходы двоичного счетчика соединены с соответствующими входами первого вентиля 2И-НЕ, тактовый вход двоичного счетчика подключен к выходу второго вентиля 2И-НЕ, первый вход которого является тактовым входом входного устройства, а второй вход подключен к выходу первого вентиля 2И НЕ. управляющий вход двоичного счетчика подключен к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, D-триггер, информационный вход которого подключен к Q-выходу еторого триггера тактируемой двухтриггер- ной схемы формирования двоичных логических сигналов, тактовый вход - к выходу первого вентиля 2И-НЕ, а его выход служит информационным выходом входного устройства.

19

| Патент США № 4045692, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Способ получения на волокне оливково-зеленой окраски путем образования никелевого лака азокрасителя | 1920 |

|

SU57A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-11-07—Публикация

1990-02-28—Подача