Риг. f

Изобретение относится к аналоговой вычислительной технике и может быть использовано в измерительной части специапизированных цифровых систем контроля, регистрации и управления реальными технологическими процессами или объектами.

Целью изобретения является повышение достоверности преобразования и расширение области использования за счет возможности преобразования измеряемых величин в г, 1-код, при ,3,..., п-1.

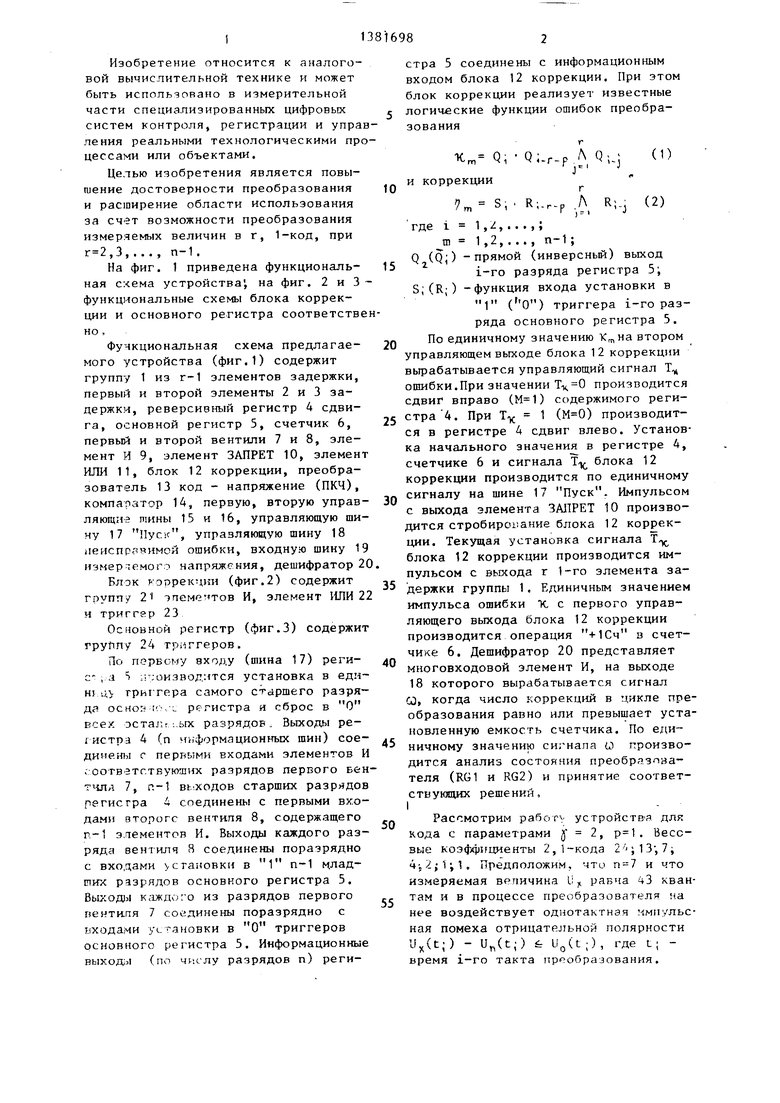

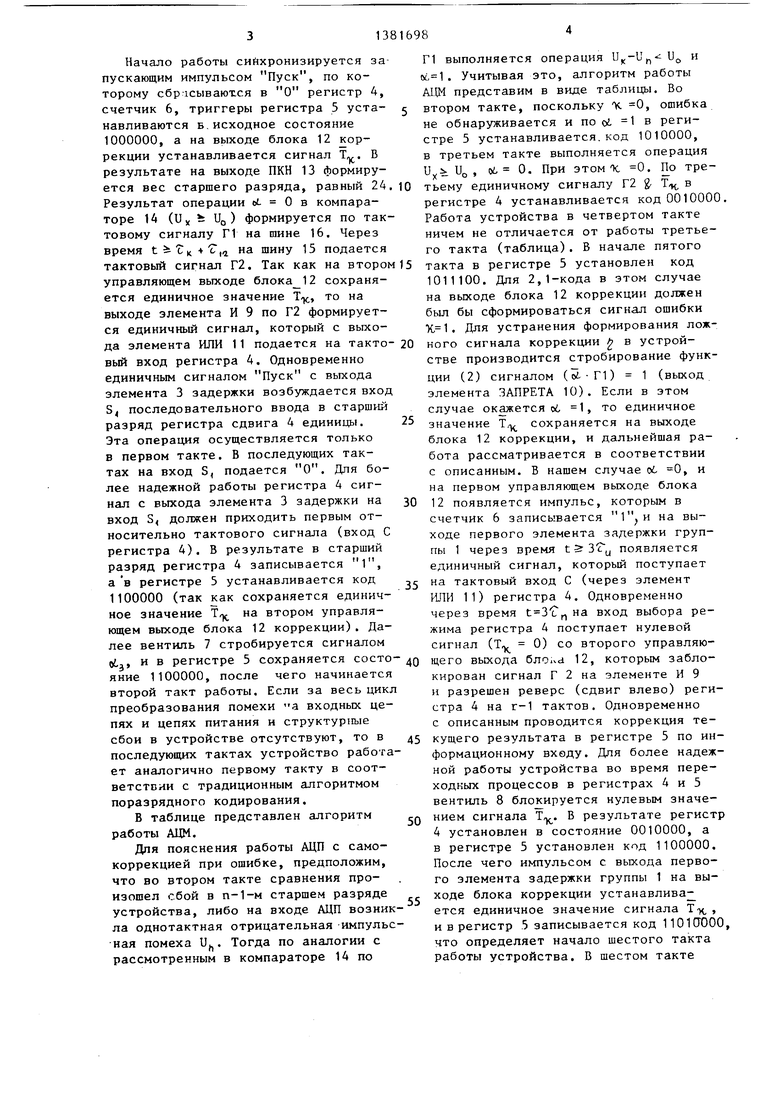

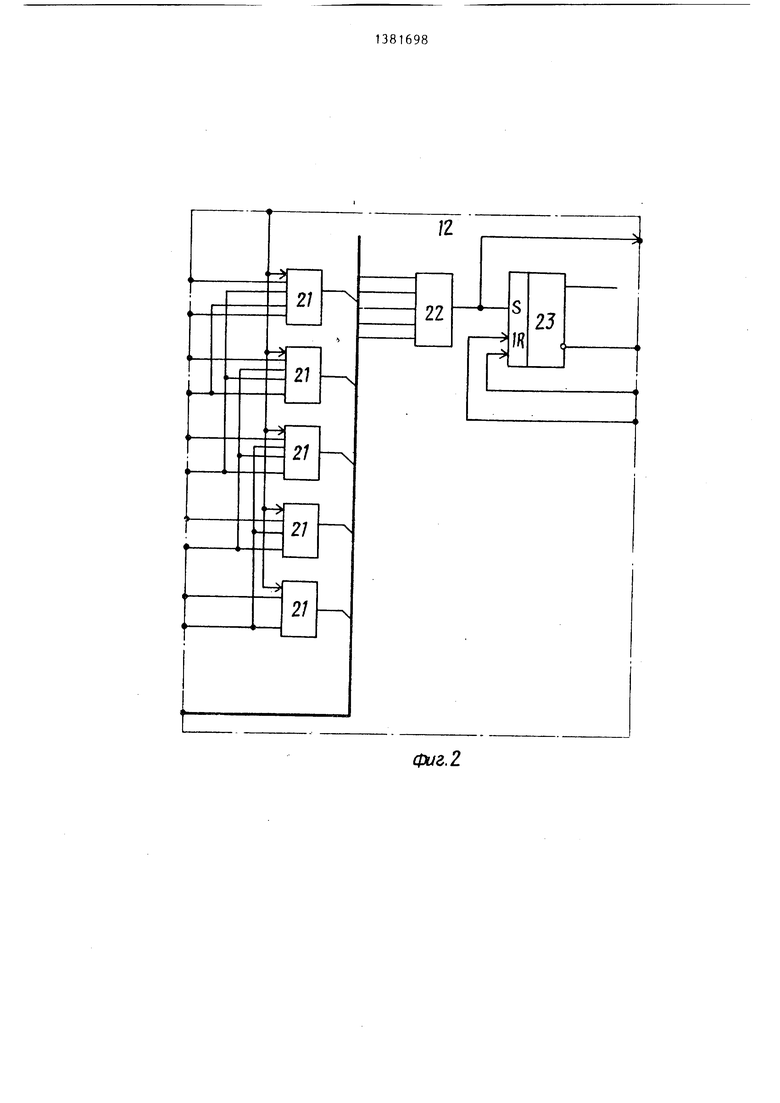

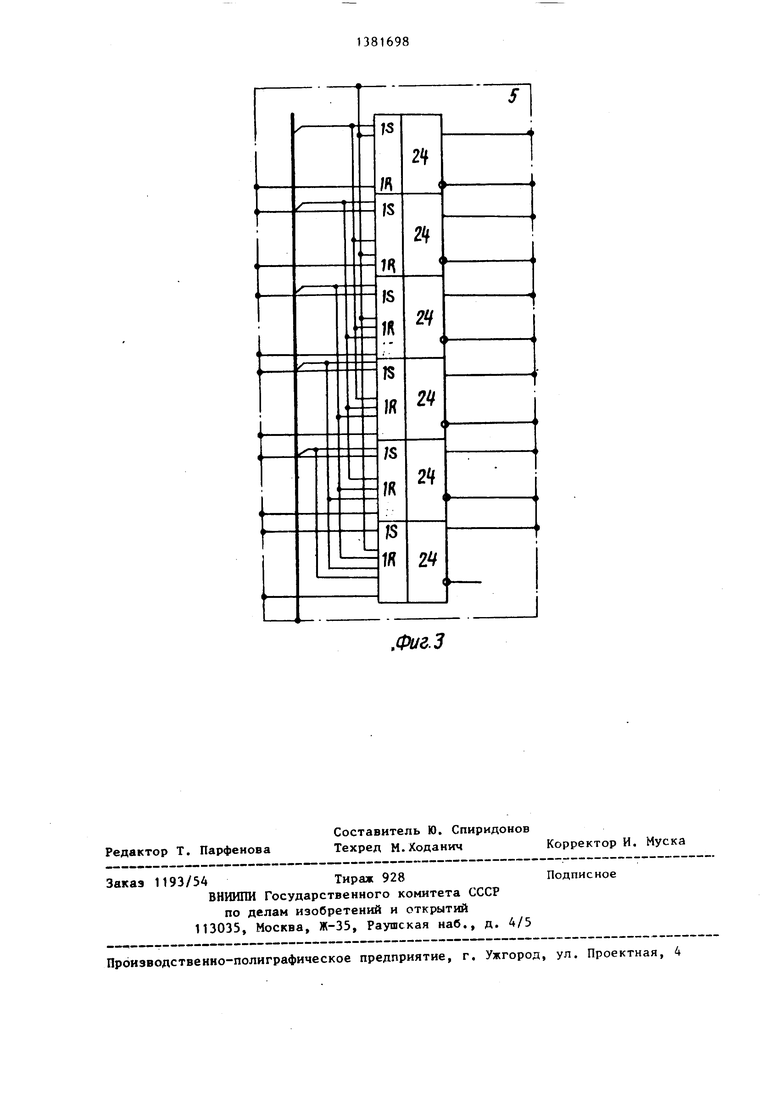

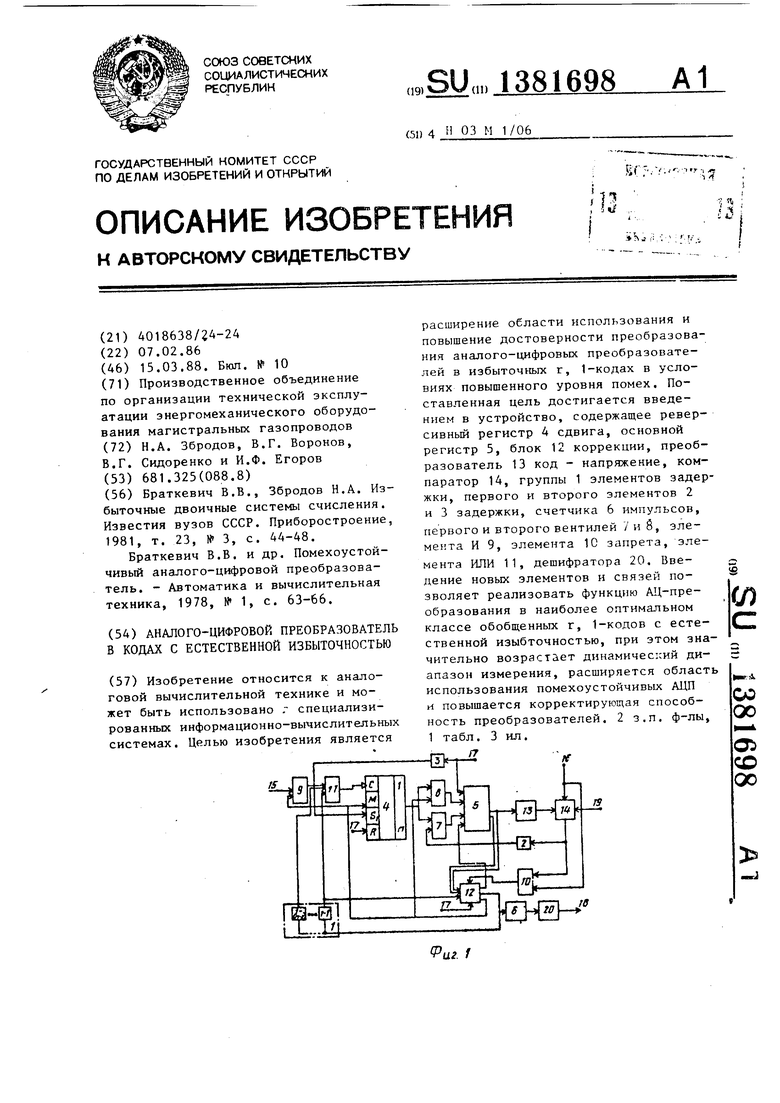

На фиг. 1 приведена функциональная схема устройства , на фиг. 2 и 3 - функциональные схемы блока коррекции и основного регистра соответствено ,

Функциональная схема предлагаемого устройства (фиг.1) содержит группу 1 из г-1 элементов задержки, первый и второй элементы 2 и 3 задержки, реверсивный регистр 4 сдвига, основной регистр 5, счетчик 6, первый и второй вентили 7 и 8, элемент И 9, элемент ЗАПРЕТ 10, элемент ИЛИ 11, блок 12 коррекции, преобразователь 13 код - напряжение (ПКЧ), компаратор 14, первую, вторую управляющие тины 15 и 16, управляющую шину 17 Пуск, управляющую шину 18 иеиспррнимой ошибки, входную шину 19 измертемого напряжения, дешифратор 20

Блок коррекиии (фиг.2) содержит групп/ 21 эпемет тов И, элемент ИЛИ 22 и триггер 23

Осрювной регистр (фиг.З) содержит группу 24 триггеров.

По первсП Гу входу (шина 17) реги- с , а S ;г;оизвол, - тся установка в единиц триггера самого старшего разряда осной г-, L регистра и сброс в О всех эста;и;.ых разрядов Выходы регистра 4 (п информационных шин) соединены с первыми входами элементов И соответствующих разрядов первого вен- 7, п-1 вь Ходов старших разрядов регистра 4 соединены с первыми входами второго вентипя 8, содержащего

Г.-1 элементов И. Выходы каждого разряда вентиля Я соединены поразрядно с входами становки в 1 п-1 лад- тих разрядов основного регистра 5. Выход1з1 к:1ждого из разрядов первого венткпя 7 соединены поразрядно с ьходами установки в О триггеров основного регистра 5. Информационные вь1ход;з1 (по числу разрядов п) регистра 5 соединены с информационным входом блока 12 коррекции. При этом блок коррекции реализует известные логические функции ошибок преобразования

10

к-т Q;

и коррекции

7т S,

где i ,2,- та

Q;.

г

л

)

R:

-J

(1)

(2)

1,2,

Q (Q;) -прямой (инверсный) выход i-ro разряда регистра 5; S; (R; ) -функция входа установки в

1 ( О) триггера i-ro разряда основного регистра 5. По единичному значению втором

20

25

30

35

40

45

0

5

управляющем выходе блока 12 коррекции вьфабатывается управляющий сигнал Т ошибки.При значении производится сдвиг вправо () содержимого регистра 4. При Т 1 () производится в регистре 4 сдвиг влево. Установка начального значения в регистре 4, счетчике 6 и сигнала Т блока 12 коррекции производится по единичному сигналу на шине 17 Пуск. Импульсом с выхода элемента ЗАПРЕТ 10 производится стробироуание блока 12 коррекции. Текущая установка сигнала Т блока 12 коррекции производится импульсом с выхода г 1-го элемента задержки группы 1. Единичным значением импульса ошибки К с первого управляющего выхода блока 12 коррекции производится операция -|-1Сч в счетчике 6. Дешифратор 20 представляет многовходовой элемент И, на вькоде 18 которого вырабатывается сигнал СО, когда число коррекций в цикле преобразования равно или превышает установленную емкость счетчика. По единичному значению сигнала и производится анализ состояния преобрг зоза- теля (RG1 и RG2) и принятие соответствуищих решений, I

Рассмотрим работу устройств-а для кода с параметрами j 2, . Весовые коэффициенты 2,1-кода 2 ;13 ,7 4i2;1;1, Предположим, что и что измеряемая величина I: равна чЗ квантам и в процессе преобразователя на нее воздействует однотактная импульсная помеха отрицательной полярности Uv(t;) - U(t;) t U(t ;), где L

X

время

V , / o

i-ro такта преобразования.

Начало работы сийхронизируется запускающим импульсом Пуск, по которому сбрасываются в О регистр 4, счетчик 6, триггеры регистра 5 уста- навливаются Б.исходное состояние 1000000, а на выходе блока 12 коррекции устанавливается сигнал Т.. В результате на выходе ПКН 13 формируется вес старшего разряда, равный 24 Результат операции oL О в компараторе 14 (DX Ь U(j ) формируется по тактовому сигналу Г1 на шине 16, Через время tit к + ,4 на шину 15 подается тактовый сигнал Г2, Так как на второ управляющем выходе блока 12 сохраняется единичное значение Т-, то на выходе элемента И 9 по Г2 формируется единичный сигнал, который с выхода элемента ИЛИ 11 подается на такто вый вход регистра 4. Одновременно единичным сигналом Пуск с выхода элемента 3 задержки возбуждается вход БД последовательного ввода в старший разряд регистра сдвига 4 единицы. Эта операция осуществляется только в первом такте. В последующих тактах на вход S, подается О. Для более надежной работы регистра 4 сигнал с выхода элемента 3 задержки на вход S, должен приходить первым относительно тактового сигнала (вход С регистра 4). В результате в старший разряд регистра 4 записывается Г , а в регистре 5 устанавливается код 1100000 (так как сохраняется единичное значение Т, на втором управляющем выходе блока 12 коррекции). Далее вентиль 7 стробируется сигналом oJ,,, и в регистре 5 сохраняется состо яние 1100000, после чего начинается второй такт работы. Если за весь цикл преобразования помехи а входных цепях и цепях питания и структурные сбои в устройстве отсутствуют, то в последующих тактах устройство работает аналогично первому такту в соответствии с традиционным алгоритмом поразрядного кодирования.

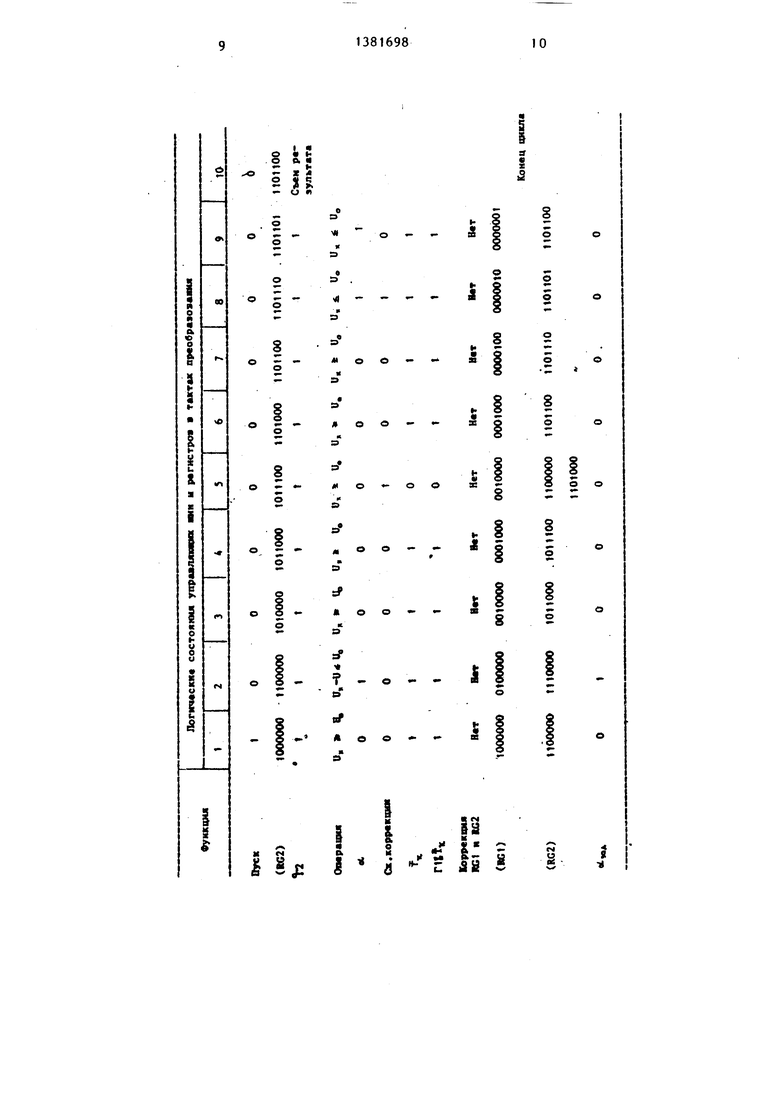

В таблице представлен алгоритм работы АЦМ.

Дпя пояснения работы АЦП с самокоррекцией при ошибке, предположим, что во втором такте сравнения произошел сбой в n-1-M старшем разряде устройства, либо на входе АЦП возникла однотактная отрицательная импульсная помеха J, Тогда по аналогии с рассмотренным в компараторе 14 по

с 5 0 5 О -. д 45

0

5

Г1 выполняется операция и uL , Учитывая это, алгоритм работы АЦМ представим в виде таблицы. Во втором такте, поскольку Х 0, ошибка не обнаруживается и по oi 1 в регистре 5 устанавливается, код 1010000, в третьем такте выполняется операция UQ , 06 0. При этом Тс 0. По третьему единичному сигналу Г2 2- Т/ регистре 4 устанавливается код 0010000. Работа устройства в четвертом такте ничем не отличается от работы третьего такта (таблица). В начале пятого такта в регистре 5 установлен код 1011100. Для 2,1-кода в этом случае на выходе блока 12 коррекции должен был бы сформироваться сигнал ошибки )(, 1. Для устранения формирования ложного сигнала коррекции в устройстве производится стробирование функции (2) сигналом () 1 (выход элемента ЗАПРЕТА 10). Если в этом случае окажется об 1, то единичное значение 1г сохраняется на выходе блока 12 коррекции, и дальнейшая работа рассматривается в соответствии с описанным. В нашем случае об 0, и на первом управляющем выходе блока 12 появляется импульс, которым в счетчик 6 записывается на выходе первого элемента задержки группы 1 через время t З с появляется единичный сигнал, которьш поступает на тактовый вход С (через элемент ИЛР1 11) регистра 4. Одновременно через время на вход выбора режима регистра 4 поступает нулевой сигнал (Т 0) со второго управляющего вьсхода бло.а 12, которым заблокирован сигнал Г 2 на элементе И 9 н разрешен реверс (сдвиг влево) регистра 4 на г-1 тактов. Одновременно с описанным проводится коррекция текущего результата в регистре 5 по информационному входу. Для более надежной работы устройства во время переходных процессов в регистрах 4 и 5 вентиль 8 блокируется нулевым значением сигнала Т. В результате регистр 4 установлен в состояние ООЮООО, а в регистре 5 установлен код 1100000. После чего импульсом с выхода первого элемента задержки группы 1 на выходе блока коррекции устанавлива ется единичное значение сигнала Т-, , и в регистр 5 записывается код 1101СЮОО, что определяет начало шестого такта работы устройства. В шестом такте

на выходе ПКН 13 устанавливается эквивалент кода 1101000, равный 41,что означаб Т Uy U,,, и ы.. 0. В конце седьмого такта в регистре 5 установлен код 1101110 44, Тогда в восьмом такте выполняется операция (). При этом о:, 1, и на выходе элемента ЗАПРЕТ 10 нулевой сигнал. Тогда Г2 2 Т 1, и в регистре 4 устанонле1;о текущее значение 0000010 а в регистре 5 устанавливается код 110111, после чего единичным сигналом будет сброшен в О разряд, соответствующий 1 в регистре 4. В результате в регистре 5 устанавливается код 1101101. В девятом такте сигнал Т. сохраняет единичное значение. По единице в младшем разряде регистра 4 определяется конец дикла и прои:1водится съем результата преобразования. По аналогии с описанным можно рассмотреть случай, когда за цикл преобразования возникают многократные помехи. При этом возможен случай, когда ошибка не может быть исправлена (отказ элементов устройства), тогда на вьгходе (18) зафик- Сируетс;я единичное значение сигнала Q .

Эффективное . ь использования предлагаемого устр -йства заключается в том, что незави :имо от чигла помех на с Ходе устройства или структурньгх сбоев резупьчат преобразования всегда истинный (тем самым увеличивается глубина коррекции). Предлагаемое устройство поэволязт реализовать функцию АЦ-преобраз( лания с самокоррекцией в г-1-кодах, что расширяет функциональные во:змг-,;чнг1сти преобра3OUато- лей используемых в качестве весов разрядов (, ,ы. При этом динамический диапа сн измерения увеличивается при г 2 а 4 раза, при г 3-в 12

раз, и т.д.

сравнению с прототилом. Кр оме того, ((педлагаемое с тройство позволяет отказаться от вспомогательного регистра (прототип), что сокращает аппаратурные затраты и уменьша.ет время ли-преобразования.

Форм

изобретения

1, Аналог о-цифровой преобразователь в кодах с естественной избыточностью, coдepжaiIU й п-разрядный реверсивный сдвиговьш регистр, п-разрядный основной регистр, преобразователь

0

5

0

5

0

5

0

5

0

5

код - напряжение, компаратор, пепвую и вторую тактовые шины, блок ции, вход Пуск которого объединен с входами начапьной установки реверсивного сдвигового регистра и основного регистра и является шиной Пуск, первый информационный вход компаратора соединен с выходом преобразователя код - напряжение, а вто рой информационный и стробирующий входы являются соответственно входной и первой тактовой шинами, отличающийся тем, что, с целью повышения достоверности преобразования и расширения области использования за счет возможности преобразования изме- ряемьЕХ величин в г. 1-код г 2,3, 4, . . .,(п-1 )J , D него введены эпемен- ты Ш1И, первый и второй элементы задержки, группа из г-1 элементов задержки, первый и второй ключи, элемент И, элемент ЗАПРЕТ, счетчик импульсов, дешифратор, выход которого являет : я шиной неисправимой ошибки, а вход соединен с выходом переноса счетчика импульсов, счетный вход которого объединен с входами элементов задержки группы и соединен с первым управляющим выходом блока коррекции, инфор1-1ационные выходы которого соединены с соответствующими информационными входами основного регистра, входы установки в О всех разрядов которого соединены i оответствую- щими выходами первого вентиля, а входы установки в Г разрядов, кроме последнего, соединены с соответствующими выходами второго пентипя, информационные входы которого с порво- го по (п-1)-й объединены с соответствующими информацион} ыми входами первого вентиля ii подключен.; к с(,о ветстяукяцим выходам реверсивного сдвигового регистрЛ; выход п-го разряда котор( сс-ядинен с п -м инфор- мац;-.оннь1М входом пер юго вр пи. йя, управляющий вход KO ioporo сиед- пен с выходом Г;рвог о элементв а;ге:/чки,

ВХОя КОТ-ТТ;ОГ,-) СДИНГ- г И1ГЧ:, СНЫМ

входом элем12 -т.1 заиретч vi подключен .. выходу комплротора, с гуч-г чрчтощий Бхс;,- которого объед{5Ь е;| с .м Г;Хо.-;ом элемента зяпрет-, которого соединен с первым у1тра|1:1я:о дим ь ходом блока коррекции, первая ; руп- i. (n-l)-x информационных в::одоз которого объедин1 на с ооотв- ч ствующими, кроме п-го, Dxoa.ir-n: пг оРразователт

код - напряжение и подключена к соот ветствующИ прямым информационным выходам ос.ювного регистра, инверс- ные информационные выходы которого, кроме первого, соединены с соотиет- ствующими входами второй группы информационных входов блока коррекции, п-й прямой выход основного регистра соединен с п-м входом преобразователя код - напряжение, вход второго элемента задержки является шиной Пуск, а выход соединен с информационным входом реверсивного сдвигового регистра, вход выбора режима которого объединен с первым входом элемента И, управляющим входом второго вентиля и подключен к второму управляющему выходу блока коррекции, второй управляющий вход которого объединен с первым входом элемента ИЛИ и подключен к выходу первого элемента задержки группы, выходы остальных элементов задержки группы соединены с соответствующими входами, кро ме г-го, элемента Ш1И, г-й вход которого соединен с выходом элемента И, второй вход которого является второй тактовой шиной, а выход элемента ИЛИ соединен с тактовым входом реверсивного сдвигового регистра.

2. Преобразователь по п. 1, отличающийся тем, что блок коррекции выполнен на элементе ИЛИ, триггере и (п-1) элементах И, первые входы которых объединены и являются первым управляющим входом блока коррекции, входом Пуск и вторым управляющим входом которого являются соответственно первый и второй R-входы триггера, S-вход которого соединен с выходом элемента ИЛИ и является первым управляющим выходом блока коррекции, вторым управляющим выходом которого является инверсный выход триггера, выходы элементов И соединены с соответствующими входами элемента ИЛИ и являеютс я соответствующими информационными выходами блока коррекции, второй группой информационных входов которого являются вторые входы cooтвeтcтвyющIix элементов И,

ш

)5

20

25

816988

третий вход i-ro элемента И , 2 ,, . . , ,--(п-1 )3 объединен с четнертым входо;- (i+1)-ro и пятым входом (i-t- +2)-го элементов И и является соответствующим входом первой группы информационных входов блока коррекции.

3. Г реобразователь по п, 1, о т- личающийся тем, что основной регистр выполнен на п-триггерах, прямые выходы которых являются соответствующими прямыми информационными выходами основного регистра, а инверсные выходы триггеров являются соответствующими инверсными информационными выходами основного регистра, первые R-входы триггеров являются соответствующими входами установки в О основного регистра, а первые S-входы триггеров, кроме п-го, являются соответствующими входами установки в 1 основного регистра, первый S-вход п-го триггера объединен с вторыми К-входами остальных триггеров и является входом начальной установки основного регистра, второй S-вход п-го триггера объединен с третьими R-входами (n-l)-ro, (п-2)-го и (ti-3)-ro триггеров и является (п-1)-м информационным входом основного регистра, второй З-вход (п-1)-го триггера объединен с четвертыми входами (п-2)-го и (п-З)-го триггеров и третьим входом (п-4)-го триггера и является (п-2)-м информационным входом основного регистра, второй S-вход i-ro триггера где 1 4,5,,.., (п-2)3 объединен с пятым R-входом (i-1)-ro триггера, четвертым входом (i-2)-ro триггера, с третьим входом (i-3)-ro триггера и является (1-1)-м информационным входом основного регистра, второй S-вход третьего триггера объединен с пятым R-входом второго и четвертым R-входом первого регистров и является вторым информационным входом основного регистра, второй S-вход второго триггера объединен с пятым R-входом первого триггера и является первым информационным входом основного регистра.

30

35

40

45

50

/2

-5.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь с самокоррекцией в кодах с естественной избыточностью | 1986 |

|

SU1381703A1 |

| Аналого-цифровой преобразователь с самокоррекцией | 1986 |

|

SU1341716A1 |

| Система передачи и приема информации с коррекцией ошибок | 1985 |

|

SU1311036A1 |

| Устройство для формирования интегральных характеристик модулярного кода | 1984 |

|

SU1216777A1 |

| Параллельно-последовательный п-разрядный аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1732471A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый и дВОичНО-дЕСя-ТичНОгО B дВОичНый | 1979 |

|

SU809155A1 |

| Устройство для определения центра массы плоской фигуры | 1985 |

|

SU1249541A1 |

| Устройство для исследования графов | 1985 |

|

SU1290345A1 |

| Логическое запоминающее устройство | 1976 |

|

SU650103A1 |

| Резервированная вычислительная система | 1990 |

|

SU1755400A1 |

Изобретение относится к аналоговой вычислительной технике и может быть использовано г специализированных информационно-вычислительных системах. Целью изобретения является расширение области использования и повышение достоверности преобразования аналого-цифровых преобразователей в избыточных г, 1-кодах в условиях повышенного уровня помех. Поставленная цель достигается введением в устройство, содержащее реверсивный регистр 4 сдвига, основной регистр 5, блок 12 коррекции, преобразователь 13 код - напряжение, компаратор 14, группы 1 элементов задержки, первого и второго элементов 2 и 3 задержки, счетчика 6 импульсов, первого и второго вентилей 7 и S, элемента И 9, элемента 1C запрета, элемента ИЛИ 11, дешифратора 20. Введение новых элементов и связей позволяет реализовать функцию АЦ-пре- образования в наиболее оптимальном классе обобщенных г, 1-кодов с естественной изыбточностью, при этом значительно возрастает динамический диапазон измерения, расширяется область использования помехоустойчивых АЦП и повышается корректирующая способность преобразователей. 2 з.п. ф-лы, 1 табл. 3 ил. (/) к А со ОО О) СО 00 rs

22

/Я

25

фг/г.2

.Фиг.З

| Браткевич В.В., Збродов Н.А | |||

| Избыточные двоичные системы счисления | |||

| Известия вузов СССР | |||

| Приборостроение, 1981, т | |||

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Браткевич В.В | |||

| и др | |||

| Помехоустойчивый аналого-цифровой преобразователь | |||

| - Автоматика и вычислительная техника, 1978, № 1, с | |||

| Способ приготовления сернистого красителя защитного цвета | 1915 |

|

SU63A1 |

Авторы

Даты

1988-03-15—Публикация

1986-02-07—Подача