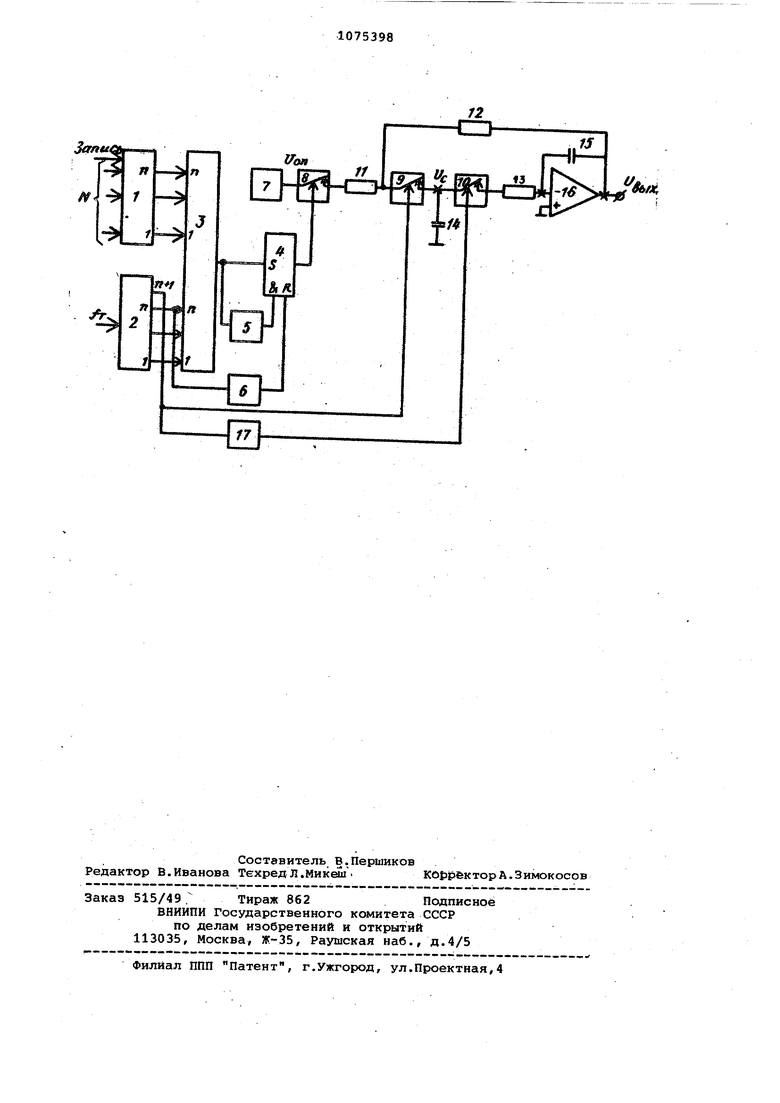

Изобретение относится к измерительной и вычислительной технике и может быть использовано в устройства преобразования цифровой информации в аналоговую, Известны цифроаналоговые преобразователи, содержащие резистивные матрицы, ключи, операционные усилители 1. Недостатком этих устройств являет ся большое число прецизионных аналоговых элементов в их составе. . Наиболее близким по технической сущности к предлагаемому изобретению является цифроаналоговый преобразователь, содержащий входной регистр, информационные входы которого подключены к шинам преобразуемого ко да, управляющий вход - к шине записи счетчик, вход которого подключен к 11шне тактовых импульсов,- а выходы п разрядов - к первым п входам блока сравнения, вторые п входов которого подключены к п выходам входного регистра, выход - к s-входу триггера и к входу Первого инвертора, выход которого подключен к первому R-входу триггера, второй R-вход которого под ключен к выходу одновибратора, вход которого подключен к выходу п-го раз ряда счетчика, источник опорного напряжения, выход которого подключен к входу первого ключа, управляющий вход которого подключен к выходу три гера, выход - к первому выводу перво го резистора, второй ключ, первый кондейсатор, первая обкладка которого подключена к общей шине, операционный усилитель, выход которого подключен к выходной шине. Преимущество известного преобразо вателя состоит в отсутствии прецизионных аналоговых элементов 2J.. Однако известные преобразователи обладают низким быстродействием. Целью изобретения является повыше ние быстродействия. Поставленная цель достигается тем что в цифроаналоговый преобразователь, содержащий входной регистр,информационные входы которого подключены к шинам преобразуемого кода, .. управляющий вход - к шине записи, счетчик, вход которого подключен к шине тактовых импульсов, а выходы п разрядов - к первым п входам блока сравнения, вторые п входов которого подключены к п выходам входного регистра, а выход - к S-входу триггера и к входу первого инвертор, выход которого подключен к первому R-входу триггера, второй Н-вход которого .подключен к выходу одновибратора, вход которого подключен к В1лходу п-г разряда счетч}}ка, источник опорного напряжения, выход которого -подключен к оду первргр ключа, управляющий вход которого подключен к выходу триггера выход - к первому выводу первого ре-. зистора, второй ключ, первый конден- . сатор, первая обкладка которого подключена к общей шине, операционный усилитель, выход которого подключен к выходной шине, введены второй инвертор, второй и третий резисторы, третий ключ, второй конденсатор, первая обкладка которого подключена к инвертир тощему входу операционного усилителя и к первому выводу третьего резистора, вторая обкладка - к выходу операционного усилителя и к первому выводу второго резистора, второй вывод которого подключен к второму выводу первого резистора и к входу второго ключа, выход которого подключен к входу третьего ключа и к , второй обкладке первого конденсатора, управляющий вход - к выходу п+1-го разряда счетчика и к входу второго инвертора, выход которого подключен |(управляющему входу третьего ключа, выход которого подключен к второму выводу третьего резистора, при этом неинвертирующий вход операционного усилителя подключен k общей шине. На чертеже приведена структурная схема устройства. Устройство содержит входной регистр 1,«информационные входы которого подключены к шинам преобразуемого кода, управляющий вход к шине записи, счетчик 2, вход которого подключен к шине тактовых импульсов, а выходы п разрядов - к первьаи п входам блока 3 еравнения,вторые п входов которого подключены к п выходам входного регистра 1, выход - к S-входу триггера 4 и к входу первого инвертора 5, выход которого подк яочен к первому R-входу триггера 4, объединённому по И с вторым R-входом триггера 4, который подключен к выходу одновибратора 6, вход которого подключен к выходу п-го разряда счетчика 2, источник 7 опорного напряжения, выход которого подключен к входу первого ключа 8, управляющий вход которого подключен к выходу триггера 4, второй ключ 9, управляющий вход которого подключен, к выходу п+1-го разряда счетчика 2, выход - к входу третьего ключа 10, первый резистор 11, первый вывод которого псшключен к выходу первого ключа 8, второй вывод - к входу второго ключа 9, второй резистор 12, третий резистор 13, первый кондейсатор 14, первая обкладка которого подключена к общей шине, а вторая - к выходу второго ключа 9, второй дсонденсатор 15, вторая обкладка которого подключена к выходу операционного усилителя 16 и к выходной шине, первая обкладка - к инвертирующему входу операционного уситилеля 16 и к первому выводу третьего резистора 13, второй вывод которого под ключей к выходу третьего ключа 10,. управл}1ющий вход которого подключен к выходу второго инвертора 17, вход которого подключен к выходу п+1-го разряда счетчика 2, при этом неинвертирукидий вход операционного усилителя 16 подключен к общей шине, а выход - к первому выводу второго резистора 12, второй вывод которого по ключен к второмувыводу первого рези стора 11. Устройство работает следукщим обр зом. Входной п-разрядный код N записывается в регистр 1 по сигналу Запись . Счетчик 2 подсчитывает импуль сы тактовой частоты f. Коды счетчика 2 и регистра 1 сравниваются в блоке 3 сравнения. В момент перехода п-го. разряда счетчика 2 из состояния в О на выходе одновибратора 6 появляется импульс 1, который при нахождении первого инвертора в состоянии 1, т.е. при неравенстве ко дов регистра 1 и счетчика 2, устанав ливает выход -триггера 4 в состояние 1, соответствующее замкнутому состоянию ключа 8, и подключает источник 7 опорного напряжения к первому резистору 11. Ключ 8 замкнут до тех пор, пока коды с выходов регистра 1 и счетчика 2 не сравняются. В момент равенства кодов на выходе блока 3 сравнения устанавливается высокий потенциал 1, который перебрасывает выход триггера 4 в состояние О, соответствующее разомкнутому состоянию ключа 8. Процесс в дальнейшем протекает аналогично и через ключ 8 на резистор 11 от источ ника 7 поступают изменяющиеся по дли тельности импульсы с частотой следования f4 1/Т| . Длительность импульсов пропорциональна входному коду N, Ключи 9 и 10 непосредственно и через инвертор управляются (п+) разрядом счетчика 2 и замыкаются в противофазе с частотой ,Тм-{-г/2 . Время замыкания каждого ключа 9 т: 10 равно Tji. В установившемся режиме на интервале замкнутого ключа 9 конденсатор 14 заряжается через резистор 12 постоянным напряжением с выхода устройства Up, и напряжением от опорного источника 7 через замкнутый или разом киутый ключ 8, что создает через резис±ор 11 импyль cный ток, среднее зна чение которого пропорционально времени замкнутого состояния ключа 8. Выходное напряжение устройства на этом интервале постоянно, так как ключ 10 разомкнут, что эквивалентно подаче нулевого напряжения на вход интеграто ра, состоящего из резистора 13, слюча 10, операционного усилителя 16 и конденсатора 15. На интервале замкнутого состояния ключа 8 (t .Q ) конденсатор l4 зарлдился до значения Uj ЧИя; - « Н-« ),(Г ,ЧR1,R«/R«+M c,4 На интервале (Т « ключ 8 разо;мкнут, конденсатор 14 разряжается до нуля. -Огидв- Гм- „)/г2,(,д.-1т„.„,, .,,. На следующем интервале Тд,, |не меняется, так как ключ 9 разомкнут :и конденсатор 14 не изменяет своего I потенциала, равного нулю, вследствие чего интегратор на резисторе 13,ключе 10, операционном усилителе 16 и конденсаторе 15 подключен к источнику нулевого потенциала и не изменяет свое выходное напряжение. Таким образом в установившемся режиме на выходе устройства напряжение постоянно и пульсации отсутствуют независимо от относительной длительности импульса г /Тд,. Результатом исследования уравнений (1) и (2) является нгшичие возможности выбрать элементы схемы, обеспечивающие высокую точность линейного преобразования кода в напряжение IL К N при одновременном получении высокого быстродействия и заданного вида переходного процесса. Динаичические параметры предлагаемого устройства оцениваются в перIBOM приближении эквивалентной передаточной функцией колебательного зве на U1 - . IP) , г«.е SifV ; )/,1/«,-, ,5Л-Йп-Сн-)1(7/Й«)Теоретические и экспериментальные исследования предлагаемого устройства показывают возможность получить малое время переходного процесса в пределгрс (2-4) 1 для скачкообразного изменения цифрового кода, i Технико-экономическая эффективность предлагаемого устройства по сравнению с известным заключается в овышении быстродействия. .Повышение быстродействия определяется тем,что.в известном устройстве с возрастанием точности (разрядности) преобразования требуется увеличение постоянной времени фильтра пропорционально точности преобразования с тем, чтобы получить величину пульсаций на уровне погрешности. В предлагаемсм устройстве выходные пульсации отсутствуют и требуемая точность преобразования не влияет на время переходного процесса устройства, которое определяется только выбором параметров элементов схемы.

/Г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения логарифма отношения двух напряжений | 1982 |

|

SU1103249A1 |

| Аналого-цифровой интегратор | 1981 |

|

SU1013978A1 |

| Логарифмический аналого-цифровой преобразователь | 1990 |

|

SU1725397A1 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1042036A1 |

| Интегрирующий преобразователь напряжения в код | 1986 |

|

SU1410275A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

| Усилитель | 1985 |

|

SU1334360A1 |

| Цифроаналоговая следящая система | 1989 |

|

SU1700536A1 |

| Функциональный аналого-цифровой преобразователь | 1983 |

|

SU1113813A1 |

| Аналого-цифровой преобразователь с промежуточным преобразованием напряжения в частоту | 1982 |

|

SU1102035A1 |

ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий входной регистр, информационные входы которого подключены к шинам преобразуемого кода, управляющий вход - к шине записи, счетчик, вход которого подключен к шине тактовых импульсов, а выходы п разрядов - к первым п входам блока сравнения, вторые п входов которого подключены к п выходам входного регистра, а выход - к S-входу триггера и к входу первого инвертора, выход которого подключен к первому R-вхсду триггера, второй Е-вход которого подключен к выходу одновйбратора, вход которого подключен к выходу п-го разряда счетчика, источник опорного напряжения, выход которого подключен к входу первого ключа, управляющий вход которого подключен к выходу триггера, выход - к первому выводу первого резистора, второй ключ, первый конденсатор, первая обкладка которого подключена к общей шине, операционный усилитель, вьход которого подключен к выходной шине, отличающийся тем, что, с целью повышения быстродействия, в него введены второй инвертор, второй и третий резисторы, третий ключ, второй конденсатор, первая обкладка которого подключена к инвертирующему входу операционного усилителя и к первому выводу третьего резистора, вторая обкладка - к выходу операционного уси- S лителя и к первому выводу второго (Л резистора, второй вывод которого подключен к второму.выводу первого резистора и к входу второго кгаоча, выход которого подключен к входу третьего ключа и к второй обкладке первого конденсатора, управляющий вход - к выходу П+1-ГО разряда счетчика и к входу второго инвертора, выход которого подключен к управляющему входу ел третьего ключа, выход которого подключен к второму выводу третьего резистора, при этом неинвертирующий Ьо вход операционного усилителя подклю Г) к общей шине. эо

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Балакай В.Г | |||

| и др | |||

| Интегральные АЦП и идп | |||

| Под ред | |||

| Л.М.Лукьянова | |||

| М., Энергия, 1978, с.10-38 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Валакай в.Г | |||

| и др | |||

| Интегральные АЦП и ЦАЙ | |||

| Под ред, Л.М.Лукьянова | |||

| М., Энергия, 1978, с.39-42, рис.1-11 (прототип). | |||

Авторы

Даты

1984-02-23—Публикация

1982-02-18—Подача