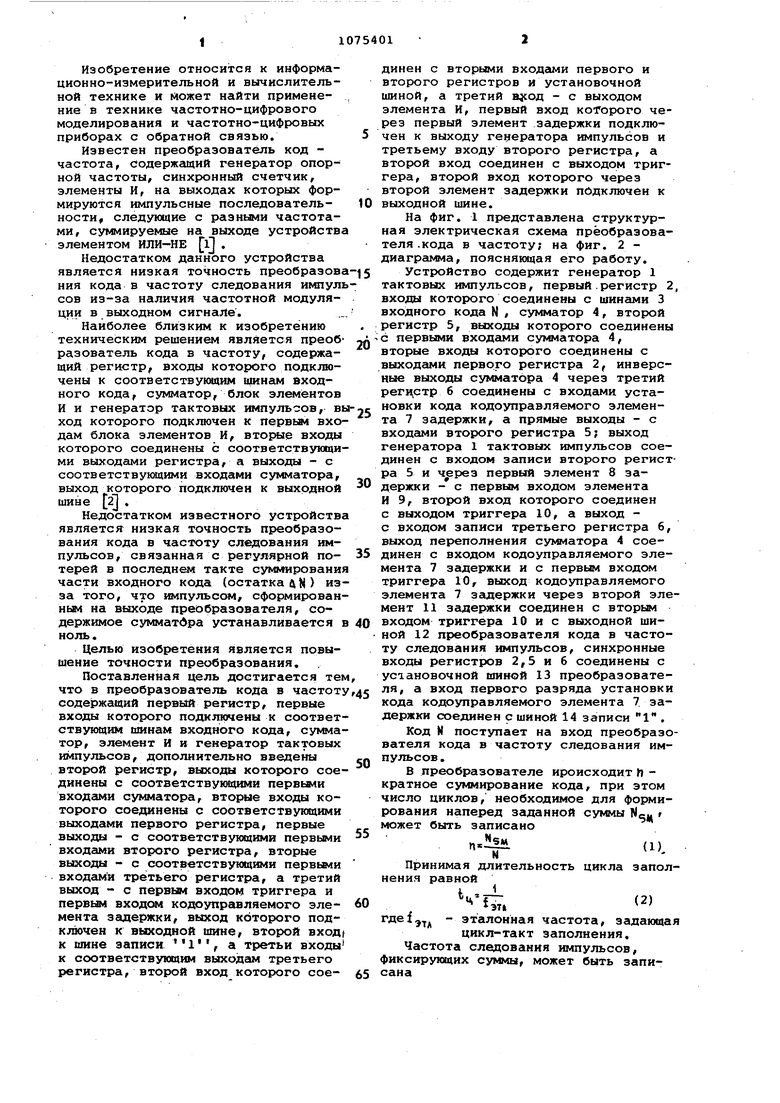

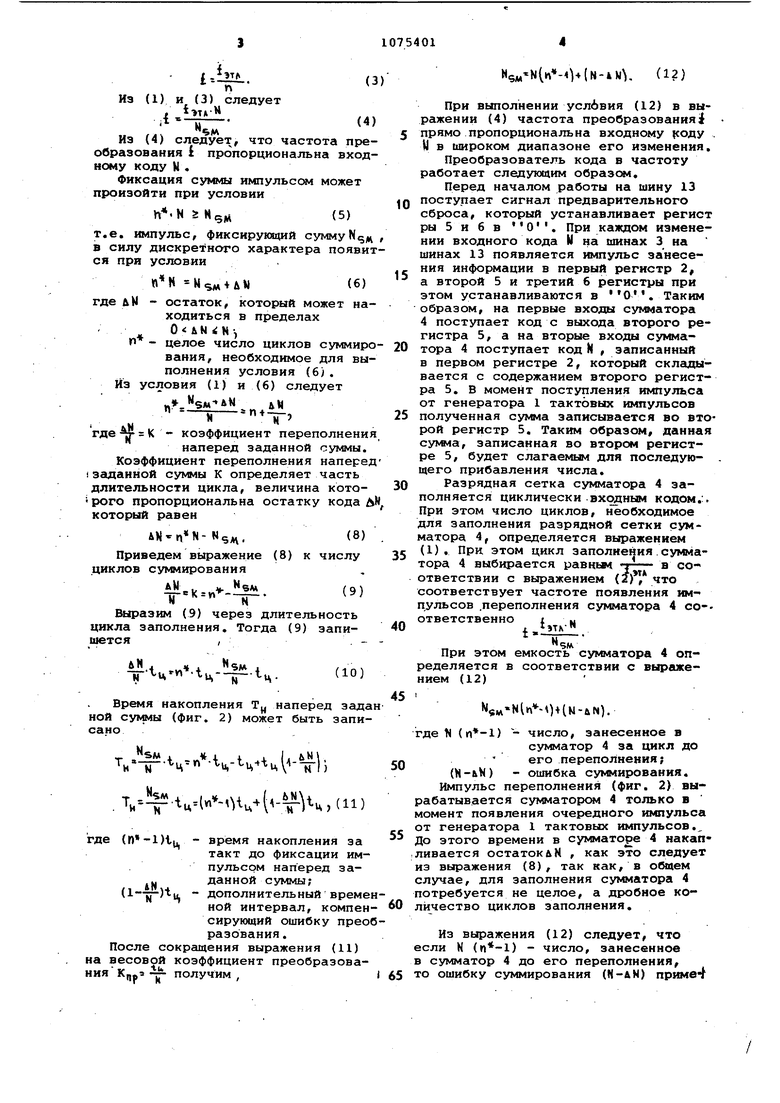

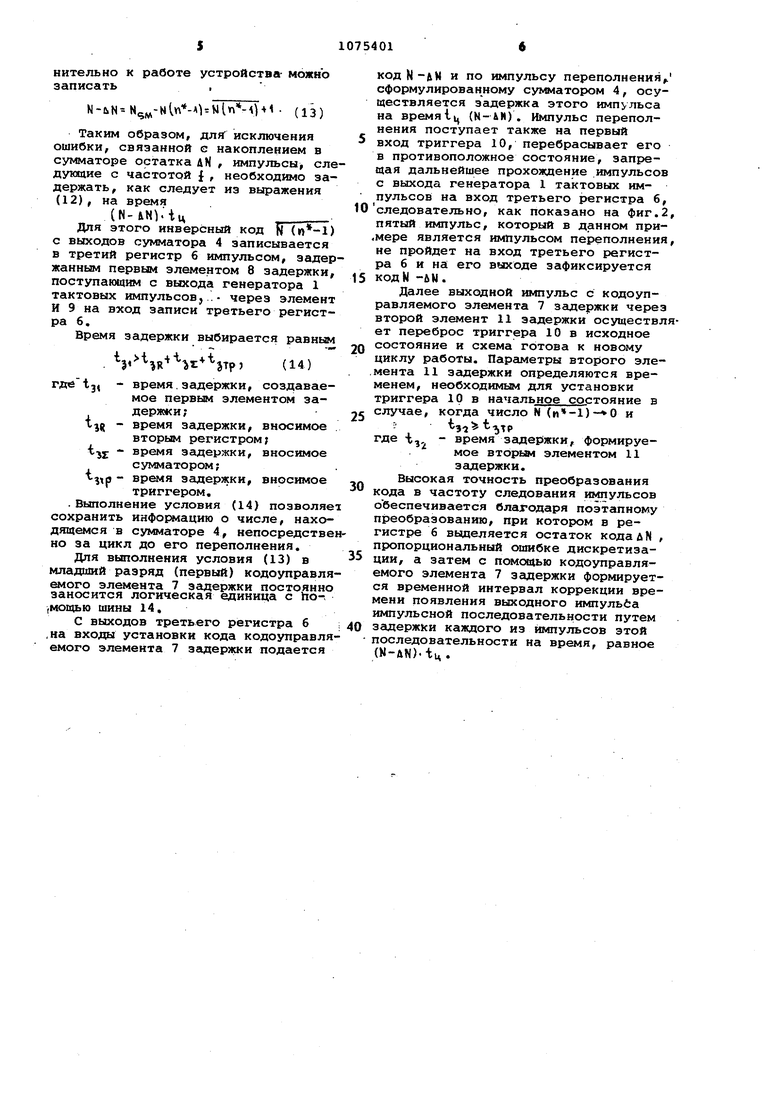

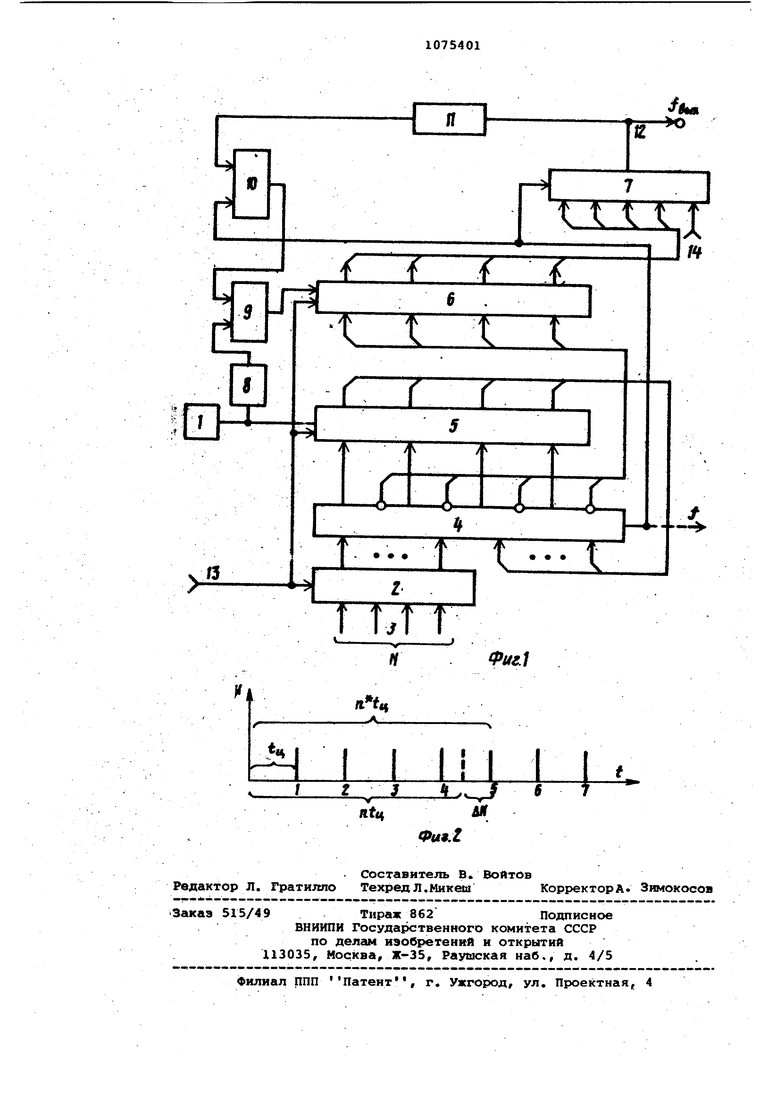

Изобретение относится к информационно-измерительной и вычислительной технике и может найти примеиение в технике частотно-цифрового моделирования и частотно-цифровых приборах с обратной связью. Известен преобразователь код частота, содержгодий генератор опорной частоты, синхронный счетчик, элементы И, на выходах которых формируются импульсные последовательности, следующие с разными частотами, су ф4ируемые на выходе устройства элементом ИЛИ-НЕ ij . Недостатком данного устройства является низкая точность преобразова ния кода в частоту следования импуль сов из-за наличия частотной модуляции в выходном сигнале. Наиболее близким к изобретению техническим решением является преобразователь кода в частоту, содержащий регистр, входы которого подключены к соответствующим шинам входного кода, сумматор, блок элементов И и генератор тактовых импульсов, ход которого подключен к первым входам блока элементов И, вторые входы которого соединены с соответствующими выходами регистра, а выходы - с соответствуквдими входами сумматора, выход которого подключен к выход(ной шине 21 . Недостатком известного устройства является низкая точность преобразования кода в частоту следования импульсов, связанная с регулярной потерей в последнем такте суммирования части входного кода (остатка 4М) изза того, что да1пульсом, сформированным на выходе преобразователя, содержимое сумматдра устанавливается в ноль. Целью изобЕ етения является повышение точности преобразования. Поставленная цель достигается тем что в преобразователь кода в частоту содержащий первый регистр, первые входы которого подключены к соответствующим шинам входного кода, cyt«4aтор, элемент И и генератор тактовых импульсов, дополнительно введены второй регистр, выходы которого соединены с соответствующими первыми входами сумматора, вторые входы которого соединены с соответствукидими выходами первого регистра, первые выходы - с соответствующими первыми входами второго регистра, вторые выходы - с соответствующими первьили входами третьего регистра, а третий выход - с первым входом триггера и первьм входс 4 кодоуправлнемого элемента задержки, выход которого подключен к выходной шине, второй вход к шине записи , а третьи входы к соответствующим выходам третьего регистра, второй вход которого соединен с вторыми входгили первого и второго регистров и установочной шиной, а третий в;сод - с выходом элемента И, первый вход которого через первый элемент задержки подключен к выходу reijepaTopa импульсов и третьему входу второго регистра, а второй вход соединен с выходом триггера, второй вход которого через второй элемент задержки подключен к выходной шине. На фиг. 1 представлена структурная электрическая схема преобразователя .кода в частоту; на фиг. 2 диагрс1мма, пояснякицая его работу. Устройство содержит генератор 1 тактовых импульсов, первый.регистр 2, входы которого соединены с шинами 3 входного кода N, сумматор 4, второй регистр 5, выходы которого соединены с первыми входами сумматора 4, вторые входы которого соединены с выходами первого регистра 2, инверсные выходы сумматора 4 через третий регистр 6 соединены с входами установки кода кодоуправляемого элемента 7 задержки, а прямые выходы - с входами второго регистра 5; выход генератора 1 тактовых импульсов соединен с входом записи второго регистра 5 и через первый элемент 8 задержки - с первым входом элемента И 9, второй вход которого соединен с выходом триггера 10, а выход с входом записи третьего регистра 6, выход пе1 еполнения сумматора 4 соединен с входом кодоуправляемого элемента 7 задержки и с первым входом триггера 10, выход кодоуправляемого элемента 7 згщержки через второй элемент 11 задержки соединен с вторым входом триггера 10 и с выходной шиной 12 преобразователя кода в частоту следования импульсов, синхронные входы регистров 2,5 и 6 соединены с усаановочной шиной 13 преобразователя, а вход первого разряда установки кода кодоуправляемого элемента 7 задержки соединен с шиной 14 записи 1 . Код К поступает на вход преобразователя кода в частоту следования импульсов , В преобразователе ироисходит ft кратное суммирование кода, при этом число циклов, необходимое для формирования наперед заданной суммы Neu г может быть записано Принимая длительность цикла заполнения равной где1 - эталонная частота, задающая цикл-такт заполнения. Частота следования импульсов, фиксирующих суммы, может быть записана-.i. Из (1) и (3) следует Из (4) следует, что частота пре образования i прсэпорциональна вход ному коду k , Фиксацня суммы импульссм может произойти при условии h.N а (5) т.е. импульс, фиксирующий суммуN в силу дискретного характера появи ся при условии MsM + ДМ где лМ - остаток, который может на ходиться в пределах О А N i М , п - целое число циклов суммир вания, необходимое для вы полнения условия (6). Из условия (1) и (6) следует 1Ц1.„,, где 1 - коэффициент переполнени наперед заданной суммы Коэффициент переполнения напере заданной суммы К определяет часть длительности цикла, величина котоiporo пропорциональна остатку кода который равен AK-n N-Ne;,(8) Приведем выражение (8) к числу циклов суивлирования i«v-«.eM М К-« -JP Выразим (9) через длительность цикла заполнения. Тогда (9) запишется ,. ill.4 ,... 4 « 4 N ч Время накопления Тц наперед зад ной сук1мы (фиг. 2) может быть запи сано .Тц-% 1 -тиЧ -1гК,(11 где )1 ц - время накопления за такт до фиксации им пульсом наперед заданной суммы; (1 - дополнительный врем ной интервал, компе сирующий ошибку пре разования . После сокращения выражения (11) на весовой коэффициент преобразова ния К„р5 - получим, (( 12) При выполнении услбвия (12) в выражении (4) частота преобразования it прямо пропорциональна входному (соду . tj в широком диапазоне его изменения. Преобразователь кода в частоту работает следующим образе. Перед началом работы на шину 13 поступает сигнал предварительного сброса, который устанавливает регист ры 5 и 6 в При каждом изменении входного кода Н на шинах 3 на шинах 13 появляется импульс занесения информации в первый регистр 2, а второй 5 и третий 6 регистры при этом устанавливаются в . Таким образом, на первые входы сумматора 4 поступает код с выхода второго регистра 5, а на вторые входы сукматора 4 поступает кодН , записанный в первом регистре 2, который складывается с содержанием второго регистра 5. В момент поступления импульса от генератора 1 тактовых импульсов полученная сумма записывается во второй регистр 5. Таким образом, данная сумма, записанная во втором регистре 5, будет слагаемым для последующего прибавления числа. Разрядная сетка сумматора 4 заполняется циклически входным кодом.:. При этом число циклов, необходимое для заполнения разрядной сетки сумматора 4, определяется выражением (1). При этом цикл заполнения.сумматора 4 выбирается равнь( в соответствии с выражением (2) что соответствует частоте появления импульсов .переполнения сумматора 4 со-, ответственно i .. , I«Ti- При этом емкость сумматора 4 определяется в соответствии с выражением (12) ) + (M-uN). где И () - число, занесенное в сумматор 4 за цикл до его переполнения; (N-bN) - ошибка суммирования. Импульс переполнения (фиг. 2) вырабатывается сумматором 4 только в момент появления очередного импульса от генератора 1 тактовых импульсов.. До этого времени в сумматоре 4 накап ливается остатоклМ , как это следует из выражения (8), так как, в оЛцем случае, для заполнения сумматора 4 потребуется не целое, а дрюбное количество циклов заполнения. Из выражения (12) следует, что если N () - число, занесенное в сумматор 4 до его переполнения, то ошибку суммирования (Н-ДИ) пример

нительно к работе устройства- можно записать

N-bN-N -Nlv -AbVlln -l)

:i3)

Таким образом, исключения ошибки, связанной с накоплением в сумматоре остатка дН , импульсы следующие с частотой f, необходимо задержать, как следует из выражения (12), на время .

(N-iNVtu

Для этого инверсный код R () с выходов сумматора 4 записывается в третий регистр 6 импульсом, задержанным первым элементом 8 задержки, поступающим с выхода генератора 1 тактовых импульсов, .- через элемент И 9 на вход записи третьего регистра 6.

Время задержки выбирается равньаи

t,.,t,.4t..t

.

(14)

где1з« - время.задержки, создаваемое первым элементом задержки;д. - время задержки, вносимое

вторым регистром; t-jj - время Зсщержки, вносимое

сумматором; - время задержки, вносимое

триггером.

. Выполнение условия (14) позволяет сохранить информацию о числе, находящемся в сумматоре 4, непосредственно за цикл до его переполнения. Для выполнения условия (13) в младший разряд (первый) кодоуправля&ЛОГО элемента 7 задержки постоянно заносится логическая единица с ho-,

,мо1цью шины 14.

С выходов третьего регистра б ,на входы установки кода кодоуправляемого элемента 7 задержки подается

код N -лМ и по импульсу переполнения,. сформулированному сумматором 4, осуществляется задержка этого импульса на время ц (И-ЛН). Шлпульс переполнения поступает также на первый вход триггера 10, перебрасывает его в противоположное состояние, запрещая дальнейшее прохождение импульсов с выхода генератора 1 тактовых импульсов на вход третьего регистра 6, следовательно, как показано на фиг.2 пятый импульс, который в данном при,мере является импульсом переполнения не пройдет на вход третьего регистра 6 и на его выходе зафиксируется кодН -йЫ.

Далее выходной импульс с кодоуправляемого элемента 7 задержки через второй элемент 11 задержки осуществлет перюброс триггера 10 в исходное состояние и схема готова к новому циклу работы. Параметры второго эле,мента 11 задержки определяются временем, необходимым для установки триггера 10 в начальное состояние в случае, когда число N () и

- -j t-jj-jp

где i, - время задержки, формируе мое вторьм элементом 11 задержки.

Высокая точность преобразования кода в частоту следования иш ульсов обеспечивается благодаря поэтапному преобразованию, при котором в регистре б вьвделяется остаток кодадН , пропорциональный ошибке дискретизации, а затем с псялощью кодоуправляемого элемента 7 задержки формируется временной интервал коррекции времени появления выходного импульба импульсной последовательности путем задержки каждого из импульсов этой последовательности на время, разное (N-AN).tn.

л

ш

tJLJ o

e

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ АНАЛОГОВЫХ СИГНАЛОВ В ИМПУЛЬСНУЮ ПОСЛЕДОВАТЕЛЬНОСТЬ, МОДУЛИРОВАННУЮ ПО ВРЕМЕНИ | 2011 |

|

RU2471287C1 |

| Устройство для регулирования расхода | 1984 |

|

SU1171759A1 |

| Цифровой генератор | 1986 |

|

SU1347164A1 |

| Преобразователь кода в частоту с переменным коэффициентом преобразования | 1984 |

|

SU1179542A1 |

| Устройство для контроля параметров объектов | 1989 |

|

SU1695270A1 |

| Генератор последовательности чисел | 1981 |

|

SU999032A1 |

| Устройство для контроля параметра объекта | 1991 |

|

SU1833841A1 |

| Устройство для допускового контроля объекта | 1984 |

|

SU1246060A1 |

| Устройство для определения максимальной гармоники спектра Уолша | 1984 |

|

SU1211751A1 |

| ПРЕОБРАЗОВАТЕЛЬ АНАЛОГОВЫХ СИГНАЛОВ В ИМПУЛЬСНУЮ ПОСЛЕДОВАТЕЛЬНОСТЬ, МОДУЛИРОВАННУЮ ПО ВРЕМЕНИ | 2008 |

|

RU2377721C1 |

ПРЕОБРАЗОВАТЕЛЬ КОДА В ЧАСТОТУ, содержащий первый регистр, первые входы которого подключены к соответствующим шинам входного кода, сумматор, элемент И и генератор тактовых импульсов, отличающийс я тем, что, с целью повышения точности преобразования, в него введены второй регистр, выходы которого соединены с соответствующими первыми входами сумматора, вторые входы которого соединены с соответствующими выходами первого регистра, первые выходы - с соответствующими первыми входами второго регистра, вторые выходы - с соответствующими первыми входами третьего регистра, а третий выход - с первым входом триггера и первым входом кодоуправляемого элемента задержки, выход которого подключен к выходной шине, второй вход - к шине записи 1, а третьи входы - к соответствующим выходам третьего регистра, второй вход которого соединен с вторили входами первого и второго регистро:в и установочной шиной, а третий -вход - с 9 выходом элемента И, первый вход ко1(0 торого через первый элемент задержки Uподключен к выходу генератора юшуль F сов и третьему входу второго регистра, .а второй вход соединен свыходом триггера,, второй вход которого через 2 второй элемент задержки подклю1чен к выходной шине. о - ел О

т тлт

Фиг.1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Гутников B.C | |||

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Л | |||

| , с | |||

| Ручная тележка для грузов, превращаемая в сани | 1920 |

|

SU238A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Мельников А.А | |||

| и др | |||

| Обработка частотных и временных импульсных сигналов | |||

| М., Энергия, 1976, с | |||

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-02-23—Публикация

1982-11-17—Подача