через элемент И 15 триггер 9 устанавливается в единичное состояние, а в регистр 5 сдвига записывается I в младший разряд. Если контро- лир.уемьш параметр меньше нижней границы допуска, то на выходе преобразователя аналог-длительность импульса появляется сигна..п логического нуля, который через элемент НЕ 24 и элемент И 14 поступасгт на вы- ход устройства для сигнализации и через элемент ИЛИ 20 запускает од- новибратор 7, который возвращает устройство в исходное состояние. Если контрольный параметр находится в поле дрпуска, то на выходе преИзобретение относится к автоматике и вычислительной технике и может быть использовано для контроля процессов в различных технологических объектах, например, .цизельэлектри- ческих агрегатах электростанций.

Цель изобретения повьппение достоверности контроля.

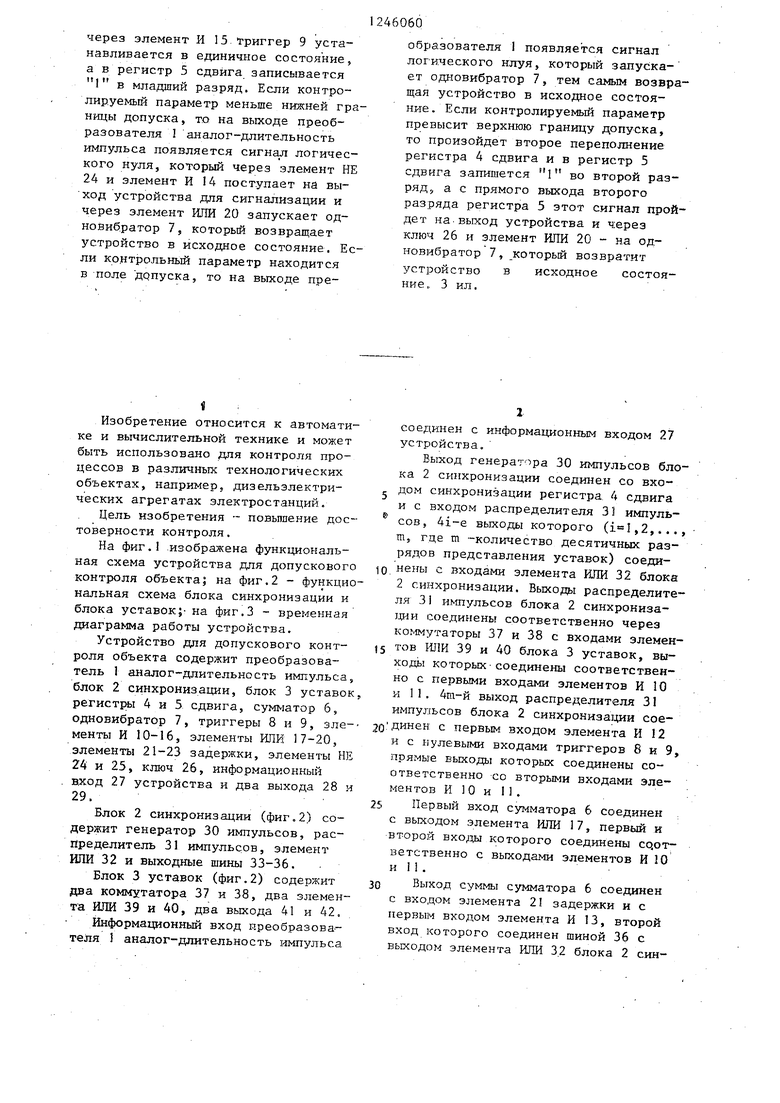

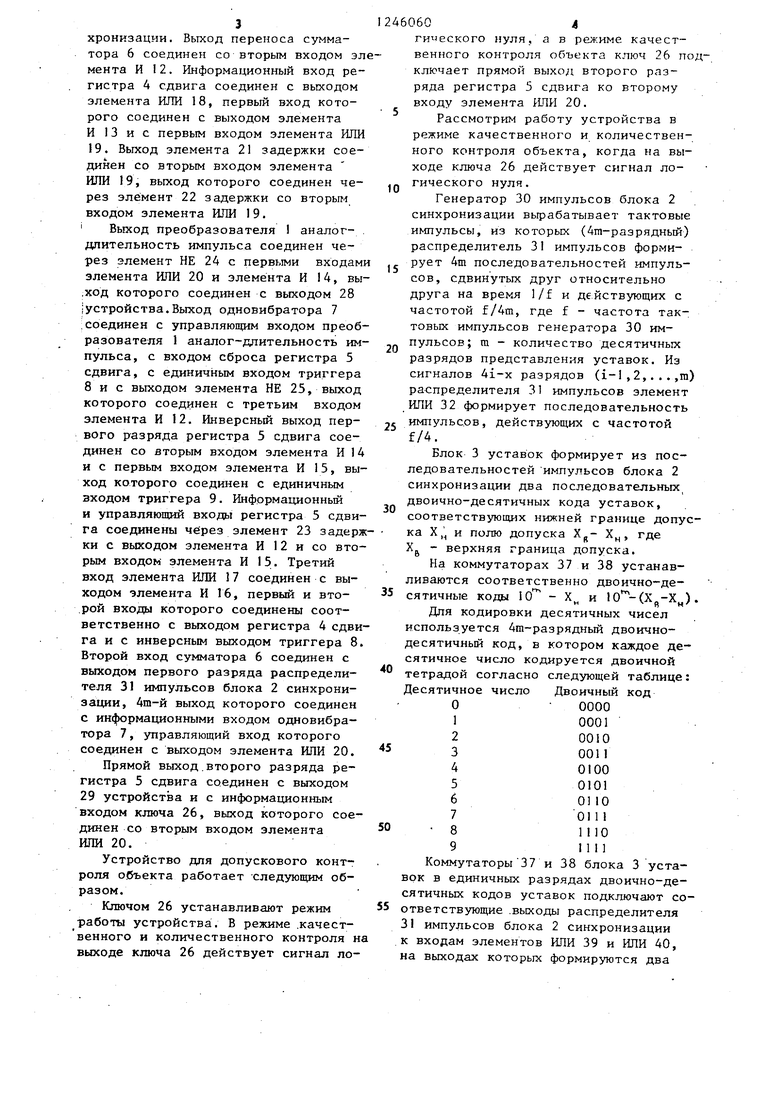

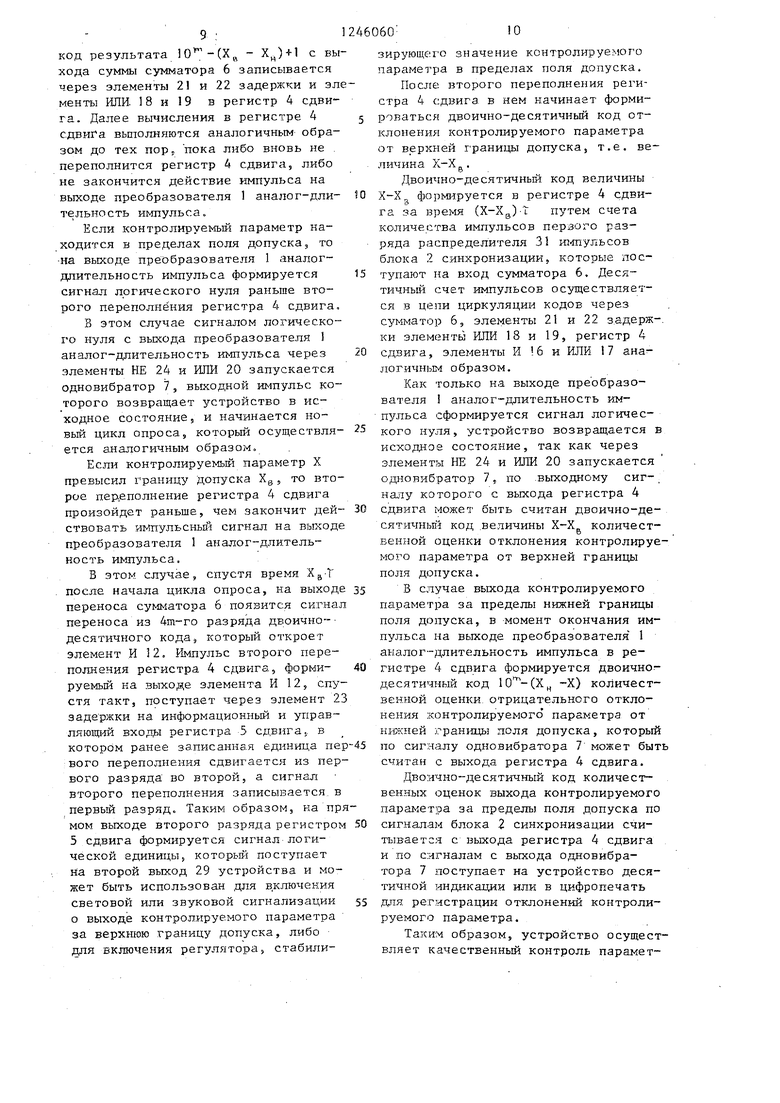

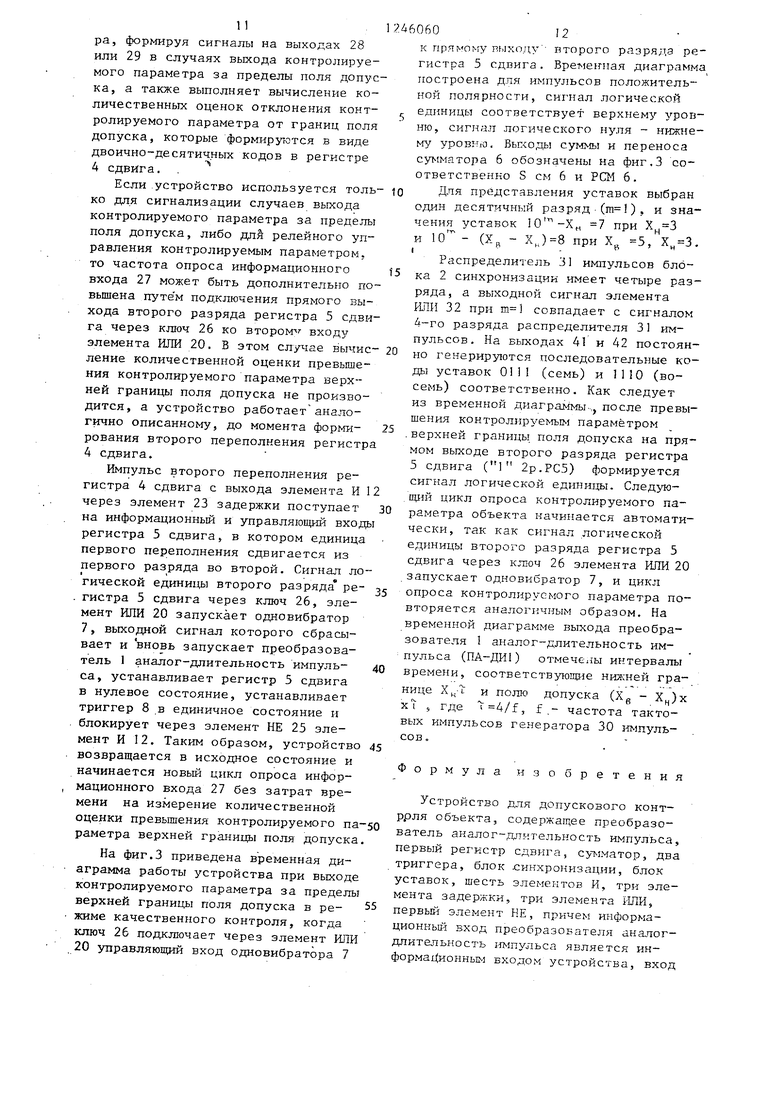

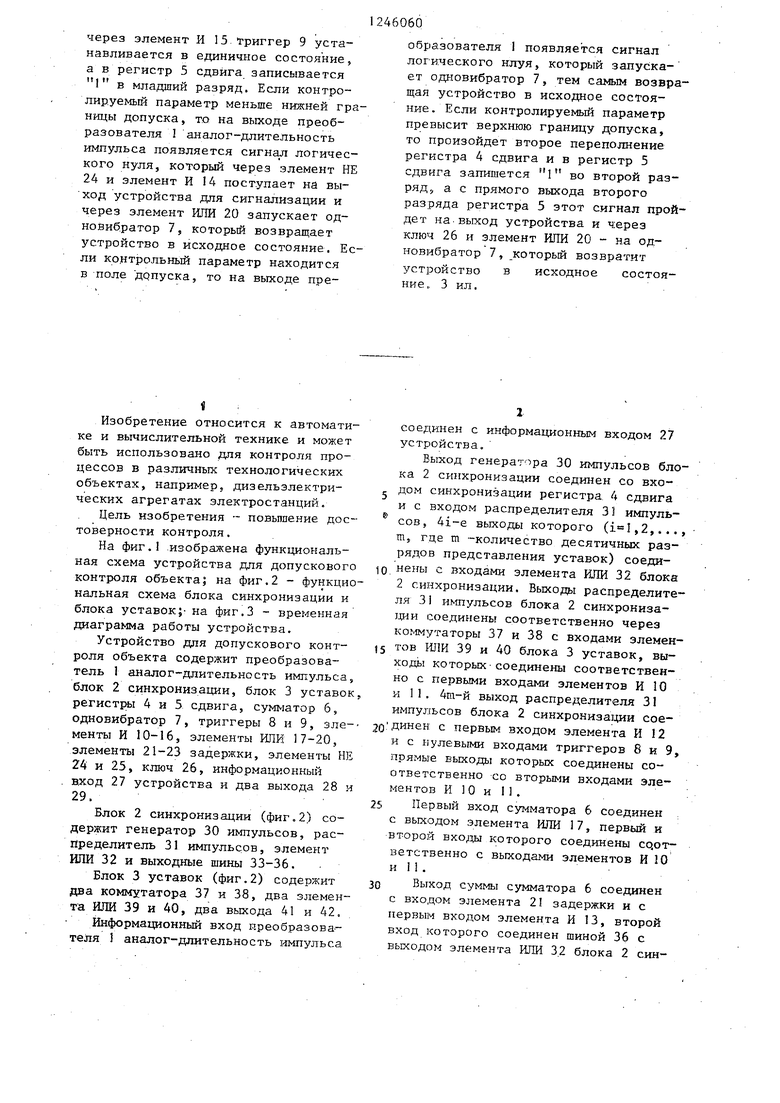

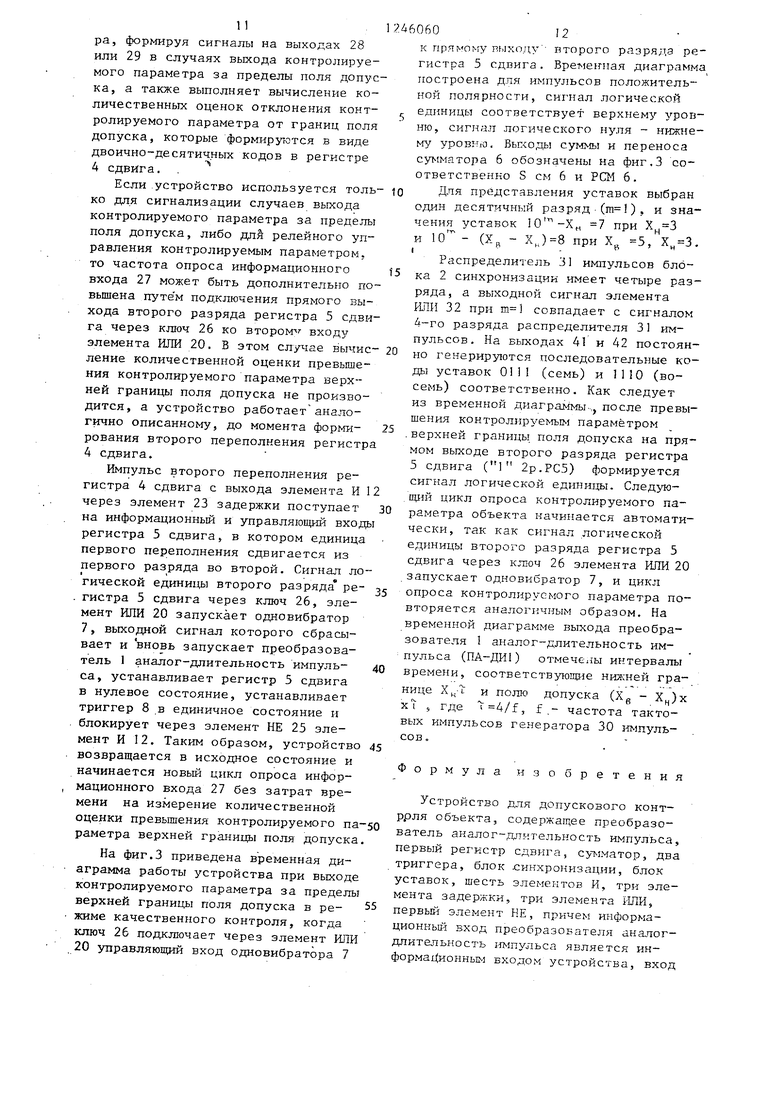

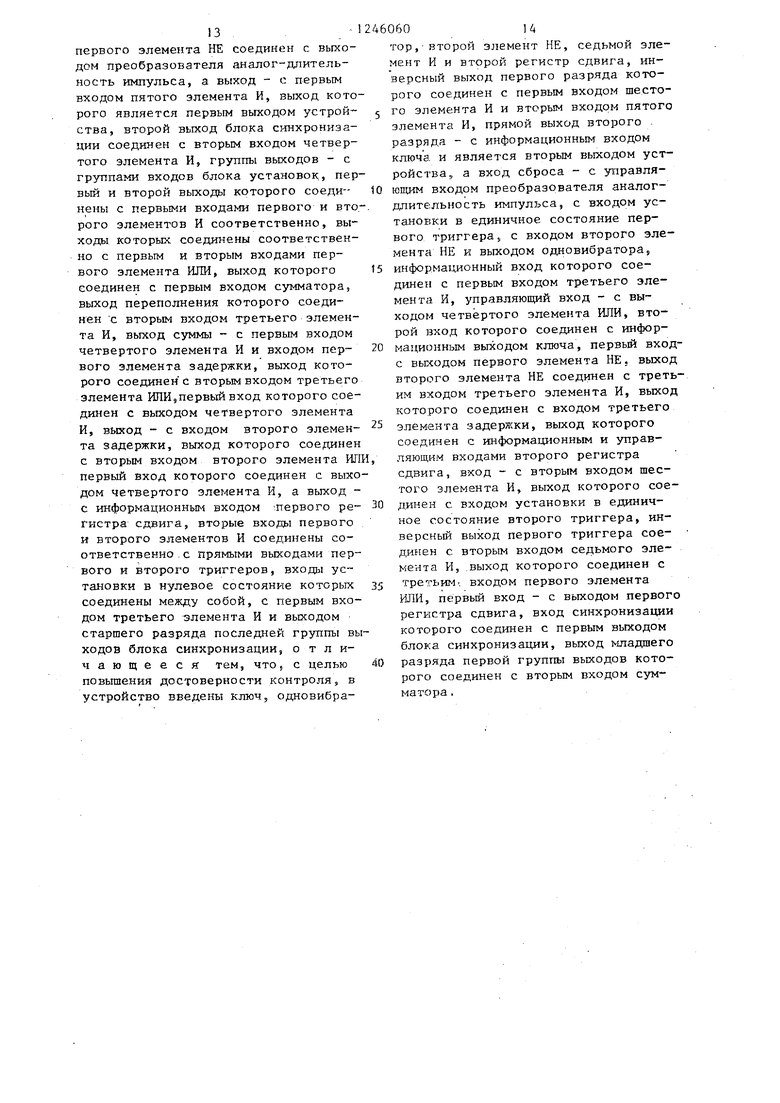

На фиг.1 изображена функциональная схема устройства для допускового контроля объекта на фиг.2 - функциональная схема блока синхронизации и блока уставок5 на фиг.З - временная диаграмма работы устройства.

Устройство для допускового контроля объекта содержит преобразователь 1 аналог-длительность импульса, блок 2 синхронизации, блок 3 уставок регистры 4 и 5, сдвига, сумматор б, одновибратор 7, триггеры 8 и 9, элементы И 10-16, элементы ИЛИ 17-20, элементы 21-23 задержки, элементы НЕ 24 и 25, ключ 26, информационный вход 27 устройства и два выхода 28 и 29.

Блок 2 синхронизации (фиг.2) содержит генератор 30 импульсов, распределитель 31 импульсов, элемент ИЛИ 32 и выходные шины 33-36.

Блок 3 уставок (фиг.2) содержит два коммутатора 37 и 38, два элемента ИЛИ 39 и 40, два выхода 41 и 42.

Информационный вход иреобразова-- теля 1 аналог-длительность импульса

образователя 1 появляется сигнал логического нлуя, который запускает одновибратор 7, тем самым возвращая устройство в исходное состояние. Если контролируемый параметр превысит верхнюю границу допуска, то произойдет второе переполнение регистра 4 сдвига и в регистр 5 сдвига запишется 1 во второй разряд, а с прямого выхода второго разряда регистра 5 этот сигнал пройдет на выход устройства и через ключ 26 и элемент ИЛИ 20 - на одновибратор 7, который возвратит устройство в исходное состояние,, 3 ил.

соединен с информационным входом 27 устройства.

Выход генератора 30 импульсов блока 2 синхронизации соединен со вхоJ дом синхронизации регистра. 4 сдвига и с входом распределителя 31 импульсов, выходы которого (,2,... m, где m -количество десятичных разрядов представления уставок) соеди10, нены с входами элемента ИЛИ 32 блока 2 синхронизации. Выхода: распределителя 3I импульсов блока 2 синхронизации соединены соответственно через ко. - мутаторы 37 и 38 с входами элемен15 тов ИЛИ 39 и 40 блока 3 уставок, вы- ходь которых-соединены соответственно с первыми входами элементов И 10 и 11. 4га-й выход распределителя 31 импульсов блока 2 синхронизации сое3,р. динен с первым входом элемента И 12 и с нулевыми входами триггеров 8 и 9 прямые Б:ЫХОДЫ которых соединены соответственно со вторыми входами элементов И 10 и 1 1 .

25 Первый вход сумматора 6 соединен с выходом элемента ИЛИ 17, первый и второй которого соединены со.от- ветственно с выходами элементов И 10 и I 1 .

30 Выкод суммы сумматора 6 соединен с входом элемента 21 задержки и с первым входом элемента И 13, второй вход которого соединен шиной 36 с выходом элемента ИЛИ 32 блока 2 сии3

хронизации. Выход переноса сумматора 6 соединен со вторым входом элемента И 12. Информационный вход регистра 4 сдвига соединен с выходом элемента ИЛИ 18, первый вход которого соединен с выходом элемента И 13 и с первым входом элемента ИЛИ 19. Выход элемента 21 задержки соединен со вторым входом элемента ИЛИ 19, выход которого соединен через элемент 22 задержки со вторым входом элемента ИЛИ 19. Выход преобразователя аналог- , длительность импульса соединен через элемент НЕ 24 с первыми входами элемента ИЛИ 20 и элемента И 14, вы- ход которого соединен с выходом 28 устройства.Выход одновибратора 7 соединен с управляющим входом преобразователя 1 аналог-дпитальность импульса, с входом сброса регистра 5 сдвига, с единичным входом триггера 8 и с выходом элемента НЕ 25, выход которого соединен с третьим входом элемента И 12. Инверсный выход первого разряда регистра 5 сдвига соединен со вторым входом элемента И 14 и с nepBbiM входом элемента И 15, выход которого соединен с единичным входом триггера 9. Информационный и управляющий входы регистра 5 сдвига соединены через элемент 23 задержки с выходом элемента И 12 и со вторым входом элемента И 15. Третий вход элемента ИЛИ 17 соединен с выходом элемента И 16, первый и второй входы которого соединены соответственно с выходом регистра 4 сдвига и с инверсным выходом триггера 8. Второй вход сумматора 6 соединен с выходом первого разряда распределителя 31 импульсов блока 2 синхронизации, 4т-й выход которого соединен с информационными входом одновибра- тора 7, управляющий вход которого соединен с выходом элемента ИЛИ 20.

Прямой выход.второго разряда регистра 5 сдвига соединен с выходом 29 устройства и с информационным входом ключа 26, выход которого соеинен со вторым входом элемента ИЛИ 20.

Устройство для допускового контроля объекта работает следующим образом.

Ключом 26 устанавливают режим аботы устройства. В режиме .качест- енного и количественного контроля на ыходе ключа 26 действует сигнал ло0

0

460604

ги еского нуля, а в режиме качественного контроля объекта ключ 26 подключает прямой выход второго разряда регистра 5 сдвига ко второму входу элемента ИЛИ 20.

Рассмотрим работу устройства в режиме качественного и количественного контроля объекта, когда на выходе ключа 26 действует сигнал логического нуля.

Генератор 30 импульсов блока 2 синхронизации вырабатывает тактовые импульсы, из которых (4in-pa3рядный) распределитель 31 импульсов формирует 4т последовательностей импульсов, сдвинутых друг относительно друга на время 1/f и действующих с частотой f/4m, где f - частота тактовых импульсов генератора 30 импульсов; m - количество десятичных разрядов представления уставок. Из сигналов 4i-x разрядов (i-I,2,...,т) распределителя 31 импульсов элемент ИЛИ 32 формирует последовательность

5 импульсов, действующих с частотой f/4.

Блок 3 уставок формирует из последовательностей импульсов блока 2 синхронизации два последовательных двоично-десятичных кода уставок, соответствующих нижней границе допуска и полю допуска Х , где Xg - верхняя граница допуска.

На коммутаторах 37 и 38 устанавливаются соответственно двоично-де5 сятичные коды Ю - Х и (Хд-Х„).

Для кодировки десятичных чисел используется 4т-разрядный двоично- десятичный код, в котором каждое десятичное число кодируется двоичной

0 тетрадой согласно следующей таблице: Десятичное число Двоичный код

0 0000

10001

200 Ш 3 ООП

40100

50101

601 10

70111 0 -81110

91111

Коммутаторы 37 и 38 блока 3 уставок в единичных разрядах двоично-десятичных кодов уставок подключают со- ответствующие .выходы распределителя 31 импульсов блока 2 синхронизации к входам элементов ИЛИ 39 и ИЛИ 40, на выходах которых формируются два

последовательных двоично-десятичных кода уставок Х и (Хц-Х соответственно/

Пуск устройства осуществляется автоматически от нулевого сигнала на выходе преобразователя 1 аналог-длительность импульса, который через элементы НЕ 24 и ИЛИ 20 запускает од новибратор 7, формирующий на выходе одиночный импульс из последовательности импульсов Ага-го выхода распределителя 31 импульсов блока 2 синхронизации.

Одиночный импульс одновибратора запускает преобразователь 1 аналог- длительность импульса, устанавливает в нулевое состояние регистр 5 сдвига, устанавливает в единичное состояние триггер 8 и блокирует через элемент НЕ 25 элемент И 12.

Преобразователь 1 аналог-длительность импульса преобразует аналоговой сигнал контролируемого параметра и импульсньш сигнал, длительность которого пропорциональна величине аналогового сигнала на входе 27. Импульсный сигнал преобразователя аналог-длительность импульса че рез элемент НЕ 24 блокирует элемент И 14 на время его действия.

Триггер 8 в единичном состоянии пропускает сигнал с прямого выхода на элемент И 10, через который последовательный двоично-десятичный код установки 10 Х„ поступает с выхода элемента ИЛИ 39 блока 3 уставок , на первьй вход элемента ИЛИ 17. В это время триггер 8 блокирует сигналом инверсного выхода элемент И 16 что обеспечивает стирание информации сдвигаемой под- действием тактовых импульсов генератора 30 импульсов блока 2 синхронизации из регистра 4 сдвига. Во время действия на первом входе сумматора 6 младшего разряда двоично-десятичного кода уставки 10. Xj на втором входе сумматора 6 действует импульс первого разряда распределителя 31 импульсов блока 2 синхронизации. Сумматор 6 осуществляет последовательно во времени за время 4т, тактов прибавление к начальному двоичному-десятичному коду уставки Х единицы младшего разряда, а последов ательный двоично- десятичный код результата через эле- менты 21 и 22 задержки ,и элементы ИЛИ 18 и 19 записывается в регистр

25

460606

4 сдвига под действием тактовых импульсов генератора 30 импульсов блока 2 синхронизации. Регистр 4 сдвига содержит количество разрядов п 5 4т-2 и дополняется элементами 21 и 22 задержки на такт до 4т раз- рядор.

Спустя 4т тактов после установки в единичное состояние триггер 8 сбра- сывается в нулевое состояние импульсом 4т-го выхода распределителя 31 импульсов блока 2 синхронизации.

В нулевом состоянии триггер 8 бло- кирует элемент И 10 и открывает эле- мент И 16, подключая через элемент 1-ШИ 7 выход регистра 4 сдвига к первому входу сз матора 6. Текущий двои1гно-десятичный код под действием тактовых импульсов генератора 30 им- пульсов блока 2 синхронизации сдви- 1аетс;я, начиная с младагего разряда, с выхода регистра 4 сдвига через элементы И 16, ИЛИ 17 на первый вход сумматора 6, на втором входе которо - го во время сдвига младшего разряда двоично-десятичного кода действует импульс пе.рвого разряда распределителя 3 импульсов блока 2 синхронизации. Двоичньм сумматор 6 последо30 вательно за время 4ш тактов увеличивает значение текущего двоично-десятичного кода регистра 4 сдвига на единицу мл:адшего разряда, а новое значение двоично-десятичного кода

35 записывается с выхода суммы сумматора 6 через элементы 21 и 22 задержки и элементы ИЛИ 18 ,и 19 в регистр 4 сдвига.

В дальнейшем устройство работает

0 аналогичным образом, и каждые 4т так- тов двоично-десятичный код в регистре 4 сдвига увеличивается на единицу. Так будет продолжаться до тех пор, пока в младшей тетраде текущего

5 значения двоично-десятичного кода на выходе суммы сумматора 6 не сформируется, код 1000 (восемь). В этом случае Бо время действия единичного сигнала четвертого разряда младшей тет50 рады на выходе суммы сумматора 6 открывается элемент И 13, через который и,мпульс вьсхода элемента ИЛИ 32 блока 2 синхронизации записывается через элементы ИЛИ 18 и 19 соответст55 венно в регистр 4 сдвига и элемент 22 задержки по месту действия соответственно сигналов второго и третьего разрядоЕ: кода младшей тетрады. Следовательно, вместо кода 000 в регистр 4 сдвига записывается код 1110, который соответствует десятичному числу восемь.

В следующие 4т тактов код младшей тетрады 1110 (восемь) увеличивается на единицу, и в регистр 4 сдвига записывается в младшей тетраде код 1111 (девять), который в следующем цикле обеспечивает автоматически в процессе двоичного суммирования кода 1П1 с единицей младшего разряда формир оваКроме того, в случае выхода конт ролируемого параметра за Н ижнюю гра ницу допуска, сигнал логического нуля с выхода преобразователя 1 ана лог-длительность импульса поступает через элементы НЕ 24 и.РШИ 20 на 10 управляющий вход одновибратора JfKO- торый вьзделяет ближайший импульс из последовательности импульсов, дей- ствзгющей на 4т-ом выходе распределителя 31 импульсов блока 2 синхрониние в сумматоре 6 сигнала переноса из

четвертого разряда младшей тетрады

,в первый разряд следующей тетрады. fs зации. Запуск одновибратора 7 воз Таким образом обеспечивается десятич- вращает описанным образом устройство в исходное состояние, и устройство начинает отрабатывать следзто- щий цикл опроса контролируемого параметра на информационном входе 27.

ньй счет в регистре .4 сдвига с начального двоичного-десятичного кода установки Ю - Х. Дальнейшие вычисления в регистре 4 сдвига выполняются аналогичным образом, а перенос из одной тетрады в следующую выполняется таким же образом, как и описанньш процесс переноса из нпад- шей тетрады во вторую тетраду.

Так будет продолжаться до тех пор, пока либо не переполнится регистр 4 сдвига, либо на выходе преобразователя 1 аналог-длительность импульса не закончится импульсный сигнал и сформируется сигнал логического нуля, j

Если контролируемый параметр X

20

Если контролируемый параметр X больше нижней границы допуска Х-, то

регистр 4 сдвига переполнится раньше чем закончит действовать импульсный

25 сигнал на выходе преобразователя I аналог-длительность импульса. В этом случае, спустя время после начала цикла опроса (формирования импульса на выходе одновибратора 7),

30 на выходе переноса сумматора 6 появляется сигнал переноса из 4т-го разряда двоично-десятичного кода, который открывает элемент И i,2. Импульс 4т-го разряда распределителя 31 им30 на выходе переноса сумматора 6 появляется сигнал переноса из 4т-го разряда двоично-десятичного кода, который открывает элемент И i,2. Импульс 4т-го разряда распределителя 31 имменьше нижней границы допуска Х,

то время действия импульса на выходе 35 пульсов блока 2 синхронизации проход преобразователя 1 аналог-длительность импульса меньше интервала времени Xg-t , где - цикл суммирования единицы в сумматоре 6; f - тактовая частота генератора 30 им- пульсов; m -количество тетрад двоично-десятичного кода уставки

дит через элементы И 12, И 15 и устанавливает триггер 9 в единичное состояние на время 4т тактов. Импульс переполнения регистра 4 сдвига формируемый на выходе элемента И 12, спустя время задержки на такт, поступает через элемент 23 задержки на информационньй и управляющий входы регистра 5 сдвига и записывается в

в регистре 4 сдвига. В этом случав на выходе преобразователя 1 аналогдит через элементы И 12, И 15 и устанавливает триггер 9 в единичное состояние на время 4т тактов. Импульс переполнения регистра 4 сдвига, формируемый на выходе элемента И 12, спустя время задержки на такт, поступает через элемент 23 задержки на информационньй и управляющий входы регистра 5 сдвига и записывается в

длительность импульса формируется него в первом разряде. На. инверсном сигнал логического нуля, который выходе первого разряда 5 сдвига фор- через элемент. НЕ 24 открывает эле- мируется сигнал логического нуля, мент И 14, на втором входе которого блокирующий элементы И 14 и 15. Триггер 9 в единичном состоянии открывает элемент И 11, через который последовательный двоично-десятичный код

действует сигнал логической-единицы

инверсного выхода первого разряда регистра 5 сдвига. Сигнал логической единицы, формируемый на выходе элемента И 14, поступает на первьй выход -28 устройства и может быть ис50

уставки 10 - (Хц - Xj,) с выхода элемента ИЛИ 40 блока 3 уставки поступает, начиная с младшего разряда, на

пользован для включения световой или 55 первый вход сумматора 6.

звуковой сигнализации о выходе контролируемого параметра за нижнюю границу допуска, либо для включения ре

46060-8

гулятора, стабилизирующего значение контролируемого параметра в пределах поля допуска.

Кроме того, в случае выхода контролируемого параметра за Н ижнюю границу допуска, сигнал логического нуля с выхода преобразователя 1 аналог-длительность импульса поступает через элементы НЕ 24 и.РШИ 20 на 0 управляющий вход одновибратора JfKO- торый вьзделяет ближайший импульс из последовательности импульсов, дей- ствзгющей на 4т-ом выходе распределителя 31 импульсов блока 2 синхрони

20

Если контролируемый параметр X больше нижней границы допуска Х-, то

регистр 4 сдвига переполнится раньше, чем закончит действовать импульсный

сигнал на выходе преобразователя I аналог-длительность импульса. В этом случае, спустя время после начала цикла опроса (формирования импульса на выходе одновибратора 7),

на выходе переноса сумматора 6 появляется сигнал переноса из 4т-го разряда двоично-десятичного кода, который открывает элемент И i,2. Импульс 4т-го разряда распределителя 31 импульсов блока 2 синхронизации проход

дит через элементы И 12, И 15 и устанавливает триггер 9 в единичное состояние на время 4т тактов. Импульс переполнения регистра 4 сдвига формируемый на выходе элемента И 12, спустя время задержки на такт, поступает через элемент 23 задержки на информационньй и управляющий входы регистра 5 сдвига и записывается в

50

уставки 10 - (Хц - Xj,) с выхода элемента ИЛИ 40 блока 3 уставки поступает, начиная с младшего разряда, на

Сумматор 6, как было ранее описано, прибавляет единицу к начальному коду уставки, и двоично-десятичньш

9 :

код результата - Х) + 1 с выхода суммы сумматора 6 записывается через элементы 21 и 22 задержки и эл менты ИЛИ. 18 н 19 в регистр 4 сдвига. Далее вычисления в регистре 4 сдвига выполняются аналогичным образом до тех пор, пока либо вновь не . переполнится регистр 4 сдвига, либо не закончится действие импульса на выходе преобразователя 1 аналог-длительность импульса.

Если контролируемый параметр находится в пределах поля допуска, то на выходе преобразователя 1 аналог- дпительность импульса формируется сигнал логического нуля раньше второго переполнения регистра 4 сдвига. В этом случае сигналом логического нуля с выхода преобразователя 1 аналог-длительность импульса через элементы НЕ 24 и ИЛИ 20 запускается одновибратор 7, выходной импульс которого возвращает устройство в исходное состояние, и начинается но- вьм цикл опроса, который осуществляется аналогичным образом.

Если контролируемый параметр X превысил границу допуска Xg, то второе пер еполнение регистра 4 сдвига произойдет раньше 5 чем закончит действовать импульсньш сигнал на выходе преобразователя I аналог-дли:тель- ность импульса.

В этом случае, спустя время после начала цикла опроса, на выходе переноса сумматора 6 появится сигнал переноса из 4т-го разряда двоично- десятичного кода который откроет элемент И 12. Импульс второго переполнения регистра 4 сдвига, форми- руемьш на выходе элемента И 12, спустя такт, поступает через элемент 23 задержки на информационньй и управляющий входы регистра 5 сдвига,, в котором ранее записанная единица первого переполнения сдвигается из первого разряда во второй, а сигнал второго переполнения записывается, в первьм разряд. Таким образом, на прямом выходе второго разряда регистром 5 сдвига формируется сигнал логической единицы, которьш поступает на второй выход 29 устройства и может быть использован для вк.пючения световой или звуковой сигна.пизации о выходе контролируемого параметра за верхнюю границу допуска, либо для включения регулятора, стабили246060

iO

зирующего значение контролируемого параметра в пределах поля допуска. После второго переполнения регистра 4 сдззига в нем начинает форми- 5 роваться двоично-десятичный код отклонения контролируемого параметра от верхней границы допуска, т.е. ве- личина Х-Х.

D

Двоично-десятичный код величины O Х-Х, формируется в регистре 4 сдвиD

га за (X-Xg)-t путем счета количества импульсов первого разряда распределителя 31 ш-шульсов блока 2 синхронизации, которые пос5 тупают на вход сумматора 6. Десятичный счет импульсов осуществляется в цепи циркуляции кодов через сумматор 6, элементы 21 и 22 задерж-. кн элементы ИЛИ 18 и 19, регистр 4

0 сдвига, э.пементы И 6 и ИЛИ 17 аналогичным образом.

Как только на выходе преобразователя 1 аналог-длительность импульса сформируется сигнал логичес5 кого нуля, устройство возвращается в исходное состояние, так как через элементы НЕ 24 и ИЛИ 20 запускается одновибратор 7, по .выходному сиг-, налу которого с выхода регистра 4

0 сдвига может быть считан двоично-де- сятичньш код ве.личины Х-Х„ количестD

венной оценки отклонения контролируемого параметра от верхней границы поля допуска.

5 В случае выхода контролируемого параметра за пределы нижней границы поля допуска, в момент окончания импульса на выходе преобразователя 1 аналог-длительность импульса в ре0 гиетре 4 сдвига формируется двоично- десятичный код (Х -X) количественной оценки, отрицательного отклонения контролируемого параметра от нижней границы поля допуска, который

по сигналу одновибратора 7 может быть считан с выхода регистра 4 сдвига.

Двоично-десятичный код количественных оценок выхода контролируемого параметра за пределы поля допуска по

0 сигналам блока .2 синхронизации счи- тыв-ается с выхода регистра 4 сдвига и по сигналам с выхода одновибратора 7 поступает на устройство десятичной индикации или в цифропечать

5 Д.ПЯ регистрации отклонений контролируемого параметра.

Таким образом, устройство осуществляет качественный контроль парамет11

pa, формируя сигналы на выходах 28 или 29 в случаях выхода контролируемого параметра за пределы поля допуска, а также выполняет вычисление количественных оценок отклонения конт- ролируемого параметра от границ поля допуска, которые формируются в виде двоично-десятичных кодов в регистре 4 сдвига.

Если устройство используется толь- ко для сигнализации случаев выхода контролируемого параметра за пределы поля допуска, либо дли релейного управления контролируемым параметром. то частота опроса информационного входа 27 может быть дополнительно по- вьппена путе м подключения прямого выхода второго разряда регистра 5 сдвига через ключ 26 ко втором входз элемента ИЛИ 20. В этом случае вычис- ление количественной оценки превышения контролируемого параметра верхней границы поля допуска не производится, а устройство работает аналогично описанному, до момента форми- рования второго переполнения регистра 4 сдвига.

Импульс второго переполнения регистра 4 сдвига с выхода элемента И 1 через элемент 23 задержки поступает на информационный и управляющий входы регистра 5 сдвига, в котором единица

40

первого переполнения сдвигается из первого разряда во второй. Сигнал логической единицы второго разряда ре- 35 гистра 5 сдвига через ключ 26, элемент ИЛИ 20 запускает одновибратор 7, выходной сигнал которого сбрасывает и вновь запускает преобразователь 1 аналог-длительность импульса, устанавливает регистр 5 сдвига Б нулевое состояние, устанавливает триггер 8 в единичное состояние и блокирует через элемент НЕ 25 элемент И 12. Таким образом, устройство 45 возвращается в исходное состояние и начинается новый цикл опроса информационного входа 27 без затрат времени на измерение количественной оценки превьшения контролируемого па-50 раметра верхней границы поля допуска.

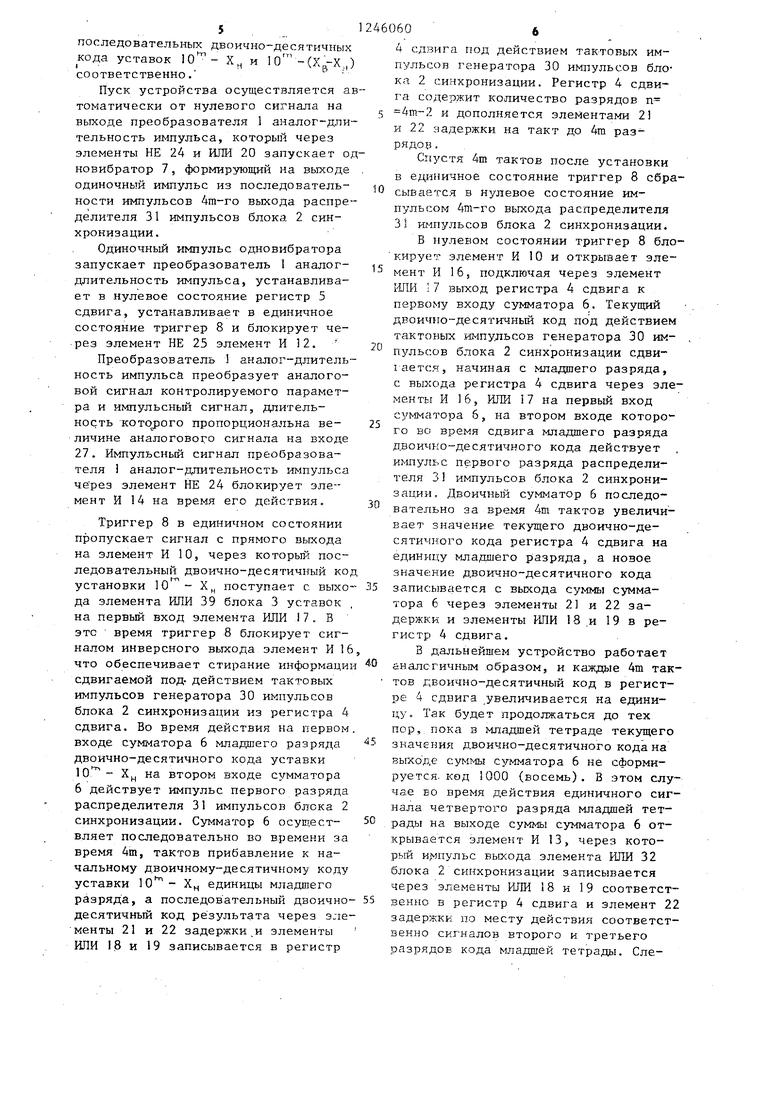

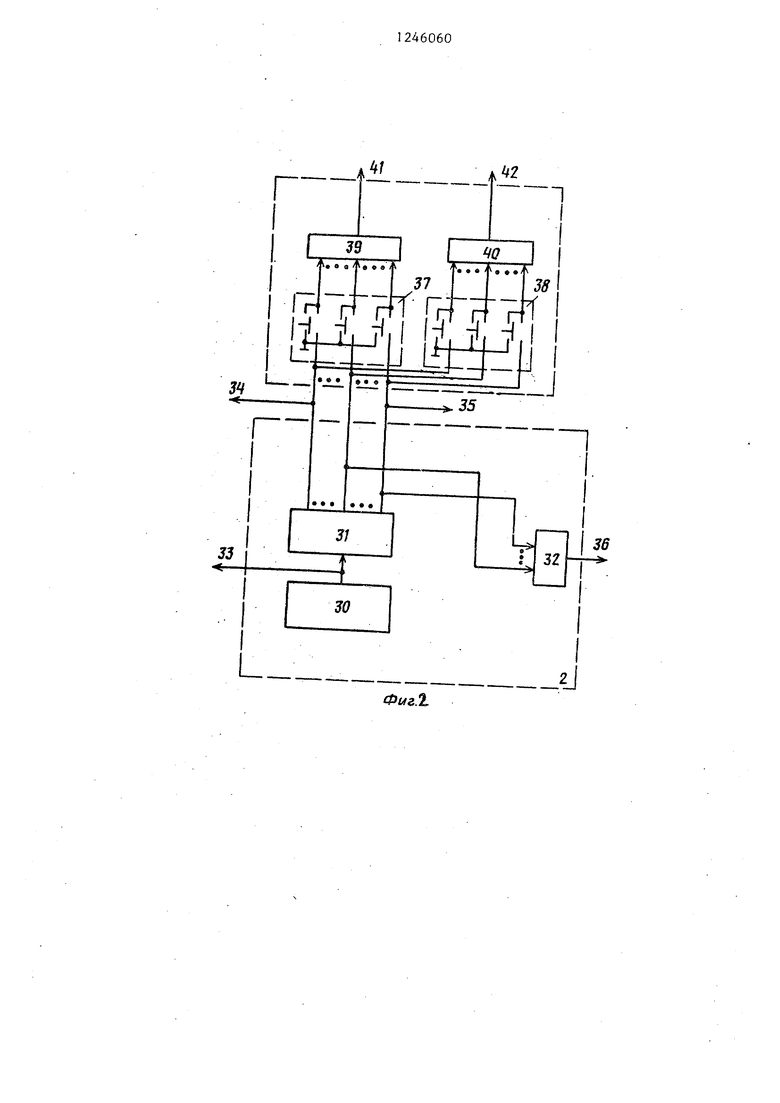

На фиг.З приведена временная диаграмма работы устройства при выходе контролируемого параметра за пределы верхней границы поля допуска в ре- 55 жиме качественного контроля, когда ключ 26 подключает через элемент ИЛИ 20 управляющий вход одновибратора 7

tO fs 20 25

О

0

5 5 0

24606012

к прямому выходу второго разряда регистра 5 сдвига. Времекмая диаграмма построена для импульсов положительной полярности, сигнал логической единицы соответствует верхнему уровню, сигнал логического нуля - нижнему уровнл. Вько,11Ы суммы и переноса сумматора 6 обозначены на фиг.З соответственно S см 6 и РСМ 6.

Для представления уставок выбран один десятичный разряд (т), и значения уставок 7 при и 10 - (Хр - при Хр 5, .

Распределитель 31 импульсов блока 2 синхронизации имеет четыре разряда, а выходной сигнал элемента ИЛИ 32 при совпадает с сигналом 4-го разряда распределителя 31 импульсов. На выходах 41 и 42 постоянно генерируются последовательные коды уставок 0111 (семь) и 1ПО (восемь) соответственно. Как следует из временной диагра мы-:, после превышения контролируемым параметром верхней границы поля допуска на прямом выходе второго разряда регистра 5 сдвига (1 2р.РС5) формируется сигнал логической единитды. Следующий цикл опроса контролируемого параметра объекта начинается автоматически, так как сигнал логической единицы второго разряда регистра 5 сдвига через ключ 26 элемента ШШ 20 запускает одновибратор 7, и цикл опроса контролируемого параметра повторяется аналогичным образом. На временной диаграмме выхода преобразователя 1 аналог-длительность импульса (ПА-ДИ1) отмече11Ы интервалы времени, соответствующие ния;ней границе X.-t и полю допуска (Xg - Х)х хТ 5 где , f .- частота тактовых импульсов генератора 30 импульсов.

Ф о

р м у л а изобретения

Устройство для допускового конт- ррля объекта, содержащее преобразователь аналог-длительность импульса, первый регистр сдвига, сумматор, два триггера, блок синхронизации, блок уставок, шесть элемектов И, Tpii элемента задержки, три элемента i-ШИ, первый элемент НЕ, причем и 1форма- ционньй вход преобразователя аналог- длительность импульса является ин- формаДионным входом устройства, вход

13

первого элемента НЕ соединен с выходом преобразователя аналог-длительность импульса, а выход - с первым входом пятого элемента И, выход которого является первым выходом устройства, второй выход блока сг-шхрониэа- ции соединен с вторым входом четвертого элемента И, группы выходов - с группами входов блока установок., первый и второй выходы которого соединены с первыми входами первого и второго элементов И соответственно, выходы которых соединены соответственно с первым и вторым входами первого элемента ИЛИ, выход которого соединен с первым входом сумматора, выход переполнения которого соединен с вторым входом третьего элемента И, выход суммы - с первым входом четвертого элемента И и входом первого элемента задержки, выход которого соединен с вторым входом третьего элемента ИЛИзПервый вход которого соединен с вь ходом четвертого элемента И, выход - с входом второго элемента задержки, выход которого соединен с вторым входом второго элемента ИЛ первый вход которого соединен с выходом четвертого элемента И, а выход - с информационным входом первого регистра сдвига, вторые вхоры первого и второго элементов И соединены соответственно , с прямыми выхюдами первого и второго триггеров, вход1з1 установки в кулевое состояние которых соединены между собой, с первым входом третьего элемента И и выходом старшего разряда последней группы выходов блока синхронизации, отличающееся тем, что,, с целью повышения достоверности контроля, в устройство введены ключ, одновибра

0

5

0

0

4606014

тор,-второй элемент НЕ, седьмой элемент И и второй регистр сдвига, инверсный выход первого разряда которого соединен с первым входом шестого элемента И и вторым входом пятого элемента И, прямой выход второго . разряда - с информационным входом ключа и является вторым выходом устройства,, а вход сброса - с управля- юп(им входом преобразователя аналог- длительность импульса, с входом установки в единичное состояние первого триггера, с входом второго элемента НЕ и выходом одновибратора, информационный вход которого соединен с первым входом третьего элемента И, управляющий вход - с выходом четвертого элемента ИЛИ, второй вход которого соединен с информационным выходом ключа, первьй вход- с выходом первого элемента НЕ. выход второго элемента НЕ соединен с третьим входом третьего элемента И, выход которого соединен с входом третьего элемента задерлски, выход которого соединен с информационным и управляющим входами второго регистра сдвига, вход - с вторым входом шестого элемента И, выход которого соединен с входом установки в единичное состояние второго триггера, ин- версньш выход первого триггера соединен с вторым входом седьмого элемента И, .выход которого соединен с третьим-, входом первого элемента ИЛИ, п€фвый вход - с выходом первого регистра сдвига, вход синхронизации которого соединен с первым выходом блока синхронизации, выход 1ушадшего разряда первой группы выходов которого соединен с вторым входом сумматора ,

5

0

5

f 39

a 9 9 I

3

J

r

J5

-

L

A/

Ц2

9 I

37

TTr

П

(;(

d

-H

ЗУ

гП

55

1

J7

зг

36

.iJ

Фиг.1

ги 30 ПШШ1Ш1ПШЛЛЯ1ШтШ11 иШПЛЛППЛ

;р pff-37

х,,{г;

fxir- w/i;

.

.„rLРедактор Н.Егорова Заказ 3998/40

Составитель В.Копьшов ТехредМ.Ходанич Корректор М.Максимишинец

Тираж 836Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 1Г3035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие,г.Ужгород,ул.Проектная, 4

.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для допускового контроляОб'ЕКТА | 1979 |

|

SU834678A1 |

| Устройство для допускового контроля параметров объектов | 1982 |

|

SU1056134A1 |

| Многоканальное устройство для до-пуСКОВОгО КОНТРОля пАРАМЕТРОВ | 1979 |

|

SU840819A1 |

| Устройство для допускового контроля | 1978 |

|

SU771619A1 |

| Устройство для контроля экспоненциальных процессов | 1984 |

|

SU1282087A1 |

| Устройство для допускового контроля | 1980 |

|

SU898390A2 |

| Устройство для вычисления показателя экспоненциальной функции | 1983 |

|

SU1129611A1 |

| Генератор циклов | 1981 |

|

SU964616A1 |

| Устройство для контроля переходных режимов объекта | 1989 |

|

SU1817062A1 |

| Устройство для контроля экспоненциальных процессов | 1990 |

|

SU1732331A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля процессов в различных технологических объектах, например дизель-электрических агрегатах электростанций, и позволяет повысить достоверность контроля. Блок 3 уставок формирует из последовательности импульсов блока 2 синхронизации два последовательных двоично-десятичных кода уставок, соответствующих нижней границе допуска и полю допуска, которые через элементы И 10 и 11, элемент ИЛИ 17 поступают на сумматор 6, ,; который последовательно увеличивает значение текущего кода регистра 4 сдвига. При переполнении регистра 4 сдвига открывается элемент И 12 и g IJ-N) 4;; О) О сь

| Устройство для допускового контроляОб'ЕКТА | 1979 |

|

SU834678A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для допускового контроля параметров объектов | 1982 |

|

SU1056134A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1986-07-23—Публикация

1984-12-30—Подача