BeHTWieft, a выхоа является вторым выхопом логического блоха.

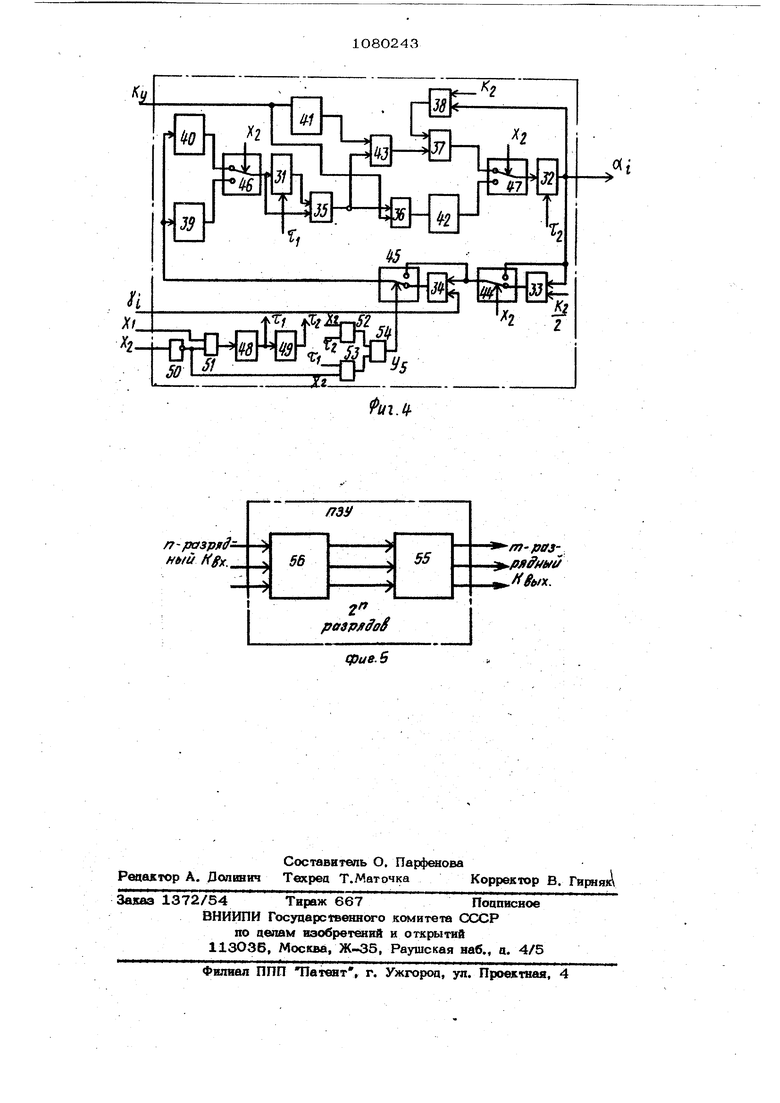

3. Устройство по п. 2, 6 т л и ч а ю ш е е с я тем, что вычислительный блок содержи трегистр промвку точного результата, регистр конечного результата шесть сумматоров кодов, причем первый, второй и третий сумматоры коаов работают в режиме сложения коцов, а четвер тый, пятый, шестой в режиме вычитания коаов, четыре функциональных преобразо вателя кодов, умножитель коаов, четыре переключателя коаов, два одновибратора, два эл и1ента ИЛИ, два элемента И, причем выход регистра конечного результата связан с одним :из входов третьего сумматора кодов, второй вход которого предназначен для подачи кода постоянного коэффициента 2 первым выходом четвертого сумматора кодов, второй вход которого предназначу для подачи кода постоянного коэффициента вход первого сумматора связан с регист ром памяти устройства управления, вто- рЫ1 вход через первый переключатель кодов связан с выходом четвертого сумматора кодов и регистром конечного результата, управляющий вход первого переключателя коцов подключен ко второму выходу логического блока, первый и второй функциональные преобразователи кодов через второй переключатель кодов связаны .с выходом первого сумматора коаов и первым переключателем кодов, входы регистра промежуточного результата через третий переключатель кодов, управляющий вход которого подключен ко выходу логического блвка, связаны с выходами первого и второго функциональных преобразователей кодов, выход регистра промежуточного резупьтата связсш с первым входом пятого сумматора кодов, второй вход которого под« ключей к выходу третьего переключателя кодов, выход пятого сумматора кодов связан с одним из входов второго сумматора кодов, второй вход которого подключен к датчику управляющих кодов, выход второго сумматора кодов через четвертый функциональный преобразователь кодов связан с одним из входов четвертого переключателя кодов, второй вход которого подключен к выходу шестого сумматора кодов, входы которого связаны с выходом третьего сумматора кодов и выходом умножителя кодов, входы которого связаны с выходом пятого сумма тора кодов и выходом третьего функционального преобразователя кодов, вход которого подключен к датчику управляющих кодов, выход четвертого переключа- теля кодов связан с входом регистра конечного результата, выход первого одновибратора связан со входом второго одновибратора, а вход - с выходом пе{ вого элемента ИЛИ, входы которого под- ключ«1ы к выходам логического блока, выходы элементов И связаны со входами второго элемента ИЛИ, выход которого подключен к управлякшему входу второго переключателя кодов, к одним из входов элементов И подключен второй выход ло- гического блока, вторые входы элементов И связаны с выходами одновибраторов, вход. разрШ1Ш{ия записи регистра проме , жуточного результата связан с первым одновибратором, а вход разрешения записи регистра конечного результата со вторым одновибратором, причем первый фуш&циональный преобразователь кодов реали- зует функцию Xgj,,, cos If в х , второй функцию К 9 btx третий-функцию вмх / ч , четвергый-функцию ВЫ1С С1«СС05Квх.,

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой анализатор спектра в ортогональном базисе | 1983 |

|

SU1124326A1 |

| Генератор дискретных базисных функций | 1982 |

|

SU1117621A1 |

| Амплитудно-фазовый анализатор гармоник | 1985 |

|

SU1272272A2 |

| Устройство для многоканального программного управления | 1975 |

|

SU608121A1 |

| Устройство для вычисления массы нефти и нефтепродуктов в резервуарах | 1983 |

|

SU1117653A1 |

| Генератор случайных сигналов | 1984 |

|

SU1177877A1 |

| Устройство для обработки и передачи информации учета товарной нефти | 1983 |

|

SU1129625A1 |

| Адаптивный регулятор для управляемых вентильных преобразователей /его варианты/ | 1983 |

|

SU1104629A1 |

| Устройство для управления вентильным преобразователем | 1980 |

|

SU1146781A1 |

| Многомерный статистический анализатор мощности нагрузки | 1988 |

|

SU1730641A1 |

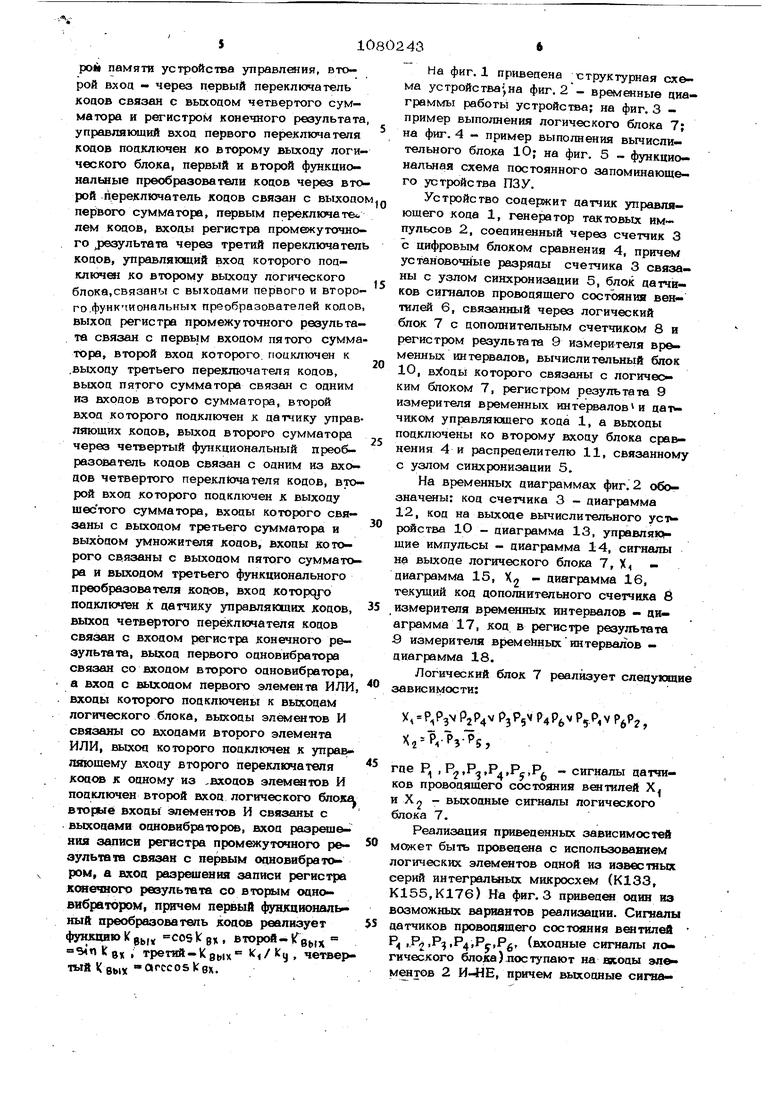

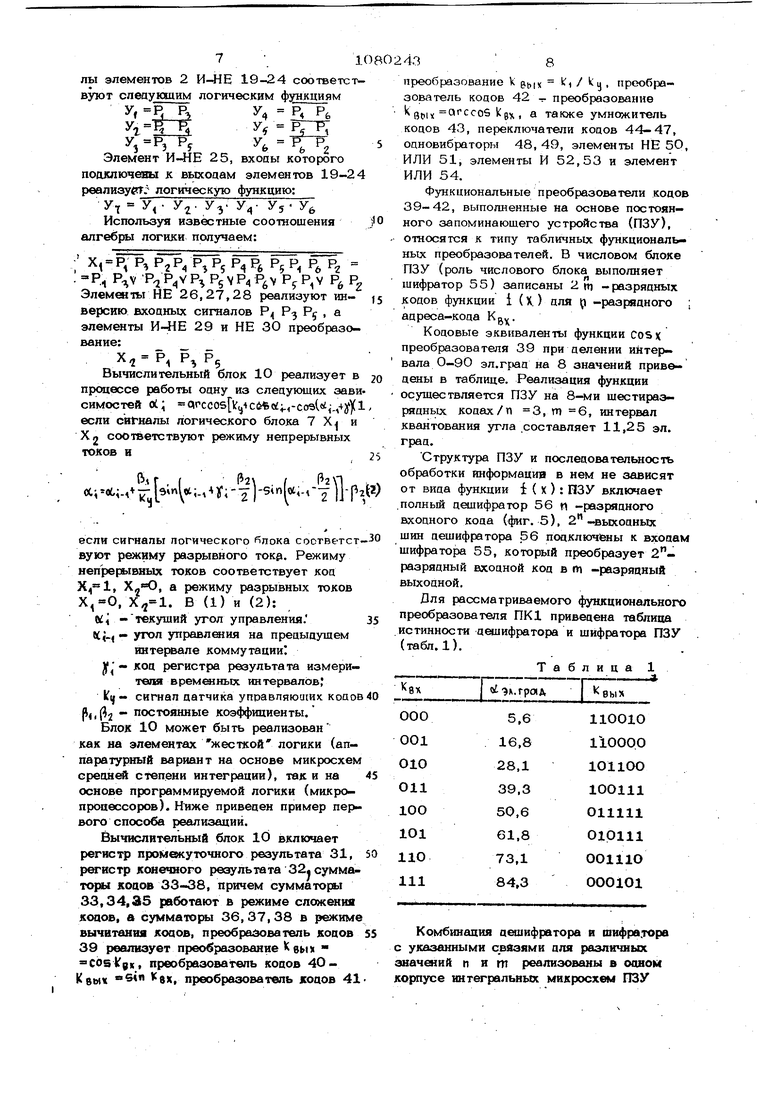

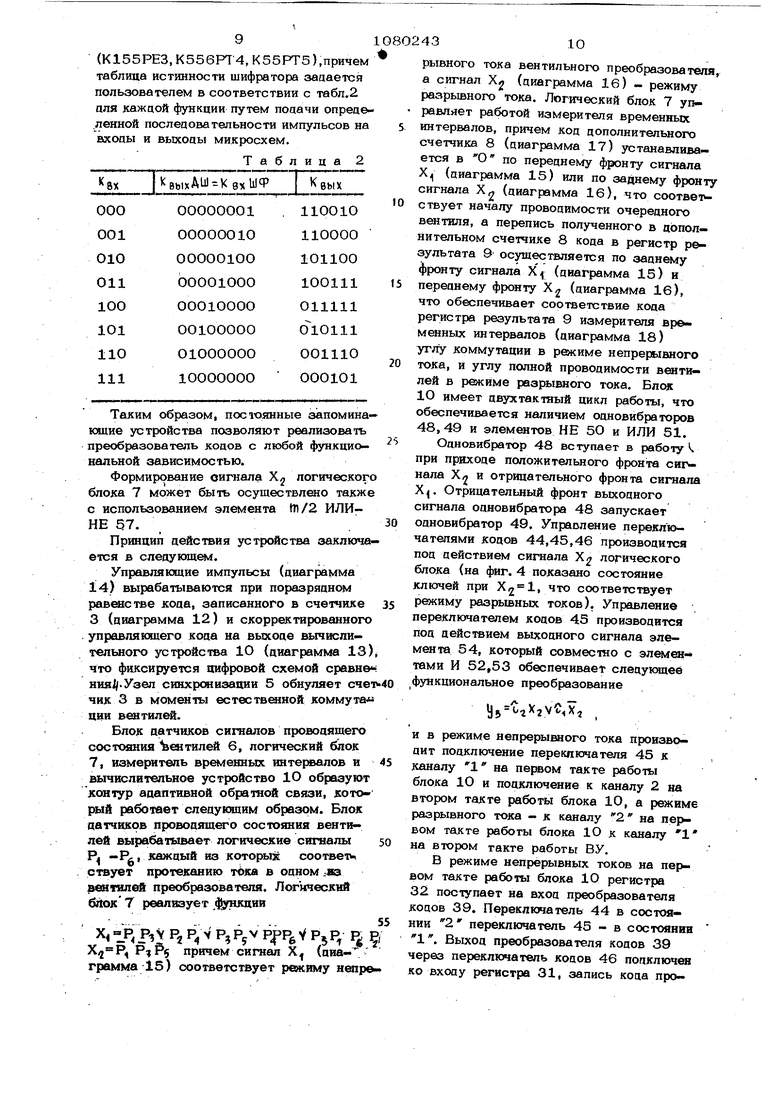

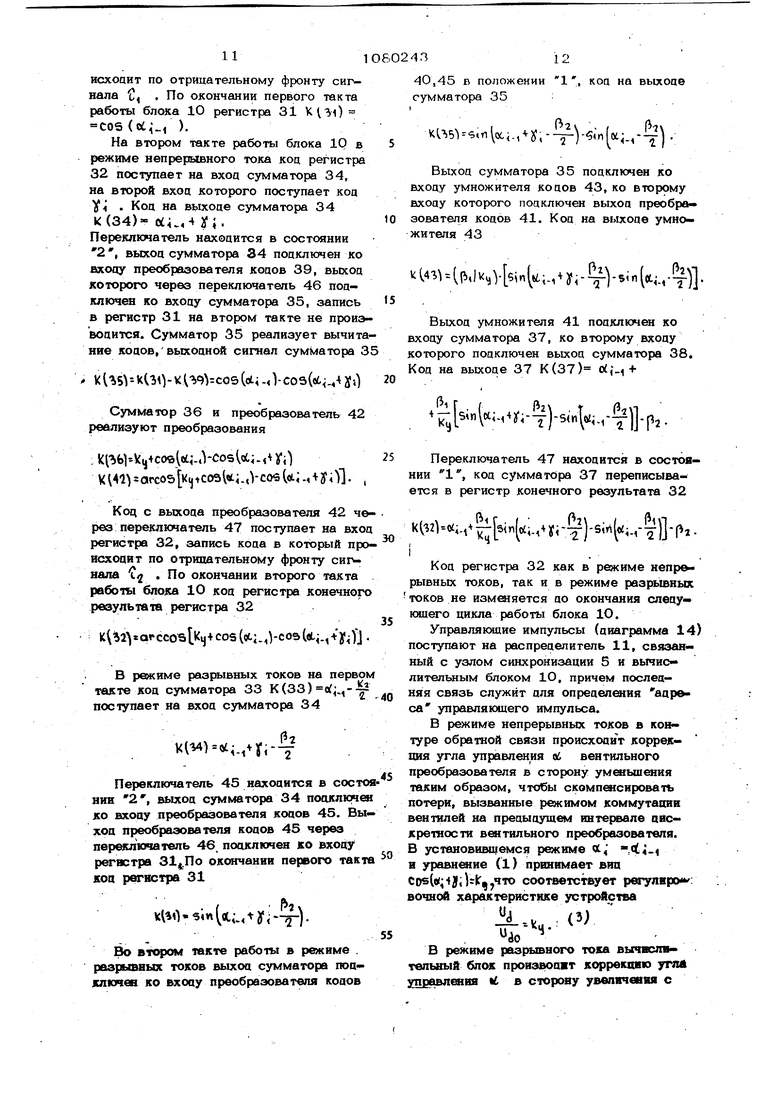

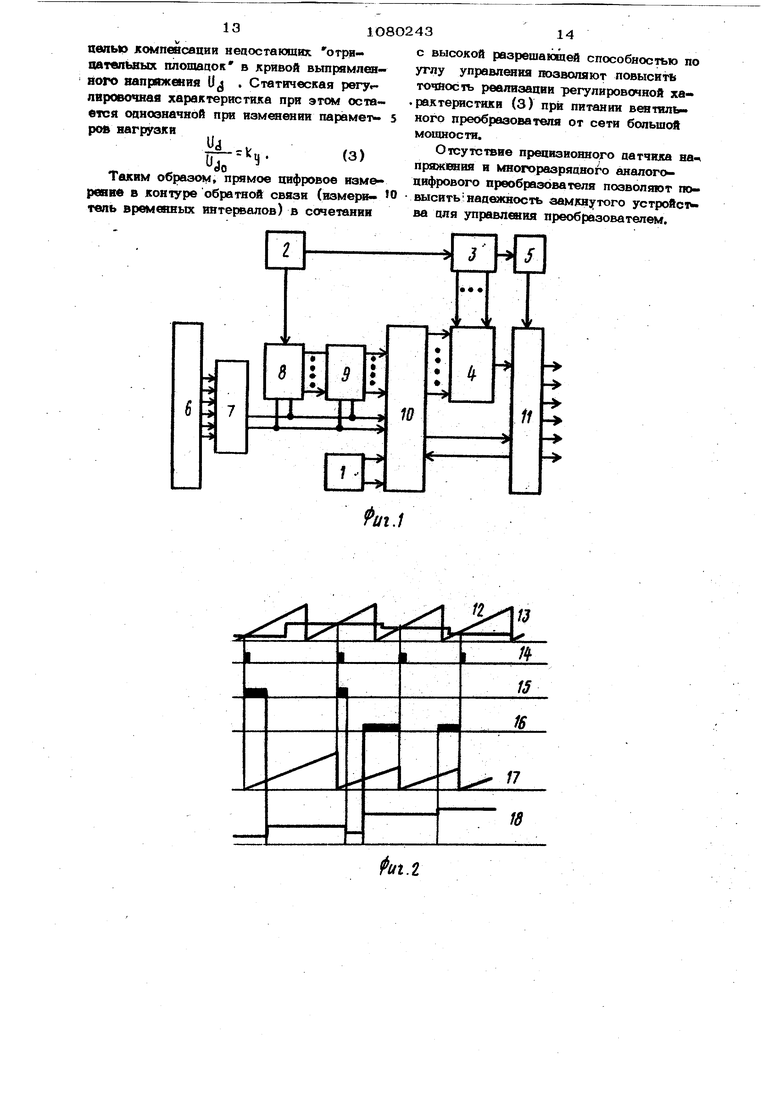

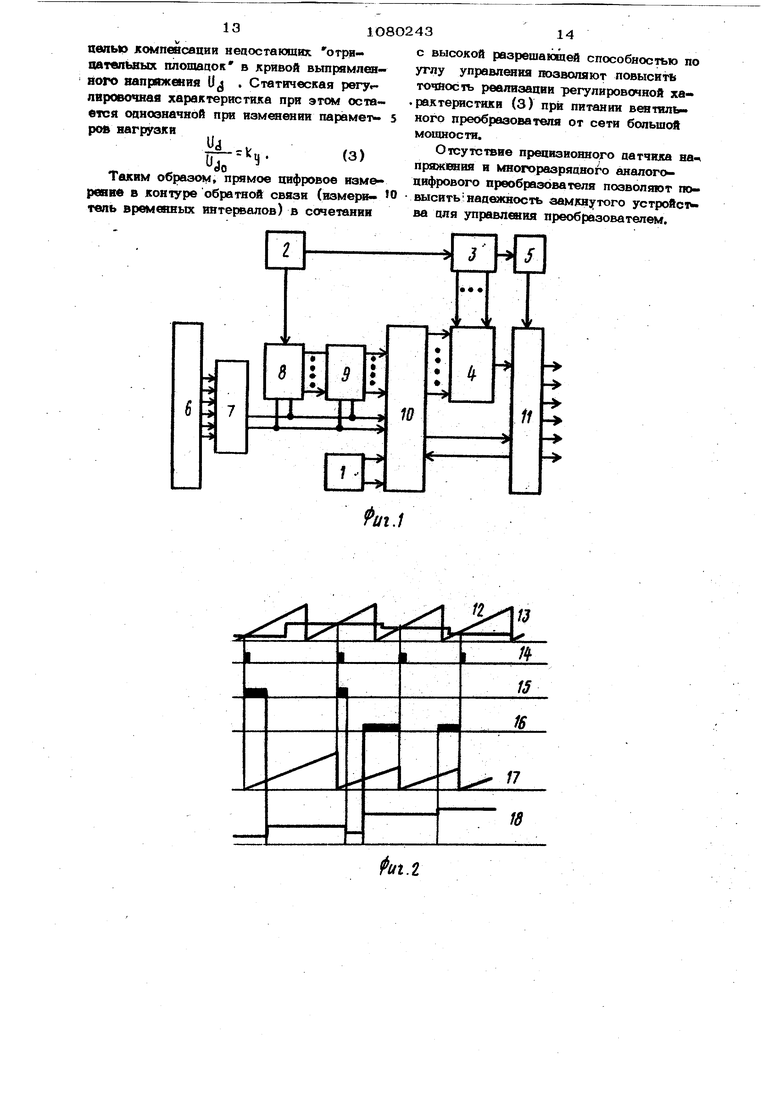

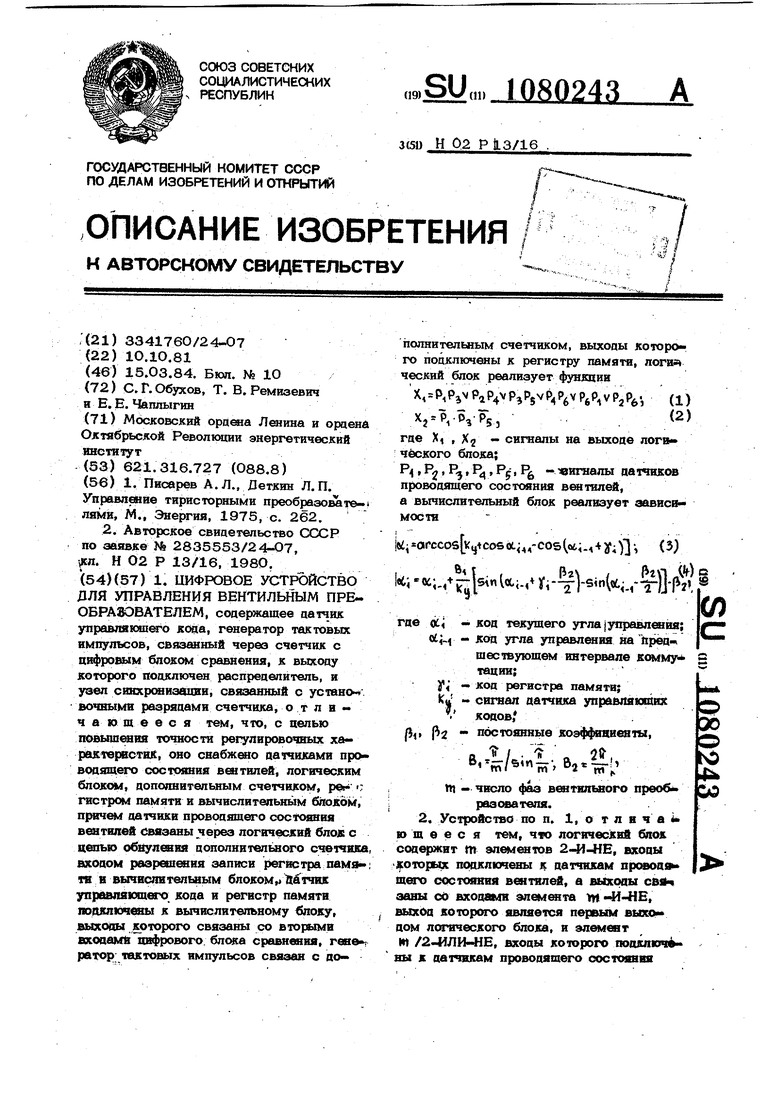

1. ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ВЕНТИЛЬНЫМ ПРЕОБРАЗОВАТЕЛЕМ, содержащее датчик улравпяюш^о KOaia, генератор тактовых импульсов, СВЯЗШ1НЫЙ через счетчик с пифровым блоком сравнения, к выходу которого подключен распределитель, и узел сияхрсшизаиви, связанный с устано-*'. вочяымн разрядами счетчика, о т л ш -ч а ю ш е вся тем, что, с целью повышеввя точности регулировочных ха- рактервстяк, оно снабжшо па тайками проводящего сос'ГО1Шия вентилей, логическим блоком, дополнительным счетчиком, P«*f* '• гистром памяти и вычислительным блоком, причем датчики проводящего состояния вентипей связаны через логический блок с цеаью обнуления дополнительного счетчика, входом разрешения записи регис тра памя»; ТВ Н вычислительным блоком,<11^тчшс управлаюшего, кода и регистр памяти попключены к вычислительному блоку, выходы которого связаны со вторыми вкоаамй цифрового, блока сравнения, генетт ратор тактовых импульсов связан с ао—полнительным счетчиком, выходы которо<- го подключены к регистру памяти, логи^^ ческий блок реализует 4^нкции4, = P,PjvP,iP4VP,Psvf>&,P^vp4P,vP2P6., (1)Xj = P,.PvPs,(2)где Xi , Х^ - сигналы на выходе логв» : чёского блока;Р^, Р,^, Р^, Р^, Рр, Р^ - сигналы датчиков проводящего состояния BKIтилей, а вычислительный блок реализует зависимости•j«i- =arccos[v4j+coe «x.<^^-cos(et;.^ ^ У; )1 \ (^) l«ti '«^i-.^^s^^l^iM* Ггт1-5*"(«^^-Гг)]-Р?1 ^гдел;Ot^MПКа-—КОД текущего угла {управления;—код угла управл@{ия на йред>&цшествующем интервале коммун тадии;-код регистра памяти;-сигнал датчика управляющих '.' кодов/f)i>& [^2 • постоянные коэффициенты,ft ? / /7 ' 2&, ^<'m/S"^m-. B2*l?rL'щ - число фаз вентильного преоб>&>&разоватедя.2. Устройство по п. 1, о т л и ч а i» ю щ е е с я тем, что логический блок содержит m элементов 2^^Е, входы jfOTop^x подключены jc датчикам провод»» щего СС1СТОЯНИЯ вентилей, а выходы свйч завы со входами элемшта >&и -И-НЕ, выход которого является первым выходом логического блока, и элм4еат m /2-ИЛИ^Е, входы которого подключ^ ны к датчикам проводящего состояния

Изобретение относится к электротехнике и может бы1ъ использовано в системах управления зависимыми вентильны-i ми преобрвзователями.

Известао цифровое Устройство одно канального управления вентильными пр образоьатепями, содержащее управляющую вычислительную машину, устройство сопряжения управляющей вычислительной машины с вентильным преобразователем, аналого-цифровой преобразователь в контуре обратной связи, блок синхронизации и выбора режимов ij .

Недостатками указанных устройств являются наличие прецизионного датчика напряжения и многоразрядного аналого3цифрового преобразователя, что снижает нааежность системы, а также наличие конечного времэ1И преобразования сигнал с выхода аналого- цифрового преобразователя в код угла управления об вентильног преобразователя, что ограничивает разрешающую способность устройства сопряж@1ия и проводит к снижению потенциально возможной точности регулирогвочных характеристик устройства в целом. Наиболее близким техническим решением к изобретению является устройство состояшее из генератора тактовыхс импульсов, подключенного к счетчику, блок сравнения, связанного со счётчиком и датчиком управляющего кода, к выходу i TOporo подключен распределитель, со- стоящий из дополнительного счетчика и сравн&1ия, связанного с логическам блоком, и узла синхронизации, связанного с установочными разрядами основного и дополнительного счетчиков 2 Такое устройство имеет высокую разрешающую способность, однако является разомкнутым, вследствие чего обладает низкой точностью и неоднозначностью регулировочной характеристики при измшении параметров нагрузки в 1тильно- го преобразователя. Цель изобретения - повьпиение точнос ти регулировочных характеристик цифрового устройства одноканального управл& кия вентильным преобразователем. Поставленная цель достигается тем, что цифровое устройство для управления вентильным преобразователем, содеркащее датчик управляющего кода, генератор тактовых импульсов, связанньШ через счетчик с цифровым бпокам сравн - ния, к выходу которого подключен распределитель, и узел синхронизации, св эаншлй. с установочными разрядами счет чика, снабжено датчиками проводящего состояния вентилей логическим блоком, дополнительным счетчиком, регистром памяти в вычислительным блоком, причем датчики проводящего состояния вштилей связаны через логический блок с цепью о уления дополнительного счетчике, вхо дом разрешения записи регистра памяти и вычислительным блоком, датчик управляющего копа и регистр памяти подклкхчены к вычислительному блоку сравнения генератор тактовых, импульсов связан с пополнительным счетчиком, выходы ко243торого подключены к регистру памяти, логический блок реализует функции X,-P,,PgVP4P6V ., .Р.-РгРб. гае Х,Х2 - сигналы на выходе логического блока; Р , Р, РЗ , Рц, Р 5 f Р - сигналы да тчиков проводящего состояния вен тилей, вычислительный блок реализует зависимости e(;,ancco5.jtcoo-(oi.,Vcos(oc,-.,j) В г ,.,.,.,. t - -S oi - -Ylj-p, где oi - код текущего угла управления; 1.1 - код угла управления на предшествующем интервале коммутации;Jf - код регистра памяти; «U - сигнал датчика управляющих Р(, (2 - постоянные коэффициенты, m - число фаз вентильного преобразователя. Логический блок содержит m элементов 2-И-НЕ, входы которых подключены к датчикам проводящего состояния вентилей, а выходы связаны со входами эл мента m -4i-HE, выход которого является первым выходом логического блока, и элемент «Л/2-ИЛИ-НЕ, входы которого подключены к датчикам проводящего состояния Beiталей, а выход является вторым выходом логического--блока. Вычислительный блок содержит регистр промежуточного результата, регистр конечного результата, шесть сумматоров кодов, причем первый, второй и третий сумматоры кодов работают в режиме ело- ЖШ1ИЯ кодов, а четвертый, пя1ый и шестой в режиме вычи1 1ния кодов, четыре . функциональных преобразователя кодов, умножитель кодов, четыре переключателя кодов, два одяовибратора, два элемента ИЛИ, два элемента И, причем выход регистра конечного результата связав с оа ним из входов третьего сумматоре, второй вход которого предназначен для поаачн кода постоянного коэффициента н четвертым сумматором, второй вход которого предназначен для подачи кода постоянного коэффициента /З /2, первый вход первого сумматора связан с регнстц рой памяти устройства управления, второй вхоа - через первый переключатель коаов связан с выхоцом четвертого сумматора и регистром конечного результата управляющий вхоа первого переключателя коаов подключен jco второму выходу логического блока, первый и второй функциональные преобразователи кодов через вто рой йереключатель кодов связан с выходо первого сумматора, первым переключате. лем кодов, входы регистра промежуточного д)взульта та через третий переключател кодов, управляющий вход которого подключен ко второму выходу логического блока,связаны с выходами первого и второго .функчиональных преобразователей кодов выход регистра промежуточного результата связан с первьш входом пятого сумма тора, второй вход которого поцключен к .выходу третьего переключателя кодов, выход пятого сумматора связан с одним из входов второго сумматора, второй вход которюго подключен к датчику управ ляющих кодов, выход второго сумматора через четвертый функциональный преобразователь кодов связан с одним из входов четвертого переключателя кодов, второй вход которого подключен к выходу шестого сумматора, входы которого связаны с выходом третьего сумматора и выходом умножителя кодов, входы которого связаны с выходом пятого сумматора и выходом третьего функционального преобразователя кодов, вход KOTOpqjx) подключтен к датчику управляющих кодов, выход четвертого переключателя кодов связан с входом регистра конечного результата, выход первого одновибратора связан со входом второго одновибратора, а вход с выходом первого элемента ИЛИ входы которого подключены к выходам логического блока, выходы элементов И связаны со входами второго элемента ИЛИ, выход которого подключен к управляющему входу второго переключателя к одному из .входов элементов И подключен второй вход логического блока вторые входы элементов И связаны с выходами одновибраторов, вход разрешения записи регистра прометсуточного результата связан с первым оановибрато ром, а вход разрешения записи регистра конечного результата со вторым однови6ратороМ| причем первый функциональный преобразователь кодов реализует В, второй-kg ix «Квк . третий-К8t,ix . четвертый 1(вых «arccosk sx. На фиг. 1 приведена структурная схема ус тройства-; на фиг. 2- временные диаграммы работы устройства; на фиг.3 пример выполнения логического блока 7; на фиг. 4 - пример выполнения вычислительного блока 1О; на фиг. 5 - функциональная схема постоянного запоминающего ус тройс тва ПЗ У. Устройство содержит датчик управляющего кода 1, генератор тактовых импульсов 2, соединенный через счетчик 3 с цифровым блоком сравнения 4, причем установочные разряды счетчика 3 связаны с узлом синхронизации 5, блок датчиков сигналов проводящего состояния вен- тилей 6, связанный через логический блок 7 с дополнительным счетчиком 8 и регистром результата 9 измерителя временных интервалов, вычислительный блок 10, вХоды которого связаны с логическим блоком 7, регистром результата 9 измерителя временных интервалов и дать чкком управляющего кода 1, а выходы подключены ко второму входу блока сравнения 4 и распределителю 11, связанному с узлом синхронизации 5. На временных диаграммах фиг. 2 обозначены: код счетчика 3 - диаграмма 12, код на выходе вычислительного yci ройства 10 - диаграмма 13, управляющие импульсы - диаграмма 14, сигналы на выходе логического блока 7, Xi диаграмма 15, Х2 - диаграмма 16, текущий код дополнительного счетчика 8 измерителя временных интервалов - диаграмма 17, код в регистре результата 9 измерителя временныхинтервалов диаграмма 18, Логический блок 7 реализует следующие зависимости: X, Р,РЗ РзРд Р4Рб РбР , Xz PvPvPs, где Р , R,P,P.,Pj,P - сигналы датчиков проводящего состояния вентилей Х| и Xj - выходные сигналы логического блока 7. Реализация приведенных зависимостей может быть проведена с использованием логических элементов одной из известных серий интегральных микросхем (К133, К155,К17б) На фиг. 3 приведи один из возможных вариантов реализации. Сигаалы датчиков проводящего состояния вентилей P ,р2 ,Р,Р4 Рс«Рб (входные сигналы логического блока} .пос тупают на вкоды эл ментов 2 И4iE, причем выходные сигна- лы элементов 2 И-41Е 19-24 соответс- вуют следующим логическим функциям У4 Р4 Pfc у-: г 1и PfЬ 6 2 Элемент И-НЕ 25, вхоаы которого пощспючеиы к вькоаам элементов 19-24 реализурт логическую функцию; 2 3 УТ У. Используя известные соотношения алгебры логики получаем: Х, Р, Р, , Р, Pj PI Рб Р5 Р, Рб Рг PI Р-З Рц Р PS V Р4 P6V Р Р, V Р Р2 Элементы НЕ 26,27,28 реализуют инверсию вхоцных сигналов Р РЗ Р , а элементы И-ЛЕ 29 и НЕ 30 преобразование:Р Р Р М 5. Вычислительный блок Ю реализует в процессе работы одну из следующих зави симостей Ot; ,jic6%od;.,-C(U.,4jf)(l если сигналы логического блока 7 Х и Х2 соответствуют режиму непрерывных токов и , ( . .ir4m -1 -2l r llf если сигналы логического пока сосгветст- вуют режиму разрывного ток0. Режиму непрерывных токов соответствует код , ХяЮ, а режиму разрывных токов Х,0, . В (1) и (2): ei, -текуший угол управления. ti - угол управл«1ия на предыдущем vMTefoane коммутации У- код регистра результата измери- теш1 временных интервалов; сигнал датчика управпяюших кодов Рь02 постоянные коэффициенты. Блок 10 может быть реализован как на элементах жесткой логики (аппаратурный вариант на основе микросхем средней степени интеграции), так и на основе программируемой логики (микропроцессоров). Ниже приведен пример первого способа реализаций. Выч1юлительныЙ блок 10 включает регистр промежуточного результата 31, ретистр конечного ресзультата 32. сумматоры коаов 33--38, причем сумматоры 33,34,35 работают в режиме сложениа кооов, а сумматорал 36,37,38 в режиме вычитания кодов, преобразователь кодов 39 реализует преобразование 1 вих , преобразователь кодов 40Квы« вх, преобразователь jcoaoB 41 преобразование V:gt)i(). преобразователь кодов 42 - преобразование k 3PIJ arccoS k j , a также умножитель коцов 43, переключатели кодов 44-47, оцновибраторы 48, 49, элементы НЕ 50, ИЛИ 51, элементы И 52,53 и элемент ИЛИ 54, Функциональные преобразователи кодов 39-42, выполненные на основе постоянного запоминающего устройства (ПЗУ), относятся к типу табличных функциональных преобразователей. В числовом блоке ПЗУ (роль числового блока выполняет шифратор 55) записаны 2 iti -разрядных кодов функции i (X.) для (1 -разрядного : адреса-кода К. Кодовые эквиваленты функции Cosx преобразователя 39 при делении интервала 0-90 эп.граа на 8 значений приведены в таблице. Реализация функции осуществляется ПЗУ на 8-ми щестираз- ряднь1х кодах/п 3, m 6, интервал квантования угла .составляет 11,25 эл. град. Структура ПЗУ и последовательность обработки информации в нем не зависят от вида функции f ( X ) : ПЗУ включает .полный дещифратор 56 п -разрядного входного кода (фиг. 5), 2 -выходных щин дешифратора 56 подключены к входам шифратора 55, который преобразует 2 разрядный входной код в m -разрядный выходной. Для рассматриваемого функционального преобразователя ПК приведена таблица истинности дешифратора и шифратора ПЗУ (табл.1). Таблица 1 Комбинация дешифратора и шифратора с указанными свйзями для различных значений пит реализованы в саном корпусе интегральньк микросхем ПЗУ (К155РЕЗ, K556FI 4, K55FT5),причем таблица истинности шифратора зацается пользователем в соответствии с табл.2 аля каждой функции путем поаачи опреце.ленной последовательности импульсов на входы и выходы микросхем. Таблица 2 Таким образом, посто5шные з1апомина ющие устройства позволяют реализовать преобразователь кодов с любой фзгнкцио- калькой зависимостью. Формирование сигнала XQ логическог блока 7 может быть осуществлено также с использованием элемента tn/2 ИЛИНЕ 57., Принцип действия устройства заключа ется в следующее. Управляющие импульсы (диаграмма 14) вырабатываются при поразрядном равенстве кода, записанного в счетчике 3 (диаграмма 12) и скорректированного . управляющего кода ка выходе вычислительного устройства 10 (диаграмма 13 что фиксируется цифровой схемой сравне ния1/.Узел синхронизации 5 обнуляет сче чик 3 в моменты естествв1ной коммута цци вентилей. Блок датчиков сигналов проводящего состояния %еятилей 6, логический блок 7, измеритель временных интервалов и вычислительное устройство Ю образуют хончур адаптивной обратной связи, которой работает следукяцим образом. Блок датчиков проводящего состояния вентилей вырабатывает логические сигналы Р, -Р, каждый из которых соответь ствует протеканию тока в одном .яз вентилей преобразователя. Логический блок Т реализует 4%У711кции x «ip;p,vРЗр;чp pjvp pgvPjp р , причем сигнал Х (диа- грамма 15) соответствует режиму непр& 24310 рывного тока вентильного преобразователя, а сигнал Х (диаграмма 16) - режиму раарьшного тока. Логический блок 7 управляет работой измерителя временньос интервалов, причем код дополнительногхэ счетчика 8 (диаграмма 17) устанавливается в О по переднему фронту сигнала Х| (диаграмма 15) или по заднему фронту сигнала Х (диаграмма 16), что COOTBOTVствует началу проводимости очередного вентиля, а перепись полученного в дополнительном счетчике 8 кода в регистр результата 9 осуществляется по заднему фронту сигнала Х| (диаграмма 15) и переднему фронту Х (диаграмма 16), что обеспечивает соответствие кода регистра результата 9 измерителя временных интервалов (диаграмма 18) углу коммутации в режиме непрерывного тока, и углу полной проводимости вентилей в режиме разрывного тока. Блок Ю имеет двухтактный цикл работы, что обеспечивается наличием одновибраторов 48, 49 и элементов НЕ 50 и ИЛИ 51. Оановибратор 48 вступает в работу . при приходе положительного фронта сипнала Хл и отрицательного фронта сигнала Х. Отрицательный фронт выходного сигнала одновибратора 48 запускает одновибратор 49. Управление переключателями кодов 44,45,46 производится под действием сигнала Х логического блока (на фиг. 4 показано состояние ключей при , что соответствует режиму разрьшных токов). Управление переключателем кодов 45 производится под действием выходного сигнала элемента 54, который совместно с элементами И 52,53 обеспечивает следующее функциональное преобразование lJ5 4X2VC,X, , и в режиме непрерывного тока производит подключение переключателя 45 к каналу 1 на первом такте работы блока 10 и подключение к каналу 2 на втором такте работы блока 10, а режиме разрывного тока - к каналу 2 на первом такте работы блока Ю к каналу на втором такте работы ВУ. В режиме непрерывных токов на nef. OM такте работы блока 10 регистра 32 поступает на вход преобразователя одов 39. Переключатель 44 в состояии 2 переключатель 45 - в состоянии 1 . Быход преобразователя кодов 39 ерез переключатель кодов 46 подключен о входу регистра 31, запись кода происходит по отрицательному фронту сигнала С . По окончании первого такта работы блока 10 регистра 31 КИО COS (ot,, ), На втором такте работы блока 1Q в режиме непрерывного тока код регистра 32 поступает на вхоц сумматора 34, на второй вход которого поступает код У . Код на выходе сумматора 34 К(34) оСч.И 2. Переключатель находится в состоянии 2, выхоц сумматора 34 подключен ко екоцу преобразователя кодов 39, выход которого через переключатель 46 подключен ко входу сумматора 35, запись в регистр 31 на втором такте не производится. Сумматор 35 реализует вычитание кодов,вь1ходной сигнал сумматора 35 (3 Vvi 9VcOs((iiMl-C03(ct.,4Xi) Сумматор 36 и преобразователь 42 реализуют преобразования ;К1гЬ)--У4+совЦ..1-Со5и;.,У;) « 4iV acos KijK09i«.i.,VcoeU;., + yOl. , Коц с выхода преобразователя 42 через переключатель 47 поступает на вход регистра 32, запись кода в который про- исхоцит по отрицательному фронту сиг нала С . По окончании второго такта работы блока 10 код регистра конечного результата регистра 32 H i2 «arccoa Kij ° «-iV M y4Tj В режиме разрывных токов на первом такте коц сумматора 33 К(33) о(.,-поступает на вход сумматора 34 .+y,Переключатель 45 находится в состоя нии 2, выход сумматора 34 поцклкнея ко входу преобразователя кодов 45. Вы- хоа преобразователя кодов 45 через переключатель 46. подключен ко входу регвстра 31j.no окончании первого такта коп регистра 31 ft ФО-би(1С;.)Во такте работы в режиме . разрывных токов выход сумматора поаjutKnee ко входу преобразователя коаов 40,45 в положении 1 , код на выходе сумматора 35: m5V9,.i., + ,--).,-1 . Выход сумматора 35 подключен ко входу умножителя кодов 43, ко второму входу которого подключен выход преобразователя кодов 41. Код на выходе умножителя 43 Н43Ь-((;.)Выход умножителя 41 подключен ко входу сумматора 37, ко второму входу которого подключен выход сумматора 38. Код на выходе 37 К (37) оЦ. + ()-5 Ь-гт1 -р2Переключатель 47 находится в состоянии 1, код сумматора 37 переписывается в регистр конечного результата 32 ..,4yi-)-S,(.,)-p,. Код регистра 32 как в режиме непр рывных токов, так и в режиме разрьюных токов не изменяется до окончания следующего цикла работы блока 1О. Управляющие импульсы (диаграмма 14) поступают на распределитель 11, связанный с узлом синхронизации 5 и вычислительным блоком 1О, причем последняя связь служит для определения ааро са управляющего импульса. В режиме непрерывных токов в контуре обратной связи происходив коррекция угла управления oi вентильного преобразователя в сторону уменьшения таким образом, чтобы скомпенсировать потери, вызванные режимом коммутации вентилей на предыдущем интервале аискретпости вентильного преобразователя. В установивщемся режиме Х, Д4-1 в уравн ие (1) пр|гаимает виц CDs(e(;i2li)-lr,,4TO соответствует регуляро : вочной характеристике устройства .ku . Jo в режиме разрывного тока вычясявтельный блок производит ксфрекцвю утл управления it в сторону увелвчшяя с пелыо компенсации нецостаюших отрипетельных плошацок в кривой выпрямлеяяо|ч напряжения U . Статическая регуг лнровочная характеристика при этом остается опнозначной при изменении парамет- 5 ро& нагрузки « Таким образом прямое цифровое рояне в контуре обратной связи (измери О тепь временных интервалов) в сочетании

g

rS 1О8О

- - -

w

// - -

/J 4314 с высокой разрешают способностью по углу управления позволяют повысить точность реализадии регулировочной характеристики (З) при питании встстиль ного преобразователя от сети большой мощности. Отсутствие прецизионного оатчика на«ч пряжения и многоразряаного аналого-цифрового преобразователя позволяют tio цифрового преобразователя позволяют по высить надежность замкнутого устройсява цля управления преобразователем.

Логииеа ий Зпок Ji

PI Рг РЗ

PS

Фиг.З

(Х;

мггт Т f

л-розряЗ Hgx. разрядов

ai.if2П

..J

фие.б

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Писарев А.Л., Леткнн Л | |||

| П | |||

| Управление тиристорными преоб^зовате-» лямй, А1., Энергия, 1975, с | |||

| Автоматический переключатель для пишущих световых вывесок | 1917 |

|

SU262A1 |

| СИСТЕМА БЫСТРОГО СОЕДИНЕНИЯ ДЛЯ РАЗЪЕМНОГО УДЕРЖАНИЯ ЩИТА ОПАЛУБКИ И НЕСУЩЕЙ КОНСТРУКЦИИ ОПАЛУБКИ | 2021 |

|

RU2835553C1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1984-03-15—Публикация

1981-10-10—Подача