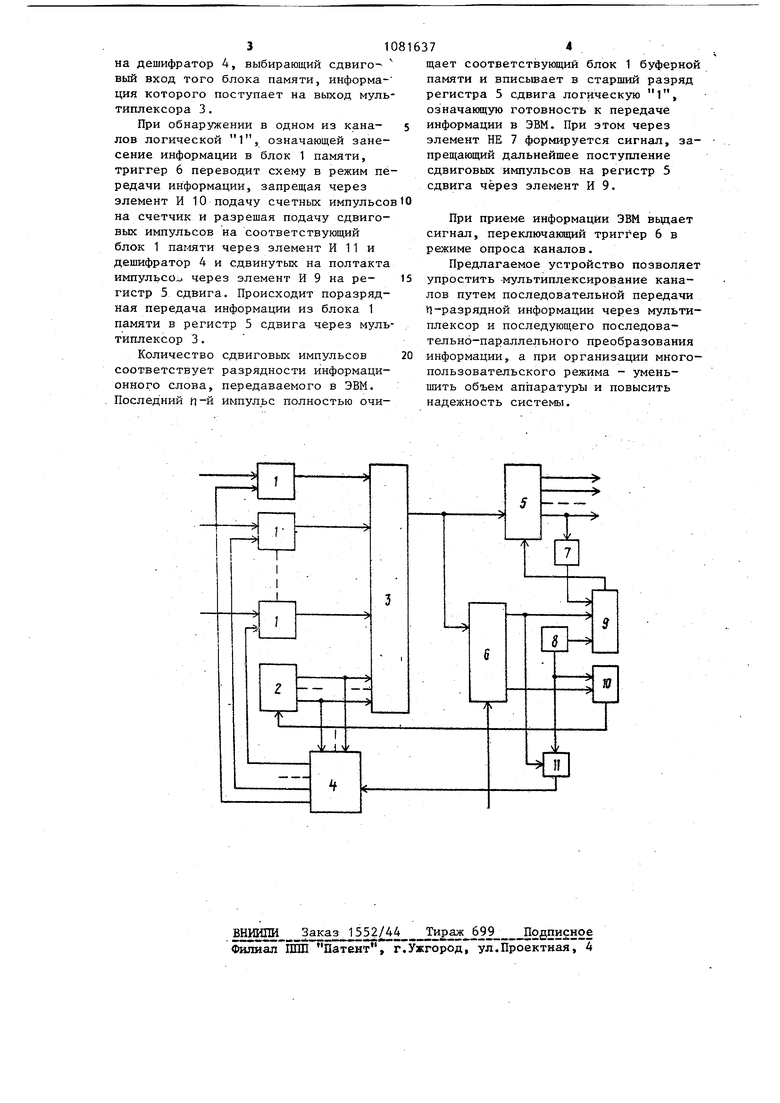

Изобретение относится к автоматике и вычислительной технике и может быть использовано для ввода информации в вычислительных системах коллек тивного пользования. Известно многоканальное устройство для ввода информации, содержащее в каждом канале первый и второй триггер и элемент И lj . Недостатком устройства является ограничение количества каналов разрядностью информационного слова, вводимого в ЭВМ. Наиболее близким к изобретению по технической сущности является устройство для ввода информации,-содержащее блоки буферной памяти в каж дом канале, мультиплексор, счетчик, причем выходы блоков буферной памяти подключены к одним входам мультиплексора, а выходы счетчика - к другим входам мультиплексора 2 , Недостатком известного устройства является низкая надежность из-за сложности узла мультиплексора, осуществляющего переключение коли чества многоразрядных цепей. Целью изобретения является повышение надежности устройства. Поставленная цель достигается тем, что в устройство для ввода информации, содержащее мультиплексор, блоки памяти, счетчик, выходы которого соединены с входами первой груп пы мультиплексора, входы второй груп пы которого соединены с выходами бло ков памяти, входы группы которых являются входами группы устройства, введены регистр сдвига, триггер, „ элемент НЕ, генератор тактовых импульсов, первый, второй и третий элементы И, дешифратор, входы группы которого соединены с выходами счетчика, вход которого соединен с выходом второго элемента И, первый вход второго и третьего элементов И соединены с первым выходом генератора импульсов, выход третьего эле мента И соединен с входом дешифратоfta, выходы которого соединены с входами блоков пайяти, выход мультиплек сора соединен с первыми входами регистра сдвига и триггера, второй вхо которого является входом устройства, первый выходтриггера соединен с вто рыми входами первого и третьего элементов И, третий вход первого элемен та И соединен с вторым выходом гене-i ратора импульсов, второй выход триггера соединен с вторым входом второго элемента И, выходы регистра сдвига являются выходами устройства, выход старшего разряда регистра сдвига через элемент НЕ соединен с первым входом первого элемента И, выход которого соединен с вторым входом регистра сдвига. На чертеже приведена блок-схема устройства. Устройство содержит блоки 1 памяти, счетчик 2, мультиплексор 3, дешифратор 4, регистр 5 сдвига, триггер 6, элемент 7, генератор 8 тактовьк импульсов, первый элемент И 9, второй элемент И 10 и третий элемент И 11. Блоки 1 памяти предназначены для хранения информации с момента ее занесения до момента передачи в ЭВМ, счетчик 2 - для циклического опроса каналов, мультиплексор 3 - для передачи информации с блоков 1 буферной памяти на вход регистра 5 сдвига, дешифратор 4 - для выдачи сдвиговых импульсов на тот блок 1 буферной памяти, информация которого передается через мультиплексор 3. Регистр сдвига 5 предназначен для последовательно-параллельного преобразования информации, триггер 6 для переключения схемы из режима опроса каналов в режим передачи информации, элемент НЕ 7 - для запрета сдвиговых импульсов в момент завершения последовательно-параллельного преобразования информации. Генератор тактовых импульсов 8 предназначен для формирования двух серий импульсов, сдвинутых одна относительно другой на полтакта. Пер- вьй элемент И 9 предназначен для формирования импульсов сдвига информации через сдвиговьй регистр 5, второй элемент И 10 - для формирования счетных импульсов в режиме опроса каналов, третий элемент И 11 - для формирования импульсов последовательного вывода информации из буферной памяти. Устройство работает следующим образом. В режиме опроса каналов счетчик 2 поочередно подключает на выход мультиплексора 3 выходы блоков 1 памяти. ОдноврЁменно счетчик воздействует

на дешифратор А, выбирающий сдвиго вый вход того блока памяти, информация которого поступает на выход мультиплексора 3,

При обнаружении в одном из каналов логической 1, означающей занесение информации в блок 1 памяти, триггер 6 переводит схему в режим передачи информации, запрещая через элемент И 10 подачу счетных импульсо на счетчик и разрешая подачу сдвиговых импульсов на соответствующий блок 1 памяти через элемент И 11 и дешифратор 4 и сдвинутых на полтакта импульсо-j через элемент И 9 на регистр 5 сдвига. Происходит поразрядная передача информации из блока 1 памяти в регистр 5 сдвига через мультиплексор 3.

Количество сдвиговых импульсов соответствует разрядности информационного слова, передаваемого в ЭВМ. Послед;ний (1-й импульс полностью очищает соответствующий блок 1 буферной памяти и вписьшает в старший разряд регистра 5 сдвига логическую 1, означающую готовность к передаче информации в ЭВМ. При этом через элемент НЕ 7 формируется сигнал, запрещающий дальнейшее поступление сдвиговых импульсов на регистр 5 сдвига через элемент И 9.

При приеме информации ЭВМ вьщает сигнал, переключающий триггер 6 в режиме опроса каналов.

Предлагаемое устройство позволяет упростить .мультиплексирование каналов путем последовательной передачи (1-разрядной информации через мультиплексор и последующего последовательно-параллельного преобразования информации, а при организации многопользовательского режима - уменьшить объем аппаратуры и повысить надежность системы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с внешними устройствами | 1987 |

|

SU1478222A1 |

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

| Устройство для ввода измерительной информации | 1986 |

|

SU1354179A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162247C2 |

| Устройство для ввода информации | 1987 |

|

SU1425636A1 |

| Устройство для вывода информации | 1983 |

|

SU1094040A1 |

| Адаптивное устройство для сопряжения ЭВМ с каналами связи | 1987 |

|

SU1532938A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162248C2 |

| Многоканальное устройство для ввода информации | 1988 |

|

SU1536369A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ, содержащее мультиплексор, блоки памяти, счетчик, выходы которого соединены с входами первой группы мультиплексора, входы второй группы которого соединены с выходами блоков , входы группы которых являются входами группы устройства, о т личающе е ся тем, что, с целью повьшения надежности устройства, в него введены регистр сдвига, триггер, элемент НЕ, генератор тактовых импульсов, первый, второй и третий элементы И, дешифратор, входы группы которого соединены с выходами счетчика, вход которого соединен с вькодом второго элемента И, первьй вход второго и третьего элементов И соединены с первым выходом генератора импульсов, выход третьего элемента И соединен с входом дешифратора j выходы которого соединены с входами блоков памяти, выход мультиплексора соединен с первыми входами регистра сдвига и триггера, второй вход которого является входом устройства, первый выход триггера соединен с вторыми входами первого I и третьего элементов И, третий вход первого элемента И соединен с втосл рым выходом генератора импульсов, второй выход триггера соединен с вторым .входом второго элемента И, выходы регистра свдига являются выходами устройства, выход старшего разряда регистра сдвига через эле:мент НЕ соединен с первым входом эо первого элемента И, выход которого соединен с вторым входом регистра а сдвига. 00 |

Авторы

Даты

1984-03-23—Публикация

1982-12-21—Подача