Изобретение относится к автоматике и вычислительной технике и мо- жет быть использовано в различных системах диагностики, прогнозирования и контроля состояния энергетического оборудования.

Цель изобретения - повышение быст родействия устройства и расширение области применения за счет установления частоты дискретизации о внешних источников.

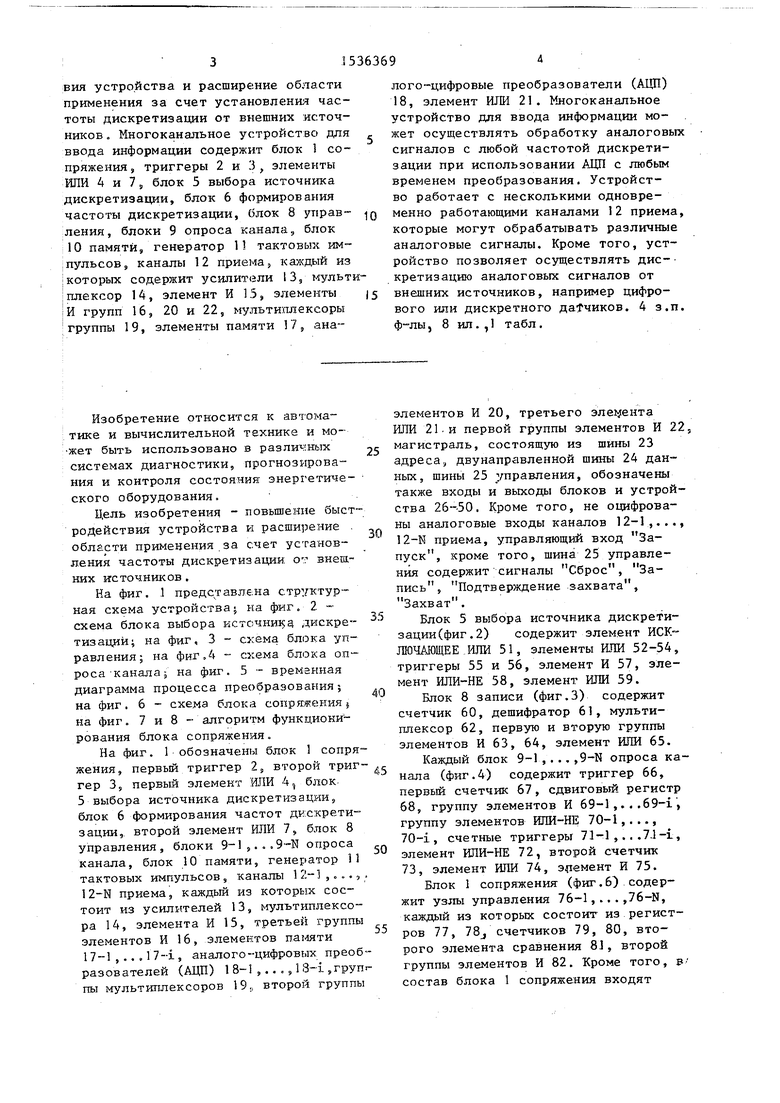

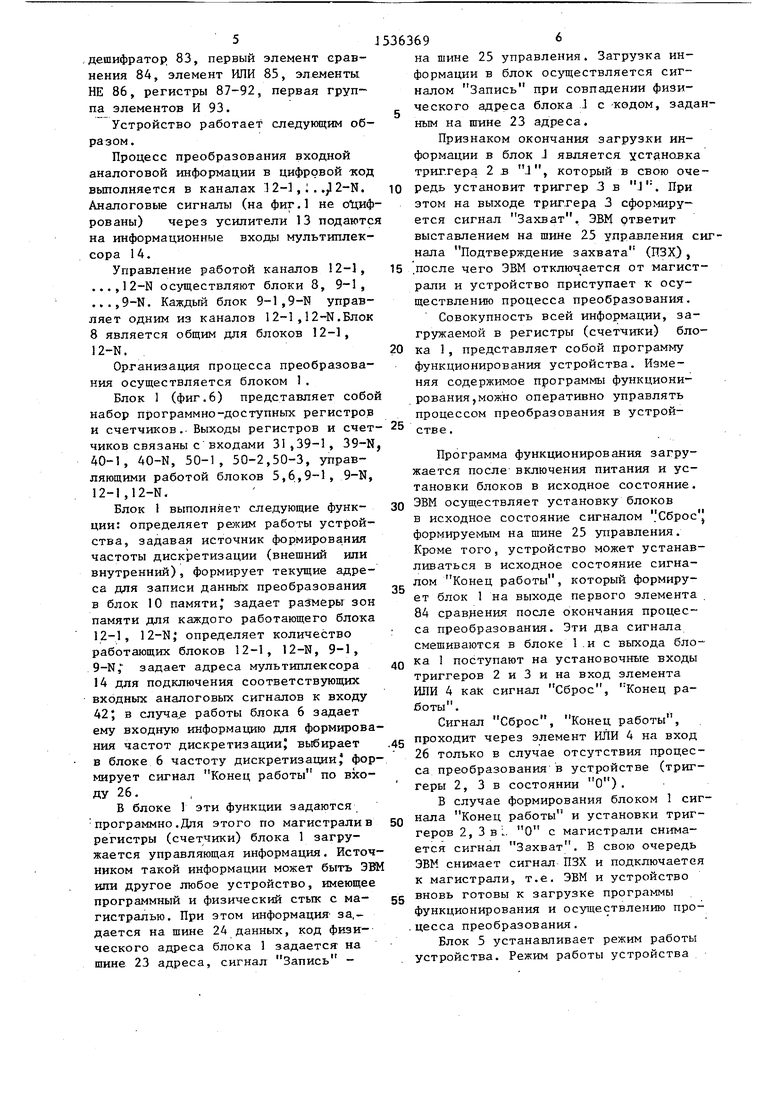

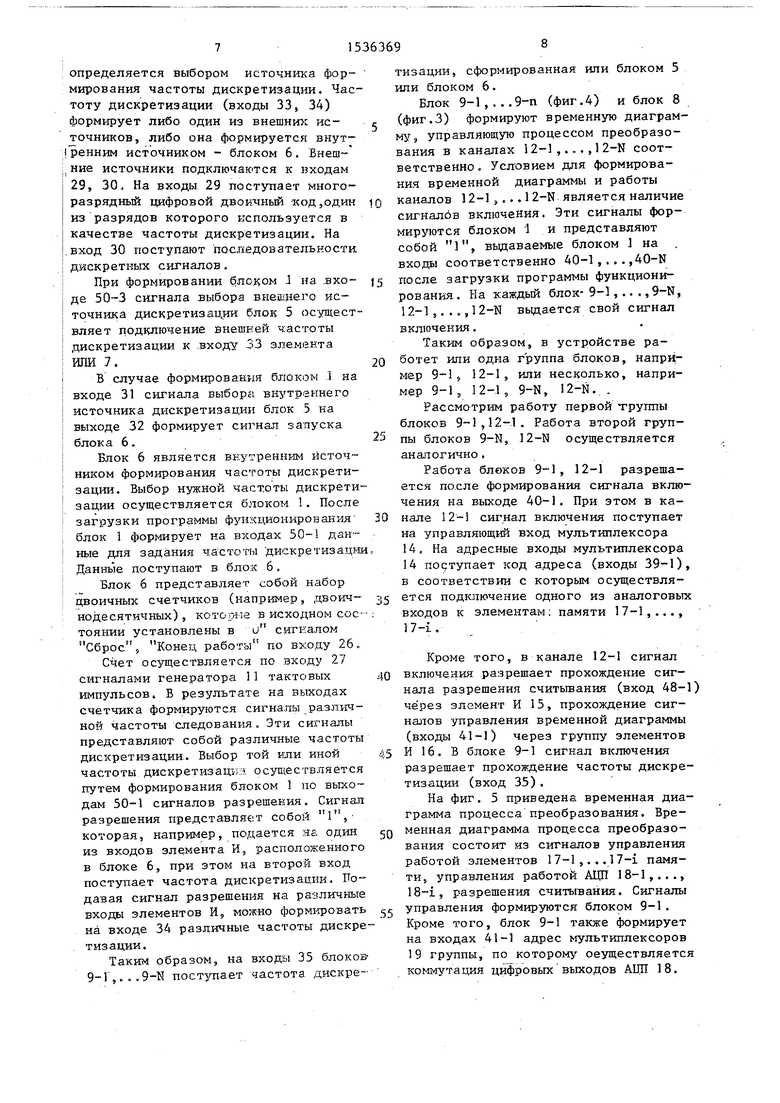

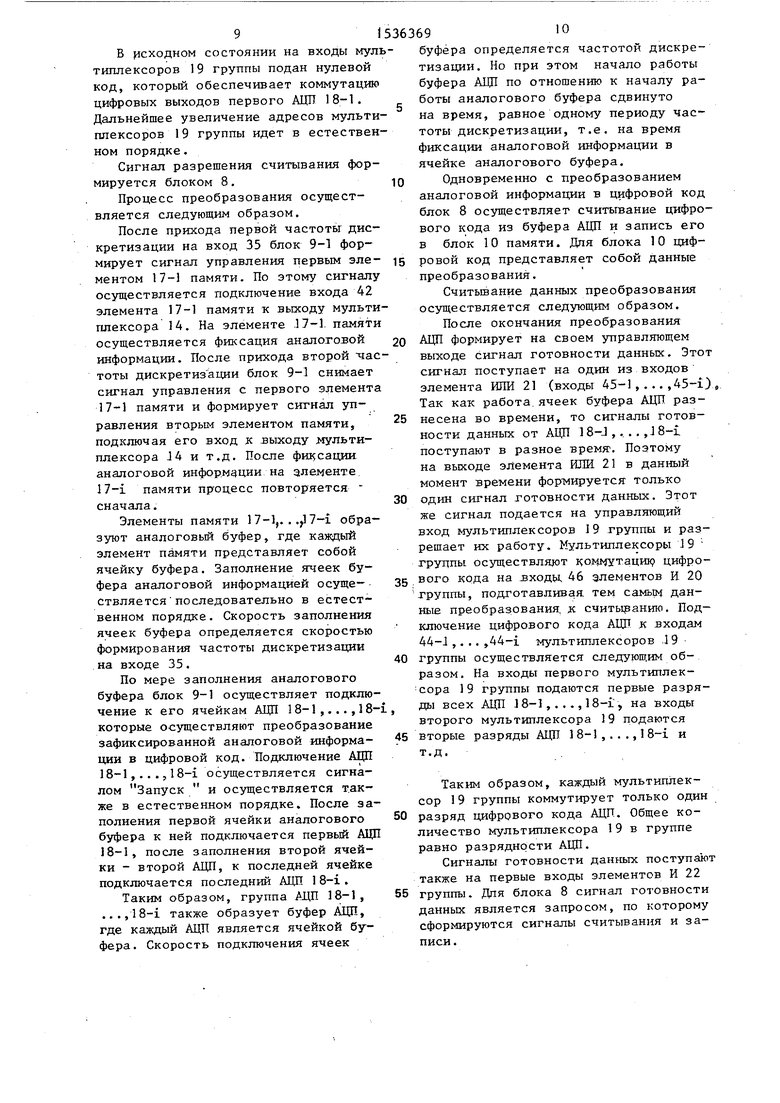

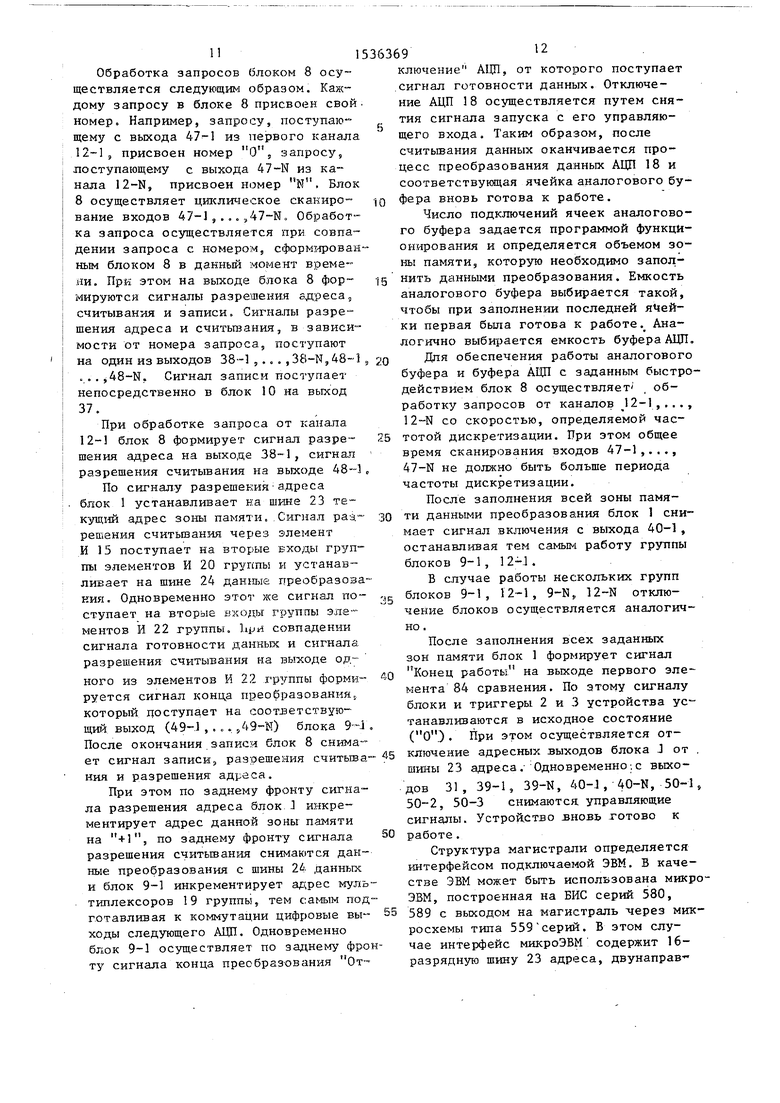

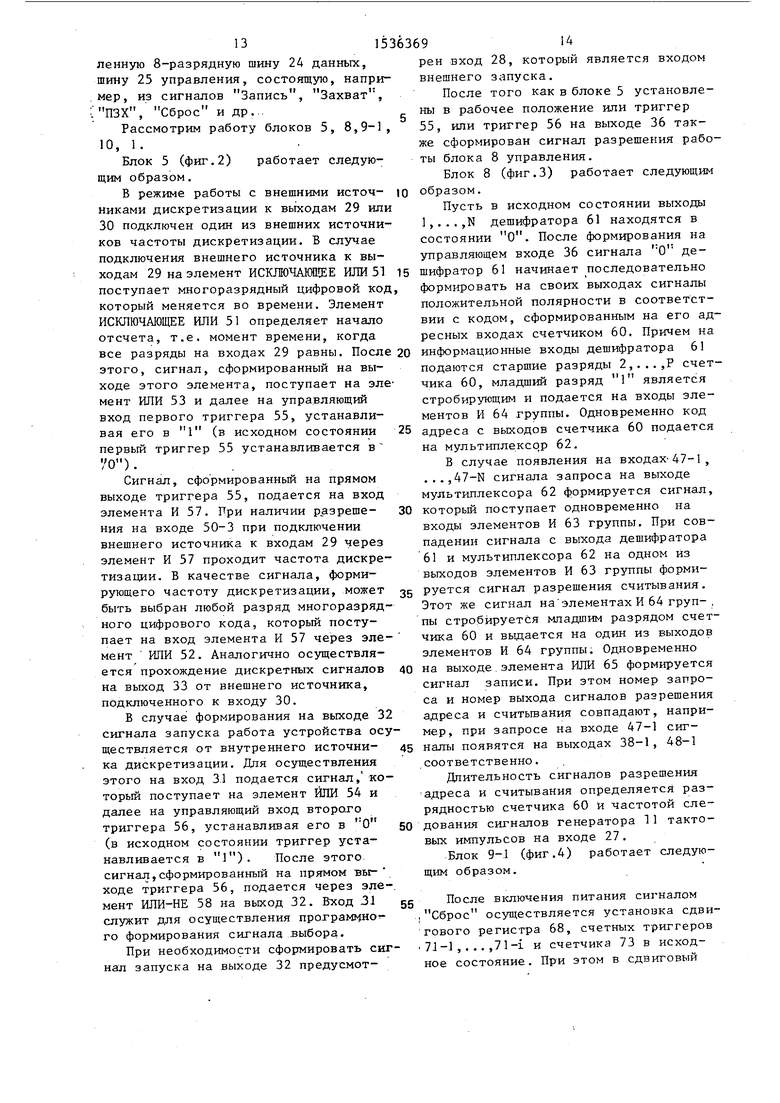

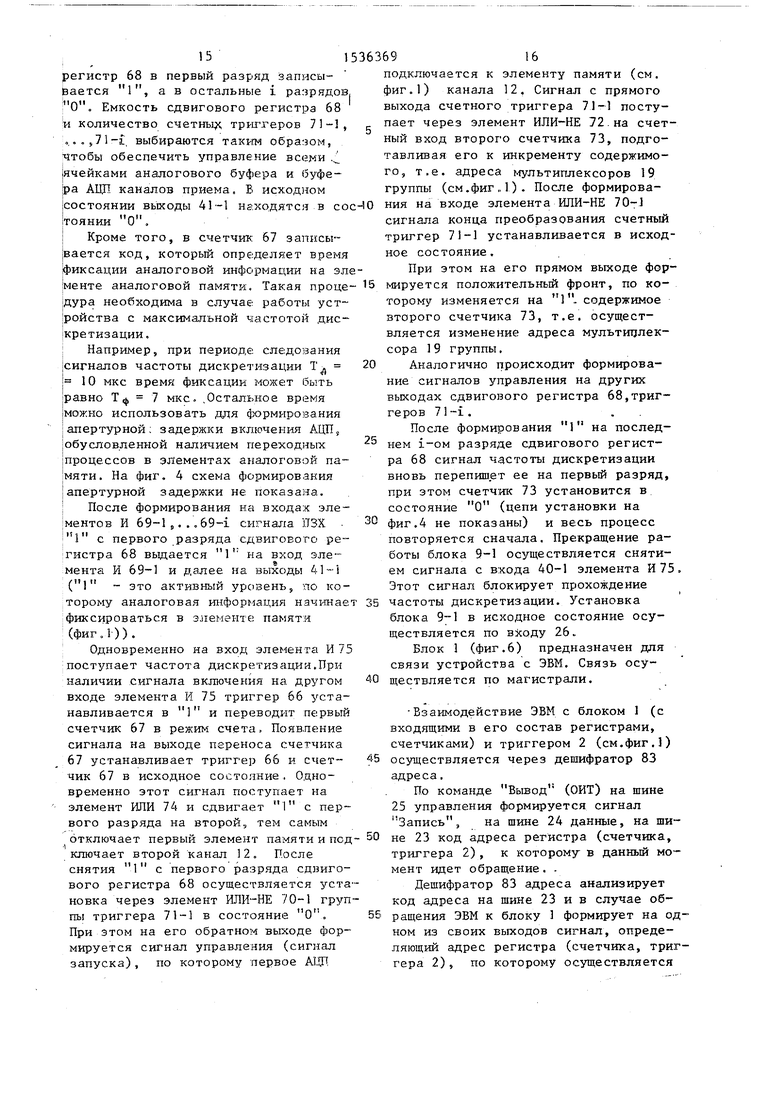

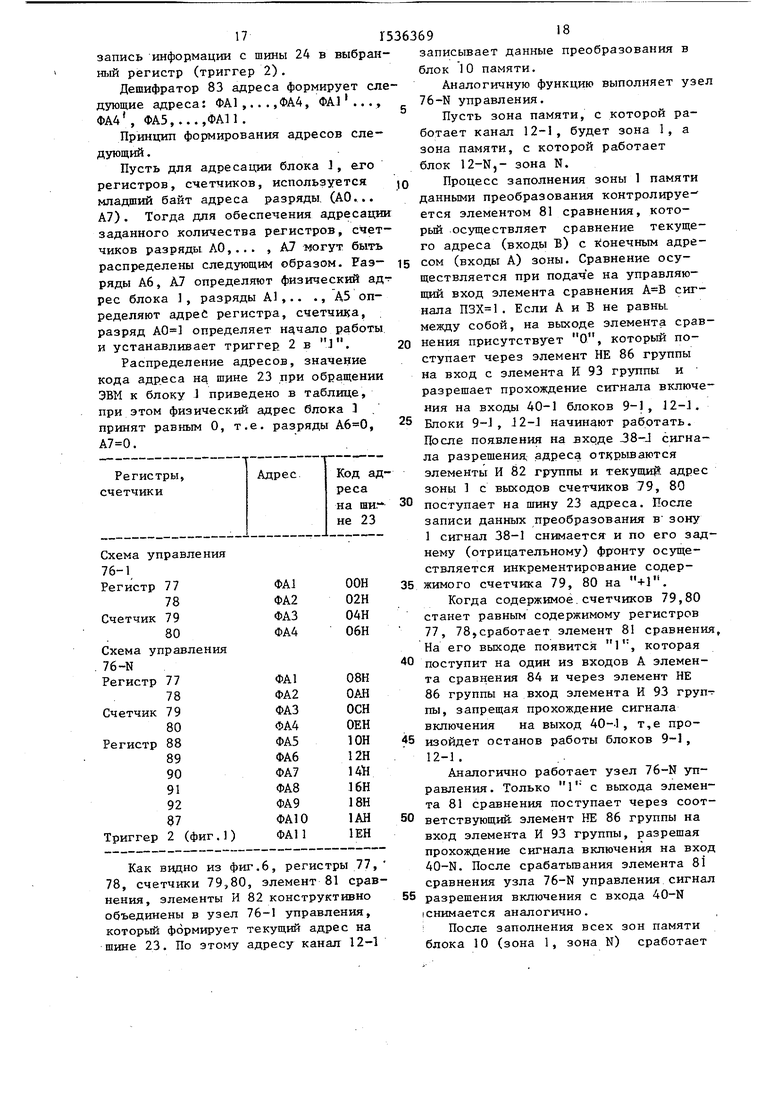

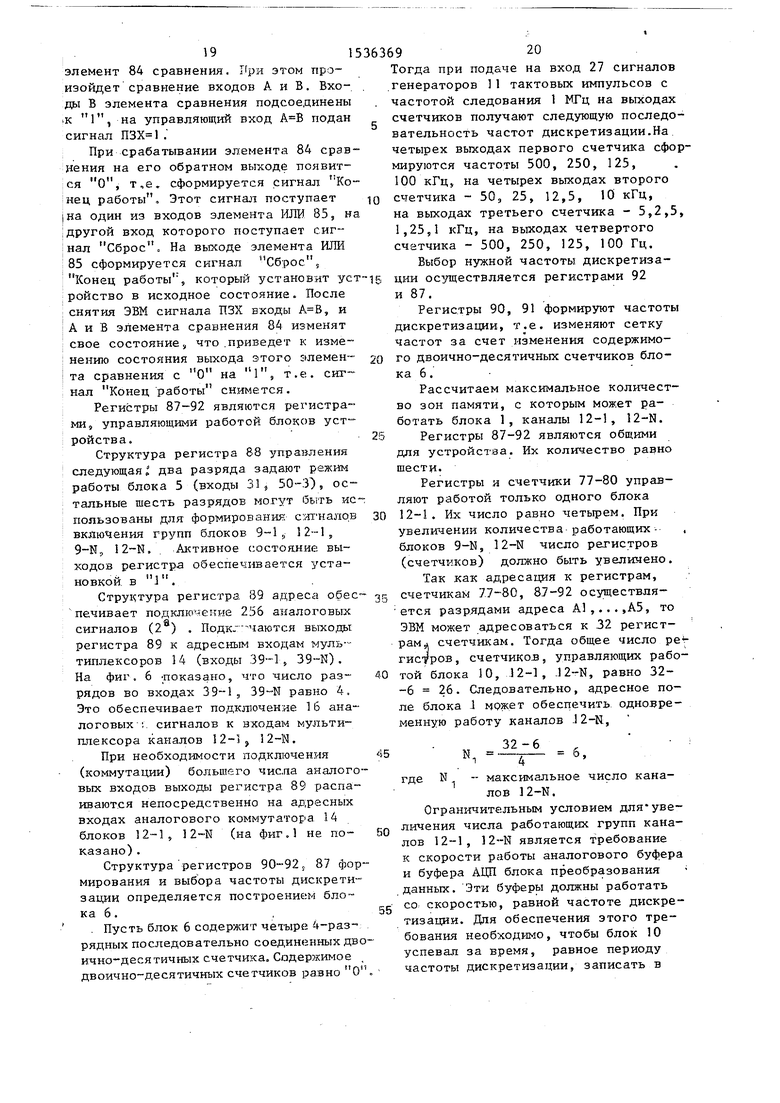

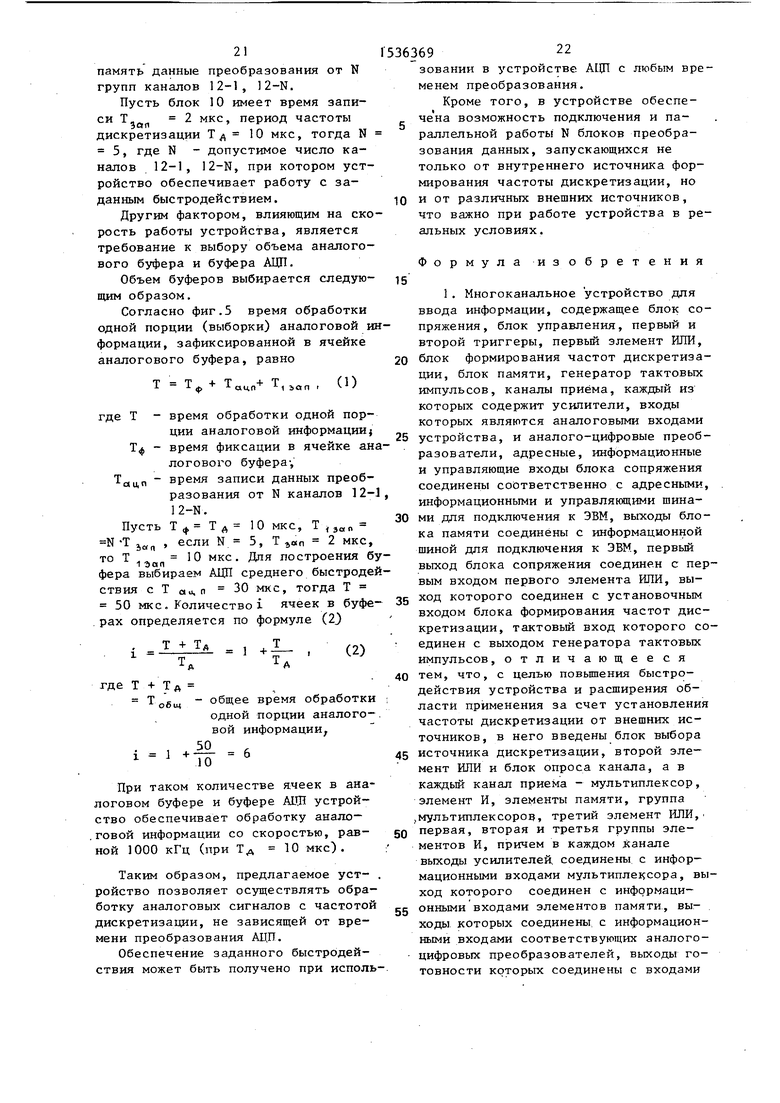

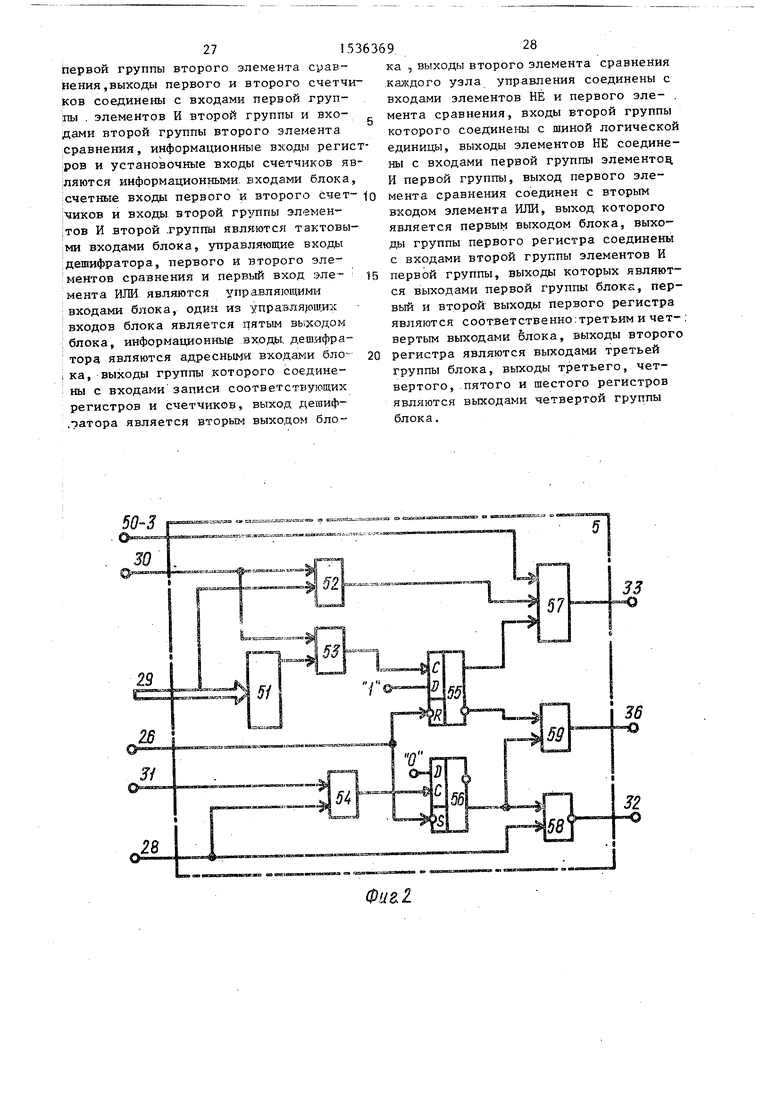

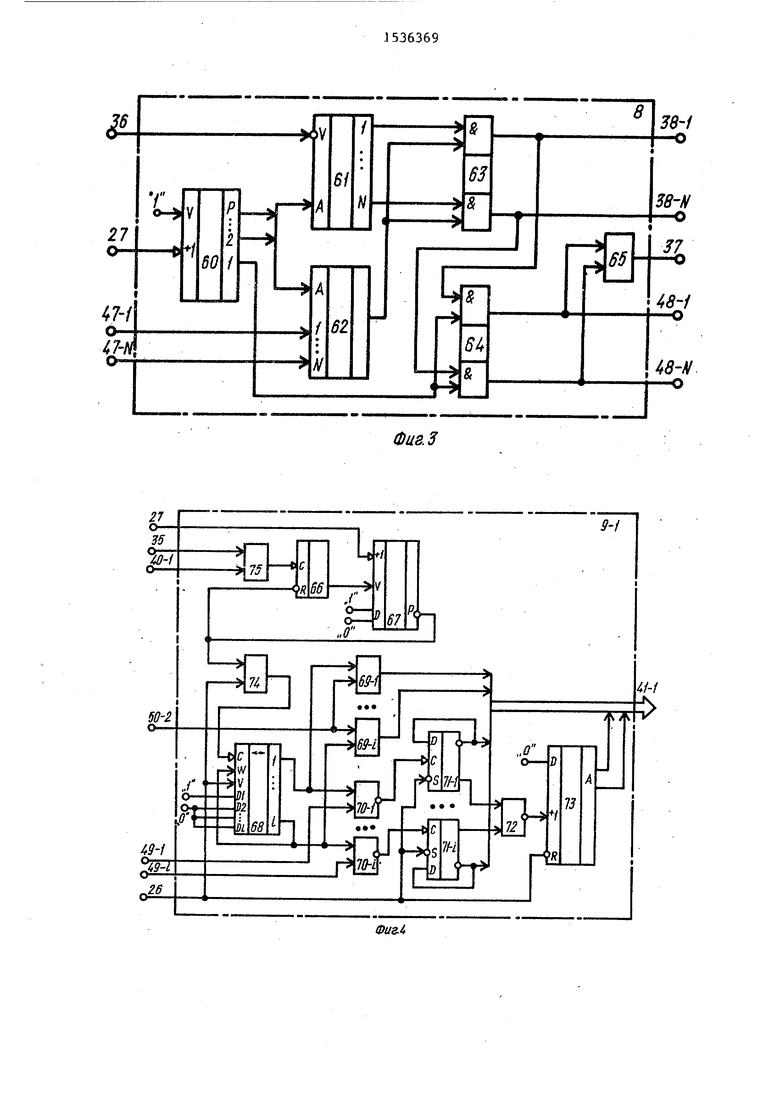

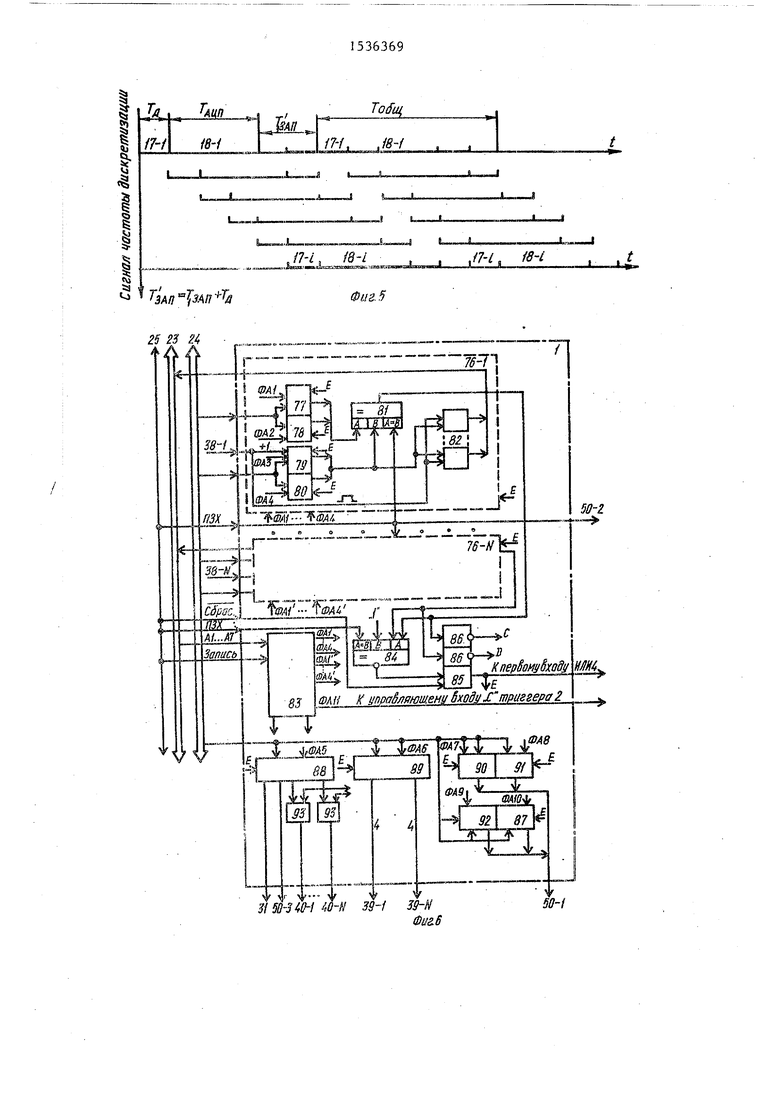

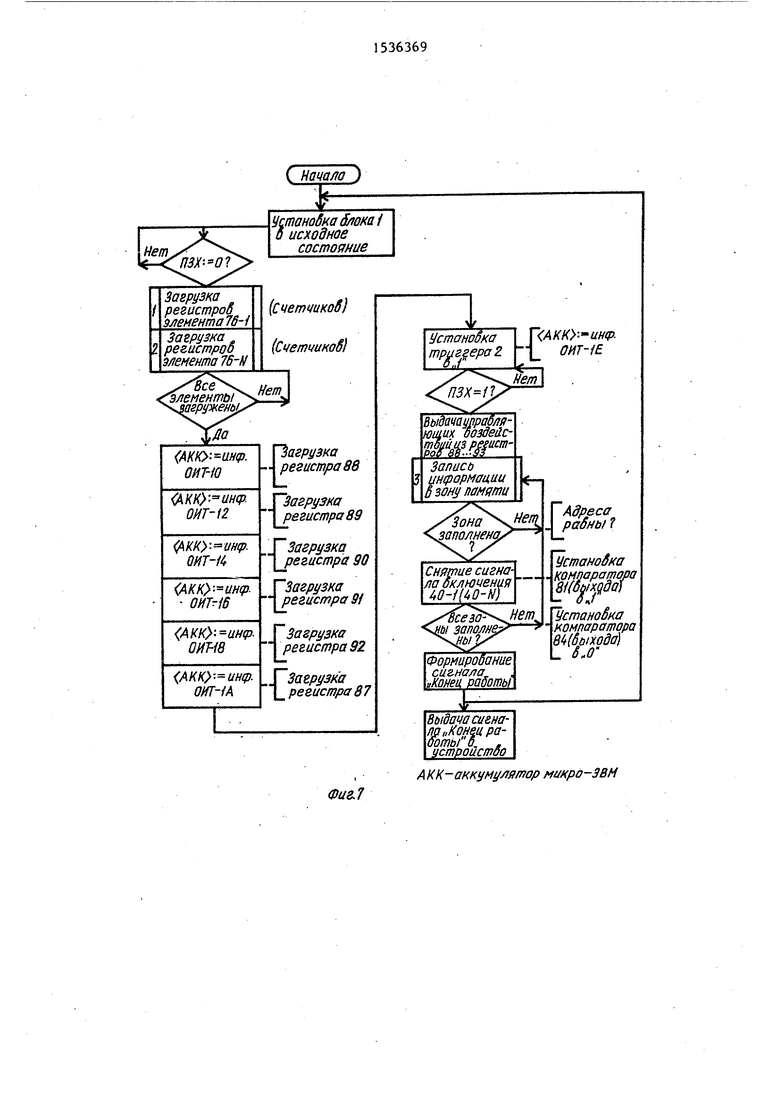

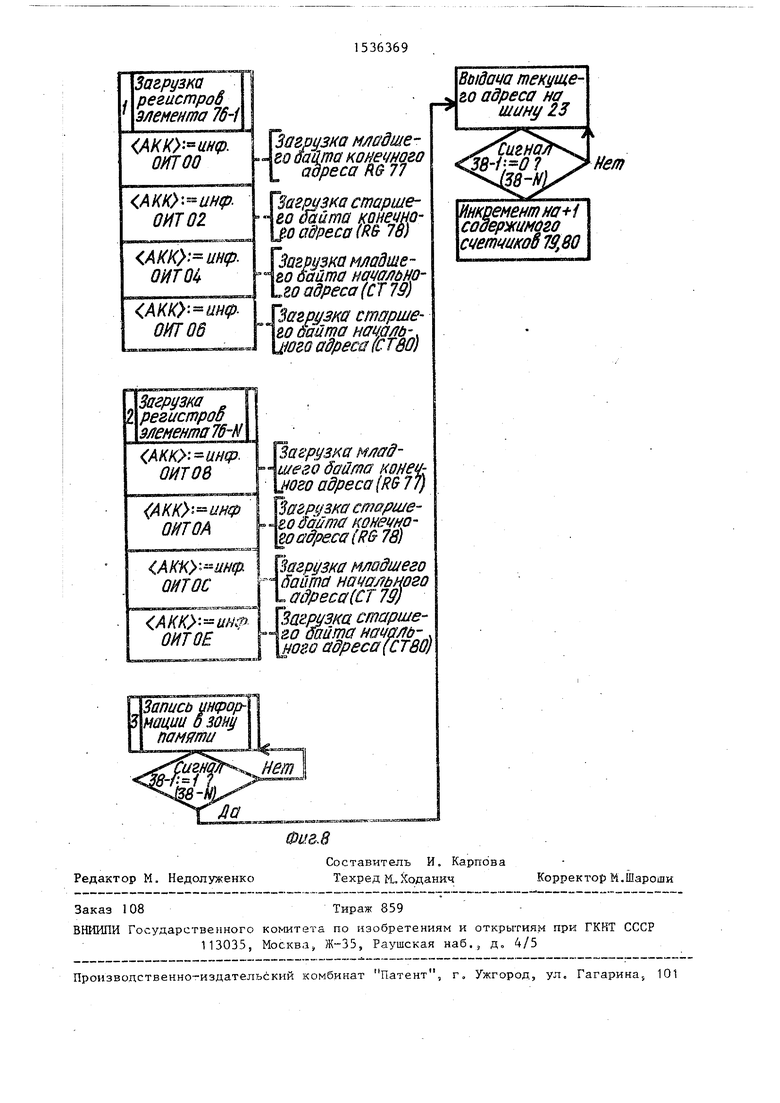

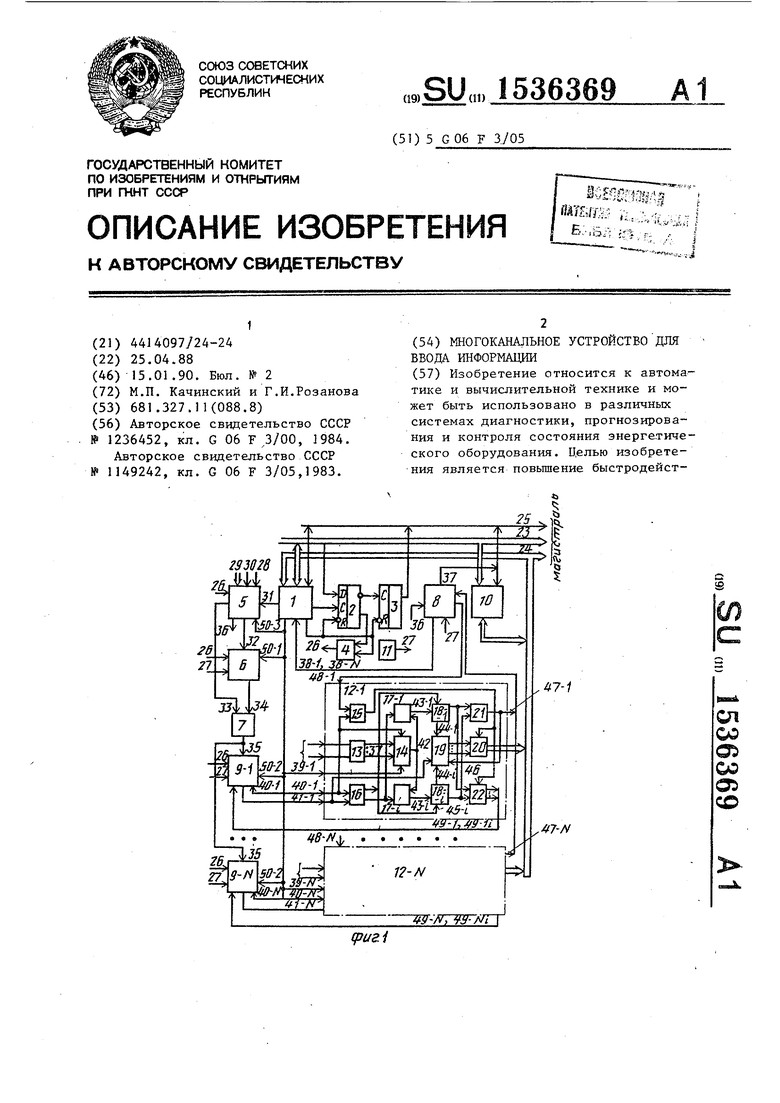

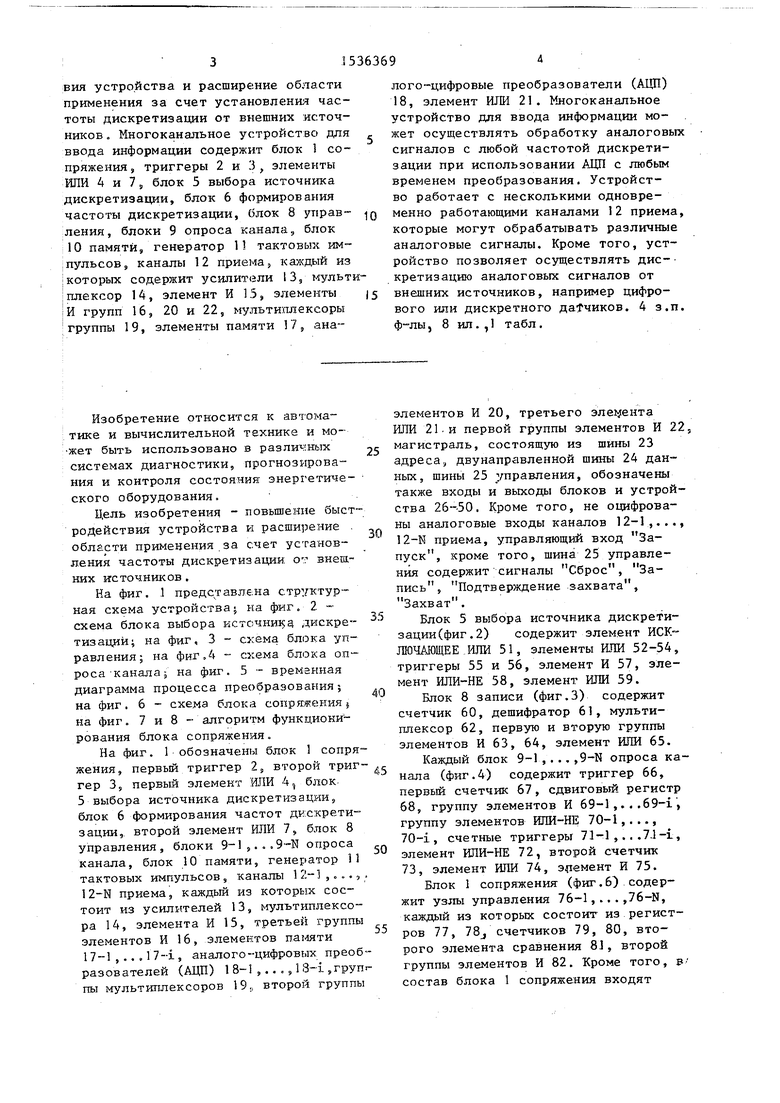

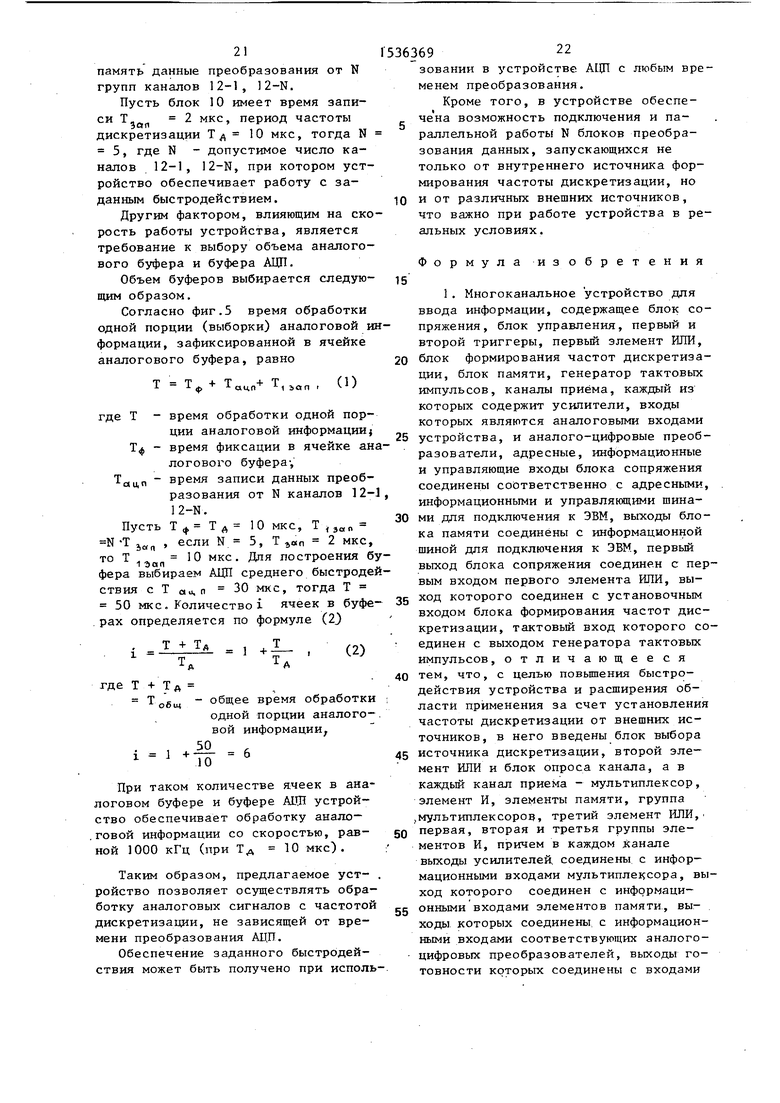

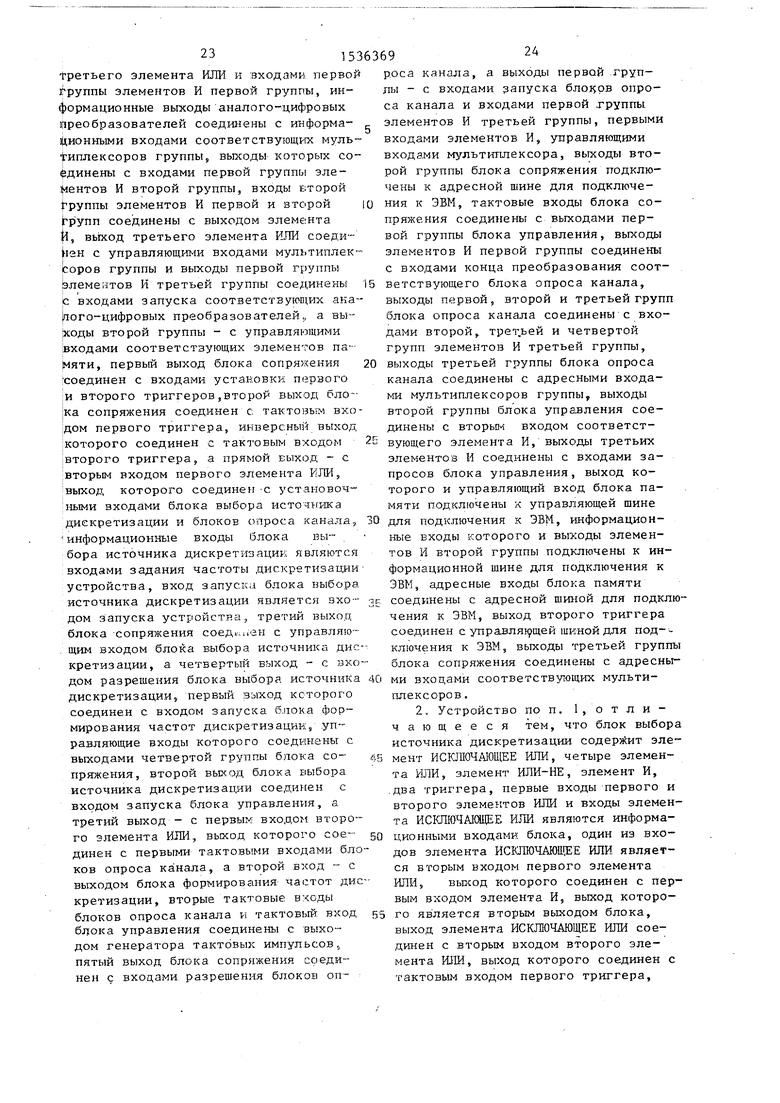

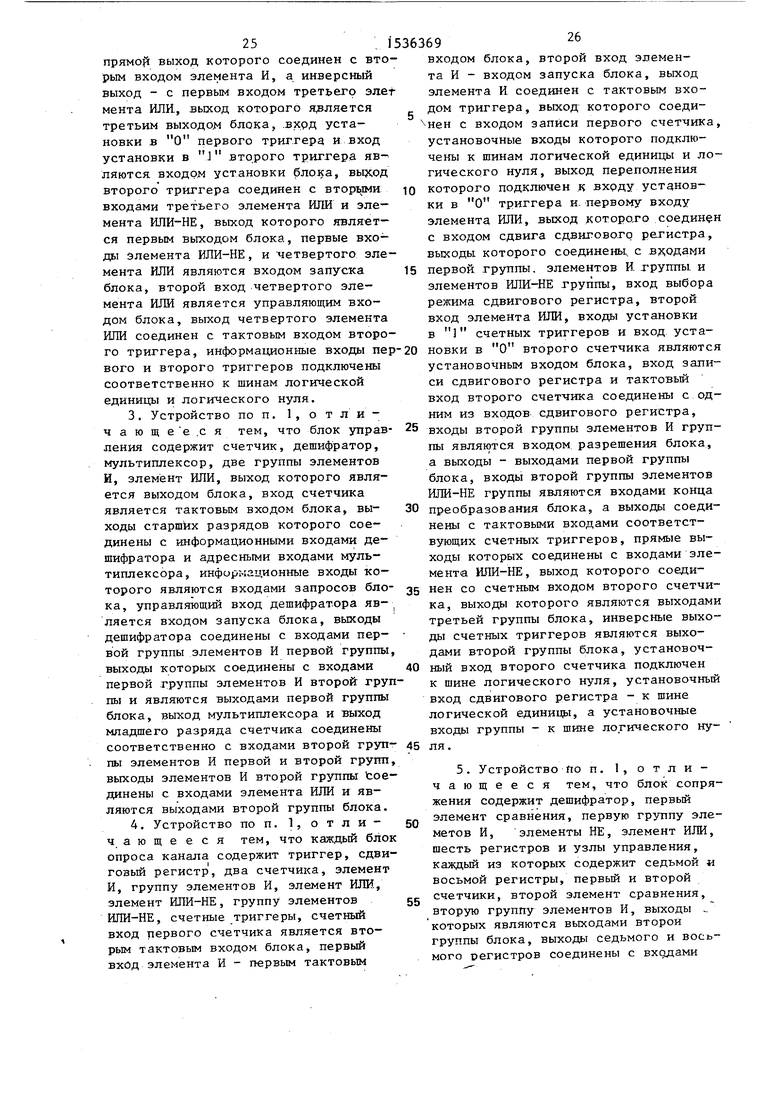

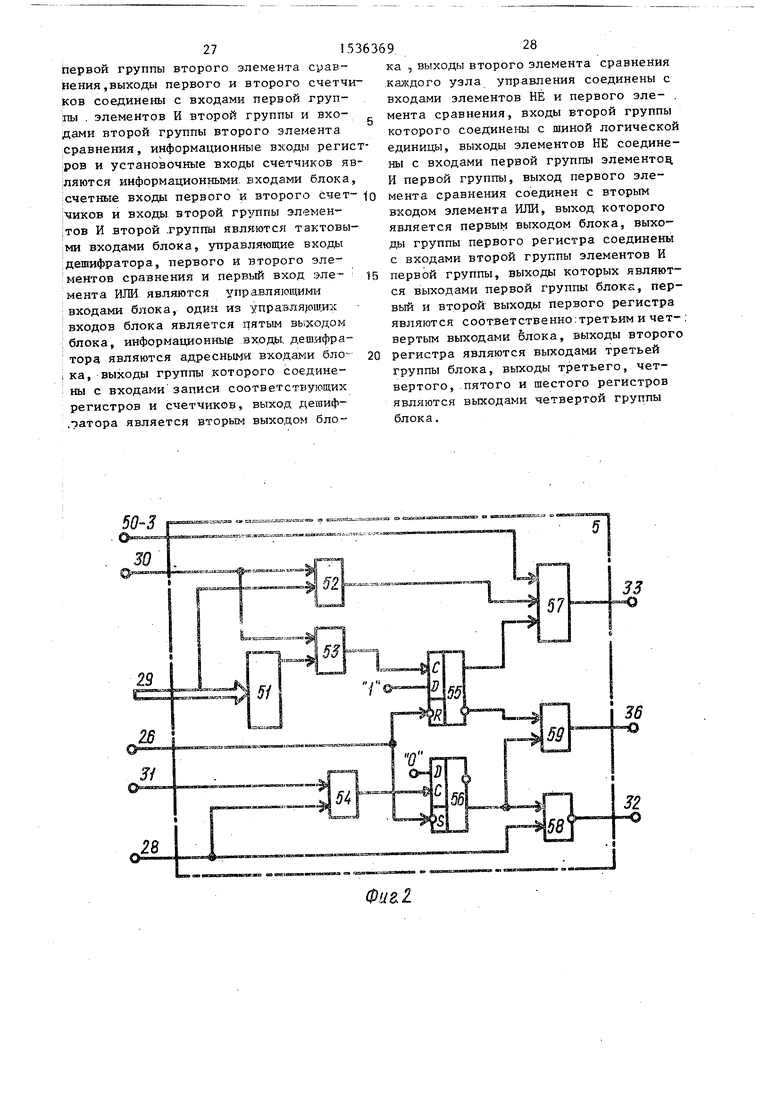

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - схема блока выбора источнику дискретизации; на фиг, 3 - схема блока управления; на фиг,4 - схема блока опроса какала; на фиг. 5 - временная диаграмма процесса преобразования; на фиг. 6 - схема блока сопряжения на фиг. 7 и 8 - алгоритм функционирования блока сопряжения.

На фиг. 1 обозначены блок 1 сопряжения, первый триггер 2S второй триггер 3, первый элемент ИЛИ 4, блок 5 выбора источника дискретизации, блок 6 формирования частот дискретизации, второй элемент ИЛИ 7, блок 8 управления, блоки 9-1,...9-N опроса канала, блок 10 памяти, генератор 11 тактовых импульсов, каналы 12-1,..., 12-N приема, каждый из которых состоит из усилителей 13, мультиплексора 14, элемента И 15, третьей группы элементов И 16, элементов памяти 17-1,...17-1, аналого-цифровых преобразователей (АЦП) 1 8-1 ,..., 1 8-1 ,груп пы мультиплексоров 19. второй группы

5

0

5

0

0

5

элементов И 20, третьего элемента ИЛИ 21 и первой группы элементов И 22, магистраль, состоящую из шины 23 адреса, двунаправленной шины 24 данных, шины 25 управления, обозначены также входы и выходы блоков и устройства 26-50. Кроме того, не оцифрованы аналоговые входы каналов 12-1,..., 12-М приема, управляющий вход Запуск, кроме того, шина 25 управления содержит сигналы Сброс, Запись, Подтверждение захвата, Захват.

Блок 5 выбора источника дискретизации (фиг. 2) содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 51, элементы ИЛИ 52-54, триггеры 55 и 56, элемент И 57, элемент ИЛИ-НЕ 58, элемент ИЛИ 59.

Блок 8 записи (фиг.З) содержит счетчик 60, дешифратор 61, мультиплексор 62, первую и вторую группы элементов И 63, 64, элемент ИЛИ 65.

Каждый блок 9-1,...,9-N опроса канала (фиг.4) содержит триггер 66, первый счетчик 67, сдвиговый регистр 68, группу элементов И 69-1,.. .69-1,

группу элементов ИЛИ-НЕ 70-1

70-i , счетные триггеры 71-1 ,.. .7.1-1, элемент ИЛИ-НЕ 72, второй счетчик 73, элемент ИЛИ 74, элемент И 75.

Блок 1 сопряжения (фиг.6) содержит узлы управления 76-1,...,76-N, каждый из которых состоит из регистров 77, 78j счетчиков 79, 80, второго элемента сравнения 81, второй группы элементов И 82. Кроме того, в состав блока 1 сопряжения входят

5

дешифратор 83, первый элемент сравнения 84, элемент ИЛИ 85, элементы НЕ 86, регистры 87-92, первая группа элементов И 93.

Устройство работает следующим образом.

Процесс преобразования входной аналоговой информации в цифровой под выполняется в каналах 1 2-1 , . . ,р 2-N. Аналоговые сигналы (на фиг.1 не рованы) через усилители 13 подаютс на информационные входы мультиплексора 14.

Управление работой каналов 12-1, ...,12-Н осуществляют блоки 8, 9-1, ...,9-N. Каждый блок 9-1,9-N управляет одним из каналов 12-1,12-N.Блок 8 является общим для блоков 12-1, 12-N.

Организация процесса преобразования осуществляется блоком 3.

Блок 1 (фиг.6) представляет собой набор программно-доступных регистров и счетчиков. Выходы регистров и счетчиков связаны с входами 31,39-1, 39-N 40-1, 40-N, 50-1, 50-2,50-3, управляющими работой блоков 5,6,9-1, 9-N, 12-1,12-N.

Блок 1 выполняет следующие функции: определяет режим работы устройства, задавая источник формирования частоты дискретизации (внешний или внутренний), формирует текущие адреса для записи данных преобразования в блок 10 памяти, задает размеры зон памяти для каждого работающего блока 12-1, 12-NJ определяет количество работающих блоков 12-1, 12-N, 9-1, 9-N, задает адреса мультиплексора 14 для подключения соответствующих входных аналоговых сигналов к входу 42 J в случа„е работы блока 6 задает ему входную информацию для формирования частот дискретизации; выбирает в блоке 6 частоту дискретизацииJ формирует сигнал Конец работы по вхо- ДУ 26.

В блоке 1 эти функции задаются программно.Для этого по магистрали в регистры (счетчики) блока 1 загружается управляющая информация. Источником такой информации может быть ЭВМ или другое любое устройство, имеющее программный и физический стык с магистралью. При этом информация за,- дается на шине 24 данных, код физического адреса блока 1 задается на шине 23 адреса, сигнал Запись -

3696

на шине 25 управления. Загрузка информации в блок осуществляется сигналом Запись при совпадении физического адреса блока 1 с кодом, задан- ным на пгине 23 адреса.

Признаком окончания загрузки информации в блок J является установка триггера 2 в J, который в свою очередь установит триггер 3 в J1 . При этом на выходе триггера 3 сформируется сигнал Захват. ЭВМ ответит выставлением на шине 25 управления сигнала Подтверждение захвата (F3X) ,

после чего ЭВМ отключается от магистрали и устройство приступает к осуществлению процесса преобразования.

Совокупность всей информации, загружаемой в регистры (счетчики) блока 1, представляет собой программу функционирования устройства. Изменяя содержимое программы функционирования, можно оперативно управлять процессом преобразования в устрой

стве.

Программа функционирования загружается после включения питания и установки блоков в исходное состояние.

ЭВМ осуществляет установку блоков

в исходное состояние сигналом Сброс формируемым на шине 25 управления. Кроме того, устройство может устанавливаться в исходное состояние сигналом Конец работы, который формирует блок 1 на выходе первого элемента 84 сравнения после окончания процесса преобразования. Эти два сигнала смешиваются в блоке 1 и с выхода блока 1 поступают на установочные входы триггеров 2 и 3 и на вход элемента ИЛИ 4 ка4с сигнал Сброс, Конец работы.

Сигнал Сброс, Конец работы,

проходит через элемент ИЛИ 4 на вход 26 только в случае отсутствия процесса преобразования в устройстве (триггеры 2, 3 в состоянии О).

В случае формирования блоком 1 сигнала Конец работы и установки триггеров 2, 3 в О с магистрали снимается сигнал Захват. В свою очередь ЭВМ снимает сигнал ПЗХ и подключается к магистрали, т.е. ЭВМ и устройство

вновь готовы к загрузке программы

функционирования и осуществлению процесса преобразования.

Блок 5 устанавливает режим работы устройства. Режим работы устройства

определяется выбором источника формирования частоты дискретизации. Частоту дискретизации (входы 33, 34) формирует либо один из внешних ис- точников, либо она формируется внут- Iренним источником - блоком 6. Внеш- ние источники подключаются к входам 29s 30, На входы 29 поступает многоразрядный цифровой цвокчный -код,один из разрядов которого используется в качестве частоты дискретизации. На вход 30 поступают последовательности дискретных сигналов.

При формировании блоком J на вхо де 50-3 сигнала выбора внешнего источника дискретизации блок 5 осуществляет подключение внешней частоты дискретизации к входу 33 элемента ИЛИ 7.

В случае формирования блоком 1 на входе 31 сигнала выбора внутреннего источника дискретизации блок 5 на выходе 32 формирует сигнал запуска блока 6.

Блок 6 является внутренним источником формирования частоты дискретизации. Выбор нужной частоты дискретизации осуществляется блоком 1. После загрузки программы функционирования блок 1 формирует на входах 50-1 данные для задания частоты дискретизации Данные поступают в блол 6.

Блок 6 представляет собой набор двоичных счетчиков (например, двоич- нодесятичных), котсзна в исходном сое тоянии установлены в и сип-алом Сброс, Конец работы по вхоцу 26.

Счет осуществляется по входу 27 сигналами генератора 11 тактовых импульсов. В результате на выходах счетчика формируются сигналы различной частоты следования. Эти сигналы представляют собой различные частоты дискретизации. Выбор той или иной частоты дискретизащ/ осуществляется путем формирования блоком 1 по выходам 50-1 сигналов разрешения. Сигнал разрешения представляет собой 1, которая, например, подается че один из входов элемента И, расположенного в блоке 6, при этом на второй вход поступает частота дискретизации. Подавая сигнал разрешения на различные входы элементов И, можно формировать на входе 34 различные частоты дискретизации.

Таким образом, на входы 35 блоков- 9-1,...9-N поступает частота дискретизации, сформированная или блоком 5 или блоком 6.

Блок 9-1,...9-п (фиг.4) и блок 8 (фиг.З) формируют временную диаграмму, управляющую процессом преобразования в каналах 12-3,.,.,12-N соответственно . Условием для формирования временной диаграммы и работы каналов 12-1 , . .. 1 2-N является наличие сигналбв включения. Эти сигналы формируются блоком 1 и представляют собой 3, выдаваемые блоком 1 на .

входы соответственно 40-140-N

после загрузки программы функционирования. На каждый блок- 9-1,...,9-N, 12-1,..., 2-N выдается- свой сигнал включения.

Таким образом, в устройстве ра- ботет или одна группа блоков, например 9-1, 12-1, или несколько, например 9-1, 12-1, 9-N, 12-N. .

Рассмотрим работу первой труппы блоков 9-1,12-1. Работа второй группы блоков 9-N, 12-N осуществляется аналогично.

Работа блоков 9-1, 12-1 разрешается после формирования сигнала включения на выходе 40-1. При этом в канале 12-1 сигнал включения поступает на управляющий вход мультиплексора 14. На адресные входы мультиплексора 14 поступает код адреса (входы 39-1) в соответствии с которым осуществляется подключение одного из аналоговых входов к элементам. памяти 17-1,..., 17-i,

Кроме того, в канале 12-1 сигнал включения разрешает прохождение сигнала разрешения считывания (вход 48через элемент И 15, прохождение сигналов управления временной диаграммы (входы 41-1) через группу элементов И 16. В блоке 9-1 сигнал включения разрешает прохождение частоты дискретизации (вход 35).

На фиг. 5 приведена временная диаграмма процесса преобразования. Временная диаграмма процесса преобразования состоит из сигналов управления работой элементов 17-1,...17-i памяти, управления работой АЦП 18-1,..., 18-i, разрешения считывания. Сигналы управления формируются блоком 9-1. Кроме того, блок 9-1 также формирует на входах 41-3 адрес мультиплексоров 19 группы, по которому осуществляется коммутация цифровых выходов АИЛ 18.

В исходном состоянии на входы мултиплексоров 19 группы подан нулевой код, который обеспечивает коммутацию цифровых выходов первого АЦП 18-1. Дальнейшее увеличение адресов мультиплексоров 19 группы идет в естественном порядке.

Сигнал разрешения считывания формируется блоком 8.

Процесс преобразования осуществляется следующим образом.

После прихода первой частоты дискретизации на вход 35 блок 9-1 формирует сигнал управления первым эле- ментом 17-1 памяти. По этому сигналу осуществляется подключение входа 42 элемента 17-1 памяти к выходу мультиплексора 14. На элементе 17-1 памяти осуществляется фиксация аналоговой информации. После прихода второй частоты дискретизации блок 9-1 снимает сигнал управления с первого элемента 17-1 памяти и формирует сигнал управления вторым элементом памяти, подключая его вход к выходу мультиплексора J4 и т.д. После фиксации аналоговой информации на элементе 17-1 памяти процесс повторяется - сначала.

Элементы памяти 17-l,...jl7-i образуют аналоговый буфер, где каждый элемент памяти представляет собой ячейку буфера. Заполнение ячеек буфера аналоговой информацией осуще- ствляется последовательно в естественном порядке. Скорость заполнения ячеек буфера определяется скоростью формирования частоты дискретизации на входе 35,

По мере заполнения аналогового буфера блок 9-1 осуществляет подключение к его ячейкам АЦП 18-1 ,...,18-i которые осуществляют преобразование зафиксированной аналоговой информации в цифровой код. Подключение АЦП 18-1,...,18-i осуществляется сигналом Запуск и осуществляется также в естественном порядке. После заполнения первой ячейки аналогового буфера к ней подключается первый АЦП 18-1, после заполнения второй ячейки - второй АЦП, к последней ячейке подключается последний АЦП 18-i.

Таким образом, группа АЦП 18-1, .. .,18-i также образует буфер АЦП, где каждый АЦП является ячейкой буфера. Скорость подключения ячеек

25

Ю

15 20

35 40

5

30

45

0

буфера определяется частотой дискретизации. Но при этом начало работы буфера АЦП по отношению к началу работы аналогового буфера сдвинуто на время, равное одному периоду частоты дискретизации, т.е. на время фиксации аналоговой информации в ячейке аналогового буфера.

Одновременно с преобразованием аналоговой информации в цифровой код блок 8 осуществляет считывание цифрового кода из буфера АЦП и запись его в блок 10 памяти. Для блока 10 цифровой код представляет собой данные преобразования.

Считывание данных преобразования осуществляется следующим образом. После окончания преобразования АЦП формирует на своем управляющем выходе сигнал готовности данных. Этот сигнал поступает на один из входов элемента ИЛИ 21 (входы 45-1 , ... ,45-i.) „ Так как работа ячеек буфера АЦП разнесена во времени, то сигналы готовности данных от АЦП 18-J ,. . . ,18-i поступают в разное время4. Поэтому на выходе элемента ИЛИ 21 в данный момент времени формируется только один сигнал готовности данных. Этот же сигнал подается на управляющий вход мультиплексоров 19 группы и разрешает их работу. Мультиплексоры 19 грудпы осуществляют коммутации цифрового кода на входы, 46 элементов И 20 группы, подготавливая, тем самым данные преобразования к считыванию. Подключение цифрового кода АЦП к входам 44-1,...,44-i мультиплексоров 19 группы осуществляется следующим образом. На входы первого мультиплексора 19 группы подаются первые разряды всех АЦП 18-1,...,18-i, на входы второго мультиплексора 19 подаются вторые разряды АЦП 18-1,...,8-i и т.д.

Таким образом, каждый мультиплексор 19 группы коммутирует только один разряд цифрового кода АЦП. Общее количество мультиплексора 19 в группе равно разрядности АЦП.

Сигналы готовности данных поступают также на первые входы элементов И 22 группы. Для блока 8 сигнал готовности данных является запросом, по которому сформируются сигналы считывания и записи.

Обработка запросов блоком 8 осуществляется следующим образом. Каждому запросу в блоке 8 присвоен свой номер. Например, запросу, поступающему с выхода 47-1 из первого канала 12-1, присвоен номер чапросу, поступающему с выхода 47-N из канала 12-N, присвоен номер N, Блок 8 осуществляет циклическое скакиро- вание входов 47-1, ...,47-N, Обработка запроса осуществляется прр совпадении запроса с номером, сформированным блоком 8 в данный момент времени. При этом на выходе блока 8 фор- мнруются сигналы разрешения адреса, считывания и записи. Сигналы разрешения адреса и считывания, в зависимости от номера запроса, поступают на один из выходов 38-1,...,38-N, ...,48-N. Сигнал записи поступает непосредственно в блок 10 на выход 37.

При обработке запроса от канала 12-1 блок 8 формирует сигнал разре- шения адреса на выходе 38-1, сигнал разрешения считывания на выходе 48-1

По сигналу разрешения адреса блок 1 устанавливает ра шине 23 текущий адрес зоны памяти. Сигнал рад- решения считывания через элемент И 15 поступает на вторые входы группы элементов И 20 группы и устанавливает на шине 24 данные преобразования. Одновременно этот же сигнал по-

ступает на вторые влоды группы элементов И 22 группы, lip и совпадении сигнала готовности данных и сигнала разрешения считывания на. выходе одного из элементов И 22 группы форми™ руется сигнал конца преобразований; который цоступает на соответствующий выход (49-1,...,49-М) блока 9 -J После окончания эалисч блок 8 снимает сигнал записи, разоешения считыва ния и разрешения адреса.

При этом по заднему фронту сигнала разрешения адреса блок 1 инкремент ируе т адрес данной зоны памяти на -И, по заднему фронту сигнала разрешения считывания снимаются данные преобразования с шины 2Ј данных и блок 9-1 инкрементирует адрес мультиплексоров 19 группы, тем самым подготавливая к коммутации цифровые вы- ходы следующего АЦП. Одновременно блок 9-1 осуществляет по заднему фро ту сигнала конца преобразования От

5 0

5

0 с

С;

0

5

5

0

ключение АЦП, от которого поступает сигнал готовности данных. Отключение АЦП 18 осуществляется путем снятия сигнала запуска с его управляющего входа. Таким образом, после считывания данных оканчивается процесс преобразования данных АЦП 18 и соответствующая ячейка аналогового буфера вновь готова к работе.

Число подключений ячеек аналогового буфера задается программой функционирования и определяется объемом зоны памяти, которую необходимо заполнить данными преобразования. Емкость аналогового буфера выбирается такой, чтобы при заполнении последней ячейки первая была готова к работе% Аналогично выбирается емкость буфера АЦП,

Для обеспечения работы аналогового буфера и буфера АЦП с заданным быстродействием блок 8 осуществляет обработку запросов от каналов J2-1,,.., 12-N со скоростью, определяемой частотой дискретизации. При этом общее время сканирования входов 47-1,..., 47-N не должно быть больше периода частоты дискретизации.

После заполнения всей зоны памяти данными преобразования блок 1 снимает сигнал включения с выхода 40-1, останавливая тем самым работу группы блоков 9-1, 12-J.

В спучае работы нескольких групп блоков 9-1, 12-1, 9-N, 12-N отключение блоков осуществляется аналогично.

После заполнения всех заданных зон памяти блок 1 формирует сигнал Конец работа на выходе первого элемента 84 сравнения. По этому сигналу блоки и триггеры 2 и 3 устройства устанавливаются в исходное состояние (О) При этом осуществляется отключение адресных выходов блока J от шины 23 адреса. Одновременно с выходов 31, 39-1, 39-N, 40-1, 40-N, 50-1, 50-2, 50-3 снимаются управляющие сигналы. Устройство вновь готово к работе.

Структура магистрали определяется интерфейсом подключаемой ЭВМ. В качестве ЭВМ может быть использована микро- ЭВМ, построенная на БИС серий 580, 589 с выходом на магистраль через микросхемы типа 559 серий. В этом случае интерфейс микроЭВМ содержит 16- разрядную шину 23 адреса, двунаправ13153636914

ленную 8-разрядную шину 24 данных, рен вход 28, который является входом

внешнего запуска.

После того как в блоке 5 установлешину 25 управления, состоящую, например, из сигналов Запись, Захват, .ПЗХ, Сброс и др.

Рассмотрим работу блоков 5, 8,9-1, 10, 1.

Блок 5 (фиг.2) работает следующим образом.

В режиме работы с внешними источ- ю никами дискретизации к выходам 29 или 30 подключен один из внешних источников частоты дискретизации. В случае подключения внешнего источника к выходам 29 на элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 51 15 шифратор 61 начинает последовательно поступает многоразрядный цифровой код, формировать на своих выходах сигналы который меняется во времени. Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 51 определяет начало отсчета, т.е. момент времени, когда все разряды на входах 29 равны. После 20 информационные входы дешифратора 61 этого, сигнал, сформированный на вы- подаются старшие разряды 2,...,Р счетны в рабочее положение или триггер 55, или триггер 56 на выходе 36 также сформирован сигнал разрешения работы блока 8 управления.

Блок 8 (фиг.З) работает следующим образом.

Пусть в исходном состоянии выходы 1,...,N дешифратора 61 находятся в состоянии О. После формирования на управляющем входе 36 сигнала О 1 деположительной полярности в соответствии с кодом, сформированным на его адресных входах счетчиком 60. Причем на

шифратор 61 начинает последовательно формировать на своих выходах сигналы информационные входы дешифратора 61 подаются старшие разряды 2,...,Р счетны в рабочее положение или триггер 55, или триггер 56 на выходе 36 также сформирован сигнал разрешения работы блока 8 управления.

Блок 8 (фиг.З) работает следующим образом.

Пусть в исходном состоянии выходы 1,...,N дешифратора 61 находятся в состоянии О. После формирования на управляющем входе 36 сигнала О 1 дешифратор 61 начинает последовательно формировать на своих выходах сигналы информационные входы дешифратора 61 подаются старшие разряды 2,...,Р счетположительной полярности в соответствии с кодом, сформированным на его адресных входах счетчиком 60. Причем на

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

| Способ компенсации фазовых искажений в многоканальных системах аналого-цифрового преобразования сигналов и устройство для его реализации | 2019 |

|

RU2723566C1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Устройство для ввода и вывода изображений объектов | 1990 |

|

SU1829045A1 |

| БОРТОВОЙ СПЕЦВЫЧИСЛИТЕЛЬ | 2013 |

|

RU2522852C1 |

| Устройство для ввода аналоговых сигналов | 1990 |

|

SU1742810A1 |

| ЦИФРОАНАЛОГОВАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ И ОБРАБОТКИ ИНФОРМАЦИИ | 1991 |

|

RU2022364C1 |

| Устройство для ввода информации от аналоговых датчиков | 1985 |

|

SU1298734A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в различных системах диагностики, прогнозирования и контроля состояния энергетического оборудования. Целью изобретения является повышение быстродействия устройства и расширение области применения за счет установления частоты дискретизации от внешних источников. Многоканальное устройство для ввода информации содержит блок 1 сопряжения, триггеры 2 и 3, элементы ИЛИ 4 и 7, блок 5 выбора источника дискретизации, блок 6 формирования частоты дискретизации, блок 8 управления, блоки 9 опроса канала, блок 10 памяти, генератор 11 тактовых импульсов, каналы 12 приема, каждый из которых содержит усилители 13, мультиплексор 14, элемент И 15, элементы И групп 16, 20 и 22, мультиплексоры группы 19, элементы памяти 17, аналого-цифровые преобразователи (АЦП) 18, элемент ИЛИ 21. Многоканальное устройство для ввода информации может осуществлять обработку аналоговых сигналов с любой частотой дискретизации при использовании АЦП с любым временем преобразования. Устройство работает с несколькими одновременно работающими каналами 12 приема, которые могут обрабатывать различные аналоговые сигналы. Кроме того, устройство позволяет осуществлять дискретизацию аналоговых сигналов от внешних источников, например цифрового или дискретного датчиков. 4 з.п. ф-лы, 8 ил., 1 табл.

ходе этого элемента, поступает на элемент ИЛИ 53 и далее на управляющий вход первого триггера 55, устанавливая его в 1 (в исходном состоянии первый триггер 55 устанавливается в /О).

Сигнал, сформированный на прямом выходе триггера 55, подается на вход элемента И 57. При наличии разрешения на входе 50-3 при подключении внешнего источника к входам 29 через элемент И 57 проходит частота дискретизации. В качестве сигнала, формирующего частоту дискретизации, может быть выбран любой разряд многоразрядного цифрового кода, который поступает на вход элемента И 57 через элемент ИЛИ 52. Аналогично осуществляется прохождение дискретных сигналов на выход 33 от внешнего источника, подключенного к входу 30.

В случае формирования на выходе 32 сигнала запуска работа устройства осуществляется от внутреннего источника дискретизации. Для осуществления этого на вход 31 подается сигнал, который поступает на элемент ИЛИ 54 и далее на управляющий вход второго триггера 56, устанавливая его в О (в исходном состоянии триггер устанавливается в 1). После этого сигнал,сформированный на прямом вы- ходе триггера 56, подается через элемент ИЛИ-НЕ 58 на выход 32. Вход 31 служит для осуществления программного формирования сигнала выбора.

При необходимости сформировать сигнал запуска на выходе 32 предусмот

5

чика 60, младший разряд 1 является стробирующим и подается на входы элементов И 64 группы. Одновременно код

5 адреса с выходов счетчика 60 подается на мультиплексор 62.

В случае появления на входах 47-1 , ...,47-N сигнала запроса на выходе мультиплексора 62 формируется сигнал,

0 который поступает одновременно на входы элементов И 63 группы. При совпадении сигнала с выхода дешифратора 61 и мультиплексора 62 на одном из выходов элементов И 63 группы формируется сигнал разрешения считывания. Этот же сигнал на элементах И 64 труп- . пы стробируется младшим разрядом счетчика 60 и выдается на один из выходов элементов И 64 группы. Одновременно на выходе элемента ИЛИ 65 формируется сигнал записи. При этом номер запроса и номер выхода сигналов разрешения адреса и считывания совпадают, например, при запросе на входе 47-1 сиг5 налы появятся на выходах 38-1, 48-1 соответственно.

Длительность сигналов разрешения адреса и считывания определяется разрядностью счетчика 60 и частотой следования сигналов генератора 11 тактовых импульсов на входе 27.

Блок 9-1 (фиг.4) работает следующим образом.

0

0

55

После включения питания сигналом ,Сброс осуществляется установка сдвигового регистра 68, счетных триггеров 71-,...,71-i и счетчика 73 и исходное состояние. При этом в сдвиговый

15

регистр 68 в первый разряд записывается 1, а в остальные i разрядов О. Емкость сдвигового регистра 68 и количество счетных, триггеров 71-1, . ..,71-Ј выбираются таким обра-эом, чтобы обеспечить управление всеми (ячейками аналогового буфера и буфера АЦП каналов приема. Б исходном

1

15

20

25

30

состоянии выходы 41-1 нгходятся в сос-Ш ния на входе элемента ИЛИ-НЕ 70-1

1ТОЯНИИ О,

Кроме того, в счетчик 67 записывается код, который определяет время фиксации аналоговой информации на эле менте аналоговой памяти. Такая процедура необходима в случае работы устройства с максимальной частотой дискретизации.

Например, при периоде следования сигналов частоты дискретизации Т „

|т(

10 мкс время фиксации может быть равно Тф 7 мкс. Остальное время можно использовать для формирования алертурной задержки включения АЦП, обусловленной наличием переходных процессов в элементах аналоговой па- мяти. На фиг. 4 схема формирования апертурной задержки не показана.

После формирования на входах элементов И 69-ls...69-i сигнала ЯЗХ 1 с первого разряда сдвигового регистра 68 выдается Г на вход элемента И 69-1 и далее на выходы 41-1 (1 - это активный уровень, по которому аналоговая информация начинает фиксироваться в зиенете памяти (фиг.1)).

Одновременно на вход элемента И 75 поступает частота дискретизация,При наличии сигнала включения на другом входе элемента И 75 триггер 66 устанавливается в 1 и переводит первый счетчик 67 в режим счета. Появление сигнала на выходе переноса 67 устанавливает триггер 66 и счетчик 67 в исходное состояние. Одновременно этот сигнал поступает на элемент ИЛИ 74 и сдвигает I с первого разряда на второй, тем самым отключает первый элемент памяти и под- 50 ключает второй канал 12. После снятия 1 с первого разряда сдвигового регистра 68 осуществляется установка через элемент ИЛИ-НЕ /0-1 группы триггера 71-1 в состояние О. При этом на его обратном выходе формируется сигнал управления (сигнал запуска), по которому первое АЦП

35

40

сигнала конца преобразования счетн триггер 71-1 устанавливается в исх ное состояние.

При этом на его прямом выходе ф мируется положительный фронт, по к торому изменяется на 1. содержимо второго счетчика 73, т.е. осуществляется изменение адреса мультипле сора 19 группы.

Аналогично происходит формирова ние сигналов управления на других выходах сдвигового регистра 68,три геров 71-i.

После формирования 1 на после нем i-ом разряде сдвигового регист ра 68 сигнал частоты дискретизации вновь перепишет ее на первый разря при этом счетчик 73 установится в состояние О (цепи установки на фиг.4 не показаны) и весь процес повторяется сначала. Прекращение боты блока 9-1 осуществляется сня ем сигнала с входа 40-1 элемента И Этот сигнал блокирует прохождение частоты дискретизации. Установка блока 9-1 в исходное состояние осу ществляется по входу 26,

Блок 1 (фиг.6) предназначен дл связи устройства с ЭВМ, Связь осу ществляется по магистрали.

45

Взаимодействие ЭВМ с блоком 1 входящими в его состав регистрами счетчиками) и триггером 2 (см.фиг осуществляется через дешифратор 8 адреса.

По команде Вывод 1 (ОИТ) на ши 25 управления формируется сигнал Запись, на шине 24 данные, на не 23 код адреса регистра (счетчи триггера 2), к которому в данный мент идет обращение. Дешифратор 83 адреса анализиру код адреса на шине 23 и в случае 5Ј ращения ЭВМ к блоку 1 формирует н ном из своих выходов сигнал, опре ляющий адрес регистра (счетчика, гера 2), по которому осуществляе

153636916

подключается к элементу памяти (см. фиг.1) канала 12. Сигнал с прямого выхода счетного триггера 71-1 поступает через элемент ИЛИ-НЕ 72 на счетный вход второго счетчика 73, подготавливая его к инкременту содержимого, т.е. адреса мультиплексоров 19 группы (см.фиг,1). После формирова5

0

5

30

50

35

40

сигнала конца преобразования счетный триггер 71-1 устанавливается в исходное состояние.

При этом на его прямом выходе формируется положительный фронт, по которому изменяется на 1. содержимое второго счетчика 73, т.е. осуществляется изменение адреса мультиплексора 19 группы.

Аналогично происходит формирование сигналов управления на других выходах сдвигового регистра 68,триггеров 71-i.

После формирования 1 на последнем i-ом разряде сдвигового регистра 68 сигнал частоты дискретизации вновь перепишет ее на первый разряд, при этом счетчик 73 установится в состояние О (цепи установки на фиг.4 не показаны) и весь процесс повторяется сначала. Прекращение работы блока 9-1 осуществляется снятием сигнала с входа 40-1 элемента И 75 . Этот сигнал блокирует прохождение частоты дискретизации. Установка блока 9-1 в исходное состояние осуществляется по входу 26,

Блок 1 (фиг.6) предназначен для связи устройства с ЭВМ, Связь осуществляется по магистрали.

Взаимодействие ЭВМ с блоком 1 (с входящими в его состав регистрами, счетчиками) и триггером 2 (см.фиг.1) осуществляется через дешифратор 83 адреса.

По команде Вывод 1 (ОИТ) на шине 25 управления формируется сигнал Запись, на шине 24 данные, на шине 23 код адреса регистра (счетчика, триггера 2), к которому в данный момент идет обращение. Дешифратор 83 адреса анализирует код адреса на шине 23 и в случае об- ращения ЭВМ к блоку 1 формирует на одном из своих выходов сигнал, определяющий адрес регистра (счетчика, триггера 2), по которому осуществляется

запись информации с шины 24 в выбранный регистр (триггер 2) .

Дешифратор 83 адреса формирует следующие адреса: ФА1,...,ФА4, ФАЛ .. ., ФА41, ФАЗ,...,ФАЛ .

Принцип формирования адресов следующий.

Пусть для адресации блока J, его регистров, счетчиков, используется младший байт адреса разряды (АО... А7). Тогда для обеспечения адресации заданного количества регистров, счетчиков разряды АО,... , А7 могут быть распределены следующим образом. Раз- ряды Аб, А7 определяют физический адрес блока , разряды А1,.. ., А5 определяют адрес регистра, счетчика, разряд определяет начало работы и устанавливает триггер 2 в J.

Распределение адресов, значение кода адреса на, шине 23 при обращении ЭВМ к блоку J приведено в таблице, при этом физический адрес блока 3 принят равным 0, т.е. разряды , .

Как видно из фиг.6, регистры 77, 78, счетчики 79,80, элемент 81 сравнения, элементы И 82 конструктивно объединены в узел 76-1 управления, который формирует текущий адрес на шине 23. По этому адресу канал 12-1

е

иis

20

30

25

записывает данные преобразования в блок 10 памяти.

Аналогичную функцию выполняет узел 76-N управления.

Пусть зона памяти, с которой работает канал 12-1, будет зона 1, а зона памяти, с которой работает блок 12-N,- зона N.

(О Процесс заполнения зоны 1 памяти данными преобразования контролируем ется элементом 81 сравнения, который осуществляет сравнение текущего адреса (входы Б) с конечным адресом (входы А) зоны. Сравнение осуществляется при подаче на управляющий вход элемента сравнения сигнала . Если А и В не равны, между собой, на выходе элемента сравнения присутствует О, который поступает через элемент НЕ 86 группы на вход с элемента И 93 группы и разрешает прохождение сигнала включения на входы 40-1 блоков 9-1, 12-1. Блоки 9-1, 12-1 начинают работать. После появления на .входе -38-J сигнала разрешения адреса открываются элементы И 82 группы и текущий адрес зоны 1 с выходов счетчиков 79, 80 поступает на шину 23 адреса. После записи данных преобразования в зону 1 сигнал 38-1 снимается и по его заднему (отрицательному) фронту осуществляется инкрементирование содер35 жимого счетчика 79, 80 на +1.

Когда содержимое счетчиков 79,80 станет равным содержимому регистров 77, 78,сработает элемент 81 сравнения. На его выходе появится 1|:, которая

40 поступит на один из входов А элемента сравнения 84 и через элемент НЕ 86 группы на вход элемента И 93 группы, запрещая прохождение сигнала включения на выход 40-1, т,е про45 изойдет останов работы блоков 9-1, 12-1.

Аналогично работает узел 76-N управления. Только I1 с выхода элемента 81 сравнения поступает через соот-

50 ветствующий элемент НЕ 86 группы на вход элемента И 93 группы, разрешая прохождение сигнала включения на вход 40-N. После срабатывания элемента 81 сравнения узла 76-N управления сигнал

55 разрешения включения с входа 40-N снимается аналогично.

После заполнения всех зон памяти блока 10 (зона 1, зона N) сработает

элемент 84 сравнения. Т ря этом произойдет сравнение входов А и В. Входы В элемента сравнения подсоединены К 1, на управляющий вход подан сигнал .

При срабатывании элемента 84 сравнения на его обратном выходе появится О, т,е„ сформируется сигнал Конец работы. Этот сигнал поступает I на один из входов элемента MJ1F 85, на другой вход которого поступает сигнал Сброс. На выходе элемента ИЛИ 85 сформируется сигнал Сброс, Конец работы1 , который установит уст ройство в исходное состояние. После снятия ЭВМ сигнала TI3X входы , и А и В элемента сравнения 84 изменят свое состояние9 что приведет к изменению состояния выхода этого алемен- та сравнения с О на 1, т.е. сигнал Конец работы снимется.

Регистры 87-92 являются регистрами, управляющими работой блоков устройства.

Структура регистра 88 улраззления следующая два разряда задают режим работы блока 5 (входы 313 50-3), остальные шесть разрядов могут быть использованы для формирования сигналов включения групп блоков 9-1„ 12-1, 9-N9 12-N. Активное состояние выходов регистра обеспечивается установкой в М .

Структура регистра 139 адреса обеспечивает подключение 256 аналоговых сигналов (2 ) . Подкачаются выходы регистра 89 к адресным входам мультиплексоров 34 (входы 39-1, 39--N). На фиг. 6 -показано, что число раз- рядов во входах 39-1, 39-N равно 4. Это обеспечивает подключение 16 аналоговых ; сигналов к входам мультиплексора каналов 12-1 12-N.

При необходимости подключения (коммутации) большего числа аналоговых входов выходы регистра 89 распаиваются непосредственно на адресных входах аналогового коммутатора 14 блоков 12-1, 12-N (на фиг.1 не по- казано).

Структура регистров 90-92s 87 формирования и выбора частоты дискретизации определяется построением блока 6 .,

Пусть блок 6 содержит четыре -разрядных последовательно соединенных двоично-десятичных счетчика. Содержимое двоично-десятичных счетчиков равно О

5

0

0

5

Тогда при подаче на вход 27 сигналов генераторов 11 тактовых импульсов с частотой следования 1 МГц на выходах счетчиков получают следующую последовательность частот дискретизации.На четырех выходах первого счетчика сформируются частоты 500, 250, 125, 100 кГц, на четырех выходах второго счетчика - 50, 25, 12,5, 10 кГц, на выходах третьего счетчика - 5,2,5, 1,25,1 кГц, на выходах четвертого счетчика - 500, 250, 125, 100 Гц.

Выбор нужной частоты дискретизации осуществляется регистрами 92 и 87.

Регистры 90, 91 формируют частоты дискретизации, т.е. изменяют сетку частот за счет изменения содержимого двоично-десятичных счетчиков блока 6 .

Рассчитаем максимальное количество зон памяти, с которым может работать блока 1, каналы 12-1, 12-N.

Регистры 87-92 являются общими для устройства. Их количество равно шести.

Регистры я счетчики 77-80 управляют работой только одного блока 12-1. Их число равно четырем. При увеличении количества работающих- , блоков 9-N, 12-N число регистров (счетчиков) должно быть увеличено.

Так как адресация к регистрам, счетчикам 77-80, 87-92 осуществляется разрядами адреса АЗ,...,А5, то ЭВМ может адресоваться к 32 регистрам, счетчикам. Тогда общее число регистров, счетчиков, управляющих работой блока 10, J2-, 12-N, равно 32- -6 26. Следовательно, адресное поле блока J может обеспечить одновременную работу каналов 12-К,

1 32-6

б,

где

N -- максимальное число каналов 12-N.

Ограничительным условием для увеличения числа работающих групп каналов 12-1, 12--N является требование к скорости работы аналогового буфера и буфера АЦП блока преобразования данных. Эти буферы должны работать со скоростью, равной частоте дискретизации. Для обеспечения этого требования необходимо, чтобы блок 10 успевал за время, равное периоду частоты дискретизации, записать в

21

память данные преобразования от N групп каналов 12-1, 12-N.

Пусть блок 10 имеет время записи Т 2 мкс, период частоты дискретизации Тд 10 мкс, тогда N 5, где N - допустимое число каналов 12-1, 12-N, при котором устройство обеспечивает работу с заданным быстродействием.

Другим фактором, влияющим на скорость работы устройства, является требование к выбору объема аналогового буфера и буфера АЦП.

Объем буферов выбирается следующим образом.

Согласно фиг.5 время обработки одной порции (выборки) аналоговой информации, зафиксированной в ячейке аналогового буфера, равно

Т т т + т 1 ф L ач.п L 1 son

(О

где Т - время обработки одной порции аналоговой информации Тф - время фиксации в ячейке аналогового буфера-,

Тацп время записи данных преобразования от N каналов 12-J, 12-N.

Пусть Т ф Т А 10 мкс, Т эап N -Т ian , если N 5, Т 2 мкс, то Т 10 мкс. Для построения буфера выбираем АЦП среднего быстродействия с Т аи, п 30 мкс, тогда Т 50 мкс. Количество ячеек в буферах определяется по формуле (2.)

Т + Т

А

1

(2)

где Т + ТА

Тобщ - общее время обработки одной порции аналоговой информации,

- ЈПри таком количестве ячеек в аналоговом буфере и буфере АЦП устройство обеспечивает обработку знало- .говой информации со скоростью, равной 1000 кГц (при ТА 10 мкс).

Таким образом, предлагаемое уст- . ройство позволяет осуществлять обработку аналоговых сигналов с частотой дискретизации, не зависящей от времени преобразования АЦП.

Обеспечение заданного быстродействия может быть получено при исполь6922

зовании в устройстве АЦП с любым временем преобразования.

Кроме того, в устройстве обеспечена возможность подключения и параллельной работы N блоков преобразования данных, запускающихся не только от внутреннего источника формирования частоты дискретизации, но и от различных внешних источников, что важно при работе устройства в реальных условиях.

Формула изобретения

15

блок формирования частот дискретизации, блок памяти, генератор тактовых импульсов, каналы приема, каждый из которых содержит усилители, входы которых являются аналоговыми входами

устройства, и аналого-цифровые преобразователи, адресные, информационные и управляющие входы блока сопряжения соединены соответственно с адресными, информационными и управляющими шинами для подключения к ЭВМ, выходы блока памяти соединены с информационной шиной для подключения к ЭВМ, первый выход блока сопряжения соединен с первым входом первого элемента ИЛИ, выход которого соединен с установочным входом блока формирования частот дискретизации, тактовый вход которого соединен с выходом генератора тактовых импульсов,отличающееся

тем, что, с целью повышения быстродействия устройства и расширения области применения за счет установления частоты дискретизации от внешних источников, в него введены блок выбора

источника дискретизации, второй элемент ИЛИ и блок опроса канала, а в каждый канал приема - мультиплексор, элемент И, элементы памяти, группа ,мультиплексоров, третий элемент ИЛИ,

первая, вторая и третья группы элементов И, причем в каждом канале выходы усилителей соединены с информационными входами мультиплексора, выход которого соединен с инфррмаци-

онными входами элементов памяти, выходы которых соединены с информационными входами соответствующих аналого- цифровых преобразователей, выходы готовности которых соединены с входами

23153636924

и входами первой роса кзнала, а выходы первой груптретъего элемента ИЛИ Группы элементов И первой группы, информационные выходы аналого-цифровых преобразователей соединены с информационными входами соответствующих нуль- иплексоров группы, выходы которых соединены с входами первой группы элементов И второй группы, входы второй группы элементов И первой и второй ю Групп соединены с выходом элемента fi, выход третьего элемента ИЛИ соеди- Иен с управляющими входами мультиплексоров группы и выходы первой группы

лы - с входами запуска блоков опроса канала и входами первой труппы элементов И третьей группы, первыми входами элементов И, управляющими входами мультиплексора, выходы второй группы блока сопряжения подключены к адресной шине для подключения к ЭВМ, тактовые входы блока сопряжения соединены с выходами первой группы блока управления, выходы элементов И первой группы соединены с входами конца преобразования соот

элемелтов И третьей группы соединены IG ветствующего блока опроса канала,

с входами запуска соответствующих ака jnoro-цифровых преобразователей,, а выводы второй группы - с управляющими входами соответствующих элементов па- Мяти, первый выход блока сопряжения соединен с входами устаьовкк первого и второго триггеров,второй выход блока сопряжения соединен с тактовь-м вхо дом первого триггера, инверсный выход которого соединен с тактовым входом второго триггера, а прямой выход - с вторым входом первого элемента РЛИ, выход которого соединен с установочными входами блока выбора источника дискретизации и блоков опроса канала, 1 информационные входы блока выбора источника дискретизации являются входами задания частоты дискретизации устройства, вход запуска блока выбора источника дискретизации является входом запуска устройства, третий выхоп, блока сопряжения соед ..ен с управляющим входом блока выбора источника дискретизации, а четвертый выход - с входом разрешения блока выбора источника дискретизации, первый которого соединен с входом запуска б пока формирования частот дискретизацииs управляющие входы которого соединены с выходами четвертой группы бпока сопряжения, второй выход блока пыбора источника дискретизации соединен с входом запуска блока управления, а третий выход - с первые входом второго элемента ИЛИ, выход которого соединен с первыми тактовыми входами блоков опроса канала, а второй вход - с выходом блока формирования частот дискретизации, вторые тактовые входы блоков опроса канала и тактовый вход блока управления соединены с выходом генератора тактовых импульсов,, пятый выход блока сопряжения соединен с входами разрешения блоков оп

лы - с входами запуска блоков опроса канала и входами первой труппы элементов И третьей группы, первыми входами элементов И, управляющими входами мультиплексора, выходы второй группы блока сопряжения подключены к адресной шине для подключения к ЭВМ, тактовые входы блока сопряжения соединены с выходами первой группы блока управления, выходы элементов И первой группы соединены с входами конца преобразования соотвыходы первой, второй и третьей групп блока опроса канала соединены с входами второйf третьей и четвертой групп элементов И третьей группы,

выходы третьей группы блока опроса канала соединены с адресными входами мультиплексоров группы, выходы второй группы блока управления соединены с вторым входом соответствующего элемента И, выходы третьих элементов И соединены с входами запросов блока управления, выход которого и управляющий вход блока памяти подключены к управляющей шине

для подключения к ЭВМ, информационные входы которого и выходы элементов И второй группы подключены к информационной шине для подключения к ЭВМ, адресные входы блока памяти

соединены с адресной шиной для подключения к ЭВМ, выход второго триггера соединен с управляющей шиной для под-- ключения к ЭВМ, выходы третьей группы блока сопряжения соединены с адресными входами соответствующих мультиплексоров .

2, Устройство по п. отличающееся тем, что блок выбора источника дискретизации содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, четыре элемента ИЛИ, элемент ИЛИ-НЕ, элемент И, два триггера, первые входы первого и второго элементов ИЛИ и входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ являются информациоиными входами блока, один из входов элемента ИСКЛЮЧАЮЩЕЕ ИЛИ является вторым входом первого элемента ИЛИ, выход которого соединен с первым входом элемента И, выход которо-

го является вторым выходом блока, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с вторым входом второго элемента ИДИ, выход которого соединен с тактовым входом первого триггера,

прямор выход которого соединен с вторым входом элемента И, а инверсный выход - с первым входом третьего элег мента ИЛИ, выход которого является третьим выходом блока, вхрд установки в О первого триггера и вход установки в J второго триггера являются входом установки блока, БЫХ.ОД второго триггера соединен с вторыми входами третьего элемента ИЛИ и элемента ИЛИ-НЕ, выход которого является первым выходом блока, первые входы элемента ИЛИ-НЕ, и четвертого элемента ИЛИ являются входом запуска блока, второй вход четвертого элемента ИЛИ является управляющим входом блока, выход четвертого элемента ИЛИ соединен с тактовым входом второ-

то триггера, информационные входы пер-20 новки в О второго счетчика являются

вого и второго триггеров подключены соответственно к шинам логической единицы и логического нуля.

входом блока, второй вход элемента И - входом запуска блока, выход элемента И соединен с тактовым входом триггера, выход которого соеди- нен с входом записи первого счетчика, установочные входы которого подключены к шинам логической единицы и логического нуля, выход переполнения

которого подключен к вхрду установки в О триггера и первому входу элемента ИЛИ, выход которого соединен с входом сдвига сдвигового регистра, выходы которого соединены, с входами

5 первой группы, элементов И группы и элементов ИЛИ-НЕ группы, вход выбора режима сдвигового регистра, второй вход элемента ИЛИ, входы установки в 3 счетных триггеров и вход уста

установочным входом блока, вход записи сдвигового регистра и тактовый вход второго счетчика соединены с одним из входов сдвигового регистра, входы второй группы элементов И группы являются входом разрешения блока, а выходы - выходами первой группы блока, входы второй группы элементов ИЛИ-НЕ группы являются входами конца преобразования блока, а выходы соединены с тактовыми входами соответствующих счетных триггеров, прямые выходы которых соединены с входами элемента ИЛИ-НЕ, выход которого соединен со счетным входом второго счетчи

третьей группы блока, инверсные выходы счетных триггеров являются выходами второй группы блока, установочный вход второго счетчика подключен к шине логического нуля, установочный вход сдвигового регистра - к шине логической единицы, а установочные

входы группы ля.

- к шине логического ну

Первой группы второго элемента сравнения,выходы первого и второго счетчиков соединены с входами первой группы . элементов И второй группы и входами второй группы второго элемента сравнения, информационные входы регисров и установочные входы счетчиков являются информационными входами блока, счетные входы первого и второго счет- чиков и входы второй группы элемен- ,тов И второй .группы являются тактовыми входами блока, управляющие входы дешифратора, первого и второго элементов сравнения и первый вход эле- мента ИЛИ являются управляющими входами блока, один из управляющих входов блока является цятым выходом блока, информационные входы, дешифратора являются адресными входами бло- , ка, выходы группы которого соединены с входами записи соответствующих регистров и счетчиков, выход дешифратора является вторым выходом блока , выходы второго элемента сравнения каждого узла управления соединены с входами элементов НЕ и первого эле- . мента сравнения, входы второй группы которого соединены с шиной логической единицы, выходы элементов НЕ соединены с входами первой группы элементов. И первой группы, выход первого элемента сравнения соединен с вторым входом элемента ИЛИ, выход которого является первым выходом блока, выходы группы первого регистра соединены с входами второй группы элементов И первой группы, выходы которых являются выходами первой группы блока, первый и второй выходы первого регистра являются соответственно третьим и чет-: вертым выходами блока, выходы второго регистра являются выходами третьей группы блока, выходы третьего, четвертого, пятого и шестого регистров являются выходами четвертой группы блок а.

Фиг.1

( Начало )

Устанобкаблока / 5 исходное состояние

Загрузка регистров элемента 76-1

Загрузка pezucmpoo лемента 76-N

(Счетчикоб) (CvemwKoS)

Загрузка регистра вв

м

Загрузка регистра 89

Г 3агрузка регистра 90

ГЗагрузка регистра 9i

Загрузка регистра 92

mm

Загрузка регистра 87

Фаг.7

Установка триггера 2.

Г АКК ---ин(р. | ОИТ-1Е

юздейс- ист

t

Адреса оаоны

т

Установка Компаратора 81(6ухдда) t: oJ Установка компаратора аЦоыхода} 6.0

выдача си&на- ig,, Конец ра- . . устроистбо

АКК--аккумулятор микро-ЭВМ

Загрузка регистров элемента 76-1

РШрузка младше- о байта конечного адреса Я& 77

Загрузка старшего байта конечно- J.O адреса (R& 78)

Загрузка младшего байта начального адреса (СЛ 9)

Загрузка старшего байта началь-. JJQBQ адреса (СТ80}

Загрузка регистров ж мен т а 76-М

. ОИТОв

.инф ОИТОА

QHTOC

Загрузка младшего байта конеи- ЈOsoadpeca{RB77)

Заврузка старшего Sou та конечно- W адреса (R& 78}

Нагрузка младшего байта начального адреса (СТ 79)

зка старшего байта начало-. ново адреса(CT8Q)

Запись инфор- Змации озону памяти

Фиг.8

Редактор М. Недолуженко

Составитель И, Карпова Техред к. Ходанич

Выдача текущего адреса на шину 2.3

Нет

Инквементна+1 содержимого счетчиков 79,80

Корректор М.Шароши

| Многоканальное устройство для регистрации информации | 1984 |

|

SU1236452A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальная система для анализа формы и регистрации аналоговых процессов | 1983 |

|

SU1149242A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-01-15—Публикация

1988-04-25—Подача