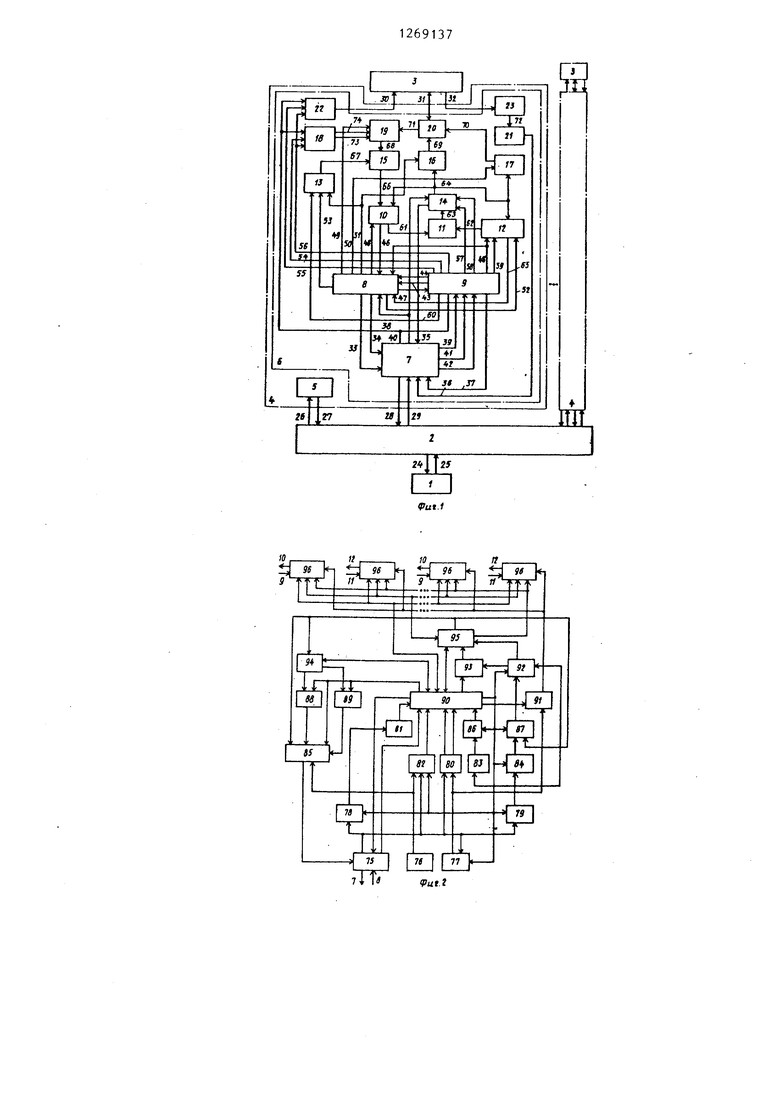

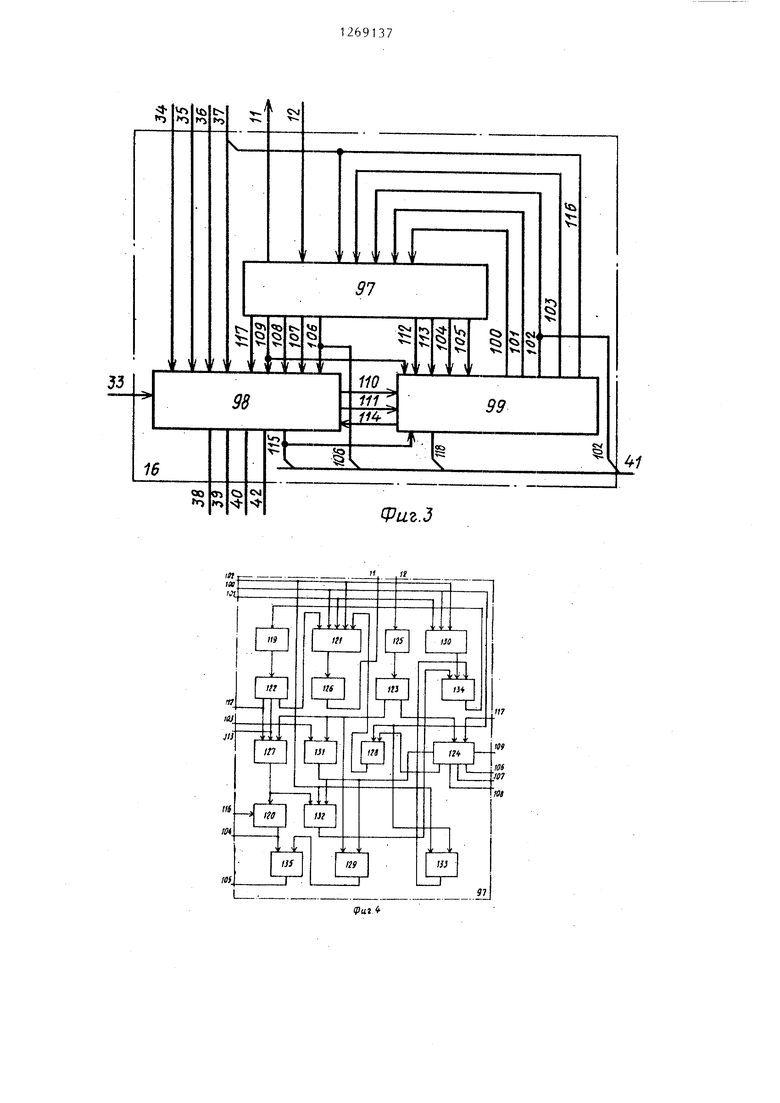

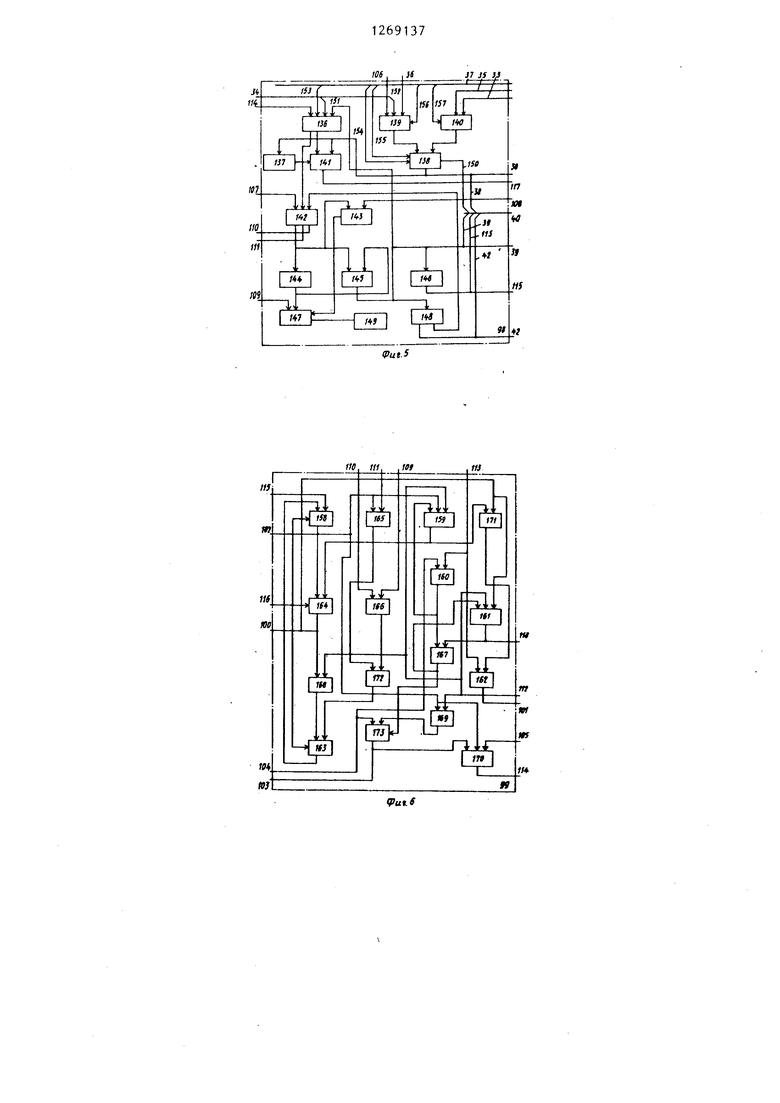

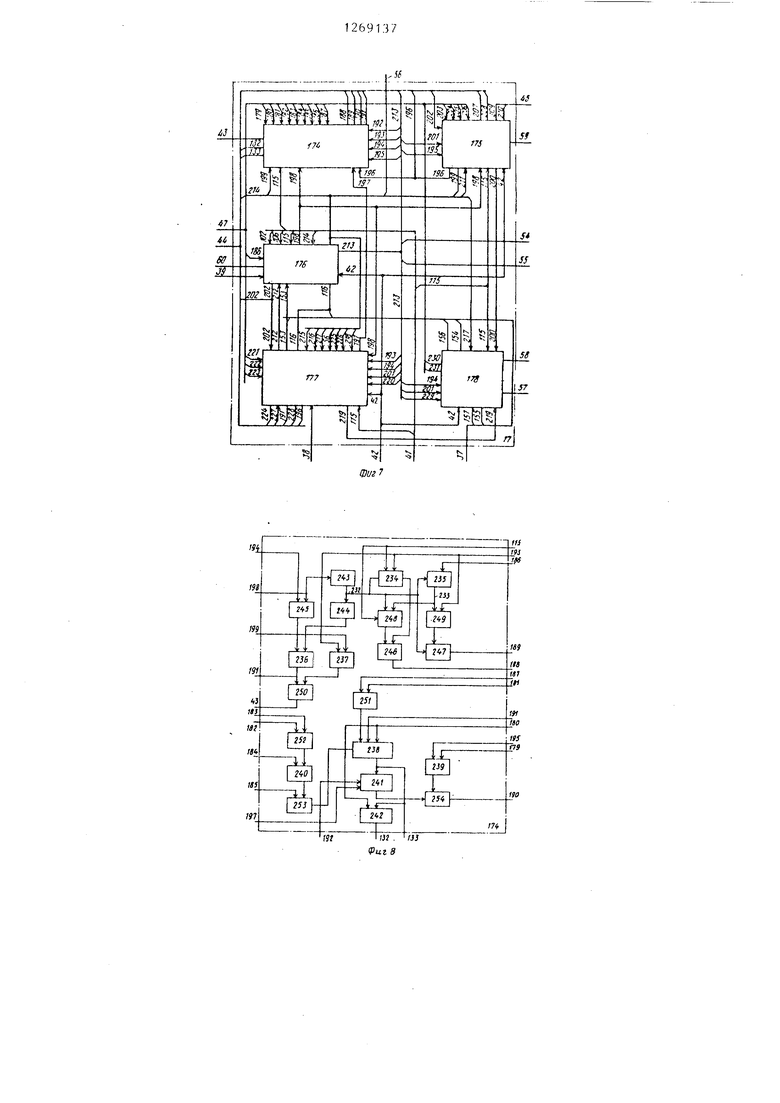

. Изобретение относится к автоматике и вычислительной технике, а именно к средствам контроля и диагностирования неисправностей цифровых компонентов (ячеек, блоков, устройств) и может быть использовано на предпри ятиях, разрабатывающих или выпускающих цифровую аппаратуру, а также в организациях, эксплуатирующих аппаратуру цифровой техники. Цель изобретения - повышение коэффициента использования оборудования и повьичение полноты контроля изделий , На фиг. 1 приведена блок-схема системы; на фиг. 2 - схема группового двунаправленного коммутатора; на фиг. 3 - схема блока приема-передачи; на фиг. 4 - схема узла приемапередачи; на фиг. 5 - схема узла регистра входного и дещифратора указаний J на фиг. 6 - схема узла управления приемом-передачей; на фиг. 7 схема блока формирования сигналов обмена; на фиг. 8 - схема узла коммутатора управляющих сигналов на фиг. 9-схема узла распределителя син хросигналов, на фиг. 10 - схема узла дешифратора признаков, на фиг. 11,узел задания временных интервалов на фиг. 12 - схема узла дешифратора управляющих сигналов; на фиг. 13 схема блока микропрограммного управления; на фиг. 14 - схема узла оперативной памяти команд; на фиг. 15 схема узла микропрограммного управления на фиг. 16 - схема узла упра ления адресами оперативной памяти тестов. Многоканальная система для контроля и диагностики цифровых блоков (фиг, 1) состоит из управляющей вычислительной машины 1, группового двунаправленного ком утатора 2, кон ролируемого объекта 3, одного или нескольких контрольно-наладочных постов 4, каждый из которых имеет диалоговое устройство 5 и канал 6, Канал 6 содержит блок 7 приема-пере дачи, блок 8 микропрограммного упра ления, блок 9 формирования сигнала обмена, узел 10 маскирования,, элемент ИЛИ 11, память 12 тестов, счет чик 13, буферный регистр, 14, второй коммутатор 15, регистр 16 тестов, р гистр 17 разделения, блок 18 управл емых источников опорного напряже-ния, блок 19 сравнения, двунаправленньпЧ коммутатор 20, шифратор 21, блок 22 управляемых источников напряжения питания, первый коммутатор 23, линии 24-74 связи. Групповой двунаправленный коммутатор 2 (фиг. 2) содержит интерфейсные усилители 75, генератор 76 адреса, счетчик 77 адреса, регистр 78 команд, регистр 79 вывода, узел 80 сравнения адреса, дешифратор 81 команд, схему 82 сравнения, дещифратор 83 указаний, регистр 84 адреса буферной памяти, коммутатор 85 шин данных к ЭВМ, регистр 86 указаний, буферную память 87, регистр 88 байта уточненного состояния, регистр 89 байта состояния, узел 90 управления, дишефратор 91 адреса, коммутатор 92 данных в регистр приема-передачи, формирователь 93 слова управления, дешифратор 94 ответа, регистр 95 приема-передачи и узлы 96 связи. Блок 7 приема-передачи (фиг. 3) содержит узел 97 приема-передачи, узел 98 регистра выходного и дешифратора указаний, узел 99 управления приемом и передачей и линии 100-118 связи. Узел 97 приема-передачи (фиг. 4) содержит счетчик 119 числа битов, счетчик 120, шифратор 121, дешифратор 122 счетчика битов, дешифратор 123, регистр 124 приема-передачи, усилитель 125 приема, усилитель 126 передачи, триггер 127 Начало слова, триггер 128 контрольного разряда, триггер 129 Нечет, схемы И 130133, схемы ИЛИ 135. Узел 98 регистра входного(фиг.5) содержит регистр 136 синхронизирующих тактов, регистр 137 индентификатора внимания, регистр 138 входного, мультиплексоры 139-141, формирователь 142 управляющих сигналов, триггер 143, триггер 144 Команда триггер 145 Прием-указание триггер 146 Указание-считывание триггер 147, Система доступна, триггер 148 Указание запись, индикатор 149 системы доступа и линии 150-157 связи. Узел 99 управления приемом-передачей (фиг. 6) содержит триггеры 158163, регистр 164 синхронизирующих тактов, элементы И 165-170, элементы ШШ 171-173. Блок 9 формирования сигналов обмена (фиг. 7) содержит коммутатор 174 управляющих сигналов, распреде3 1

литель 175 синхросигналов, узел 176 задания нременных интервалов, дешифратор 177 признаков, дешифратор 178 управляющих сигналов, линии 179231связи. Узел 174 (фиг, 8) содержит линии

232и 233 связи, элементы И 234-242, одновибраторы 243 и.244, триггеры 245-247, элементы ИЛИ 248-254.

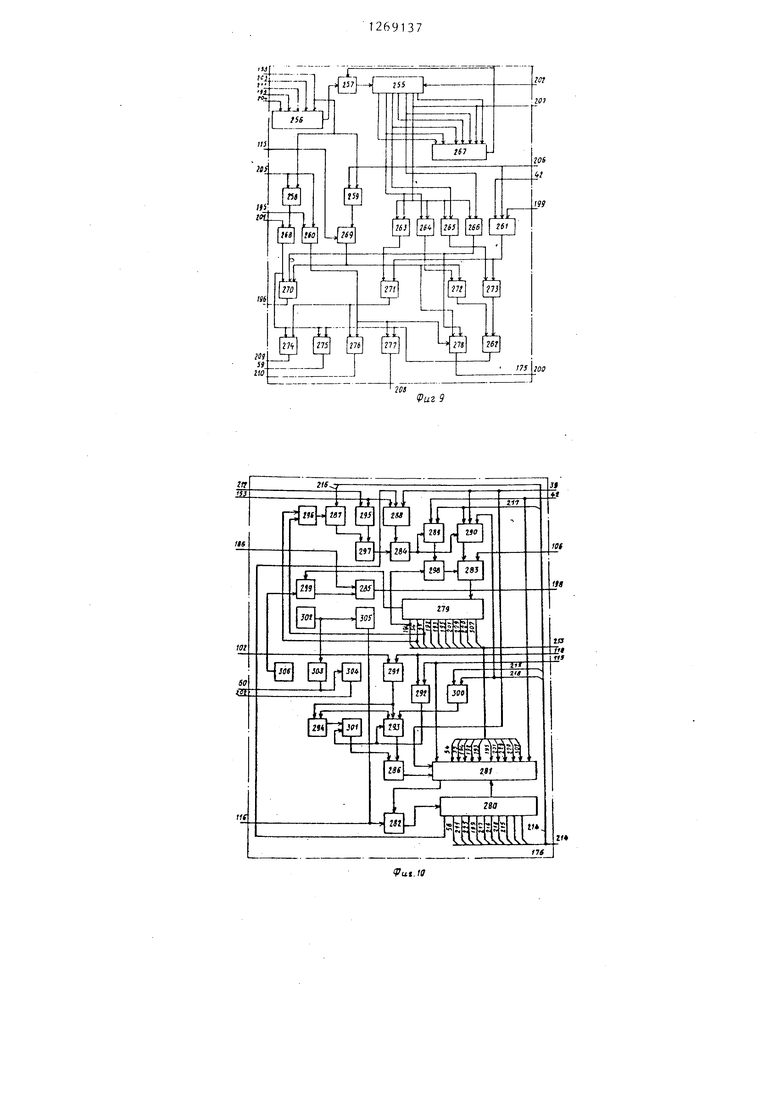

Узел 175 (фиг. 9) содержит регист 255 синхронизирующих тактов, элементы ИЛИ 256-262, триггеры 263-266, элементы И 267-278.

Узел 176 (фиг. 10) содержит дешифратор 279 признаков, дешифратор 280 микроопераций, формирователь 281 условий перехода, регистр 282 микроопераций, регистр 283 признаков, триггеры 284-286, элементы И 287295., элементы ИЛИ 296-301, генератор 302, удвоитель 303 частоты, делители 304 и 305 частоты, кнопку 306 пуска, линию 307 связи.

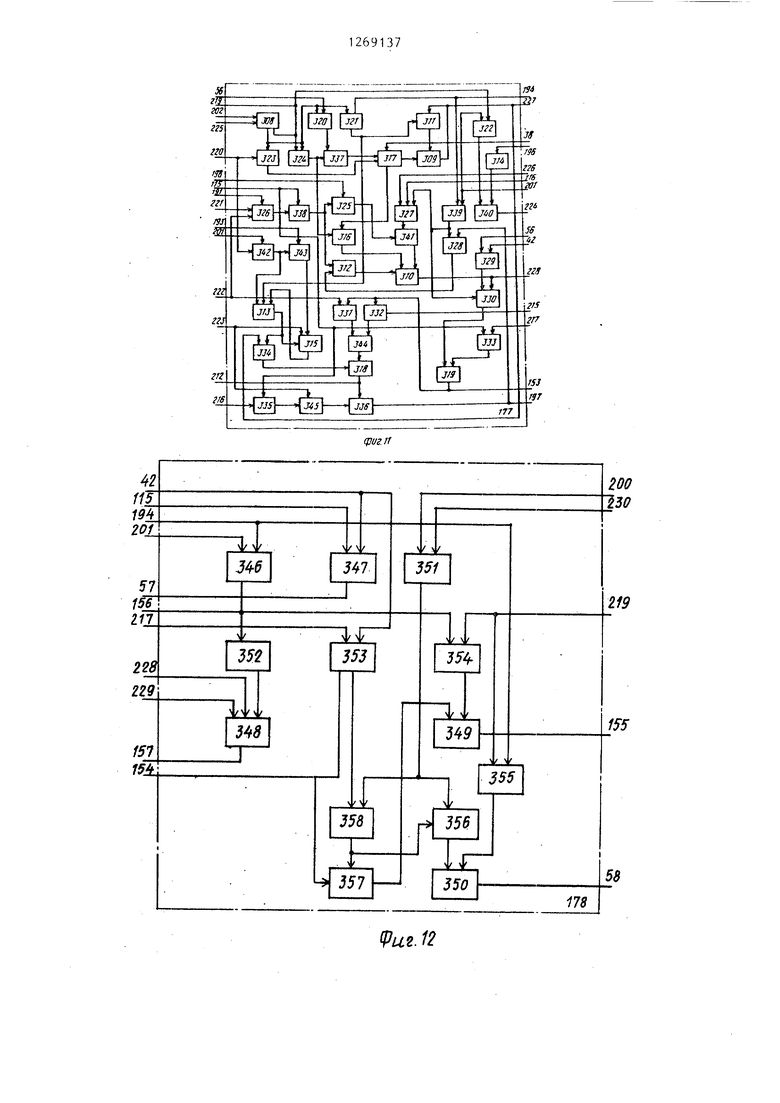

Узел 177 ( фиг. 11) содержит схемы 308-310 сравнения, счетчики 311-313, одновибраторы 314 и 315, регистры 316 и 317, триггеры 318 и 319, элементы И 320-336, элементы ИЛИ 337-345.

Узел 178 (фиг. 12) содержит злементы ИЛИ 346-350, элементы И 351-. 357, одновибратор 358,

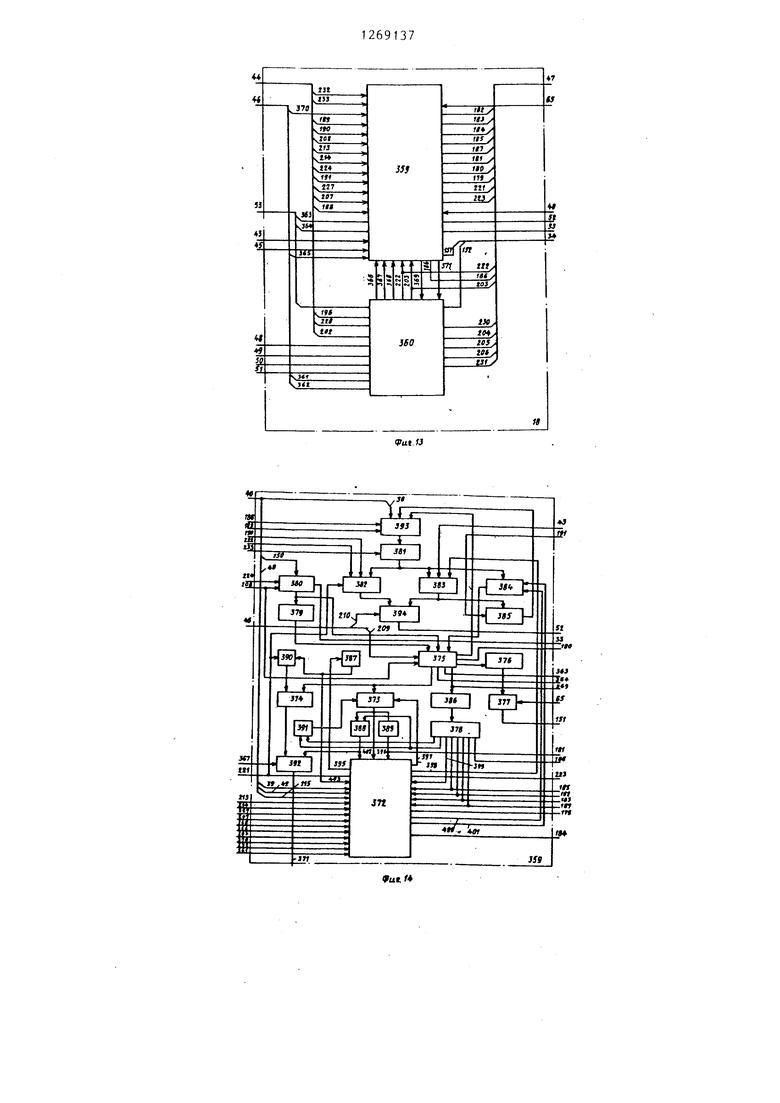

Блок 8 микропрограммного управления (фиг, 13) содержит узел 359 управляющей памяти и формирования ад ресов, узел 360 микропрограммного управления, связи 361-371, Узел 359 (фиг, 14) содержит формирователь ; 372 адресов, счетчик 373 циклов программ, счетчик 374 циклов импульсной последовательности, оперативную память 375 команд, .формироват ель 376 четности, формирователь 377 сигнала ошибки, дешифратор 378 кода операций генератор 379 четности оперативной памяти команд, регистр 380 формирования слов оперативной памяти команд буферный регистр 381 адреса, первый и второй регистры 382 и 383 адреса оперативной памяти тестов, регистр 384 адреса команд, регистр .385 переадресации, регистр 386 кода операции триггер 387 циклов импульсной последовательности, триггер 388 групповой операции, триггер 389 конца циклов, элемент И 390, элемент ИЛИ 391, мультиплексор 392 признаков, мультиплексоры 393 и 394, линии 395-403 связи.

374

Узел 360 (фиг. 15) содержит формирователь 404 сигналов управления, постоянную память 405, регистр 406 микрокоманд, преобразователь 407 кода длительности, дешифратор 408 . микрокоманд,элемент И 409, элемент ИЛИ 410, шифратор 411,

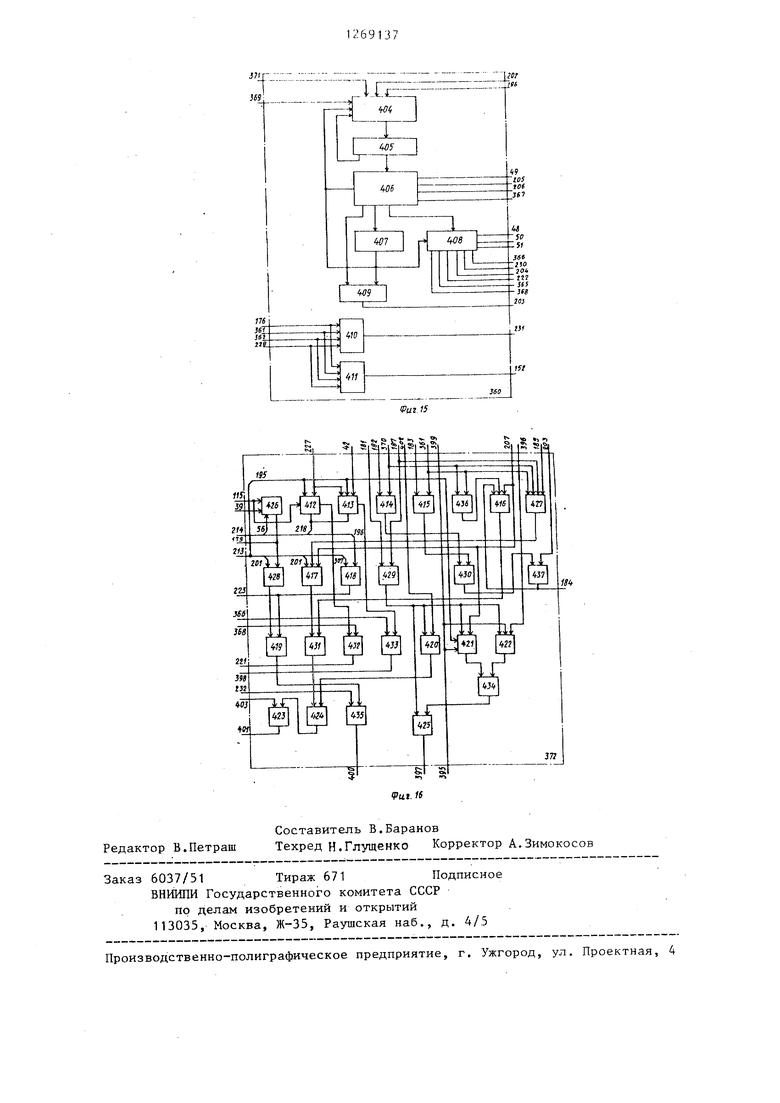

Формирователь 372 (фиг. 16) содержит элементы И 412-426, элементы ИЛИ 427-436, триггер 437 условного перехода.

Многоканальная система работает следующим образом.

Система работает под управлением программы, хранящейся в памяти управляющей ЭВМ 1, Тестовая информация для проверки контролируемых изделий находится в памяти машины.

Обмен информацией между управляющей ЭВМ 1 и устройствами 5 и 6, входящими в состав каждого контрольно-наладочного поста 4, осуществляется через групповой двунаправленный коммутатор 2,

Система связи группового двунаправленного коммутатора 2 с диалоговым устройством 5 и каналом 6, обеспечивает единый принцип обмена инфор-. мацией 1 для обоих устройств, т,е, единый формат данных и единый способ управления. Обмен информацией группового двунаправленного коммутатора 2 с диалоговым устройством и каналом 6 осуществляется в последовательном коде с помощью четырнадцати разрядных слов: управления (СУ) для передачи указаний из группового двунаправленного коммутатора 2, данных (СД) - для передачи данных, из коммутатора 2 в диалоговое устройствво 5 и канал 6 и для обратной передачи данных из этих устройств в коммутатор 2, -состояние (СС) - для передачи в коммутатор 2 информации о состоянии диалогового устройства 5 и канала 6,

Работу системы можно разделить на т)и этапа: опрос требований на обслуживание устройств 5 и 6, установление логической связи устройств 5 и

6 с ЭВМ и выполнение процедуры обмеа данными, выполнение процедур контоля и диагностики подключенного контрольно-наладочному посту 4 контролируемого изделия 3,В исходном состоянии (при включеии питания устройств) все регистры счетчики коммутатора 2 и устройств

5 и 6 сброшены, после чего начинаетс цикл внутреннего опроса всех устpoiicTB, подключенных к коммутатору 2

При сбросе в узле 90 управления коммутатора 2 (фиг.2) устанавливается состояние Внутренний опрос. В формирователе 93 формируется слово упраления с установленным битом Опросить, которое передается в регистр 95 приема-передачи. Код слова управления с установленным битом Опросит из регистра 95 передается последовательным кодом через соответствующий узел 96, и линии 26, 27 и 28, 29 последовательного интерфейса связи в соответствующее устройство 5 и 6. Каждое из устройств 5 и 6 всех контрольно-наладочных постов имеет свои адреса. Адрес соответствующего устройства в процессе внутреннего он роса вырабатывается счетчиком 77 адг раса и дешифратором 91. В ответ на указание Опросить соответствующее устройство отвечает словом состоя ния, ответ анализируется дешифратором 94 ответа. Если нет ошибки при передаче слова управления и нет требования на прерывание, узел 90 управления разрешает увеличение на единицу содержимого счетчика 77 и опрашивается следующее по порядку устройство. Таким образом осушествляется циклический опрос всех подключённых к коммутатору 2 устройств 5 и 6. Опрос осуществляется непреры но до появления запроса на прерывание от любого из устройств или до: начала, обмена по инициативе ЭВМ 1. Второй этап работы, начинается с момента выставления запроса на прерывание от любого из устройств. Например, оператор любого поста 4, набрав на клавиатуре устройства 5 необходимые исходные данные для проверки изделия 3 (в исходных данных задаются имя изделия, режим контроля и другая информация), нажатием на клавишу программного прерывания устройства 5 выставляет требование на обслуживание данного поста со стороны ЭВМ 1.

На- дешифратор 94 коммутатора 2 (фиг. 2) поступает слово состо-яния из устройства 5 с идентификатором Внимание. При этом опрос прекращается и узел 90 управления формирует сигнал прерывания, поступающий через интерфейсные усилители

75 в ЭВМ 1 . В дальнеГгшем выполняется последовательность выборки устройства, в процессе которой через усилители 75 в ЭВМ 1 с генератора 76 передается адрес коммутатора 2, со счетчика 77 адрес устройства, затребовавшего обсл живание от ЭВМ, с регистра 89 байт состояния.

Из ЭВМ 1 через интерфейсные усилители 75 в регистр 78 команд поступает код команды Читать, который декодируется дешифратором 81.

Сигнал с выхода дешифратора поступает в узел 90 управления, где вырабатывается указание Читать с устройства, затребовавшего обслуживание, которое через регистр ,95, интерфейсный узел 96 приема-передачи передается в последовательном коде через линии 26 и 27 связи в диалоговое устройство 5.

Диалоговое устройство 5 по указанию с коммутатора 2 Читать осуществляет передачу содержимого буферной памяти через линии 26 и 27 связи, интерфейсный узел 96, регистр 95 приема-передачи в буферную память 87 коммутатора 2 (фиг. 2). По окончании передачи содержимого буферной памяти диалогового устройства 5 в буферную память 87 коммутатора 2 происходит передача в ЭВМ из буферной памяти коммутатора 2, через коммутатор 92, регистр 95 приемапередачи, коммутатор 85 и интерфейсные усилители 75.

В ЭВМ анализируется запрос оператора поста и в соответствии с организаующей программой. вызывается из архива соответствующая функциональна программа контроля для конкретного объекта, указанного в запросе оператора.

Массив данных функциональной программы контроля включает информацию для выработки указаний управления аппаратными средствами и информацию, предназначенную для выдачи соответствующих воздействий на проверяемый объект. Этот массив данных в соответствии с организующей программой системы, передается через коммутатор 2 в канал 6. Принятая из него по линии 28 и 29 связи информация поступает в блок 7 приема-передачи канала 6 .

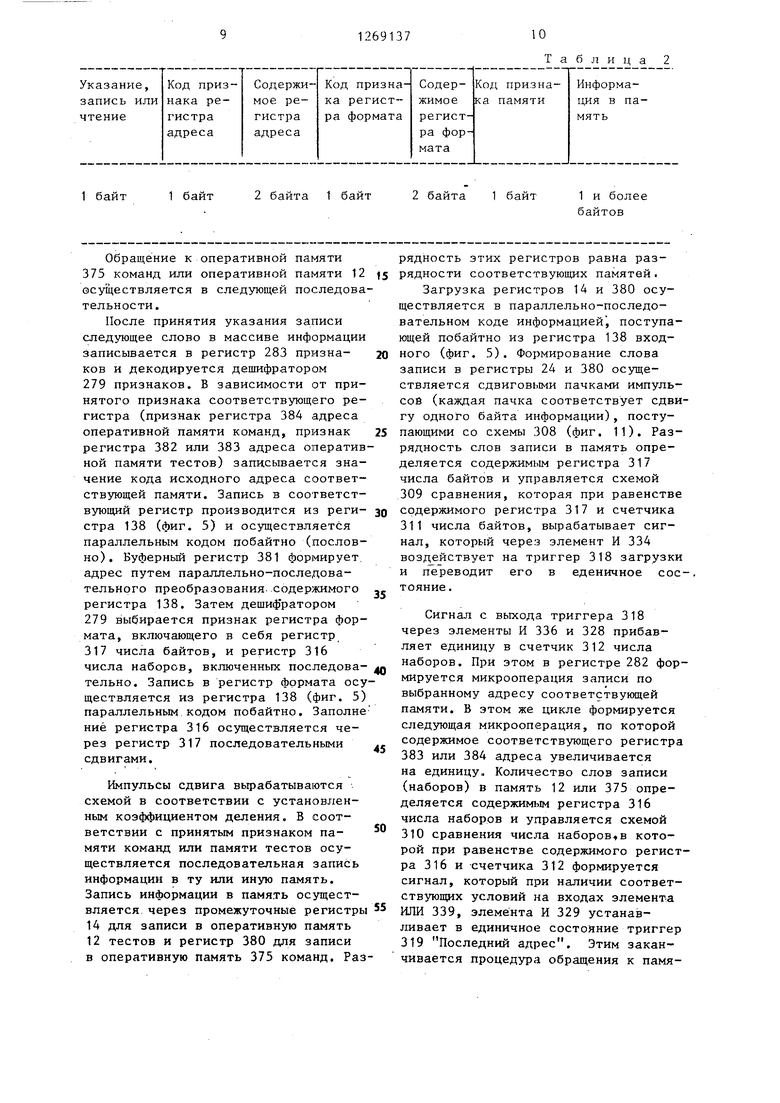

В узле 97 канала 6 (фиг. 4) принятая информация усиливается усили7телсм 125, с которого эта информация передается на дешифратор 123, где послй декодирования выделяются из двух полярных импульсов сигналы в виде логической единицы и логического нуля. С выхода дешифратора 123 информация подается на последовательный вход регистра 124, где осуществляется преобразование информации из последовательного кода в параллельный. Каждое слово принятой информации проверяется на нечет ность триггером 129 Нечет. В случае цриема слова с четным числом битов на выходе схемы ИЛИ 135 формируется сигнал Ошибка в приеме Первый разряд каждого слова массива информации всегда равен единице, и при дешифрации данного разряда устанавливается в единичное состояние триггер 127 Начало слова, который запускает счетчик 120. Если за установленное время работы счетчика слов будет принято не полностью (меньше 14 битов), то на выходе схемы ИЛИ 135 формируется сигнал Ошибка в при еме. Счетчик 119 числа битов предназначен для формирования 14-разрядного слова. Массив информации в процессе обме на ЭВМ 1 с каналом 6 имеет следующую структуру: слова, указывающие действие (запись или считывание)i слова указывающие направление, куда (в какой узел или блок) должны записываться или же откуда должна считываться информация; слова, указывающие формат (размерность) информации и слова данных. Слова управления отличаются от слов данных состоянием второго разряда. Принятое слово с указанием действия из регистра 124 приема-передачи узла 97 (фиг. 4) параллельным кодОм передается в узел 98 (фиг, 5) на фор мирователь 142 управляющих сигналов Сигналом с выхода формирователя 142 взводится триггер 145 Прием-указание, По сигналу с выхода треггера 145 Прием-указание в зависимости от принятого указания взводится или триггер 146 Указание-считывание или же триггер 148 Указание-запись Единичный сигнал с выхода триггера 146поступает в узел 176 блока 9 (фиг, 10) на первый вход элемента И 289, на второй вход которого подает378ся сигнал с выхода триггера 284 приянаков. Микрооперация, поступающая на первый вход элемента И 289 с выхода дешифратора 280 микроопераций, разрешает запись информации в регистр 283 признаков из регистра 124 (фиг.4). Следующая микрооперация, поступающая с выхода дешифратора 280 микроопераций через элемент И 288, сбрасывает триггер 284 признаков в нулевое состояние, тем самым обеспечивается хранение кода признака в регистре 283 на время приема информации в узел с соответствующим признаком. Последнее слово информации, принимаемое в узел с данным признаком, взводит триггер 319 Последний адрес (фиг. 11), сигнал с выхода которого через элемент И 288 переводит триггер 284 признаков в единичное состояние, и обеспечивается разрешение приема в регистр 283 нового признака. Процедуру загрузки соответствующих блоков и узлов устройства контроля можно рассматривать как два этапа загрузки. Первый этап - загрузка соответствующей информацией блока 18 программируемых источников напряжения (логических нуля и единицы) и блока 22 программируемых источников напряжения питания объекта контроля. Структура массива при записи в блоки 18 и 22 приведена в табл, 1. Таблица j 1 байт 1 байт 1 и более байтов Второй этап -.загрузка соответствующей информацией блоков и узлов, участвую1цих в формировании массивов информации при обращении к памяти 12 тестов или к памяти 375 команд. Структура массива информации при обращении к соответствующей памяти приведена в табл. 2,

Таблица

| название | год | авторы | номер документа |

|---|---|---|---|

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Устройство для обработки сейсмической информации | 1984 |

|

SU1168963A1 |

| Микропрограммное устройство сопряжения | 1984 |

|

SU1179359A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1456963A1 |

| Устройство для контроля | 1981 |

|

SU1072052A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для сопряжения | 1980 |

|

SU926645A2 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

Изобретение относится к области вычислительной техники и используется для контроля и диагностики неисправностей цифровых устройств. Целью изобретения является повышение коэффициента использования оборудования и полноты контроля изделий. Система содержит групповой двунаправленныи коммутатор, каналы, каждьп из которых содержит блоки приема-передачи, управляемых источников опорного напряжения, микропрограммного управления, формирования сигналов обмена, блоки управляемых источников напряжения питания, узел маскирования, память тестов, счетчик, коммутаторы, регистры - буферный, разделения, тестов, .. блок сравнения, шифратор.Изобретение обеспечивает формирование программируемых временных диаграмм обмена с частотой работы вьше частоты работы управляющей ЭВМ, контроль задержек схемы контролируемого объекта, конт- s роль различных типов схем, неодно(Л кратное повторение отдельных участков программ контроля и формирование конт.рольных сигналов на любые контакты I объекта, 1 а.п.ф-лы, 16 ил,,2 табл. 5 ГчЭ О5 СО со

2 байта 1 байт

1 байт

1 байт Обращение к оперативной памяти 375 команд или оперативной памяти 12 осуществляется в следующей последова тельности. После принятия указания записи следующее слово в массиве информации записывается в регистр 283 признаков и декодируется дешифратором 279 признаков. В зависимости от принятого признака соответствующего регистра (признак регистра 384 адреса оперативной памяти команд, признак регистра 382 или 383 адреса оператив ной памяти тестов) записывается значение кода исходного адреса соответствующей памяти. Запись в соответствующий регистр производится из регистра 138 (фиг. 5) и осуществляется параллельным кодом побайтно (пословно). Буферный регистр 381 формирует, адрес путем параллельно-последовательного преобразования, содержимого регистра 138. Затем дешифратором 279 выбирается признак регистра формата, включающего в себя регистр 317 числа байтов, и регистр 316 числа наборов, включенных последовательно. Запись в регистр формата осу ществляется из регистра 138 (фиг. 5) параллельным кодом побайтно. Заполне ние регистра 316 осуществляется через регистр 317 последовательными сдвигами. Импульсы сдвига вьфабатываются схемой в соответствии с установленным коэффициентом деления. В соответствии с принятым признаком памяти команд или памяти тестов осуществляется последовательная запись информации в ту или иную память. Запись информации в память осуществляется через промежуточные регистры 14 для записи в оперативную память 12 тестов и регистр 380 для записи в оперативную память 375 команд, Раз

2 байта 1 байт

1 и более байтов рядность этих регистров равна разрядности соответствующих памятей . Загрузка регистров 14 и 380 осуществляется в параллельно-последовательном коде информацией, поступающей побайтно из регистра 138 входного (фиг. 5). Формирование слова записи в регистры 24 и 380 осуществляется сдвиговыми пачками импульсов (каждая пачка соответствует сдвигу одного байта информации), поступающими со схемы 308 (фиг. 11). Разрядность слов записи в память определяется содержимым регистра 317 числа байтов и управляется схемой 309сравнения, которая при равенстве содержимого регистра 317 и счетчика 311 числа байтов, вырабатывает сигнал, который через элемент И 334 воздействует на триггер 318 за.грузки и переводит его в еденичное состояние. Сигнал с выхода триггера 318 через элементы И 336 и 328 прибавляет единицу в счетчик 312 числа наборов. При этом в регистре 282 формируется микрооперация записи по выбранному адресу соответствующей памяти. В этом же цикле формируется следующая микрооперация, по которой содержимое соответствующего регистра 383 или 384 адреса увеличивается на единицу. Количество слов записи (наборов) в память 12 или 375 определяется содержим з1м регистра 316 числа наборов и управляется схемой 310сравнения числа наборов в которой при равенстве содержимого регистра 316 и счетчика 312 формируется сигнал, который при наличии соответствующих условий на входах элемента ИЛИ 339, элемента И 329 устанавливает в единичное состояние триггер 319 Последний адрес. Этим заканчивается процедура обращения к памяПти 12 или 375 при выполнении операций записи или считывания информаци Оперативная память 12 тестов условно разбита на две зоны. Первая зона определяется адресами от О до N и выбирается регистром 383 адреса Эта зона хранит информацию, приняту из ЭВМ 1, в которой содержатся маски входящих и выходящих контактов контролируемого объекта 3, маски блокировки контроля определенных контактов и тестовые наборы, состоящие из значений входных воздейст вий и ожидаемых ответных реакций об „ 3 екта 3 контроля. Вторая зона определяется адресами от N+1 до последнего и-выбираетс регистром 382 адреса. Эта зона зарезервирована для хранения входньк воздействий и ответных реакций объе та 3 контроля. Граница между двумя приведенными зонами не имеет фиксированного значения и определяется объемом информации (количеством наборов), записа ной в первой зоне. Последний адрес первой зоны запоминается регистром 385 переадресации и хранится до загрузки новой программы контроля. Указанный способ адресации oneративной памяти тестов позволяет мн гократно выполнять программу контро ля, запоминать ответные реакции объ екта контроля в фиксированной для данной программы зоне памяти. Тем самым обеспечивается возможность работы в автономном режиме канала 6 Автономный режим работы канала 6 позволяет проводить контроль в режи ме разбраковки (по принципу Годен многих однотипных объектов контроля с использованием программы контроля хранящейся в оперативной памяти 375 команд и в оперативной памяти 12. тестов, без участия ЭВМ 1. Третий этап работы системы начинается с момента приема из ЭВМ 1 команды Пуск или с момента нажати кнопки Пуск (работа в автономном режиме). При приеме массива информа ции из ЭВМ 1 последним словом в мас сиве может быть команда Пуск. Информация, в которой содержится код команды Пуск, из регистра 124 приема-передачи параллельным кодом подается в регистр 283 признаков. После декодирования дешифратором 279 признаков вырабатывается сигнал 3712 который подается на один из выходов элемента ИЛИ 299, на второй вход последнего поступает сигнал с кнопки 36 Пуска.Сигнал,вырабатываемый на выходе элемента ИЛИ 299, устанавливает в единичное состояние триггер 285 Пуск, выход которого взводит триггер 245 Зона (фиг. 8). Одновременно с установкой в единичное состояние триггера 245, тем же сигналом запускается одновибратор 243 который, в свою очередь,запускает одновибратор 244. Сигналы с выхода триггера 245 и с выхода одновибратора 244 подаются на входы элемента И 236, выходной сигнал котчэрого управляет переписью содержимого регистра 383 адреса в регистр 385 переадресации. По линии 198 связи сигнал с выхода триггера 285 через элементы ИЛИ 256 и 257 запускает регистр 255 синхронизирующих тактов (фиг.9), который через триггеры 263-266 и элементы И 270-278 формирует сигналы управления обращением к памяти 375 команд и к памяти 12 тестов. При обращении к оперативной памяти 375 команд осуществляется чтение по адресу, указанному в регистре 384 адреса команд. Содержание опертивной памяти 375 команд представляет собой 32-разрядное слово команды, структура которого имеет следующий вид: разряды с первого по восьмой код операции, с девятого по восемнадцатый - коды адресов перехода, девятнадцатый - модификатор перехода, двадцатый - признак записи в счетчик времени, с двадцать первого по тридцать второй - коды количест-ва циклов. В зависимости от того, как формируется адрес следующей команды, в процессе выполнения программы контроля могут встречаться следующие команды: не нарушающие естественный порядок следования команд; безусловного перехода; условного перехода. Чтение команды сопровождается сигналом с выхода элемента И 270 (фиг, 9). По этому сигналу осуществляется запись кода операции команды в формирователь 404;-. Код операции является адресом первой микрокоманды микропрограммы, записанной в память 405. Каждая микрокоманда, прочитанная из памяти 405, имеет следующую структуру: разряды с первого по седьмой - код управ131

ления адресом следующей мирсрокоманды восьмой и девятьш - управление занесением и хранением признаков переходов, с десятого до пятнадцатый код микрокоманды, шестнадцатый - принак конца операции, с семнадцатого по двадцатый - код времени выполнения микрокоманды, двадцать первый и двадцать второй - стробирование компараторов уровней, с двадцать третьего по двадцать пятый - управление мультиплексором 392 признаков, двадцать шестой - признак памяти- команд или памяти тестов, двадцать седьмой признак записи-чтения. Первые девять разрядов микрокоманды определяют порядок формирования адреса следующей микрокоманды. Разряды с десятого по двадцать седьмой заносятся в регистр 406 микрокоманд и хранятся в течение времени исполнения данной мирокоманды.

Каждой команде, выбранной из оперативной памяти команд, соответствует своя микропрограмма. Коды микропрограмм с выхода регистра 406 микрокоманд поступают на дешифратор 408 микрокоманд, где декодируются, и по соответствующим связям подаются сигналы управления аппаратными средствами для формирования временной диаграммы обмена с контролируемым изделием и анализа его ответной реакции. Последняя микрокоманда каждой микропрограммы имеет признак конца операции, который во время вьтолнени микрокоманды хранится в регистре 406 микрокоманд и с его выхода поступает на первый вход элемента И 409. На второй вход элемента И 409 поступает сигнал с выхода преобразователя 407, осуществляющего преобразование кода длительности микрокоманды во временной интервал. При совпадении сигналов на вьгходе элемента И 409. появляется.сигнал, являющийся стартовым для начала чтения очередной команды из оперативной памяти 375 команд под управлением регистра 255 синхронизирующих тактов,, Обращение к памяти происходит также по микрокоманде сигналом с выхода дешифратора 408.

Режим обращения, записи ши чтени задается двадцать седьмым разрядом микрокоманды. Контроль начинается с команды разделения контактов: сопряжения с контролируемым объектом на

3714

входные и выходные с помощью коммутатора 20, Для этого на управляющий вход коммутатора подается код с выхода регистра 17 разделения, информация в который заносится из памяти тестов по сигналу с выхода дешифратора 408 микрокоманд. Аналогично по соответствующим командам осуществляется передача информации в узел 10 маскирования для маскирования соответствующих контактов, не участвующи в анализе, и в регистр 16 тестов. В последнем хранится информация о входных воздействиях и ожидаемых значениях ответных реакций контролируемого объекта.

Одновременно с записью информации в регистр 16 тестов запускается счетчик 13 времени, по окончании счета которого происходит стробирование второго коммутатора 15 с записью в него информации о состоянии контакто контролируемого объекта через коммутатор 20 и блок 19 сравнения. В последнем осуществляется контроль логических уровней на соответствие с. зталлоншзм значениям, запрограммированным в блоке 18. Управление на блоке сравнения (прием прямого, инверсного кода, логический контроль) осуществляется 21- и 22-м разрядами микрокоманды (фиг. 1). Величины опорных напряжений логического нуля и логической единицы формируются под управлением кода, поступающего из блока 18. .Через второй коммутатор информация поступает на узел 10 маскирования, где осуществляется логическое сравнение принятой информации с ожидаемой, хранящейся в регистре 14. По соответствующей микрокоманде результат поразрядного и обобщенного сравнения по микрокоманде передается через элемент ШЖ 11 в буферный регистр 14 и записывается по соответствующему адресу в оперативную память 12 тестов для хранения.

При обнаружении несоответствия значения сигнала на любом контакте контролируемого объекта 3 ожидаемому значению вырабатывается сигнал прерывания, поступающий в блок 8 микропрограммного управления и щифратор , 411, где формируется код идентификатора внимания, которьй поступает на мультиплексор 139 (фиг. 5) и далее через регистры 137 и 138, мультиплексор 141, подается на регистр 124 приема-передачи, а с регистра 124 через триггер 128, шифратор 121, усилитель 126 передачи, связь 28 подается в коммутатор 2 и далее в ЭВМ 1. В ЭВМ 1 анализируется принятый код и в соответствии с организующей программой формируется команда Читать с оперативной памяти 12 тестов. В коммутаторе 2 по команде Читать формируется соответствующее указание, которое передается в канал 6. Канал 6 по принятии указания Читать из оперативной памяти 12 тестов осуществляет передачу содержимого памяти через коммутатор 2 в ЭВМ 1 где производится анализ принятой информации. По результату анализа ЭВМ вырабатывает соответствующие директивы оператору контрольно-наладочного поста. Оператор контрольно-наладочного поста общается с системой через диалоговое устройство 5.Все сообщения о ходе процесса диагностирования программа выводит на экран диалогового устройства 5. Оператор поста на основании директив программы с помощью коммутатора 23 вводит в систему информацию о состоянии сигна лов в контрольных точках. В шифраторе 21 формируется шифр кода состояния контрольных точек, который через блок 7 канала 6 и коммутатор 2 передается для анализа в ЭВМ. В процессе вьтолнения программ контроля и диагностических процедур может возникнуть необходимость в. мно гократном исполнении любой команды. Для этого предусмотрена подготовител ная команда Групповая операция. По этой команде производится запись кода количества повторений следующей за ней команды в счетчик 373 цик лов. Разряды кода операции данной команды декодируются дешифратором 378, и сигналом с его выхода устанавливается в единичное состояние триггер 388 групповой операции. Сигнал с триггера 388 через линию 402 i воздействует на элемент И, формируя сигнал Запрет :изменения содержимого регистра 384 адреса команд. При этом в каждом цикле выполнения коман ды происходит уменьшение содержимого счетчика 373 циклов на единицу. Этот сигнал формируется по сигналу с выхода регистра 255 синхронизирующих тактов, поступающему на элемент И 1 3716 421. Повторение этой команды продолжается до обнуления счетчика 373 и сброса им триггера 388 групповой операции, который снимает запрет на увеличение содержимого регистра адреса команд на плюс единицу. Б целом ряде случаев возникает необходимость многократного исполнения некоторой последовательности команд. Циклирование участков программы контроля осуществляется командой Цикл программ и обеспечивает многократное выполнение какого-либо участка программы. По команде Подготовка циклов происходит запись кода количества циклов повторений участка программы в счетчик 373 циклов программ и начинается первая команда участка. Триггер 389 сброшен, и разрешается формирование сигнала плюс единица в регистр адреса команд. За последней командой в цикле следует команда Переход по счетчику циклов. В адресной части этой команды записан код адреса перехода к начальной команде цикла. По выполнении последней команды цикла из счетчика 373 циклов программ вычитается единица. При завершении циклической программы счетчик обнуляется и триггер 389 конца цикла устанавливается в единицу, разрешая переход к адресу следующей команды. В ПРОТИВНОМ случае осуществляется переход к начальной команде Переход по счетчику циклов. Передача кода адреса из оперативной памяти 375 команд в регистр 384 адреса команд происходит под управлением формирователя 372. Для организации выдачи на объект контроля импульсной последовательности предусмотрена команда Цикл импульсной последовательности. Выполнение ее заключается в следующем. Если информация на определенных контактах объекта 3 контроля, содержащаяся в памяти 12 по адресу К,будет иметь противоположное значение информации на тех же контактах по адресу К+1, то при циклировании участка программы,, состоящего из этих двух адресов на соответствующих контактах объекта 3, будет подаваться опреде- ленная последовательность импульсов. Количество импульсов задается в команде Цикл импульсной последовательности и записывается в счетчик 374 циклов импульсной последователь17ности при чтении из оперативной памяти 375 команд. По сигналу с выхода дешифратора 378 кода операции устанавливается в единичное состояние триггер 387 цикт лов импульсной последовательности, импульс с выхода которого разрешает элементу И 390 пропуск импульсов обратного счета на вход счетчика 374 циклов импульсной последовательное.ти. Выход счетчика 374 через мультиплексор 392 признаков подключается к формирователю 404 и анализируется им в процессе выполнения микропрограммы, реализующей команду Цикл импульсной последовательности. После обнаружения указанного приз нака микропрограмма выходит из цикла и завершает выполнение команд, В связи с тем, что некоторые неисправности БИС не могут быть обнаружены тестовыми проверками, контролир /ющими по сути только статические состояния сигналов на входах и выходах важное значение приобретает контроль задержек, вносимых элементами схемы объекта при различных режимах, С это целью в систему введен счетчик 13. После считывания из оперативной памяти 12 тестового набора и передачи его в регистр 16 тестов микропрограммы реализуется цикл ожидания окончания счета счетчика 13. Так как вьщача тестового набора и запуск счетчика происходят oAHOBpeMeHHOj а прием ответной реакции осуществляетс по окончании счета счетчика, то это позволяет контролировать временные задержки распространения сигнала в контролируемом объекте и определять частоту подачи тестовых воздействий Девятнадцатый разряд оперативной па мяти команд служит для модификации команд Условный переход и Безусловный переход. При значении едини цы этого разряда изменяется адрес чтения из оперативной памяти команд при значении нуль - адрес считьвзани из оперативной памяти тестов. Повышение коэффициента использования оборудования и увеличение пол ноты контроля обеспечивается структурой аппаратных и программных средств системы. Наличие блока приема-передачи, блока формирования си налов обмена счетчика позволяет работать в автономном режиме, т.е,. проводить контроль изделия по програ 3718 ме, записанной в буферную память каждого канала. ЭВМ после загрузки программ контроля в память соответствующего канала логически отключается от него и может быть задействована для р€;шения других задач. Повышение полноты контроля достигнуто путем появления неисправностей, проявляющихся только в динамических режимах на скоростях обмена с контролируемым изделием, равных скоростям работы в реальных условиях функционирования, и за счет выявления параметрических неисправностей с помощью блока сравнения уровней сигналов обмена на выходах контролируемого изделия с эталонными значениями задгшаемыми программным источником опорного напряжения при одновременном изменении (в допустимых пределах) напряжения питания контролируемого изделия с помощью программируемого источника напряжения питания. Сопрягаемость системы со стандартным интерфейсо ввода-вывода позволяет образовать комплексы по контролю изделий на базе, имеющихся на предприятиях вычислительных средств. Формула изобретения 1. Многоканальная система для . контроля и диагностики цифровых блоков, содержащая групповой двунаправ ленный коммутатор, вход и выход которого соединены соответственно с входом и выходом системы, а группа входов и группа выходов - с первыми входами и выходами соответствующих каналов, вторые входы которых соединены с группой входов системы, а каждый канал содержит блок микропрограммного управления, память тестов, буферный регистр, узел маскирования, регистр тестов, первый и второй коммутаторы, шифратор, регистр разделения, элемент ИЛИ, причем второй вход- канала соединен через первый коммутатор с входом шифратора, первый выход узла маскирования соединен с первым входом элемента ИЛИ, отличающаяся тем, что, с целью повьшхения коэффициента использования оборудования-и повьш1ения полноты контроля, второй вход и входвыход каждого канала соединены соответственно с группой выходов и группой входов - выходов системы, а в 191 каждт,ый канал введены двунаправленный коммутатор, блок приема-передачи блок формирования сигналов обмена, блок управляемых источников опорного напряжения, блок сравнения, счетчик, причем первые вход и выход блока приема-передачи соединены соответйтвенно с первыми входом и выходом канала, второй выход которого соединен с выходом блока управляемых источников напряжения питания, первые входы последнего блока управляемых источников опорного напряжения и блока формирования сигналов обмена соединены с вторым выходом блока приема-передачи, с третьего по пятый выходы которого соединены соо.тветственно с второго по четвертый входами блока формирования сигналов обмена , с первого по восьмой выходы которого соединены соответственно с первым и вторым входами блока микропрограммно го управления, с вторыми входами бло ка управляемых источников напряжения питания и блока управляемых источников опорного напряжения, с первым и вторым входами буферного регистра, с первым входом памяти тестов и вторым входом блока приема-передачи, с третьего по шестой входы которого соединены соответственно с выходом шифратора, первым и вторым выходами блока микропрограммного управ ления и с первым входом буферного регистра, второй выход которого соединен с первыми входами регистра тес тов, регистра разделения и узла маскирования и с вторым входом памяти тестов, первый и второй выходы которой соединены соответственно с первым. входом элемента ИЛИ и третьим входом блока микропрограммного управ ления, с третьего по восьмой входы которого соединены соответственно с третьим входом памяти тестов, с первым входом счетчика, с первым входом блока сравнения, с вторым входом регистра разделения, с пятым входом блока формирования сигналов обме«а и с вторым входом узл4 маскирования, первый и второй выходы которого соединены соответственно с вторым входом элемента ИЛИ и четвертым входом блока микропрограммного управления, девятый выход которого соединен с вторыми входами регистра тестов и счетчика, выходы последнего и блока сравнения соединены с входами второ- го коммутатора, выход которого соединен с третьим входом узла маскирования, шестой выход блока приема-передачи соединен с третьим входом буферного регистра и пятым входом блока микропрограммного управления, шестой вход которого соединен с девятым выходом блока формирования сигналов обмена и с четвертым входом буферного регистра, десятый выход блока формирования сигналов обмена соединен с третьим входом счетчика, а одиннадцатый выход - с третьими входами блока управляемых источников напряжения питания и блока управляемых сигналов источников опорного напряжения, первый и второй выходы последнего и выход двунаправленного коммутатора соединены соответственно с вторым, третьим и четвертым входами блока сравнения, выхрды регистра тестов и регистра разделения соединены соответственно с первым и вторым входами двунаправленного коммутатора, соединенного двусторонней связью с вхо- дом-выходом канала. 2. Система по п. 1, отлича ющ а я с я тем, что блок формирования сигналов обмена содержит узел задания временных интервалов, распределитель синхросигналов, коммутатор управляющих сигналов обмена, дешифратор признаков, дешифратор управляющих сигналов, причем первый выход коммутатора управляющих сигналов обмена соединен с первым выходом блока второй выход которого соединен с вторым,третьим и четвертым выходами коммутатора управляюш;их сигналов обмена, первым и вторым выходами распределителя синхросигналов, первым, вторым выходами распределителя синхросигналов, первым, вторым и третьим выходами дешифратора признаков, третий и четвертый выходы блока, с первого по четвертый входы коммутатора управляю- сигналов обмена, с первого по четвертый входы дешифратора признаков, первый и второй входы распределителя синхросигналов и с первого по третий входы дешифратора управляюпщх сигналов соединены с первым выходом узла задания временных интервалов, второй выход которого соединен с десятым выходом блока, пятый, шестой и седьмой выходы которого соединены соответственно с первым и вторым выходами дешифратора управляющих сиг2112

налов и с третьим выходом распределителя синхросигналов, четвертый и пятый выходы которого соединены с девятым выходом блока, восьмой выход которого соединен с третьего шеетой выходами дешифратора управляющих сигналов, третьим выходом узла задания временных интервалов и пятым входом дешифратора признаков, шестой вход которого соединен с первым входом блока, второй вход которого соединен с nepBbiM входом узла задания временных интервалов, четвертый выход которого соединен с седьмого по тринадцатый входами дешифратора признаков, с третьим входом распределителя синхросигналов, с четвертым входом дешифратора управляющих сигналов и одиннадцатым выходом блока, третий вход которого соединен с четырнадцатым входом дешифратора признаков, пятыми входами коммутатора управлянйцих сигналов обмена и дешифратора управляющих сигналов, с четвертым входом распределителя синхросигналов и с первого по четвертый входами узла задания временных интервалов, пятый выход которого соединен с пятым входом распределителя синхросигналов, пятнадцатым входом дешифратора признаков и шестым входом коммутатора управляющих сигналов обмена, седьмой вход которого соединен с шестым выхог

3722

дом распределителя синхросигналов, шестой вход которого соединен с шестым выходом узла задания временныхинтервалов и шестнадцатым входом дешифратора признаков, с четвертого по седьмой выходы которого соединены соответственно с пятым и шестым входами узла задания временных интервалов, восьмым входом коммутатора управляющих сигналов обмена и шестым . входом дешифратора управляющих сигналов, четвертый вход блока соединен с семнадцатым входом дешифратора признаков, седьмым входом дешифратора управляющих сигналов, восьмым входом узла задания временных интервалов и седьмым входом распределителя синхросигналов, пятый вход блока соединен с девятым входом узла задания временных интервалов, с восемнадцатого по двадцатый входами дешифратора признаков, с девятого по семнадцатый входами коммутатора управляющих сигналов обмена, восьмым и девятым входами дешифраторов управляющих сигналов и с восьмого по одиннадцатьй входами распределителя синхросигналов, седьмой выход которого соединен с двадцать первым входом дешифратора признаков и с восемнадцатым входом коммутатора управляющих сигналов обмена, пятый выход которого соединен с двадцать вторым входом дешифратора признаков.

л

106, SS

т 101

т

ipt

L

Риг 9

X

(Риг. 12

f

| Автоматизированная система для испытания сложных объектов | 1980 |

|

SU955095A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Система централизованного контроля радиоэлектронных изделий | 1978 |

|

SU744481A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1986-11-07—Публикация

1984-06-25—Подача