Изобретение относится к телевиде нию, а именно к электронному синтезу сложных ТВ-изображений 5 и может найти применение при построении разнообразных алфавитно-цифровьЕ и графических дисплеев, ТВ испытательных изображений и таблиц в системах передачи неподвижных ТВ-изображений при создании телевизионных мультфильмов и фоновых изображений для игровых автоматов и тренажеров; в специализированных устройствахдля отображения информации в частности при формировании мнемосхем и всюду5 где необходимо создать сложное телевизионное изображение, передавать его по узкополосному каналу связи, предварительно исключив избыточность, и восстановить простейшим образом либо обеспечить пере программированный синтез изображений путем использования минимального объема памяти. Особое значение предлагаемое изобретение имеет при создании ТВ-систем массового информационно-справочного обслуживания. Известны устройства электронного формирования сложных телевизионных изображений, основанные на аналоговых, дискретных и кoмбJ ниpoвaнныx методах формирования lj . Однако данные устройства предназначены для формирования конкретных изображений и поэтому не позволяют формировать разнообразные изоб ражения путем смены программ. Значительное сокращение избыточности телевизионных изобралсений обе печивается в цифровых системах, в к торых телевизионньй сигнал подвергают линейному преобразованию. Исходное изображение разбивают на зоны, калодая из которых описывается матрицей сплП элементами 2 . ,,„ К недостаткам устройств, реализующих принцип линейного преобразования, следует отнести значительную сложность декодирования. Так, например, применение преобразования Фурье требует 4 перемножени и такое же число сложений преобразование Адамара требует 4 сложений, а для вычисления преобразования Карунена-Лоэва-Пугачевя тре буется примерно п арифметических операций. Наиболее близким по технической сущности к предлагаемому является устройство для формирования сигналов алфавитно-цифровых и графических изображений, содержащее синхрогенератор, блок адресных счетчиков, выходы которого соединены с соот:зетст)зующими адресными входами блока пагадти и генератор символов з. Указанное устройство сложно, так как независимо от сложности сигналов изображения в формировании принимает участие весь объем памяти. Цель изобретения - упрощение устройства путем сокращения объема памяти при сохранении функциональных зозможностей и улучшение качественнык параметров формируемых изображепий, Поставленная цель достигается тем, что в устройство для форг-трования сигналов алфавитно-цифровых и графических изображений, содержгш.ее синхрогенератор, блок адресных счетчиков, 1зьгходь5 которого соединены с соответствующими адресными выходами блока памяти, и генератор символов, введены блок запрета смены адреса, включенньп между первым выходом синхрогенератора и первым и вторым вxoдa ш блока адресных счетчиков, блок формирования управляющих сигналов, блок восстановления, блок управления реверсированием символов, блок формирования сигналов цветовых компонент и цифроаналоговый преобразователь (ЦАП)э при этом информационный вход блока формирования управляющих сигналов с Е;Ь ходом блока памяти и объединенными информационными входами блока загтрета смены a,4pecas блока адресных счетчиков5 и блока восстановления, синхровход соединен с вторым выходом синхрогенератора} первый 2ЫХОД - с управляющим входом блока восстановления, а яторой выход- с управлякадими входаг-да блока запрета смены адреса и блока адресных счетчиков первьй второй и третий выходы блока восстановления подключены к первым входам соответственно блока управления реверсированием символов( генератора символов и блока формирования сигналов цветовых компонент, а четвертый выход - к; дополнительному информационному входу блока формирования управляющих сигналов 5 третий выход синхрогенератора соединен с синхровходом

3

блока управления реверсированием символов, выход которого через последовательно соединенные генератор символов и блок формирования сигналов цветовых компонент подключен ко входу ЦА11.

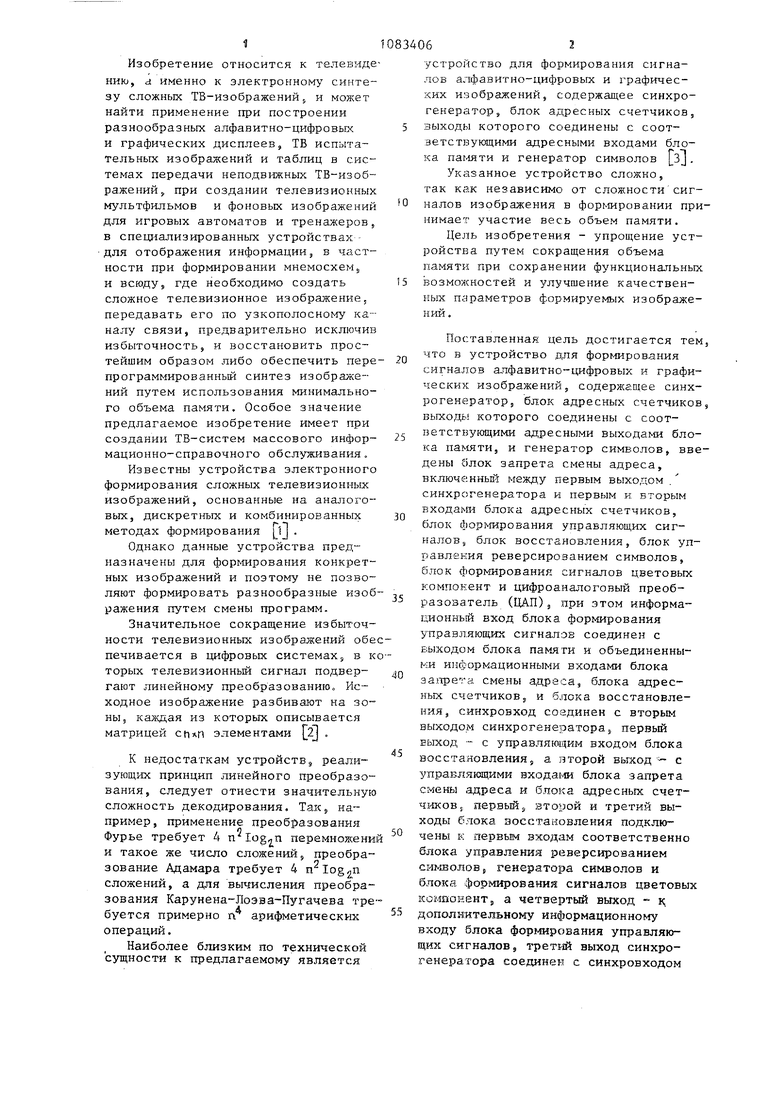

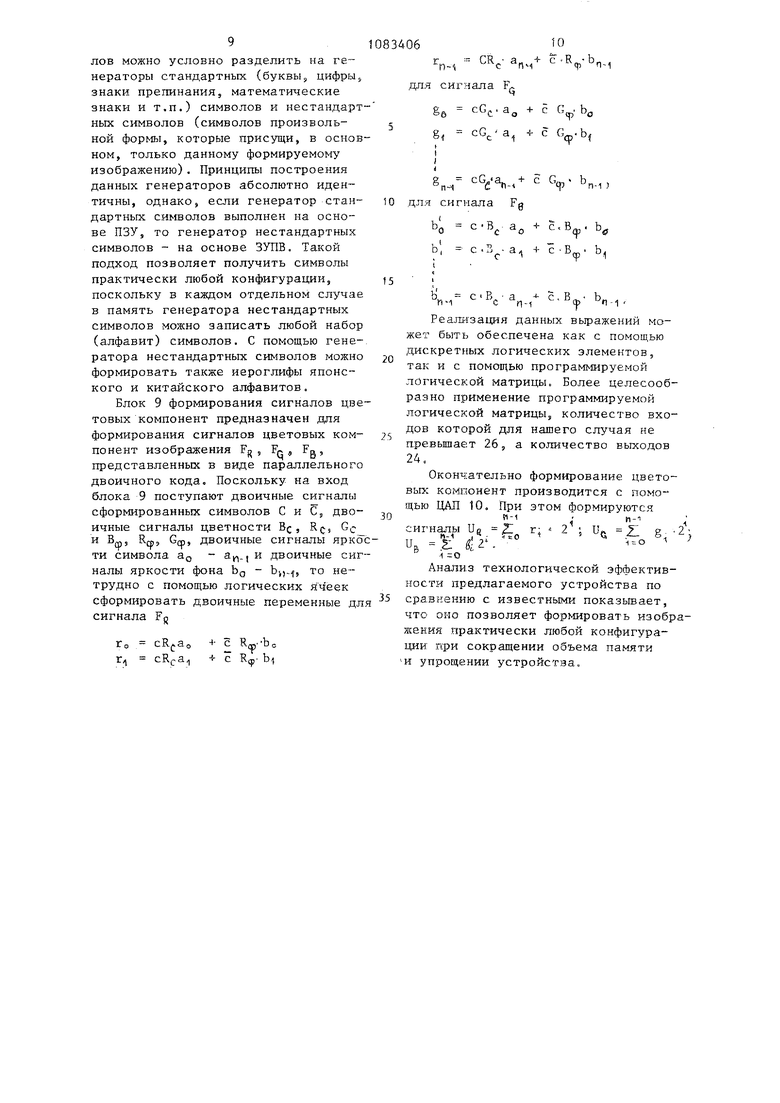

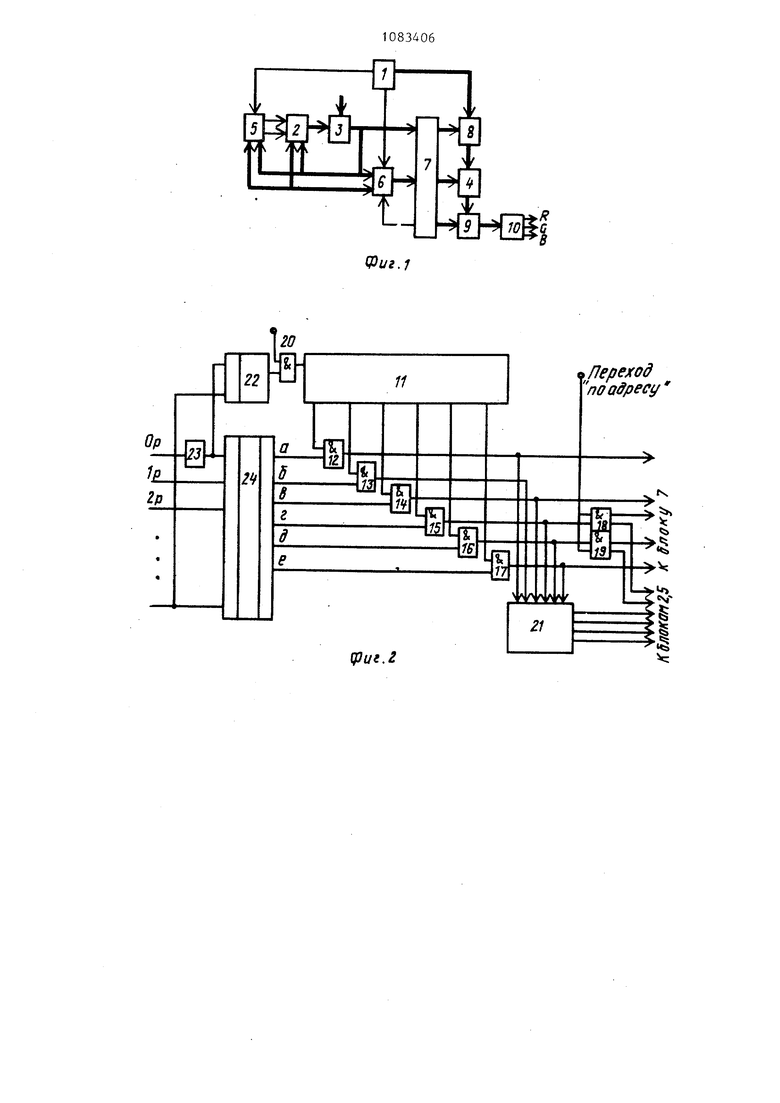

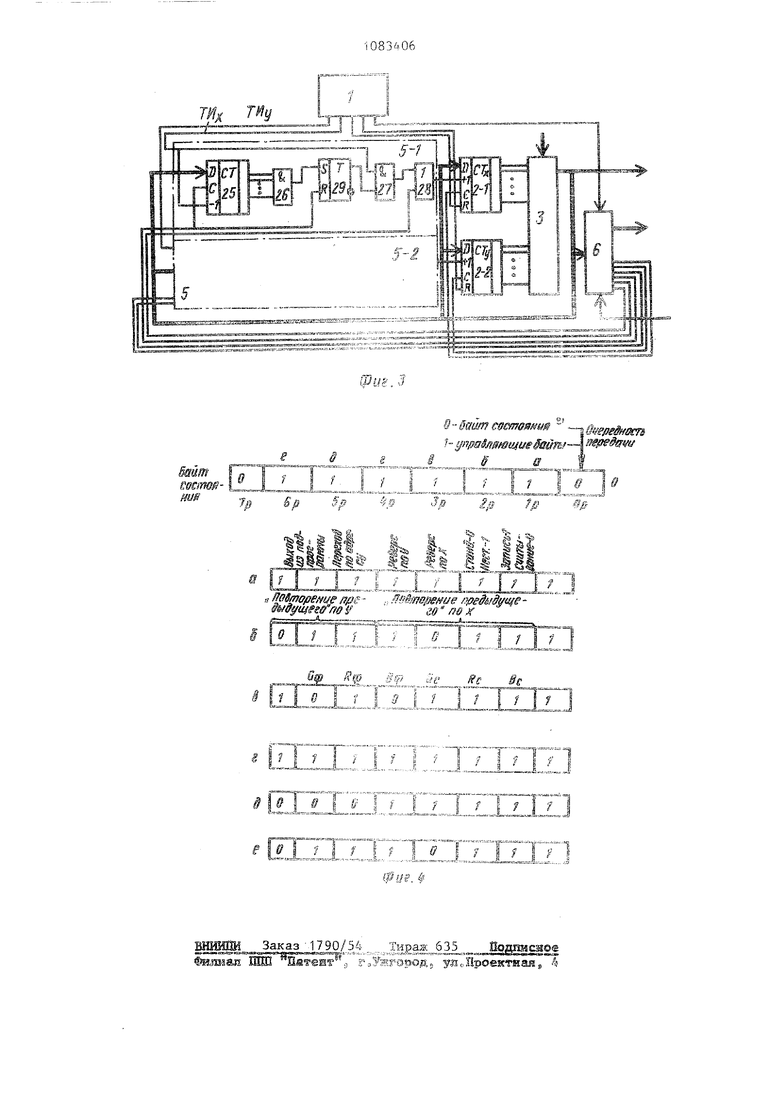

На фиг, 1 представлена структурная электрическая схема устройства для формирования сигналов алфавитноцифровых и графическ,их изображений; на фиг. 2 - структурная электрическая схема блока формирования управляющих сигналов; на фиг. 3 - структурные электрические схемы блока запрета смены адреса и блока адресных счетчиков и основные их связи с блоком предсказания; на фиг. 4 таблица формируемых символов.

Устройство содержит синхрогенератор 1, блок 2 адресных счетчиков, состоящий из первого и второго адресных счетчиков 2-1 и 2-2, блок 3 памяти и генератор 4 символов, блок 5 запрета смены адреса, состоящий из параллельных каналов 5-М и 5-2, блок 6 формирования управляющих сигналов, блок 7 восстановления, блок 8 управления реверсированием символов, блок 9 формирования сигналов цветовых компонент и ЦАП 10.

При этом блок 6 формирования управляющих сигналов содержит распрделитель 11 импульсов, элементы 12-20 логического формирования, логический формирователь 21, триггер 22, инвертор 23, регистр 24 промежуточной памяти.

Блок 5 запрета смены адреса соде жит два идентичных параллельных канала 5-1 и 5-2, состоящих из двоичных счетчиков 25, логических ячеек 26-28 и триггеров 29.

Устройство работает следующим образом.

Блок 3 памяти предназначен для хранения программы компоновки телевизионного изображения, состоящей из кодов, символов и управляющих кодов. Он дозволяет сохранять информацию между циклами обновления и выдавать ее синхронно с телевизионной разверткой. В зависимости от характера применения устройства бло памяти может быть выполнен в виде запоминающего устройства с произволной выборкой информации (телевизионные дисплеи и видеотерминалы, знакоформирующие устройства и т.п.) либ.о

834064

в виде постоянного запоминающе1-о устройства (генераторы телевизионных испытательных изображений и таблиц, специализированные устройства 5 отображения информации и т.п.).

Объем памяти определяется числом выбранных знакомест и разрядностью кодов, которая в данном случае достигает 7-8 бит. В режиме формироваQ ния испытательных изображений и таблиц, а также при использовании устройства в качестве ТВ специализированного устройства отображения информации блок памяти может быть

с выполнен в виде перепрограммируемого либо сменного блока памяти. В остальном блок памяти ничем не отличается от запоминающих устройств современных алфавитно-цифровых дисплеев.

Информация, подлежащая отображению, располагается в очередности, показанной в таблице на фиг. 4. При этом каждому из отображаемых симво5 лов соответствует определенное количество байтов. Байт состояния, отличакяцийся от остальных байтов наличием нуля в нулевом разряде, показьшает, какой из последующих байтов должен быть считан в промежуточную память блока восстановления. Это указание обеспечивается записью единицы в разряды 1-6. При этом из соответствукяцих байтов считывается информация Управление символом (фиг. 4о), Повторение предыдущего (фиг. 45), Переход на новую цветность (фиг. 4Ь), Переход на новую яркость символа (фиг. ), Переход на новую яркость фона (фиг. 4д), а также Переход на новый символ (фиг. 4е).

Параллельньй код с выхода блока 3 памяти в режиме считьшания инфор5 мации поступает на информационньй вход блока 6. Блок 6 предназначен для выделения из приходящего массива информации управляющих символов и формирования из них управляющих

0 сигналов, которые представляют собой распределительные импульсы. Они поступают на управлякмций вход блока восстановления, указывая тем самым, в какой из регистров следует запи5 СЕТЬ очередной байт информации. Помимо этого блок 6 формирует управляющие сигналы, которые, будучи поданными на входы блока 2 адресных счетчиков5 изменяют характер следования тактовых импульсов ТИ и ТИц. Блок 6 формирования управляющих сигналов (фиг. 2) представляет собо цифровое устройство, регистр 24 промежуточной памяти которого вьще-ляет и запоминает байт состояния. Для этого младший разряд входных сигналов подключают к входу Ра

решение записи регистра. Распределитель 11 импульсов, выполненный5 например, в виде счетчика-дешифратора, с помощью логических ячеек И поочередно считывает информацию с разрядов регистра промежуточной памяти. Логический формирователь 215 состоящий из логических элементов типа И и ИЛИ, производит формирование импульсов управления работой блока адресных счетчиков. Помимо этого, в состав блока 6 входит RS-триггер 225 запуск которого осуществляется управляющим импульсом символа Переход на новьй символ, а сброс - нулевым разрядом очередного байта состояния. Формируемьш при этом сигнал с элемента 20 (И) управляет работой распределителя импульсов создавая приоритет символу Переход на новый символ. Элементы 18 и 19, представляющие собой коммутирующие ячейки, управляемые импульсом Переход по адресу,, обеспечивают переключение символов Переход на новую яркость си 4вола и Переход на новую яркость фона в необходимое направление.

Блок 7 восстановления представляет собой устройство промежуточной памяти, в котором происходит запоминание всех параметровS входящих в управляющие символы данного знакоместа, а также тех, которые в предыдущем знакоместе не требуют изменений. Блок восстановления выполняется с помощью двух групп регистров памяти. На информационные входы первой группы регистров (пять регистров предназначенных для приема управляющих символов, одновременно подаются коды с выхода блока . При этом запись того или иного управлякгщего символа в свой регистр обеспечивается управляюп;ими сигналами разрешения записи, поочерпедно подаваемыми с выхода блока 6. После того, как произойдет прием всех управляющих

вола,, яркости символа, яркости фона, цветности и управления. Исключение Составляют коды повторения, которые непосредственно записываются в блок адресных счетчиков.

Блок 2 адресных счетчиков предназначен для формирования сложной последовательности тактовых импульсов запуска адресньк счетчиков. Крограмка подачи тактовых и тульсов запуска на выходы .адресных счетчиков записывается в постоянное запоминаюш;ее устройство (ПЗУ) блока памяти и в процессе считьшания информации поступает на вход блока.

Программа управления адресными счетчиками предусматривает возможность как пропуска циклов, так и лерехоца по заданному адресу Блок адресных счетчиков в данном случае обеспечивает уплэавляемьй пропуск циклов,. Действительно, если группа смежных символов в формируемом изобрйженли не требует какого-либо перехода в процессе считьшания, что обычно происходит 3 процессе отображения идентичньш символов с оди-f яакоБымк характеристикаг-ш яркости и ifBeTHocTHj, то, естественно; в процессе синтеза изображений не нужно изменять коды формируемых изображений, а следовательноэ и адреса этих кодов. Поэтому- достаточно пропустит необгодимое количеепво циклов путем згггрета тактсзых импупъсов запуска,, подаваемых на вход адресных счетчиков. Такая операция в блоке дцрескьн счетчиков реализуется следующим образом. В нормальном режиме,; т S, при поочередном очитывании с ячеек блока гшмяти. тактовые импульсы знакомест горизонтальной ди1;яретизации ТИи с выхода синхрогенератора 1 (фиг 3) подаются через логические ячейки 27 и 28 (соотв-атственно И к ИЛИ) на счетный вход первого адресного счетчика 2-1 унел гчивая тем сз.ьиш формируемьй символов, одновременно происходит перезапись всех символов во вторую грушту регистров. Таким образом, если в первой группе регистров происходит прием сигналов изменения (перехода параметров формируемых изображений, то во второй группе регистров формируются коды всех параметров изображения для данного знакоместа, а именно коды его адрес на +1. На второй вход логической ячейки 27 подается 1, снимаемая с прямого выхода RS-триггера 29. Данный сигнал является стробИруЮЩИМ для импульсов THj{ . При считывании информации управляющий символ (байт) Повторение предьщущего, показывающий, сколько раз следует повторить предьщущий символ, записывается в двоичньй счетчик 25. Логическая ячейка 26, подключенная к инверсным выходам двоичного счетчика, формирует импульсы, логическая функция которых F abJd соответствует появлению импульсов при нулевом состоянии двоичного счетчика. Поэтому при записи байта Повторение предьщущего в двоичный счетчик 25 одновременно с записью производится установка RS-триггера в состояние О путем подачи импульса записи на вхо R. С этого момента прекращается пос тупление импульсов ТИх на счетньй вход первого адресного счетчика 2-1 до тех пор, пока состояние двоичного счетчика 25 в режиме вычитания не станет равным .О. При это импульс с выхода логической ячейки 26 установит RS-триггер в состояние 1 и тактовые импульсы ТИ) начнут поступать на счетный вход адресного счетчика 2-1. Таким образом, на выходе логической ячейки 27 формирует ся импульс продвижения адреса к оче редному байту состояний на каждом знакоместе, в то время как импульсы продвижения адреса к остальным байтам данного знакоместа формируются логическим формирователем 21 блока 6 и подаются на второй вход логичес кой ячейки 28 (ИЛИ). Таким образом независимо от наличия символа Повторение предыдущего, на адресный счетчик поступят все импульсы, необходимые для опроса памяти данного знакоместа. Следует добавть, что блок запрета смены адреса по вертикали не имеет принципиальных отличий, однако не требует ячейки ИЛИ, аналогично логической ячейке 28. Адресные счетчики блока 2 (фиг. предназначены для формирования текущих адресов для считьшания информации с блока памяти. Они обеспечивают как единичное приращение адреса по осям X и У в счетном режиме, так и переход по заданному адресу 6« практически к любому знакоместу адресного поля. Адресные счетчики состоят из двух двоичных счетчиков для обеспечения раздельной выборки данных по горизонтали и вертикали, помимо счетного входа, имеют входы параллельной записи информации и ничем не отличаются от известных микроэлектронных схем, Синхрогенератор представляет собой устройство, предназначенное для формирования необходимых тактовых и синхронизирующих импульсов. Блок 8 управления реверсированием символов представляет собой устройство, позволякнцее по командам, записанным в байте Управление символом (фиг, 4а), обеспечить реверсирование (симметричное отображенке) символа по горизонтали, по вертикали либо по горизонтали и вертикали одновременно. Применение такого приема позволяет в некоторых случаях уменьшить количество символов, записываемых в генератор символов, в 4 раза. Так, например, при формировании круговых фигур на ТВ-растре, в генератор символов достаточно записать символы, описывающие лишь одну четверть формируемой фигуры. Остальные части, представляющие собой конгруэнтные зеркальносимметричные фигуры, могут быть получены путем применения реверсирования , Блок 8 состоит из узлов инверсии кодов. Так, например, реверсирование символов по горизонтали при матричном способе формирования символов можно обеспечить путем изменения направления сдвига (влево вправо) сдвигового регистра, используемого для параллельно-последовательного преобразования данных, считываемых с матрицы ПЗУ генератора символов. Реверсирование символов по вертикали при матричном способе формирования символов нетрудно обеспечить путем инверсии кодов выборки данных при считывании с матрицы ПЗУ генератора символов, Описанные операции щироко применяются в разнообразных устройствах автоматики и достаточно полно описаны в l , Генератор 4 символов предназначен для формирования разнообразных символов (знаков) в пределе выбранного знакоместа. Генератор симво9

лов можно условно разделить на генераторы стандартных (буквы, цифры знаки препинания, математические знаки и т.п.) символов и нестандартных символов (символов произвольной формы, которые присущи, в основном, только данному формируемому изображению). Принципы построения данных генераторов абсолютно идентичны, однако, если генератор стандартных символов выполнен на основе ПЗУ, то генератор нестандартных символов - на основе ЗУПВ. Такой подход позволяет получить символы практически любой конфигурации, поскольку в каждом отдельном случае в память генератора нестандартных символов можно записать любой набор (алфавит) символов. С помощью генератора нестандартных символов можно формировать также иероглифы японского и китайского алфавитов.

Блок 9 формирования сигналов цветовых компонент предназначен для формирования сигналов цветовых компонент изображения Fj , FQ , Fg , представленных в виде параллельного двоичного кода. Поскольку на вход блока 9 поступают двоичные сигналы сформированных символов С и С, двоичные сигналы цветности В, R(s G и Вф, Rq,5 Сф, двоичные сигналы ярко ти символа ад - .., и двоичные сигналы яркости фона bg - bj,., то нетрудно с помощью логических ячеек сформировать двоичные переменные дл сигнала Fg

Го с ,; г , + с Кф Ь

83406О

V. СЯ,-а„,+ c.,,,

для сигнала

ее cG.a + 5 G. Ь„

g ч- с G.b

t I

8пи S b,.,,

10 для сигнала Fg

4 с-В а ч- с,В(. b

Ь, с .S а + с ср Ц

м Рс- п-, - Ь.1, Реализация данных выражений может быть обеспечена как с помощью дискретных логических элементов, так и с помощью программируемой логической матрицы. Более целесообразно применение программируемой логической матрицы, количество входов которой для нашего случая не превьнпает 26, а количество выходов 24.

Окончательно формирование цветовых компонент производится с помощью ЦДЛ 10. При этом формируются

Ug , т- UQ Z: g 2 и l. 0 1

1 О

Анализ технологической эффективности предлагаемого устройства по 5 сравнению с известными показьтает, что оно позволяет формировать изображения практически любой конфигурации при сокращении объема памяти И упрощении устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации на экране телевизионного индикатора | 1984 |

|

SU1292029A1 |

| Устройство для формирования видеосигналов | 1985 |

|

SU1317473A1 |

| Устройство для отображения информации на экране электроннолучевой трубки | 1977 |

|

SU656083A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1988 |

|

SU1508272A1 |

| Устройство для отображения алфавитно-цифровой и графической информации | 1977 |

|

SU720801A1 |

| Устройство для отображения информации на газоразрядной индикаторной панели | 1983 |

|

SU1119065A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1339627A1 |

| Устройство для отображения информации на газоразрядной индикаторной панели | 1989 |

|

SU1605279A2 |

| Устройство для отображения информации на телевизионном индикаторе | 1983 |

|

SU1091216A1 |

| Устройство для отображения информации на телевизионном индикаторе | 1987 |

|

SU1495845A1 |

УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СИГНАЛОВ АЛФАВИТНО-ЦИФРОВЫХ И ГРАФИЧЕСКИХ ИЗОБРАЖЕНИЙ, содержащее синхрогенератор, блок адресных счетчиков, выходы которого соединены с соответствующими адресными выходами блока памяти, и генератор символов , отличающееся тем, что, с целью упрощения устройства путем сокращения объема памяти при сохранении функциональных возможностей и улучшения качественных параметров формируемых изображений, в него введены блок запрета смены адреса, включенный между первым выходом синхрогенератора и первым и вторым входами блока адресных счетчиков, блок формирования управляющих сигналов, блок восстановления, блок управления реверсированием символов, блок формирования сигналов цветовых компонент и цифроаналоговый преобразователь (ЦАП), при этом информационньм вход блока формирования управляющих сигналов соединен с выходом блока памяти и объединенными информационными входами блока запрета смены адреса, блока адресных счетчиков и блока восстановления, синхровход соединен с вторым выходом синхрогенератора, первый выход - с управляющим входом блока восстановления, а второй выход - с управляющими входами блока запрета смены адреса и блока адресных счетчиков, (Л первый, второй и третий выходы блока восстановления подключены к первым входам соответственно блока управления реверсированием символов, генератора символов и блока формирования сигналов цветовых компонент, а четвертый выход - к дополнительному информационному входу блока форми00 рования управляющих сигналов, третий со 4 выход синхрогенератора соединен с синхровходом блока управления реверо сированием символов, выход которого через последовательно соединенные о генератор символов и блок формирования сигналов цветовых компонент подключен к входу ЦАП.

ие.2 Переход по адресу

ЕЭШ5е1 Г ШгеЯКгК2Е:-- ;: :

fflff

ifpSffiopeffijf /tpe- ,. lsBmsi}gff4je гщ б/дуще /uifga ffelf гоп&

м / / I i й

Cpus. 3

в- 1аитсостойим 1- ti imi gfetwtfffoum -

.

.3ч

SJTfeЙ

;feb;fei

Т

/ i 1

., ...1..I. i

I

117

й Т Г 7Т7ТТ

. .

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| М | |||

| , Сов | |||

| радио, 1979, с, 256 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Под ред | |||

| М.И.Кривошеева | |||

| М., Связь, 1980, с | |||

| Бесколесный шариковый ход для железнодорожных вагонов | 1917 |

|

SU97A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-03-30—Публикация

1982-05-17—Подача