Изобретение относится к автоматике и вычислительной технике и может быть использовано для проектирования разнообразных буквенно-цифровых и графических дисплеев с отображением информации на стандартном (в том числе цветном и проекционном) телевизионном (ТВ) индикаторе.

Указанные свойства могут также найти применение при построении разнообразных ТВ синтезаторов, применяемых в вычислительной технике, технике связи, в АСУ, при построении ТВ игровых автоматов и тренажеров и т. -д., всюду, где возникает необходимость оперативного ввода и вывода буквенно-цифровой и графической информации с возможностью ее редактирования и отображения без применения и с применением вычислительных устройств.

Целью изобретения является повышение точности устройства за счет обеспечения неискаженного формирования цветных и многоградационных изображений.

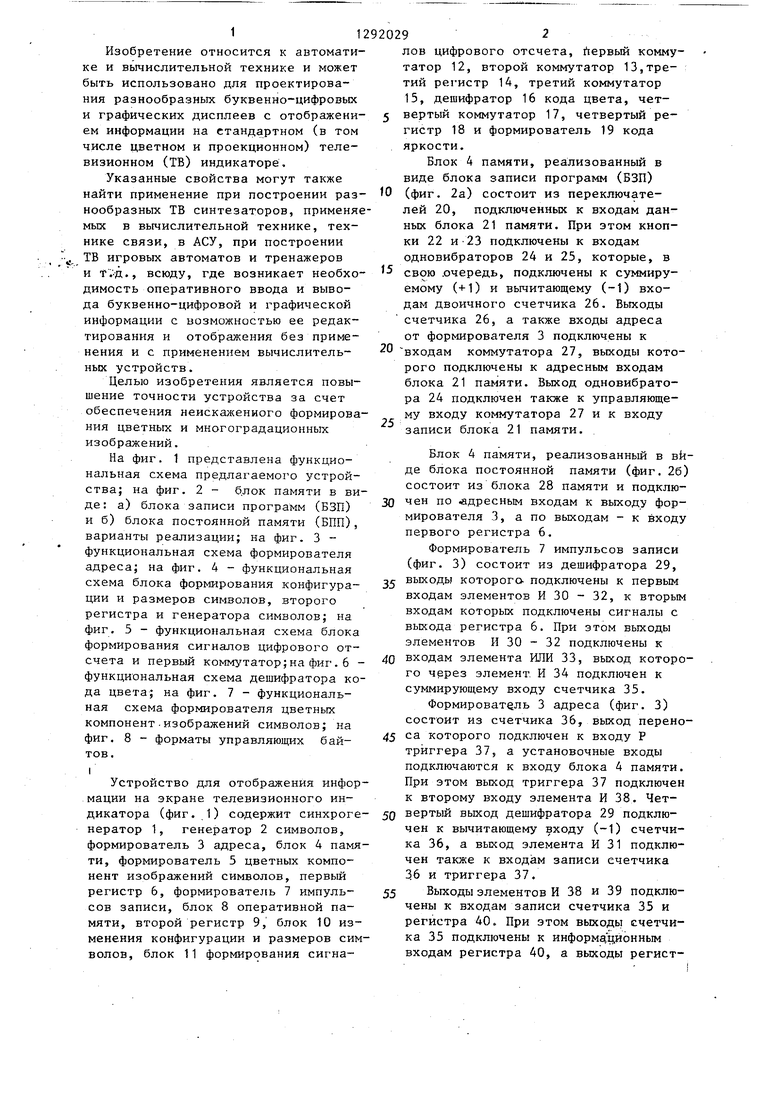

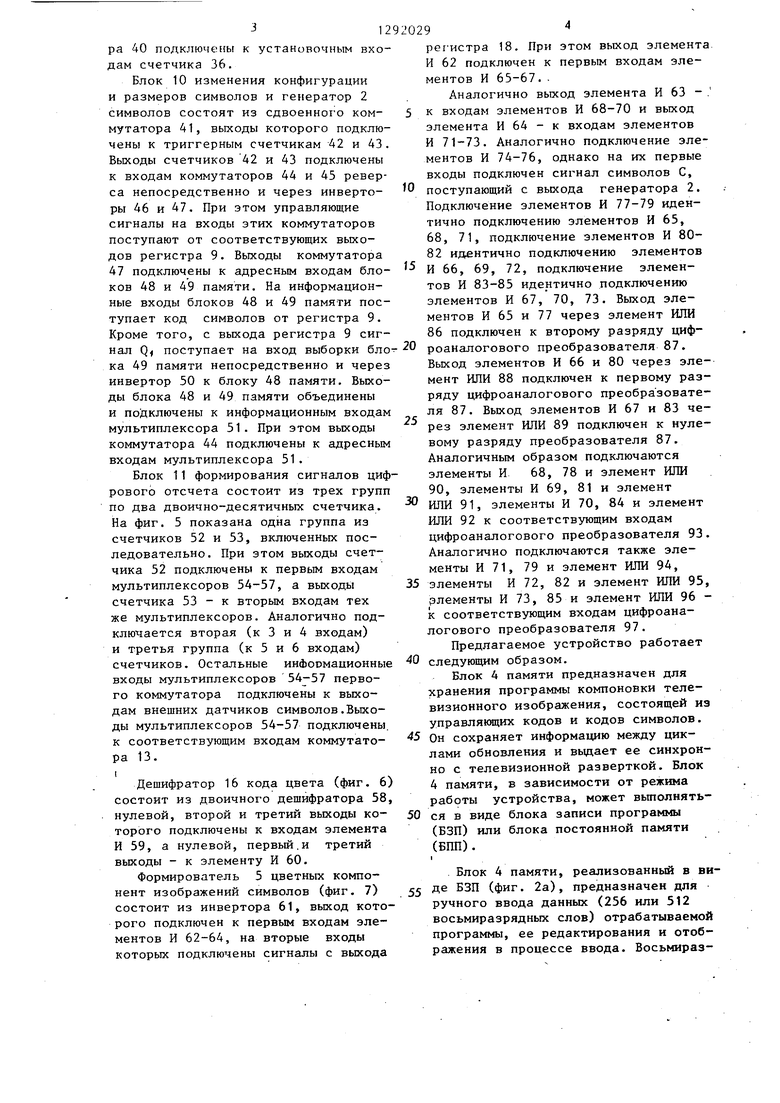

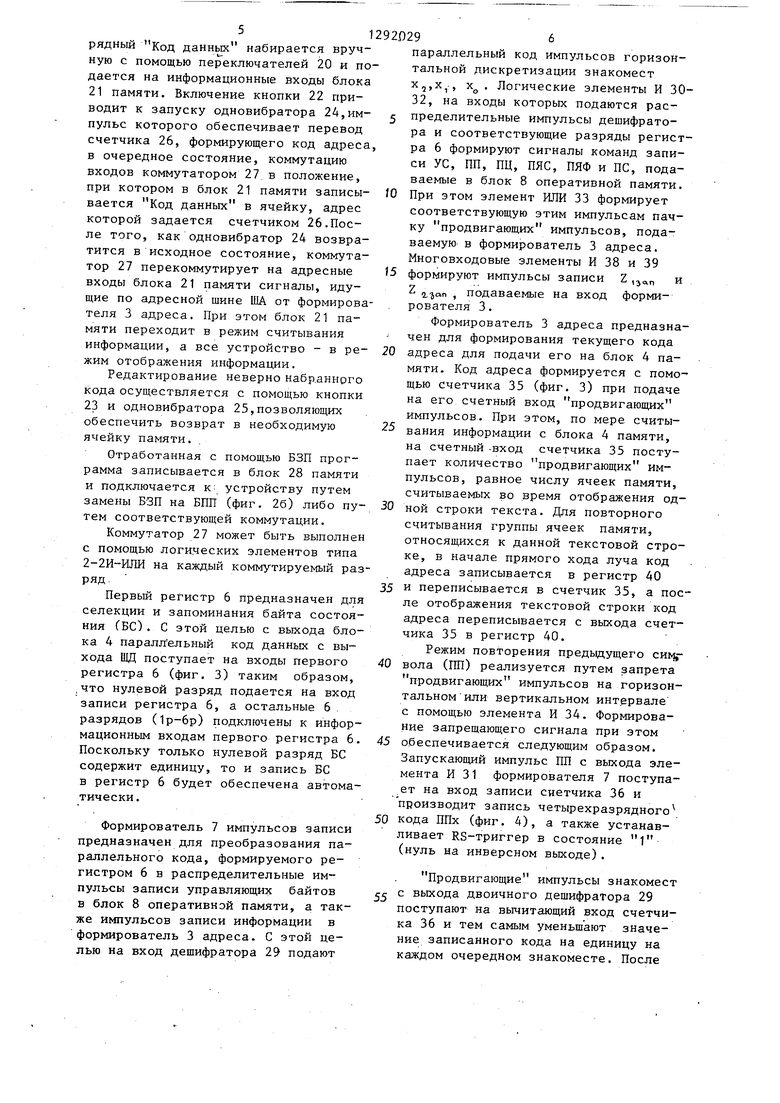

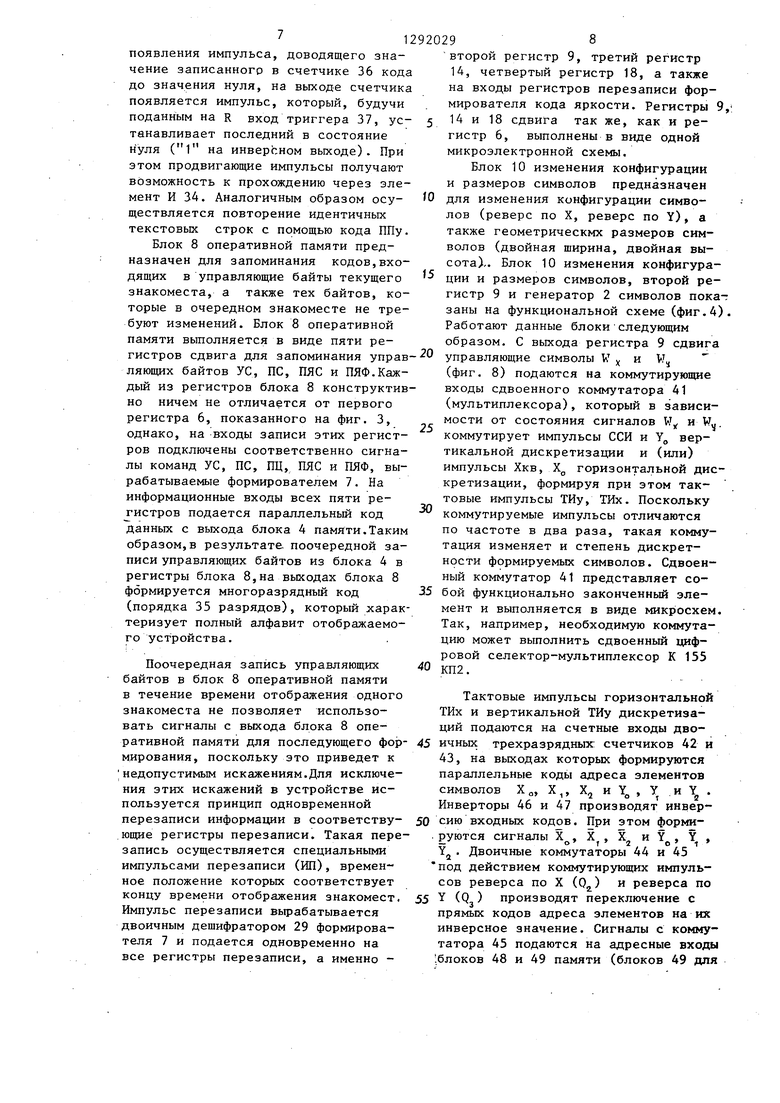

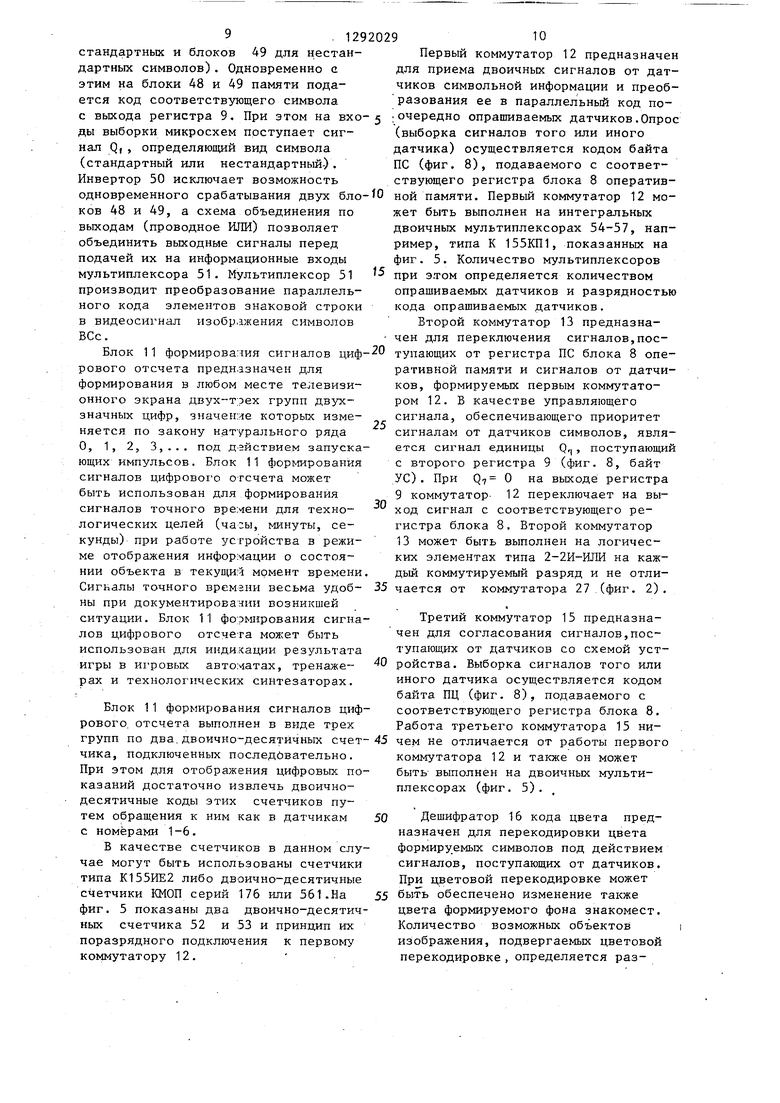

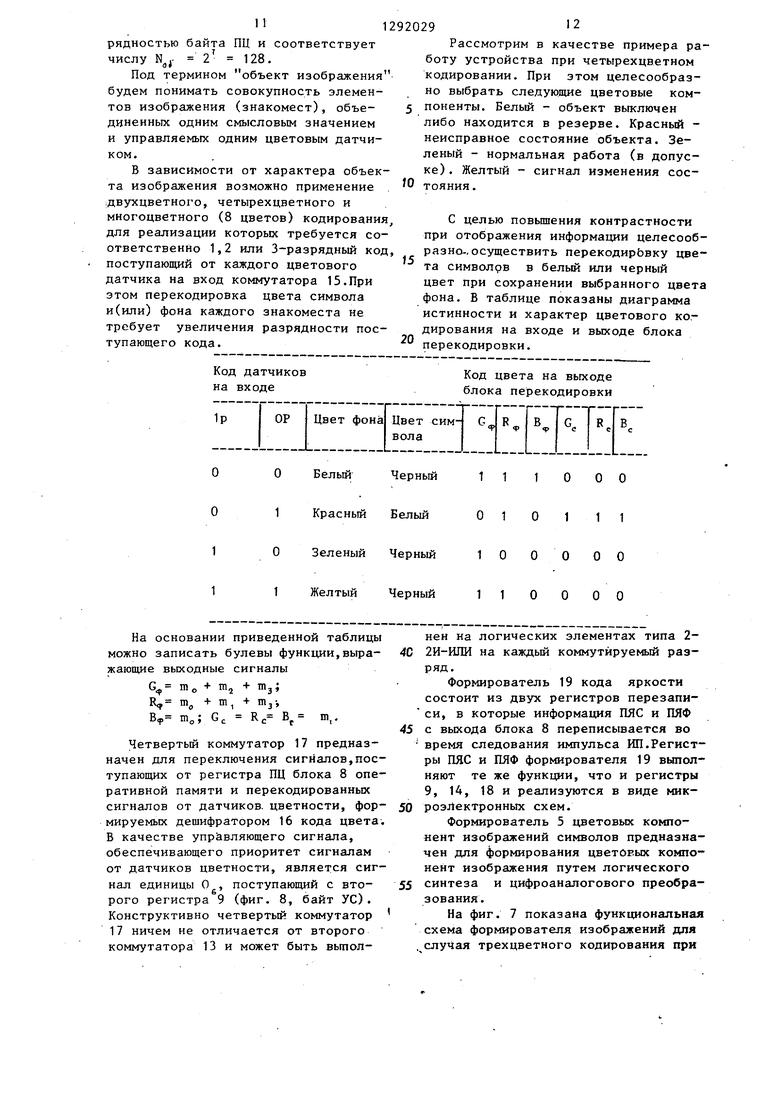

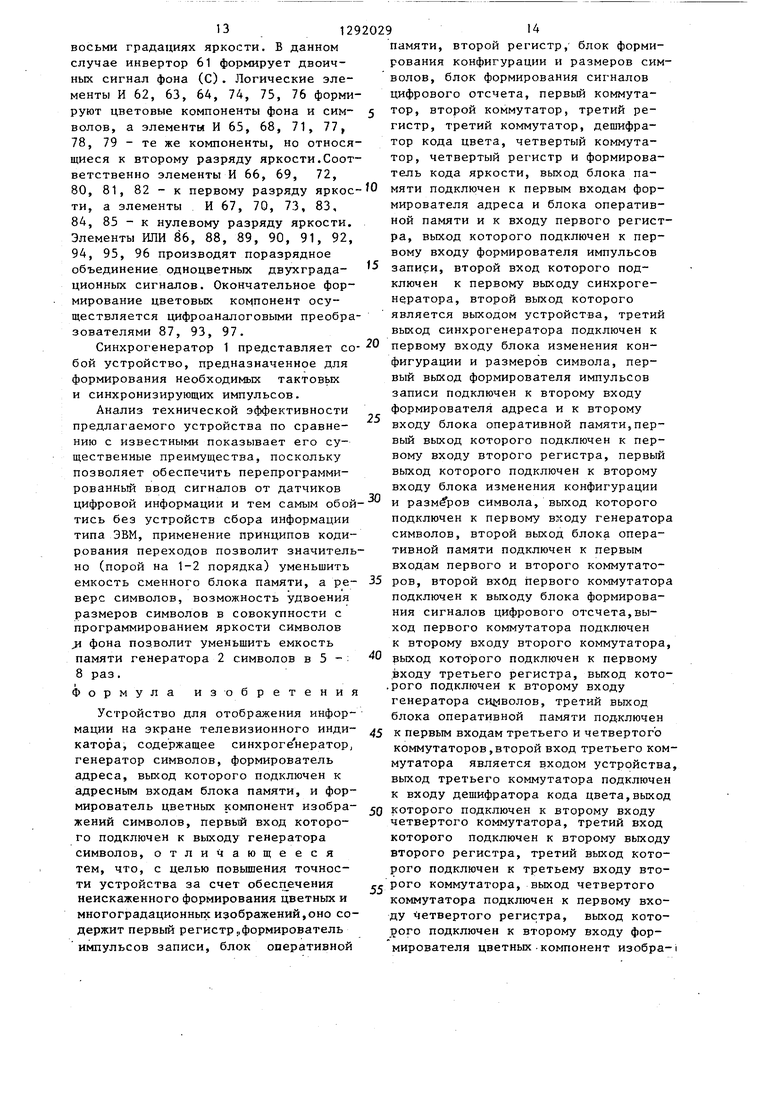

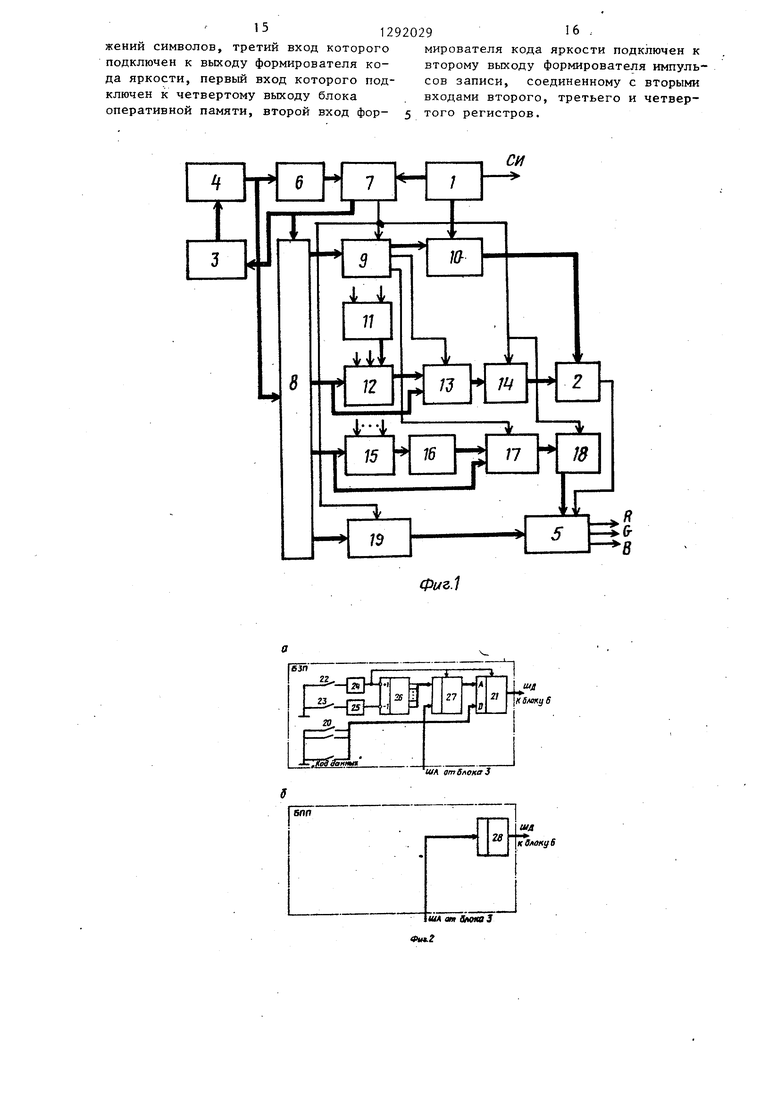

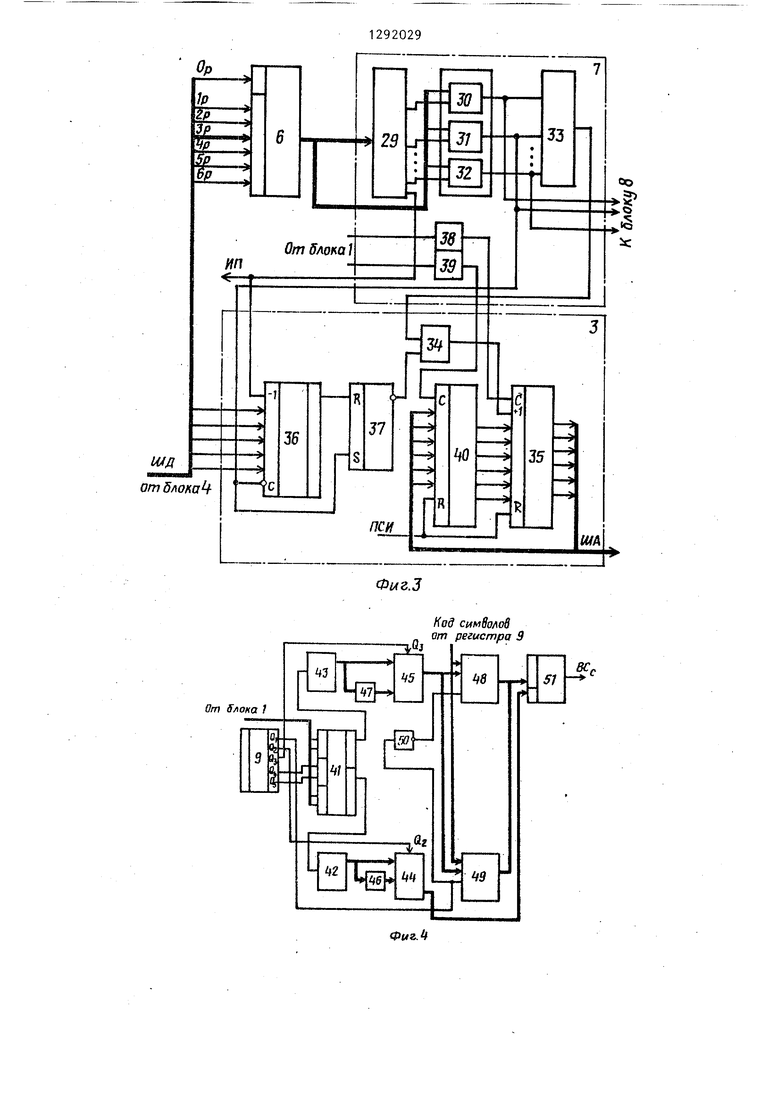

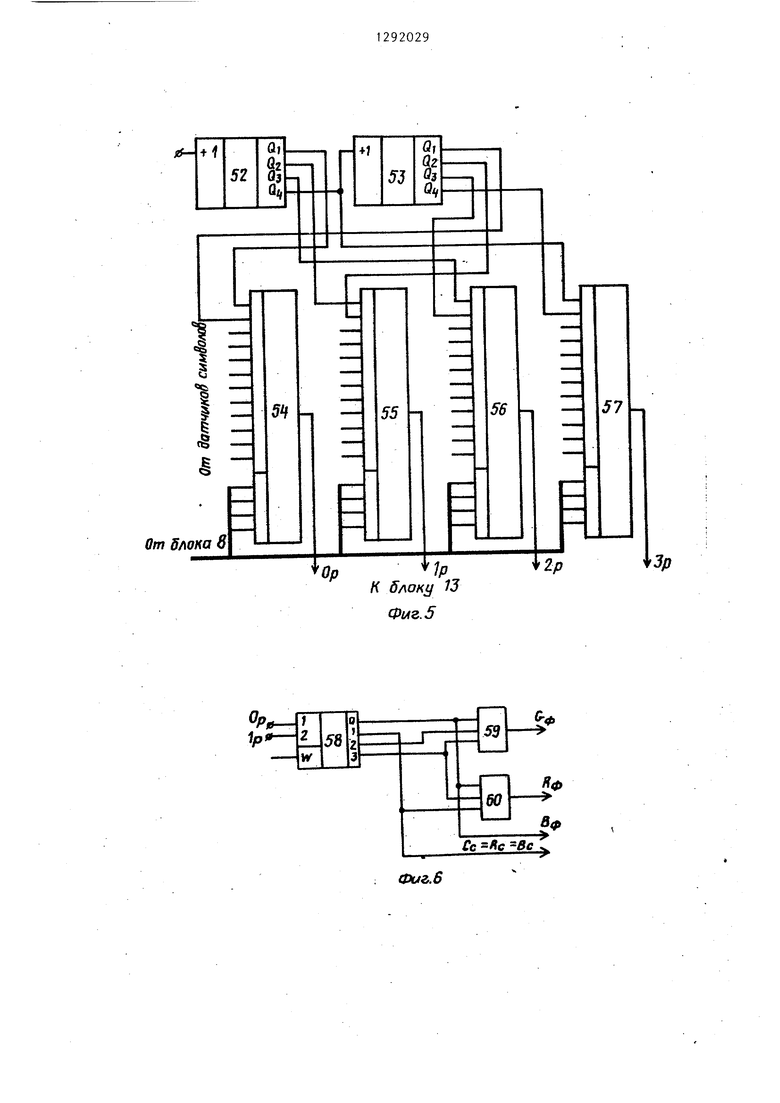

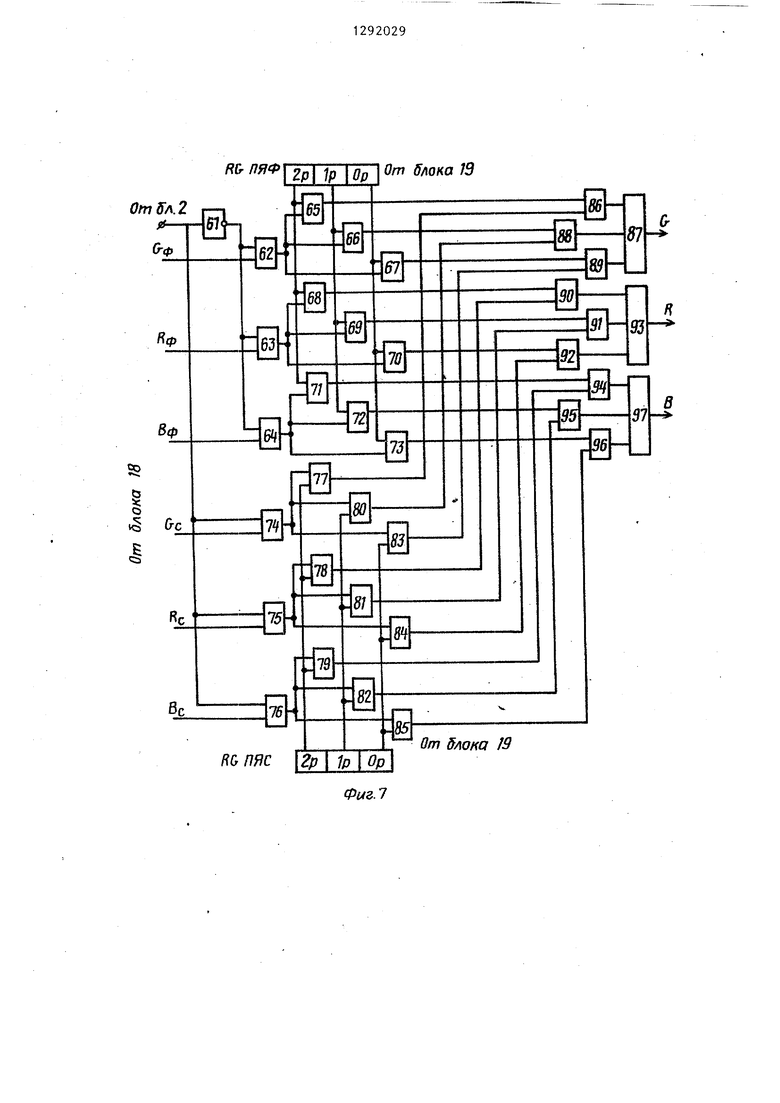

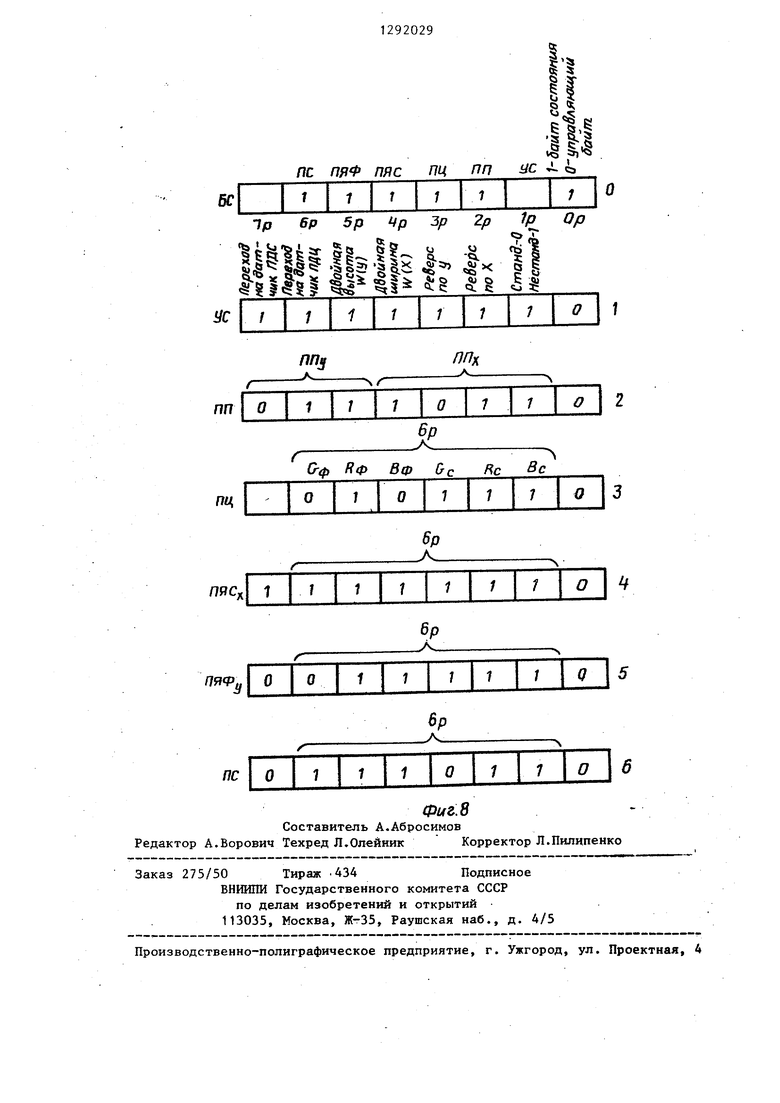

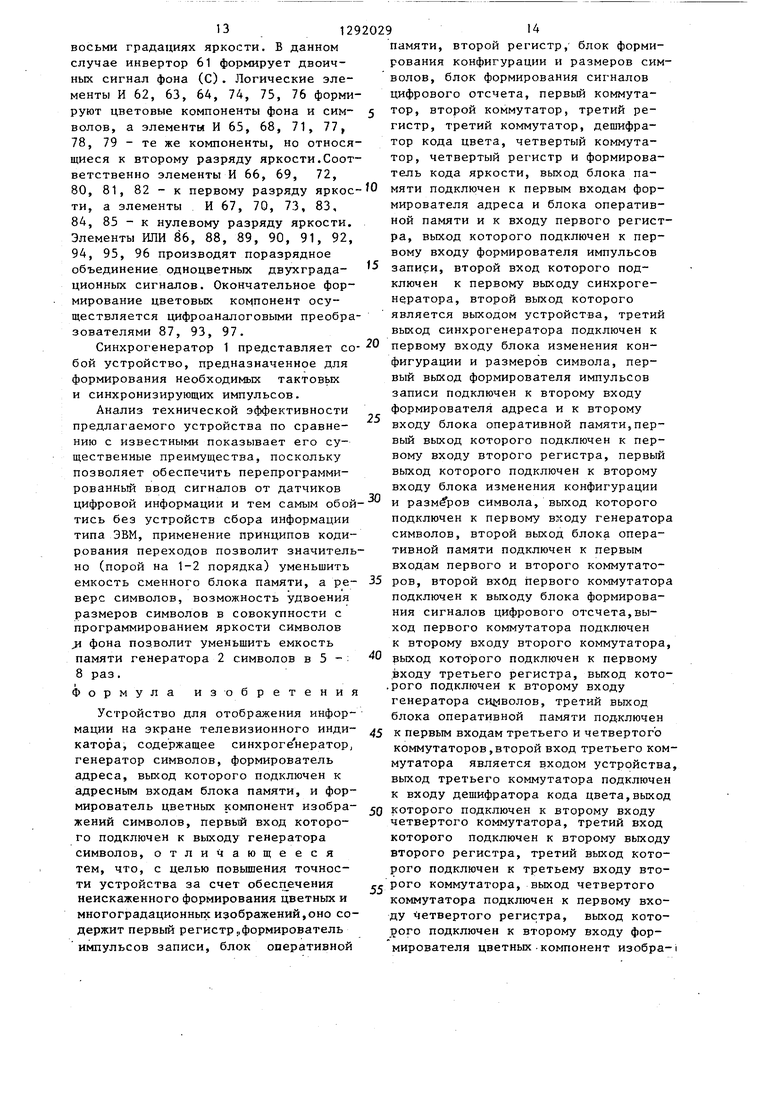

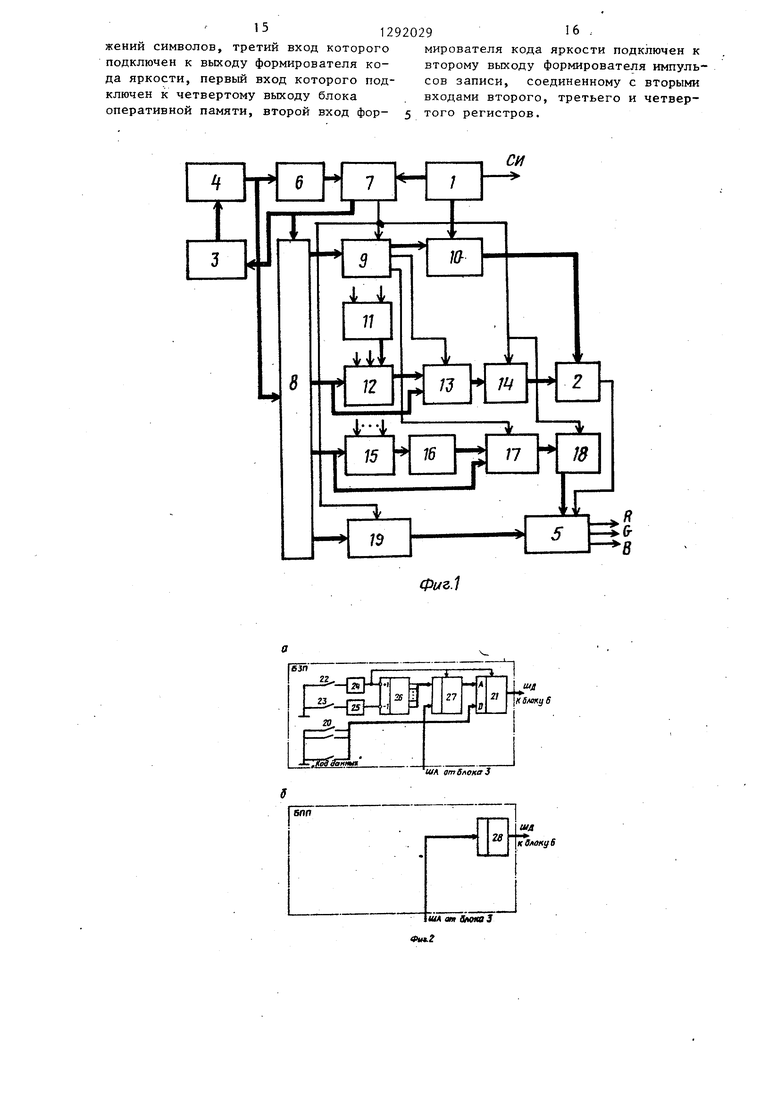

На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 - блок памяти в виде: а) блока записи программ (БЗП) и б) блока постоянной памяти (БПП), варианты реализации; на фиг. 3 - функциональная схема формирователя адреса; на фиг. 4 - функциональная схема блока формирования конфигурации и размеров символов, второго регистра и генератора символов; на фиг. 5 - функциональная схема блока формирования сигналов цифрового отсчета и первый коммутатор;на фиг. 6 - функциональная схема дешифратора кода цвета; на фиг. 7 - функциональная схема формирователя цветных компонент.изображений символов; на фиг. 8 - форматы управляющих байтов.

I

Устройство для отображения информации на экране телевизионного индикатора (фиг.1) содержит синхроге нератор 1, генератор 2 символов, формирователь 3 адреса, блок 4 памяти, формирователь 5 цветных компонент изображений символов, первый регистр 6, формирователь 7 импульсов записи, блок 8 оперативной памяти, второй регистр 9, блок 10 изменения конфигурации и размеров символов, блок 11 формирования сигналов цифрового отсчета, первый коммутатор 12, второй коммутатор 13,третий регистр 14, третий коммутатор 15, дешифратор 16 кода цвета, четвертый коммутатор 17, четвертый регистр 18 и формирователь 19 кода яркости.

Блок 4 памяти, реализованный в виде блока записи программ (БЗП)

(фиг. 2а) состоит из переключателей 20, подключенных к входам данных блока 21 памяти. При этом кнопки 22 и-23 подключены к входам одновибраторов 24 и 25, которые, в

свою .очередь, подключены к суммируемому (+1) и вычитающему (-1) входам двоичного счетчика 26. Выходы счетчика 26, а также входы адреса от формирователя 3 подключены к

входам коммутатора 27, выходы которого подключены к адресным входам блока 21 памяти. Выход одновибрато- ра 24 подключен также к управляющему входу коммутатора 27 и к входу

записи блока 21 памяти.

Блок 4 памяти, реализованный в виде блока постоянной памяти (фиг. 26) состоит из блока 28 памяти и подключен по адресным входам к выходу формирователя 3, а по выходам - к входу первого регистра 6.

Формирователь 7 импульсов записи (фиг. 3) состоит из дешифратора 29,

выходы которога подключены к первым входам элементов И 30 - 32, к вторым входам которых подключены сигналы с выхода регистра 6. При этом выходы элементов И 30 - 32 подключены к

входам элемента ИЛИ 33, выход которого через элемент, И 34 подключен к суммирующему входу счетчика 35.

Формирователь 3 адреса (фиг. 3) состоит из счетчика 36, выход переноса которого подключен к входу Р триггера 37, а установочные входы подключаются к входу блока 4 памяти. При этом выход триггера 37 подключен к второму входу элемента И 38. Четвертый выход дешифратора 29 подключен к вычитающему входу (-1) счетчика 36, а выход элемента И 31 подключен также к входам записи счетчика 36 и триггера 37.

Выходы элементов И 38 и 39 подключены к входам записи счетчика 35 и регистра 40„ При этом выходы счетчика 35 подключены к информационным входам регистра 40, а выходы регист- 12

pa 40 подключены к установочным входам счетчика 36.

Блок 10 изменения конфигурации и размеров символов и генератор 2 символов состоят из сдвоенного коммутатора 41, выходы которого подключены к триггерным счетчикам 42 и 43. Выходы счетчиков 42 и 43 подключены к входам коммутаторов 44 и 45 реверса непосредственно и через инверторы 46 и 47, При этом управляющие сигналы на входы этих коммутаторов поступают от соответствующих выходов регистра 9. Выходы коммутатора 47 подключены к адресным входам блоков 48 и 49 памяти. На информационные входы блоков 48 и 49 памяти поступает код символов от регистра 9. Кроме того, с выхода регистра 9 сигнал Q поступает на вход выборки блока 49 памяти непосредственно и через инвертор 50 к блоку 48 памяти. Выходы блока 48 и 49 памяти объединены и подключены к информационным входам мультиплексора 51. При этом выходы коммутатора 44 подключены к адресным входам мультиплексора 51.

Блок 11 формирования сигналов цифрового отсчета состоит из трех групп по два двоично-десятичных счетчика. На фиг. 5 показана одна группа из счетчиков 52 и 53, включенных последовательно. При этом выходы счетчика 52 подключены к первым входам мультиплексоров 54-57, а выходы счетчика 53 - к вторым входам тех же мультиплексоров. Аналогично подключается вторая (к 3 и 4 входам) и третья группа (к 5 и 6 входам) счетчиков. Остальные информационные входы мультиплексоров 54-57 первого коммутатора подключены к выходам внешних датчиков символов.Выходы мультиплексоров 54-57 подключены, к соответствующим входам коммутатора 13.

Дешифратор 16 кода цвета (фиг, 6) состоит из двоичного дешифратора 58, нулевой, второй и третий выходы которого подключены к входам элемента И 59, а нулевой, первый.и третий выходы - к элементу И 60.

Формирователь 5 цветных компонент изображений символов (фиг, 7) состоит из инвертора 61, выход которого подключен к первым входам элементов И 62-64, на вторые входы которых подключены сигналы с выхода

9

регистра 18. При этом выход элемента И 62 подключен к первым входам элементов И 65-67. .

Аналогично выход элемента И 63 - .

к входам элементов И 68-70 и выход элемента И 64 - к входам элементов И 71-73. Аналогично подключение элементов И 74-76, однако на их первые входы подключен сигнал символов С, поступающий с выхода генератора 2. Подключение элементов И 77-79 идентично подключению элементов И 65, 68, 71, подключение элементов И 80- 82 идентично подключению элементов

И 66, 69, 72, подключение элементов И 83-85 идентично подключению элементов И 67, 70, 73. Выход элементов И 65 и 77 через элемент ИЛИ 86 подключен к второму разряду цифроаналогового преобразователя 87, Выход элементов И 66 и 80 через элемент ИЛИ 88 подключен к первому разряду цифроансшогового преобра зовате- ля 87. Выход элементов И 67 и 83 через элемент ИЛИ 89 подключен к нулевому разряду преобразователя 87, Аналогичным образом подключаются элементы И 68, 78 и элемент ИЛИ 90, элементы И 69, 81 и элемент

ИЛИ 91, элементы И 70, 84 и элемент ИЛИ 92 к соответствующим входам цифроаналогового преобразователя 93, Аналогично подключаются также элементы И 71, 79 и элемент ИЛИ 94,

элементы И 72, 82 и элемент ИЛИ 95, элементы И 73, 85 и элемент ИЛИ 96 - к соответствующим входам цифроаналогового преобразователя 97.

Предлагаемое устройство работает

следующим образом.

Блок 4 памяти предназначен для хранения программы компоновки телевизионного изображения, состоящей из управляющих кодов и кодов символов,

Он сохраняет информацию между циклами обновления и выдает ее синхронно с телевизионной разверткой. Блок 4 памяти, в зависимости от режима работы устройства, может ньшолняться в виде блока записи программы (БЗП) или блока постоянной памяти (БПП),

1

Блок 4 памяти, реализованный в ви- де БЗП (фиг, 2а), предназначен для ручного ввода данных (256 или 512 восьмиразрядных слов) отрабатываемой программы, ее редактирования и отображения в процессе ввода. Восьмиразрядный Код данных набирается вручную с помощью переключателей 20 и подается на информационные входы блока 21 памяти. Включение кнопки 22 приводит к запуску одновибратора 2А,импульс которого обеспечивает перевод счетчика 26, формирующего код адреса в очередное состояние, коммутацию входов коммутатором 27 в положение, при котором в блок 21 памяти записывается Код данных в ячейку, адрес которой задается счетчиком 26.После того, как одновибратор 24 возвратится в исходное состояние, коммутатор 27 перекоммутирует на адресные входы блока 21 памяти сигналы, идущие по адресной шине ША от формирователя 3 адреса. При этом блок 21 памяти переходит в режим считывания информации, а все устройство - в режим отображения информации.

Редактирование неверно набр.анного кода осуществляется с помощью кнопки 23 и одновибратора 25,позволяющих обеспечить возврат в необходимую ячейку памяти.

Отработанная с помощью БЗП программа записывается в блок 28 памяти и подключается к: устройству путем замены БЗП на БПП (фиг. 26) либо путем соответствующей коммутации.

Коммутатор 27 может быть выполнен с помощью логических элементов типа 2-2И-ИЛИ на каждый коммутируемый разряд.

Первый регистр 6 предназначен для селекции и запоминания байта состояния (ЕС). С этой целью с выхода блока 4 паралл ельный код данных с выхода ШД поступает на входы первого регистра 6 (фиг. 3) таким образом, ,что нулевой разряд подается на вход записи регистра 6, а остальные 6 разрядов (1р-6р) подключены к информационным входам первого регистра 6 Поскольку только нулевой разряд БС содержит единицу, то и запись БС в регистр 6 будет обеспечена автоматически.

Формирователь 7 импульсов записи предназначен для преобразования параллельного кода, формируемого регистром 6 в распределительные импульсы записи управляющих байтов в блок 8 оперативной памяти, а также импульсов записи информации в формирователь 3 адреса. С этой целью на вход дешифратора 29 подают

5

0

5

0

5

0

5

0

параллельный код импульсов горизонтальной дискретизации знакомест х,,х,, х . Логические элементы И 30- 32, на входы которых подаются распределительные импульсы дешифратора и соответствующие разряды регистра 6 формируют сигналы команд записи УС, ПП, ПЦ, ПЯС, ПЯФ и ПС, подаваемые в блок 8 оперативной памяти. При этом элемент ИЛИ 33 формирует соответствующую этим импульсам пачку продвигающих импульсов, подаваемую в формирователь 3 адреса. Многовходовые элементы И 38 и 39 формируют импульсы записи Z ,j.«.n и Z 2.ап , подаваемые на вход формирователя 3.

Формирователь 3 адреса предназначен для формирования текущего кода адреса для подачи его на блок 4 памяти. Код адреса формируется с помощью счетчика 35 (фиг. 3) при подаче на его счетный вход продвигающих импульсов. При этом, по мере считывания информации с блока 4 памяти, на счетный -вход счетчика 35 поступает количество продвигающих импульсов, равное числу ячеек памяти, считываемых во время отображения одной строки текста. Для повторного считывания группы ячеек памяти, относящихся к данной текстовой строке, в начале прямого хода луча код адреса записывается в регистр 40 и переписывается в счетчик 35, а после отображения текстовой строки код адреса переписывается с выхода счетчика 35 в регистр 40.

Режим повторения предьиущего СИ1 вола (ШТ) реализуется путем запрета продвигающих импульсов на горизонтальном или вертикальном интервале с помощью элемента И 34. Формирование запрещающего сигнала при этом обеспечивается следующим образом. Запускающий импульс ПП с выхода элемента И 31 формирователя 7 поступает на вход записи снетчика 36 и производит запись четырехразрядного кода ППх (фиг. 4), а также устанавливает RS-триггер в состояние (нуль на инверсном выходе).

1 .

Продвигающие импульсы знакомест с выхода двоичного дешифратора 29 поступают на вычитающий вход счетчика 36 и тем уменьшают значение записанного кода на единицу на каждом очередном знакоместе. После

появления импульса, доводящего значение записанного в счетчике 36 кода до значения нуля, на выходе счетчика появляется импульс, который, будучи поданным на R вход триггера 37, устанавливает последний в состояние н уля (1 на инверсном выходе). При этом продвигающие импульсы получают возможность к прохождению через элемент И 34. Аналогичным образом осуществляется повторение идентичных текстовых строк с помощью кода ППу.

Блок 8 оперативной памяти предназначен для запоминания кодов,входящих в управляющие байты текущего знакоместа, а также тех байтов, которые в очередном знакоместе не требуют изменений. Блок 8 оперативной памяти выполняется в виде пяти регистров сдвига для запоминания управ

ляющих байтов УС, ПС, ПЯС и ПЯФ.Каждый из регистров блока 8 конструктивно ничем не отличается от первого регистра 6, показанного на фиг. 3, однако, на входы записи этих регистров подключены соответственно сигналы команд УС, ПС, ПЦ, ПЯС и ПЯФ, вырабатываемые формирователем 7. На информационные входы всех пяти регистров подается параллельный код данных с выхода блока 4 памяти.Таким образом,в результате поочередной записи управляющих байтов из блока 4 в регистры блока 8,на выходах блока 8 формируется многоразрядный код (порядка 35 разрядов), который характеризует полный алфавит отображаемого устройства.

Поочередная запись управляющих байтов в блок 8 оперативной памяти в течение времени отображения одного знакоместа не позволяет использовать сигналы с выхода блока 8 опе

ративной памяти для последующего фор- 45 ичных трехразрядных счетчиков 42 и

мирования, поскольку это приведет к ;недопустимым искажениям.Для исключения этих искажений в устройстве используется принцип одновременной перезаписи информации в соответствующие регистры перезаписи. Такая перезапись осуществляется специальными импульсами перезаписи (ИП), временное положение которых соответствует концу времени отображения знакомест. Импульс перезаписи вьфабатывается двоичным дешифратором 29 формирователя 7 и подается одновременно на все регистры перезаписи, а именно t5

второй регистр 9, третий регистр 14, четвертый регистр 18, а также на входы регистров перезаписи формирователя кода яркости. Регистры 9,

5 14 и 18 сдвига так же, как и регистр 6, выполнены в виде одной микроэлектронной схемы.

Блок 10 изменения конфигурации и размеров символов предназначен

JO для изменения конфигурации символов (реверс по X, реверс по Y), а также геометрическмх размеров символов (двойная ширина, двойная высота),. Блок 10 изменения конфигурации и размеров символов, второй регистр 9 и генератор 2 символов показаны на функциональной схеме (фиг.4). Работают данные блоки следующим образом. С выхода регистра 9 сдвига -20 управляющие символы W и V,, (фиг. 8) подаются на коммутирующие входы сдвоенного коммутатора 41 (мультиплексора), который в зависимости от состояния сигналов W и W. коммутирует импульсы ССИ и У вертикальной дискретизации и (или) импульсы Хкв, Xjj горизонтальной дискретизации, формируя при этом тактовые импульсы ТИу, ТИх. Поскольку коммутируемые импульсы отличаются по частоте в два раза, такая коммутация изменяет и степень дискретности формируемых символов. Сдвоенный коммутатор 41 представляет со35 бой функционально законченный элемент и выполняется в виде микросхем. Так, например, необходимую коммутацию может выполнить сдвоенный цифровой селектор-мультиплексор К 155

40 КП2.

Тактовые импульсы горизонтальной ТИх и вертикальной ТИу дискретизаций подаются на счетные входы дво30

43, на выходах которых формируются параллельные коды адреса элементов

символов

X.

Х„ и Y.

и

1 2 -о т

Инверторы 46 и 47 производят инвер- сию входных кодов. При этом формируются сигналы X

Х- и Y.

Y,j . Двоичные коммутаторы 44 и 45 под действием коммутирующих импульсов реверса по X (.Q) и реверса по 55 Y (Q ) производят переключение с прямых кодов адреса элементов на их инверсное значение. Сигналы с коммутатора 45 подаются на адресные входы блоков 48 и 49 памяти (блоков 49 для

9. 1292029

стандартных и блоков 49 для нестандартных символов). Одновременно с этим на блоки 48 и 49 памяти подается код соответствующего символа с выхода регистра 9, При этом на вхо-j ды выборки микросхем поступает сигнал QI , определяющий вид символа (стандартный или нестандартный-). Инвертор 50 исключает возможность

одновременного срабатывания двух ной памяти. Первый коммутатор 12 моков 48 и 49, а схема объединения по выходам (проводное ИЛИ) позволяет объединить выходные сигналы перед подачей их на информационные входы мультиплексора 51. Мультиплексор 51 производит преобразование параллельного кода элементов знаковой строки в видеосигнал изображения символов ВСс.

Блок 11 формирования сигналов циф--20 тупающих от регистра ПС блока 8 оперового отсчета предназначен для формирования в любом месте телевизионного экрана двух-трех групп двухзначных цифр, значен: 1е которых изменяется по закону натурального ряда О, 1, 2, 3,... под действием запускающих импульсов. Блок 11 формирования сигналов цифрового отсчета может быть использован для формирования сигналов точного времени для технологических целей (часы, минуты, секунды) при работе устройства в режиме отображения информации о состоянии объекта в текущий момент времени Сигналы точного времени весьма удобны при документировании возникшей ситуации. Блок 11 фо:рш1рования сигналов цифрового отсчета может быть использован для инди.кации результата игры в игровых автоматах, тренажерах и технологических синтезаторах.

Блок 11 формирования сигналов цифрового, отсчета выполнен в виде трех

групп по два.двоично-десятичных счет-45 чем не отличается от работы первого

коммутатора 12 и также он может быть выполнен на двоичных мультиплексорах (фиг. 3).

Дешифратор 16 кода цвета предназначен для перекодировки цвета формируемых символов под действием сигналов, поступающих от датчиков. При цветовой перекодировке может быть обеспечено изменение также цвета формируемого фона знакомест. Количество возможных объектов изображения, подвергаемьк цветовой перекодировке , определяется разчика, подключенных последовательно. При этом для отображения цифровых показаний достаточно извлечь двоично- десятичные коды этих счетчиков путем обращения к ним как в датчикам 50 с номерами 1-6.

В качестве счетчиков в данном случае могут быть использованы счетчики типа К155ИЕ2 либо двоично-десятичные счетчики КМОП серий 176 или 561.На 55 фиг. 5 показаны два двоично-десятичных счетчика 52 и 53 и принцип их поразрядного подключения к первому коммутатору 12.

10

Первый коммутатор 12 предназначен для приема двоичных сигналов от датчиков символьной информации и преобразования ее в параллельный код по- ;очередно опрашиваемых датчиков.Опрос (выборка сигналов того или иного датчика) осуществляется кодом байта ПС (фиг. 8), подаваемого с соответствующего регистра блока 8 оператив

жет быть выполнен на интегральных двоичных мультиплексорах 54-57, например, типа К 155КП1, показанных на фиг. 5. Количество мультиплексоров при Э.ТОМ определяется количеством опрашиваемых датчиков и разрядностью кода опрашиваемых датчиков.

Второй коммутатор 13 предназначен для переключения сигналов,пос5

0

ративной памяти и сигналов от датчиков, формируемых первым коммутатором 12. В качестве управляющего сигнала, обеспечивающего приоритет сигналам от датчиков символов, является сигнал единицы Q,|, поступающий с второго регистра 9 (фиг. 8, байт УС). При Q7 О на выходе регистра 9 коммутатор- 12 переключает на выход сигнал с соответствующего регистра блока 8. Второй коммутатор 13 может быть выполнен на логических элементах типа 2-2И-ИЛИ на каждый коммутируемый разряд и не отли- 5 чается от коммутатора 27 (фиг. 2).

Третий коммутатор 15 предназна- чен для согласования сигналов,поступающих от датчиков со схемой уст- 0 ройства. Выборка сигналов того или иного датчика осуществляется кодом байта ПЦ (фиг. 8), подаваемого с соответствующего регистра блока 8. Работа третьего коммутатора 15 нирядностью байта ПЦ и соответствует числу N,,- 2 128,

Под термином объект изображения будем понимать совокупность элементов изображения (знакомест), объединенных одним смысловым значением и управляемых одним цветовым датчиком.

В зависимости от характера объекта изображения возможно применение двухцветного, четырехцветного и многоцветного (8 цветов) кодирования для реализации которых требуется соответственно 1,2 или 3-разрядный код поступающий от каждого цветового датчика на вход коммутатора 15.При этом перекодировка цвета символа и(или) фона каждого знакоместа не требует увеличения разрядности поступающего кода.

Код датчиков на входе

На основании приведенной таблицы можно записать булевы функции,выражающие выходные сигналы

Гоо m, т„;

3

н TOj + m и m, + , GC RC B,

m.

Четвертый коммутатор 17 предназначен для переключения сигналов,поступающих от регистра ПЦ блока 8 оперативной памяти и перекодированных сигналов от датчиков, цветности, формируемых дешифратором 16 кода цвета. В качестве управляющего сигнала, обеспечивающего приоритет сигналам от датчиков цветности, является сигнал единицы О , поступающий с второго регистра 9 (фиг. 8, байт УС). Конструктивно четвертый коммутатор 17 ничем не отличается от второго коммутатора 13 и может быть вьтол0

5

0

Рассмотрим в качестве примера работу устройства при четырехцветном кодировании. При этом целесообразно выбрать следующие цветовые компоненты. Белый - объект выключен либо находится в резерве. Красный - неисправное состояние объекта. Зеленый - нормальная работа (в допуске) . Желтый - сигнал изменения состояния .

С целью повьппения контрастности при отображения информации целесообразно- осуществить перекодирЬвку цвета символрв в белый или черный цвет при сохранении выбранного цвета фона. В таблице показаны диаграмма истинности и характер цветового ко,- дирования на входе и выходе блока перекодировки.

Код цвета на выходе блока перекодировки

нен на логических элементах типа 2- 2И-ИЛИ на каждый коммутируемый разряд.

Формирователь 19 кода яркости состоит из двух регистров перезапи- си, в которые информация ПЯС и ПЯФ с выхода блока 8 переписывается во время следования импульса ИП.Регистры ПЯС и ПЯФ формирователя 19 выполняют те же функции, что и регистры 9, 14, 18 и реализуются в виде мик- роэЛектронных схем.

Формирователь 5 цветовых компонент изображений символов предназначен для формирования цветовых компонент изображения путем логического синтеза и цифроаналогового преобразования.

На фиг. 7 показана функциональная схема формирователя изображений для случая трехцветного кодирования при

восьми градациях яркости. Б данном случае инвертор 61 формирует двоичных сигнал фона (С). Логические элементы И 62, 63, 64, 74, 75, 76 формируют цветовые компоненты фона и символов, а элементы И 65, 68, 71, 77, 78, 79 - те же компоненты, но относящиеся к второму разряду яркости.Соответственно элементы И 66, 69, 72,

памяти, второй регистр, блок формирования конфигурации и размеров символов, блок формирования сигналов цифрового отсчета, первый коммутатор, второй коммутатор, третий регистр, третий коммутатор, дешифратор кода цвета, четвертый коммутатор, четвертый регистр и формирователь кода яркости, выход блока па80, 81, 82 - к первому разряду яркое- О мяти подключен к первым входам форти, а элементы И 67, 70, 73, 83, 84, 85 - к нулевому разряду яркости. Элементы ИЛИ 86, 88, 89, 90, 91, 92, 94, 95, 96 производят поразрядное объединение одноцветных двухграда- ционных сигналов. Окончательное формирование цветовых компонент осуществляется цифроаналоговыми преобразователями 87, 93, 97.

мирователя адреса и блока оперативной памяти и к входу первого регист ра, выход которого подключен к первому входу формирователя импульсов 5 записи, второй вход которого подключен к первому выходу синхроге- нератора, второй выход которого является выходом устройства, третий выход синхрогенератора подключен к

Синхрогенератрр 1 представляет со- первому входу блока изменения конбой устройство, предназначенное для формирования необходимых тактовьк и синхронизирующих импульсов.

Анализ технической эффективности предлагаемого устройства по сравнению с известными показывает его существенные преимущества, поскольку позволяет обеспечить перепрограммированный ввод сигналов от датчиков цифровой информации и тем самым обойтись без устройств сбора информации типа ЭВМ, применение принципов кодирования переходов позволит значительно (порой на 1-2 порядка) уменьшить емкость сменного блока памяти, а ре вере символов, возможность удвоения размеров символов в совокупности с программированием яркости символов ji фона позволит уменьшить емкость памяти генератора 2 символов в 5 -: 8 раз. Формула изобретения

Устройство для отображения информации на экране телевизионного индикатора, содержащее синхроге нератор, генератор символов, формирователь адреса, вьсход которого подключен к адресным входам блока памяти, и формирователь цветных компонент изображений символов, первый вход которого подключен к выходу генератора символов, отличающееся тем, что, с целью повьшения точности устройства за счет обеспечения неискаженного формирования цветных и многоградационных изображений,оно содержит первый регистр ..формирователь импульсов записи, блок оперативной

-

памяти, второй регистр, блок формирования конфигурации и размеров символов, блок формирования сигналов цифрового отсчета, первый коммутатор, второй коммутатор, третий регистр, третий коммутатор, дешифратор кода цвета, четвертый коммутатор, четвертый регистр и формирователь кода яркости, выход блока памирователя адреса и блока оперативной памяти и к входу первого регистра, выход которого подключен к первому входу формирователя импульсов записи, второй вход которого подключен к первому выходу синхроге- нератора, второй выход которого является выходом устройства, третий выход синхрогенератора подключен к

25

30

35

фигурации и размеров символа, первый выход формирователя импульсов записи подключен к второму входу формирователя адреса и к второму входу блока оперативной памяти,первый выход которого подключен к первому входу второго регистра, первый выход которого подключен к второму входу блока изменения конфигурации и размеров символа, выход которого подключен к первому входу генератора символов, второй выход блока оперативной памяти подключен к первым входам первого и второго коммутаторов, второй вход первого коммутатора подключен к выходу блока формирования сигналов цифрового отсчета,выход первого коммутатора подключен к второму входу второго коммутатора, выход которого подключен к первому

йходу третьего регистра, выход которого подключен к второму входу генератора си 1волов, третий выход блока оперативной памяти подключен к первым входам третьего и четвертого коммутаторов, второй вход третьего коммутатора является входом устройства, выход третьего коммутатора подключен к входу дешифратора кода цвета,выход которого подключен к второму входу четвертого коммутатора, третий вход которого подключен к второму выходу второго регистра, третий выход которого подключен к третьему входу вто- гс рого коммутатора, выход четвертого коммутатора подключен к первому входу четвертого регистра, выход которого подключен к второму входу формирователя цветных-компонент изобра-i

40

45

50

151292029 6 жений символов, третий вход которого мирователя кода яркости подключен к подключен к выходу формирователя ко- второму выходу формирователя импуль- да яркости, первый вход которого под- сов записи, соединенному с вторыми ключен к четвертому выходу блока входами второго, третьего и четвер- оперативной памяти, второй вход фор- з того регистров.

Фиг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования видеосигналов | 1985 |

|

SU1317473A1 |

| Устройство для отображения информации на газоразрядной индикаторной панели | 1989 |

|

SU1605279A2 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| Устройство для отображения графической информации на телевизионном индикаторе | 1983 |

|

SU1161985A1 |

| Устройство для отображения информации на газоразрядной индикаторной панели | 1983 |

|

SU1119065A1 |

| Формирователь символов для устройств отображения информации на матричных экранах | 1989 |

|

SU1688280A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1695372A1 |

| Устройство для отображения информации на газоразрядной индикаторной панели переменного тока | 1989 |

|

SU1793458A1 |

| Устройство для формирования сигналов алфавитно-цифровых и графических изображений | 1982 |

|

SU1083406A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1986 |

|

SU1427412A1 |

Изобретение относится к электронному синтезу изображений на ТВ- растре и может быть использовано при построении разнообразных ситуационных дисплеев, ТВ-тренажеров и игровых автоматов и всюду, где необходимо формировать сложные изображения, Целью изобретения является повьппе- ние точности устройства за счет обеспечения неискаженного формирования цветных и многоградационных изображений. Устройство содержит синхроге- нератор, генератор символов, формирователь адреса, блок памяти,формирователь цветных компонент изображений символов, первый, второй, третий и четвертый регистры, формирователь иьтульсов записи, блок оперативной памяти, блок изменения конфигурации и размеров символов, первый, второй, третий и четвертый коммутаторы, дешифратор кода цвета и формирователь кода яркости. Устройство позволяет формировать сложные цветные и многоградационные изображения. В ил. 1 табл. (/)

КИмкуб

шл ателояаЗ

snn

ша

квлакуб

ША аа Икот 3 ачн.г

Фиг.З

Код Символов от регистра 9

51

К,

+ f

52

Oi

а

1

5it

с§ I

От длока в

К блоку 13

Фиг. 5

+J

5-J

Ov

55

55

57

t2p

Зр

Фи&.6

ПЯФ

Zp IP 5/ioKO 75

От Ул. 2

::б5

G-ф

87

Кф

&t

Ос

77К

78

93

97

В

73

1 -

6г

; Фиг. 7

От лока 19

IP

Op

Фиг.8

Составитель А.Абросимов Редактор А.Ворович Техред Л.ОлеЙник Корректор Л.Пилипенко

Заказ 275/50 Тираж .434Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для отображения информации | 1975 |

|

SU540271A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1976 |

|

SU633042A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1987-02-23—Публикация

1984-07-11—Подача