входов блока памяти, группа выходов которого подключена соответственно к группе управляющих входов второго .коммутатора, и блок задания законов распределений, состоящий из идентичш узлов, каакдый из который содержит группу регистров, группу сумматоров, группу схем сравнения, первую и вторую группы элементов И, в каждом узле выходы первого регистра группы соединены с первыми входами соответствующих элементов И первой группы, выходы К-го регистра группы (к 2 п) соединены соответственно с входами первой группы (к-1)-го сумматора группы, вторая группа входов первого сумматора группы соединена соответственно с выхода й1 первого регистра группы, вторая группа входов М-го сумматора группы (, п-1) соединена соответственно с выходами {М-1)-го сумматора группы, выходы всех сумматоров группы подключены к первым входам соответствукицих элементов И первой группы, выходы которых соединены с входами первой группы соответствующих схем сравнения группы, выход К-й схемы сравнения группы соединен с прямым входом (K-l)-ro элемента И второй группы, выход Р-й схемы сравнения группы (, n-l) подключен к Р-м инверсным входам элементов И второй группы с номером, болыпим Р, выход первой схемеы сравнения группы и выходы элементов И всех узлов блока задания законов распределения подключены соответственно к входам первого коммутатора, входы второй группы схем сравнения узла блока задания закона распределения подключены соответственно к выходам генератора случайного кода, выходы регистров группы блока задания закона распределения подключены соответственно к второй группе информационных входов второго коммутатора, выходы блока памяти подключены к вто рым входам элементов И первой группы соответствующего узла блока задания закона распределения, отличающееся тем, что, с целью расширения функциональных возможностей устройства за сч€т моделирования процессов искажений передаваемых сообщений, оно дополнительно содержит генератор сообщений, блок анализа сообщений, состоящий из четырех элементов ИЛИ, трех элементов И, первой и второй групп элементов И, четырех регисров и трех групп регистраторов, причем в блоке анализа сообщений одноименные входы первого и второго элементов НПИ объединены и соединены с входами соответствующих регистраторов первой группы, выход первого элемента ИЛИ подключен к входу первого регистратора, вькод второго элемента ИЛИ подключен к первым входам первого, второго, третьего элементов И, выходы которых соединены соответственно с входами второго, третьего и четвертого регистраторов, выход третьего элемента ИЛИ соединен с первь1ми входами элементов И первой группы, вторые входы которых подключены соответственно к входам первого элемента ИЛИ, выход четвертого элемента ИЛИ подключен к второму входу третьего элемента И и первым входам элементов И второй группы, вторые входы которых подключены соответственно к входам первого элемента ИЛИ и выходам генератора сообщений, второй вход первого элемента И и входы третьего и четвертого элементов ИЛИ соединены соответственно с выходами блока памяти, к блок задания матри переходных вероятностей, состоящий из группы узлов памяти и коммутатора, информационные входы которого подключены соответственно к выходам узлов памяти, группа управляющих входов кo yтaтopa подключена соответственно к выходам генератора сообщений, группа выходов коммутатора блока задания матриц переходных вероятностей соединена соответственно с входами регистров групт пы блока задания закона распределения. Изобретение относится к вычислительной технике и может быть использовано для моделирования каналов передачи дискретной информации при стационарных распределениях потоков сообщений,а также в качестве анали.. зируниЦего устройства передаваемого сообщения в канале связи. Известно устройство для моделирования марковских процессов, содержаще .генератор пуассоновского потока импульсов, элемент И, регистр, блок элементов И, блок элементов ИЛИ, бло запоминающих логических элементов, причем выход генератора пуассоновско го потока импульсов соединен с первы входом элемента И, выход которого со единен ,с первым входом регистра, пер вый вход которого соединен с вт,орым входом регистра, вторые выходы которого соединены с первыми входами блока матрицы логических.элементов, .выходы которого соединены через блок элементов ИЛИ с первыми входами блок элементов И, вторые входы которого соединены с выходом генератора тактовых импульсов и вторьм входом элемента И, а выходы соединены с входами блока запоминающих логических эле ментов, которого соединены со ответственно со вторыми входами блока матрицы логических элементов и с выходами устройства СЪ Недостаток известного устройства состоит в том, что его нельзя исполь зовать для моделирования процесса пе редачи и искажения кодов в канапе пе редачи дискретной информации как мар ковского процесса, также не учитывается время пребывания устройства в каждом состоянии, что ограничивает функциональные возможности известног устройства. Известно устройство для моделироваИия марковских процессов, содержащее генератор тактовых импульсов, первый генератор случайных импульсов выход которого соединен с первым вхо дом первого элемента И, второй вход которого соединен с выходом генерато ра тактовых импульсов, первый и втор блоки элементов И, блок матрицы логических элементов, блок запоминающих логических элементов, каждая ячейк 1 которого состоит из триггера и элемента ИЛИ, регистр, входы которого соединены соответственно с первой группой выходов блока матрицы логических элементов, вторая группа выходов которого соединена соответственно с-выходами блока запоминающих логических элементов, входы которого соединены с выходами первого блока элементов И, группа первых входов , которого объединена и подключена к выходу генератора тактовых импульtoB, вторая группа входов первого блока элементов И соединена соответственно с выходами блока логических элементов, второй и третий регистры, второй генератор случайных импульсов и второй элемент И, первый вход которого соединен с выходом второго генератора случайных импульсов, а второй вход,- с вторым входом первого элемента И и с управляющим входом третьего регистра, разрядные входы которого соединены соответственно с разрядными выходами второго регистра, вход которого соединен с выходом первого элемента И, при этом разрядные выходы третьего регистра соединены соответственно с группой информационных входов второго блока элементов И, группа управляющих входов которого объединена и подключена к выходу второго элемента И С 23. Недостаток известного устройства состоит в ограниченных функциональНых возможностях, так как при моделировании не учитывается время пребывания системы в каждом состоянии и оно не может моделировать канал передачи дискретной информации. Наиболее близким к изобретению по совокупности функциональньрс и конструктивных признаков является устройство для моделирования полумарковски}с процессов, содержащее первый и второй коммутаторы, блок памяти, блок генераторов случайных интервалов времени, блок задания законов распределений, блок генерации случайного хода, элемент И, блок задания времени ожидания, генератор тактовых импульсов, причем входы устройства соединены с первыми входами блока задания законов распределений, вторые входы которого соединены с выходами блока генерации случайного кода, вход которого соединен с входом блока генераторов случайных интервалов времени, выходом элемента И и первым икодом пер;вого коммутатора, входы которого соединены с первымн выходами блока задания законов распределений, а выходы соединены с входами блока памяти выходы которого соединены с третьими входами блока задания законов рас пределений, выходами устройства и первыми входами второго коммутатора вторые входы которого соединены с вторыми выходами блока задания заког нов распределений, третьи входы соединены с выходами блока генераторов случайных интервалов времени, а выходы.- с входами блока 10 задания времени ожидания, другой вход которого соединен с выходом генератора тактовых импульсов и первым входом элемента. И, второй вход которого соединен с выходом блока задания времени ожидания Сз 1, Недостаток известного устройства состоит в следующем. Известно, что процесс передачи и искажения кодов по каналу является марковским, причем под состоянием процесса понимается передача кода с } ошибками (, п, п, - длина кода) Возможно задать распределение ) ожидание случайного процесса э состо янии передачи сI ошибками в коде и вероятности перехода П - перехода из состояния передачи кодов с I ошиб ками в состояние передачи кодов с j ошибками. Однако функциональные возможности известного устройства ограничены, так как оно не может моделировать процесс передачи и искажения сообщений по каналу передачи дискрет ной информации. Цель изобретения - расширение функциональных возможностей за счет моделирования процессов искажений передаваемых сообщений, Цель достигается тем, что в устройство для моделирования канала передачи дискретной информации, содержащее генератор тактовых импульсов, элемент И, генератор случаййого кода, первый и второй коммутаторы блок памяти, блок генераторов случайных интервалов блок задания времени ожидания, состоядай из двух групп злементов И, двух групп элементов ИЛИ, первого и второго элементов И, триггера,.генератора тактовых импульсов, коммутатора, узла умножения, сумматора, реверсивного счетчика и дешифратора, первые входы первого и второго элементов И 064 блока задания времени ожидания соединены с выходом генератора тактовых импульсов устройства, причем в блоке задания времени ожидания выход первого элемента и блок задания времени ожидания подкдлючен к единичному входу триггера, нулевой вход которого соединен соответствующим выходом коммутатора и входом разрешения записи реверсивного счетчика, прямой выход триггера подключен к входу генератора тактовых импульсов, выход которого соединен с входом коммутатора, группа выходов которого подключена к первым входам соответствующих злементов И первой и второй группы, выходы элементов И первой группы подключены соответственно к входам злементов ИЛИ первой группы, а выходы злементов И второй группы соединены соответственно к выходам элементов ИЛИ второй группы, выходы элементов . ИЛИ первой и второй групп подключены соответственно к входам первой и второй группы узла умножения, выходы которого соединены соответственно с разрядными входами сумматора, выходы которого подключены соответственно к разрядным входам реверсивного счетчика, ш 1ходы которого соединены соответственно с входами дешифратора, выход которого соединен с установочным входом сумматора и вторым входом первого элемента И, инверсный выход триггера подключен к второму входу второго элемента И, выход которого подключен к вычитающему входу |Е еверсивного счетчика, шсход деши атора блока задания времени ожидания соединен с первым входом элемента И устройства, второй вход элемента И подключен к выходу генератора тактовых импульсов, а выход элемента И подключен к управлякщему входу первого коммутатора, входу генератора случайного кода, и входу блока генератора случайных интервалов, группа выходов которого соединена соответственно с первой группой информационных входов второго коммутатора, группа выходов которого подключена соответственно к вторым входам элемента И первой и второй групп блока задания времени ожидания, Группе выходов первого коммутатора и соединена соответственно с группой входов блока памяти, группа выходов которого подключена соответственно к группе управляющих входов второго коммутатора, и блок

51088006

задания законов распределений, состоящий из идентичных узлов, каждый из которых содержит группу регистров, группу сумматоров, группу схем сравнения, первую и вторую группы элементов И, в каждом уэле выходы первого регистра группы соединены с первыми входами соответствуюищх элементов И первой группы, выходы К-го регистра группы (, п) соединены соответственно с входами первой группы (K-l)-ro сумматора групп, вторая группа входов первого сумматора группы соединена соответственно с выходами первого регистра группы, вторая группа входов М-го сумматора Группы (, п-1) соединена соответственно с выходами (М-1)го сумматора группы выходы всех сумматоров группы подклю чены к первым входам соответствуйишх элементов И .первой группы, выходы которых соединены с входами первой груп пы соответствующих схем сравнения группы, выход К-й схемы сравнения группы соединен с прямым входом (K-l)-ro элемента И второй группы, выход Р-й схемы сравнения группы (Р, п-1) подключен к Р-м инверсным входам элементов И второй группы с номером, большим Р, выход первой схе1 ал сравнения группы и выходы элементов И всех узлов блока задания законо распределения подключены соответствен но к входам первого коммутатора, входы второй группы схем сравнения каждого узла блока задания закона распределения подключены соответственно к выходам генератора случайного кода выходы регистров группы блока задания закона распределения подключены соответственно к второй группе информационных входов второго коммутатора, выходы блока памяти подключены к вторым входам элементов И первой группы соответствующего узла блока задания закона распределения, отличающее ся тем, что, с целью расщирения функциональных возможностей устройства за счет моделирования процессов искажении передаваемых сообщений, оно дополнительно содержит генератор сообщений, блок анализа сообщений, состоящий из четырех элементов ИЛИ, трех элементов И, первой и второй групп элементов JH, четырех регистров и трех групп регистраторов, причем в блоке анализа сообщений одноименные входы первого и второго элементов ИЛИ объединены и

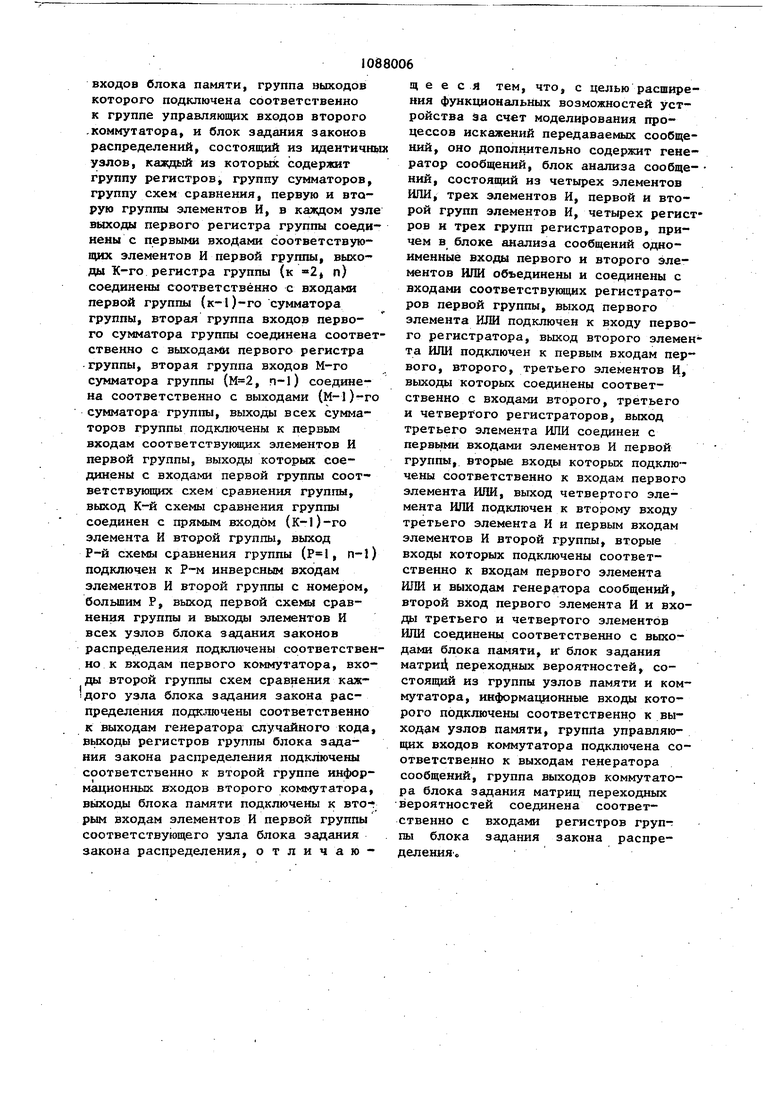

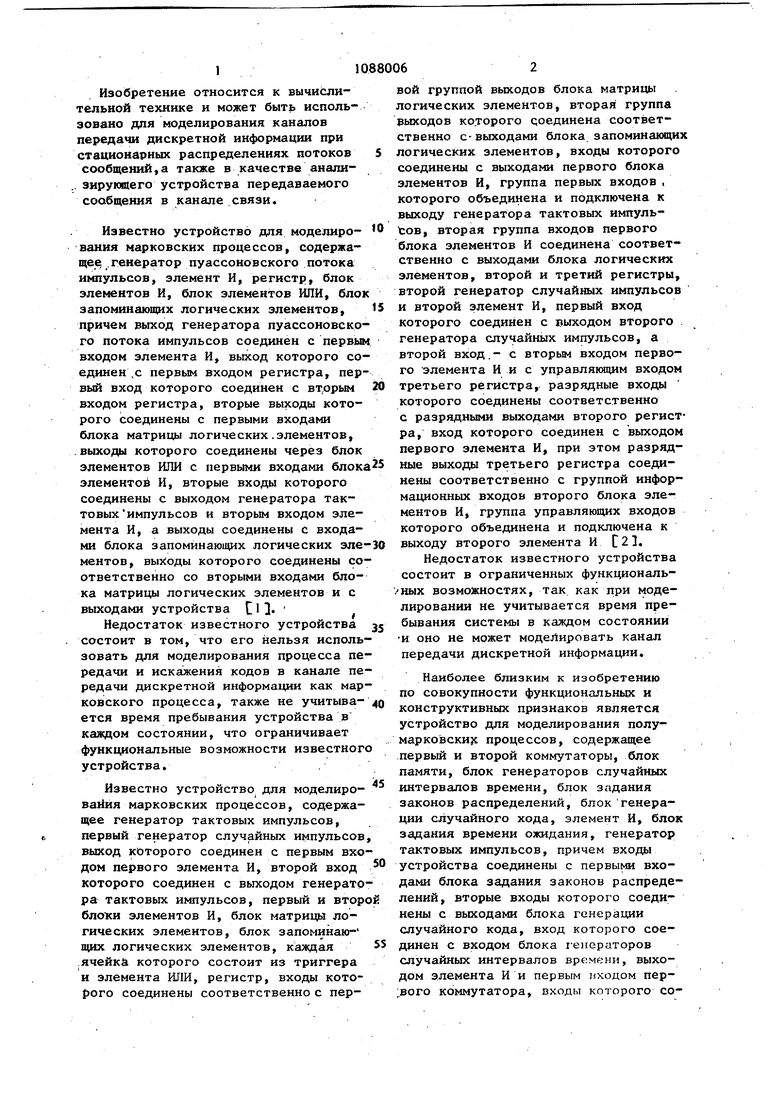

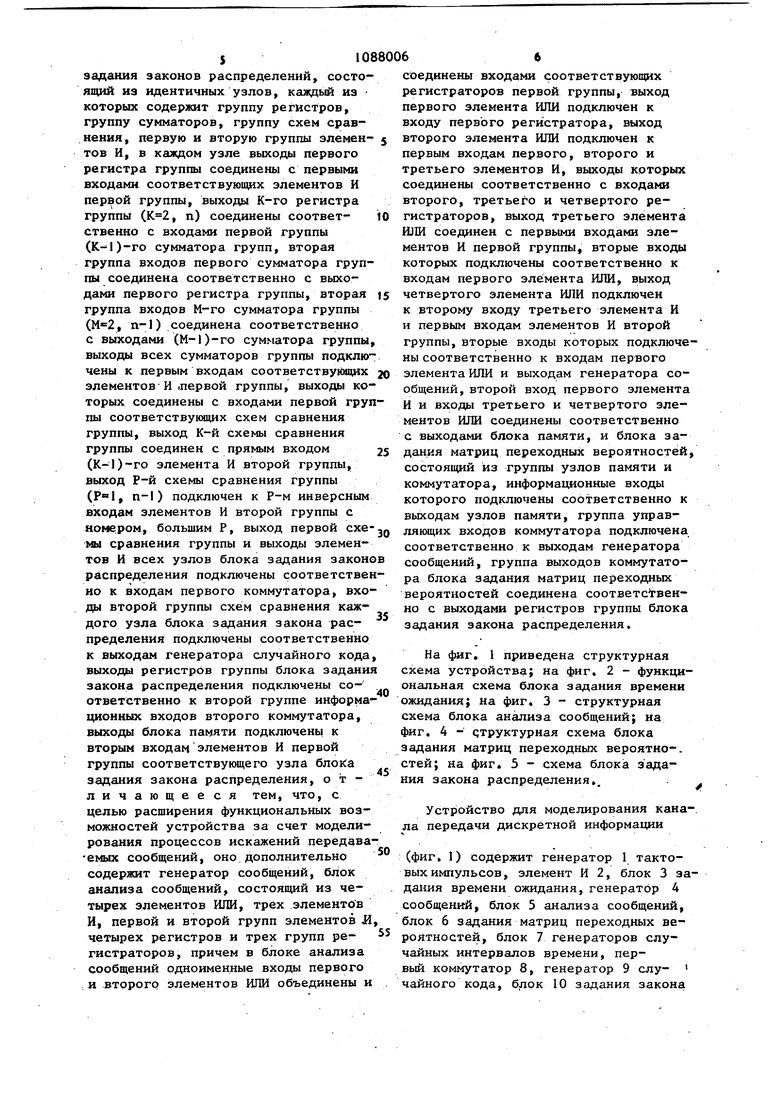

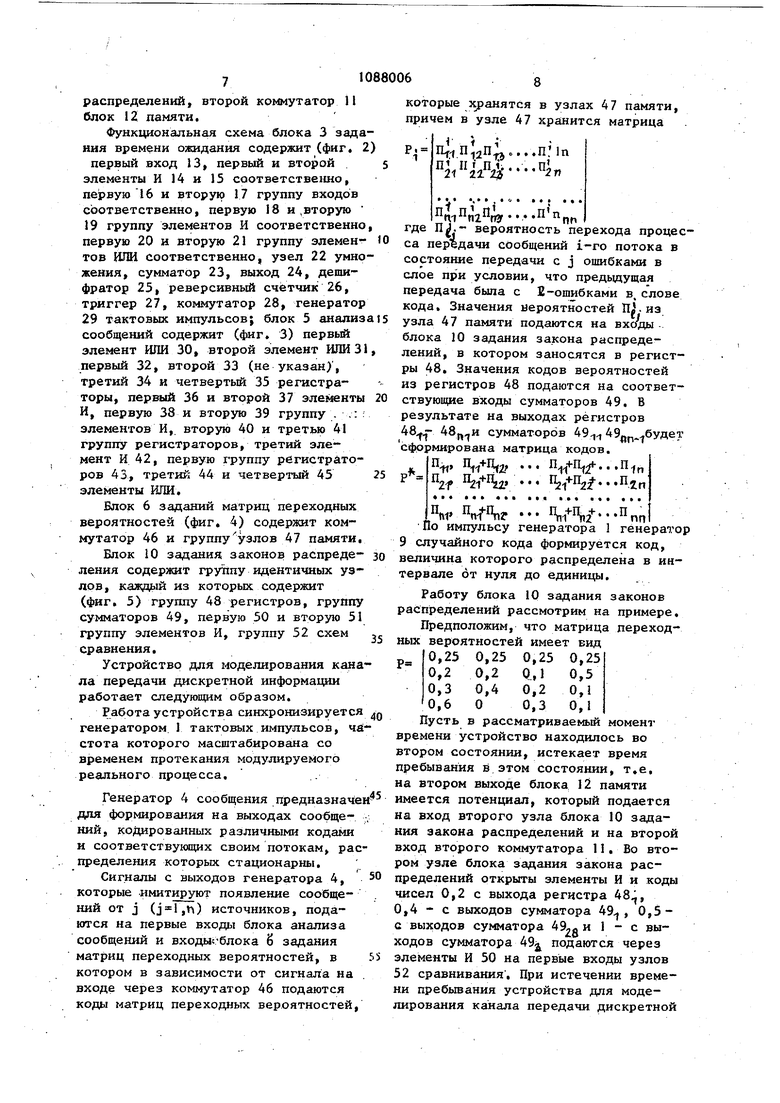

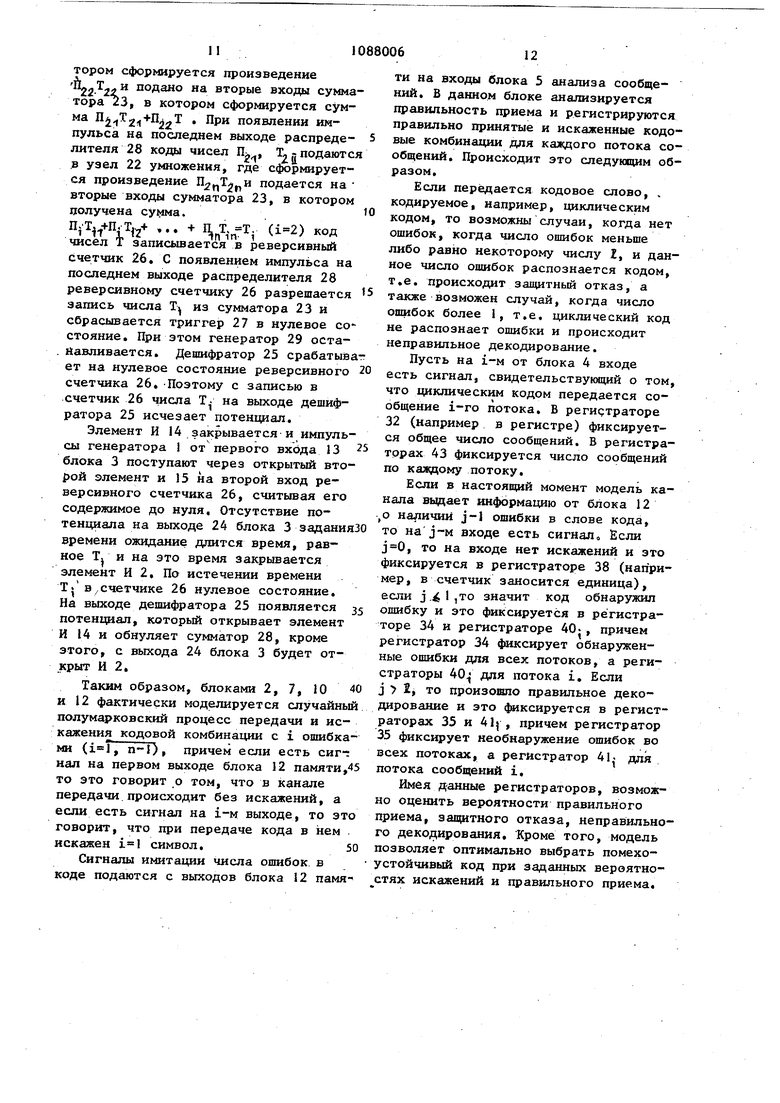

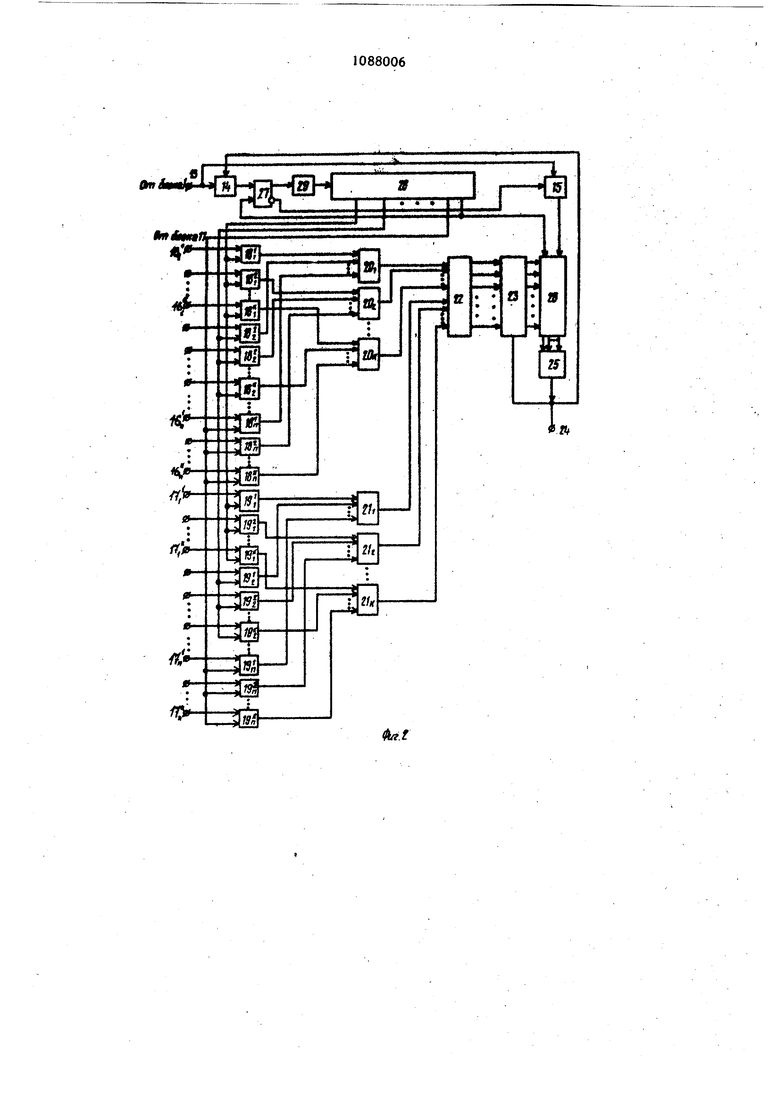

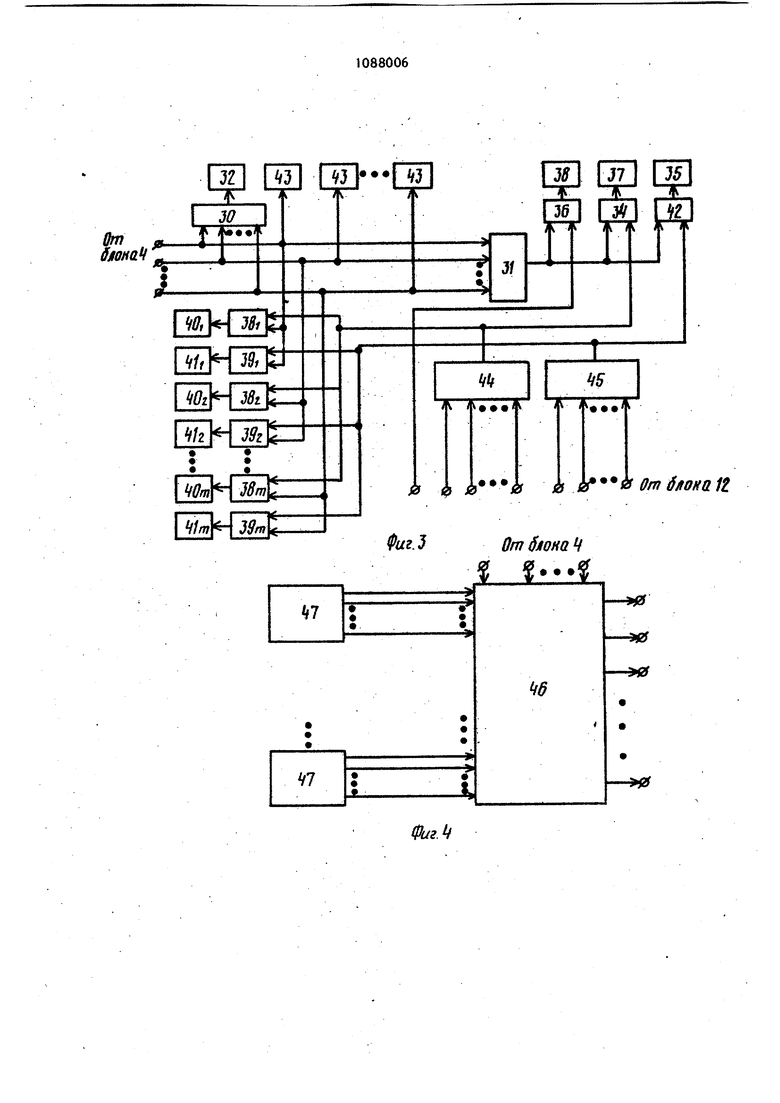

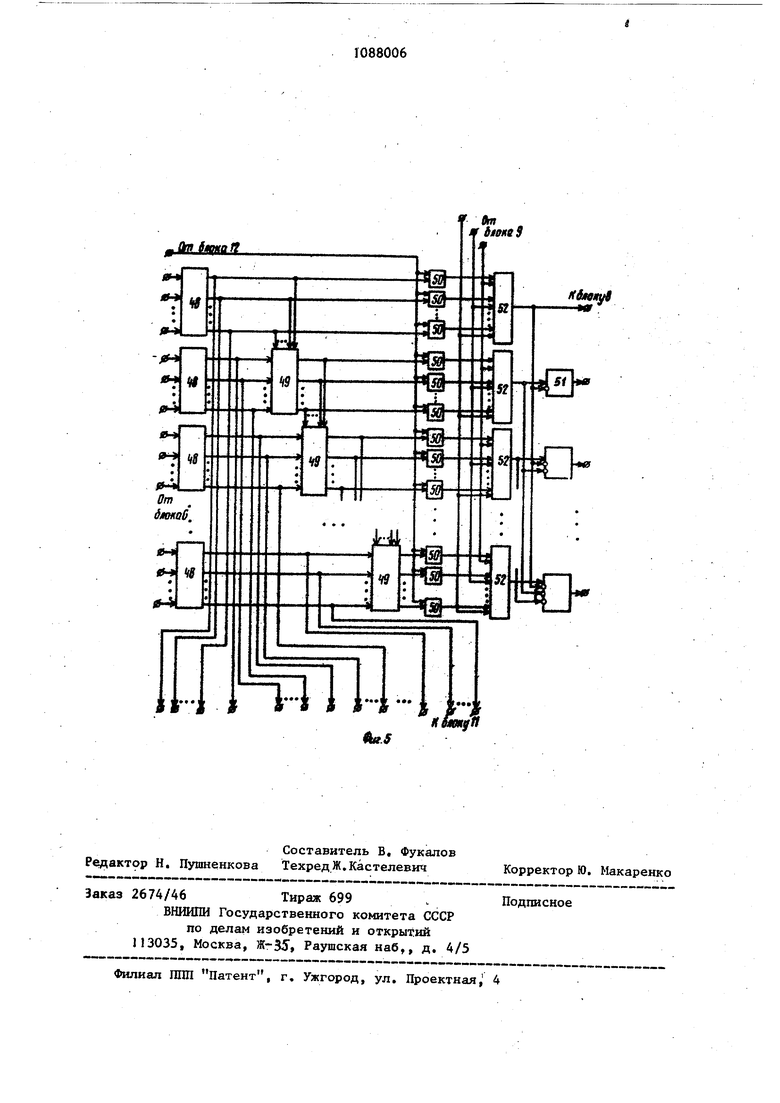

соединены входами соответствующих регистраторов первой группы, выход первого элемента ИЛИ подключен к входу первого регистратора, выход второго элемента ИЛИ подключен к первым входам первого, второго и третьего элементов И, выходы которых соединены соответственно с входами второго, третьего и четвертого регистраторов, выход третьего элемента ИЛИ соединен с первыми входами элементов И первой группы, вторые входы которых подключены соответственно к входам первого элемента ИЛИ, выход четвертого элемента ИЛИ подключен к второму входу третьего элемента И и первым входам элементов И второй группы, вторые входы которых подключены соответственно к входам первого элемента ИЛИ и выходам генератора сообщений, второй вход первого элемента И и входы третьего и четвертого элементов ИЛИ соединены соответственно с выходами блока памяти, и блока заДания матриц переходных вероятностей, состоящий из группы узлов памяти и коммутатора, информационные входы которого подключены соответственно к выходам узлов памяти, группа управляющих входов коммутатора подключена соответственно к выходам генератора сообщений, группа выходов коммутатора блока задания матриц переходных вероятностей соединена соответственно с выходами регистров группы блока задания закона распределения. На фиг. 1 приведена структурная схема устройства; на фиг. 2 - функциональная схема блока задания времени ожидания; на фиг. 3 - структурная схема блока анализа сообщений; на фиг. 4 - структурная схема блока задания матриц переходных вероятно-, стей; на фиг. 5 - схема блока задания закона распределения.. Устройство для моделирования кана-. ла передачи дискретной информации (фиг. 1) содержит генератор 1 тактовых импульсов, элемент И 2, блок 3 задания времени ожидания, генератор 4 сообщений, блок 5 анализа сообщений, блок 6 задания матриц переходных вероятностей, блок 7 генераторов случайных интервалов времени, парвый коммутатор 8, генератор 9 случайного кода, блок 10 задания закона распределений, второй коммутатор II блок 12 памяти. Функциональная схема блока 3 зада ния времени ожидания содержит (фиг 4 2 первый вход 23, первый и второй элементы И 14 и 15 соответственно, ) 16 и вторую 17 группу входов соответственно, первую 18 и ,вторую 19 группу элементов И соответственно первую 20 и вторую 21 группу элементов ШШ соответственно, узел 22 умно жения, сумматор 23, выход 24, дешифратор 23, реверсивный счётчик 26, триггер 27, коммутатор 28, генератор 29 тактовых импульсов; блок 5 анализ сообщений содержит (фиг. 3) первьй элемент ШШ 30, второй элемент ИЛИ 31 первый 32, второй 33 (не указан), третий 34 и четвертый 35 регистраторы, первый 36 и второй 37 эле1;юнты И, первую 38 и вторую 39 группу ..:; элементов И,, вторую 40 и третью 41 группу регистраторов, третий элемент И 42, первую группу рбгистраторов 43, третий 44 и четвертый 45 элементы ИЛИ, Блок 6 заданий матриц переходных вероятностей (фиг, 4) содержит коммутатор 46 и группу узлов 47 памяти. Блок 10 задания законов распределения содержит rpyiiny идентичных узлов, каждый из которых содержит (фиг, 5) группу 48 регистров, группу сумматоров 49, первую 50 и вторую 51 группу элементов И, группу 52 схем сравнения, Устройство для моделирования кана ла передачи дискретной информации работает следующим образом. Работа устройства синхронизируется генератором. 1 тактовых импульсов, ча стота которого масштабирована со временем протекания модулируемого реального процесса. Генератор 4 сообщения предназначе для формирования на выходах сообщаНИИ, кодированных различными кодами и соответствуняцих своим потокам, рас пределения которых стационарны. Сигналы с выходов генератора 4, которые имитируют появление сообщений от j (,n) источников, подаются на первые входы блока анализа сообщений и входыгблока ё задания матриц переходных вероятностей, в котором в зависимости от сигнала на входе через коммутатор 46 подаются коды матриц переходных вероятностей. которые хранятся в узлах 47 памяти, причем в узле 47 хранится матрица 1%п:52П-...п: In 1Пп1« --...Пп„ где nj.- вероятность перехода процесса пер4дачи сообщений i-ro потока в состояние передачи с j ошибками в слое при условии, что предыдущая передача была с 2-ошибками в. слове кода. Значения вероятностей Ш-из уэла 47 памяти подаются на вхс/ды / -«V / блока 10 задания закона распределений, в котором заносятся в регистры 48, Значения кодов вероятностей из регистров 48 подаются на соответствующие входы сумматоров 49. В результате на выходах регистров 48„ и сумматорбв 49 49,,.. .будет сформирована матрица кодов. V% «H+nt/-nin zf -П.гп fV П„ГП„Г По импульсу генератора 1 генератор 9 случайного кода формируется код. величина которого распределена в интервале от нуля до единицы. п гаооту блока 10 задания законов распределений рассмотрим на примере, „ Предположим,что матрица переходных вероятностей имеет вид 0,25 0,25 0,25 0,25| 0,2 0,2 Q.,1 0,5 0,3 0,4 0,2 0,1 0,6 О 0,3 0,1 Пусть в рассматриваемый момент времени устройство находилось во втором состоянии, истекает время пребывания в этом состоянии, т.е. на втором выходе блока 12 памяти имеется потенциал, который подается на вход второго узла блока 10 задания закона распределений и на второй вход второго коммутатора 11, Во втором узле блока задания закона распределений открыты элементы И и коды чисел 0,2 с выхода регистра 48, 0,4 - с выходов сумматора 49, 0,5с вых;одов сумматора 9Ja 1 с выходов сумматора 49j подаются через элементы И 50 на первые входы узлов 52 сравнивания. При истечении времени пребывания устройства для моделирования канала передачи дискретной информации потенциалом с выхода блока 3 задания времени ожидания открывается элемент И 2. Потенциал с выхода генератора 1 тактовых импульсов поступает на входы блока 1 генераторов случайных интервалов времени, первый вход первого коммутатора 8 и вход генератора 9 случайного кода, причём на выходе последнего сформируется код числа, равномерно распределеннрго в интервале от нуля до единицы, как было описано. Данный код подается на вторые входы узлов 52 сравнения, где происходит сравнение по величине кода числа, равномерно распределенного в интервале от нуля до единицы А, и кодов , подаваемьгк на вторые входы - В. При.условии, если число Б больше либо равно А на выходе узлов 52 сравнения появляется потенциал. Предположим, что сгенерирован код А 0.100000, что соответствует числу 0,5 единичной системы счисления. Тогда на выходах узлов 52 и 53 сравнения для рассматриваемого примера будут потенциалы, подаваемью на входы элементов И з потен1щал с выхода узла 52, сравнения закроет элемент и 51 и потенциал будет лишь на выходе элемента И 51 , что свидетельствует о переходе устрой ства в третье состояние и задание нового закона распределения. Потенциал с выхода блока 10 задани законов распределений подается на соответствующий вход первого коммутато ра 8, на вход блока 12 памяти. На третьем выходе блока I2 памяти устанавливается потенциал, что соответствует переходу системы в состояние передачи слов кода с двумя ошибками в слове. Процесс задания времени ожидания устройства для моделирования канала передачи дискретной информации протеч кает следующим образом. Канал передачи дискретной информации характеризуется третьим состоянием. На выходах блока 7 генераторов случайных интерва лов времени формируются коды интервалов времени, отвечающие распределением Fjj (t)- перехода из i-ro состоянияВ j-oe. Данные коды подаются на входы второго коммутатора 11, на другиевходы которого подаются с выходов блока 10 коды вероятностей . матрицы переходных вероятностей, а на второй вход коммутатора 11 подается потенциал с третьего выхода блока 12 памяти. На Еходах 16 блока 3 устанавливаются значения кодов третьей строки матрицы переходных вероятностей, которые хранятся в регистрах 8аг48зблока 10. На входах 17 устанавливаются коды, полученные в генераторах блока 7 генераторов случайных интервалов времени. Блок 3 задания времени ожидания задает время ожидания устройства в i-OM состоянии канала передачи дискретной информации в соответствии с формулой где - элементы матрицы переходных вероятностей; интервалы времени, генерируемые генераторами случайных интервалов времени, полученные в соответствии с распределениями Fy (t). Процесс задания происходит следующим образом. Импульс от генератора 1 поступает на первый вход 13 блока 3, через открытый первый элемент И 14 по заданному фронту импульса перебрасывается Tptirrep 27, который запускает генератор 29 тактовых импульсов, частота которого до.пжна быть в 2, раз,выше частоты генератора I, В этом случае в паузе между соседними импульсами генератора 1 совершается задание T.j . Генератор 29 тактовых импульсов управляет движением распределителя 28 сигналов. Вначале появляется импульс на первом из первых выходов распределителя 28 который открывает третьи 18 и четвертые 19 элементы И. В этом случае коды вероятности П,, и число 1„ подаются с их выходов через элемент ИЛИ 20 и 21 на первые и вторые входы узла 22 умножения, в котором происходит умножение подается с выхода узла 22 умножения на входы сумматора 23, который перед, этим был сброшен в нулевое состояние по первому входу. Затем появляется потенциал на втором выходе распределителя 28 и через открытые третьи элементы И 18 и четвертые элементы И 19 коды чисел Т22, .через первые 20 и вторые 21 элементы ИЛИ подаются на первые и вторые входы узла 22 умножения, в котором сформируется произведение . подано на вторые входы сумматора 3, в котором сформируется сумма .2,,+ЩлТ . При появлении импульса на последнем выходе распределита ля 28 коды чисел Щ, 1,,:. подаются .в узел 22 умножения, где сформируется произведение подается на вторые входы сумматора 23, в котором получена сумма. ,

- -

чисел Т записывается в реверсивный счетчик 26. С появлением импульса на последнем выходе распределителя 28 реверсивному счетчику 26 разрешается 5 запись числа Т из сумматора 23 и сбрасывается триггер 27 в нулевое состояние. При этом генератор 29 останавливается . Дешифратор 25 срабатывает на нулевое состояние реверсивного 20 счетчика 26. Поэтому с записью в счетчик 26 числа Т| на выходе дешифратора 25 исчезает потенциал.

Элемент И 14 закрывается и импульсы генератора 1 от первого входа 13 блока 3 поступают через открытый второй элемент и 15 на второй вход реверсивного счетчика 26, считывая его содержимое до нуля. Отсутствие потенциала на выходе 24 блока 3 заданияЗО времени ожидание длится время, равное Т, и на это время закрывается элемент И 2, По истечении времени Т«в,счетчике 26 нулевое состояние. На выходе дешифратора 25 появляется 35 потенциал, который открывает элемент И 14 и обнуляет сумматор 28, кроме этого, с выхода 24 блока 3 будет открыт И 2.

Таким образом, блоками 2, 7, 10 40 и 12 фактически моделируется случайный полумарковский процесс передачи и искажения кодовой комбинахщи с i ошибками (, п-1) , причем если есть сиг-: нал на первом выходе блока 12 памяти ,5 то это говорит о том, что в канале передачи происходит без искажений, а если есть сигнал на i-M выходе, то это говорит, что при передаче кода в нем искажен символ.50

Сигналы имитации числа ошибок в коде подаются с выходов блока 12 памя

ти на входы блока 5 анализа сообщений. В данном блоке анализируется правильность приема и регистрируются правильно принятые и искаженные кодовые комбинации для каждого потока сообщений. Происходит это следующим образом.

Если передается кодовое слово, , кодируемое, например, циклическим кодом, то возможны случаи, когда нет ошибок, когда число ошибок меньше либо равно некоторому числу 2, и данное число ошибок распознается кодом, т.е. происходит защитньш отказ, а также возможен случай, когда число ошибок более 1, т.е. циклический код не распознает ошибки и происходит неправильное декодирование.

Пусть на i-M от блока 4 входе есть сигнал, свидетельствующий о том, что циклическим кодом передается сообщение i-ro потока. В регистраторе 32 (например в регистре) фиксируется общее число сообщений. В регистраторах 43 фиксируется число сообщений по каждому потоку.

Если в настоящий момент модель канала ведает информацию от блока 12 о наличии J-1 ошибки в слове кода, то на J-M входе есть сигнал Если , то на входе нет искажений и это фиксируется в регистраторе 38 (например, в счетчик заносится единица), если J.4 iTO значит код обнаружил ошибку и это фиксируется в регистраторе 34 и регистраторе 40-, причем регистратор 34 фиксирует обнаруженные ошибки для всех потоков, а регистраторы 40| для потока i. Если j 2, то произошпо правильное декодирование и это фиксируется в регистраторах 35 и 4lj , причем регистратор 35 фиксирует необнаружение ошибок во всех потоках, а регистратор 41 для потока сообщений 1.

Имея д-анные регистраторов, возможно оценить вероятности правильного приема, защитного отказа, неправильного декодирования. Кроме того, модель позволяет оптимально выбрать помехоустойчивый код при заданньж вероятностях искажений и правильного приема.

От 6/юмаЧ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования канала связи | 1983 |

|

SU1132294A1 |

| Устройство для моделирования канала передачи дискретной информации | 1985 |

|

SU1273943A1 |

| Устройство для моделирования систем массового обслуживания | 1984 |

|

SU1229771A1 |

| Устройство для моделирования систем передачи дискретной информации | 1983 |

|

SU1112367A1 |

| Устройство для моделирования марковских потоков сигналов | 1983 |

|

SU1088004A1 |

| Устройство для моделирования марковских потоков сигналов | 1983 |

|

SU1137477A2 |

| Устройство для моделирования стохастических объектов | 1984 |

|

SU1251096A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ РАСПРЕДЕЛЕНИЯ РАВНОМЕРНО ЦЕЛОЧИСЛЕННЫХ ПСЕВДОСЛУЧАЙНЫХ ВЕЛИЧИН | 1990 |

|

RU2042187C1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ТЕХНОЛОГИИ ПРОГРАММИРОВАНИЯ | 1990 |

|

RU2041487C1 |

| Устройство для статистического контроля логических блоков | 1983 |

|

SU1173415A1 |

УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ КАНАЛА ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЩШ, содержащее генератор тактовых импульсов, элемент И, генератор случайного кода, первый и второй коммутаторы, блок памяти, блок генераторов случайных интервалов, блок задания времени ожидания, состояний из двух групп элементов И, двух групп элементов ИЛИ, первого и второго элементов И, триггера,- генератора тактовых импульсов,. коммутатора, узла умножения, сумматора, реверсивного счетчика и дешифратора, первые входы первого и второго элементов И блока задания времени ожидания соединены с выходом генератора тактовых импульсов устройства, причем в блоке задания времени ожидания выход первого элемента И блока задания времени ожидания подключен к единичному входу триггера, нулевой вход которого соединен соответ,ствующим выходом коммутатора и входом разрешения записи реверсивного счетчика, прямой выход триггера подключен к входу генератора тактовых импульсов, выход которого соединен с входом коммутатора, группа выходов которого подключена к первым входам соответствующих элементов И первой и второй групп, выходы элементов И первой группы подключены соответственно к входам элементов ИЛИ первой группы, а выходы элементов И второй группы соединены соответственно с входами элементов ИЛИ второй группы, выходы элементов ИЛИ первой и второй групп подключены соответственно к входам первой и.второй групп узла умножения, выходы которого соединены соответственно с разрядными входами сумматора, выходы которого подключены соотi ветственно к разрядным входам реверсивного счетчика, выходы которого сое(Л (Динены соответственно с входами дешифратора, выход которого соединен с устаС новочным входом сумматора и вторым входом первого элемента И, инверсный выход триггера подключен к второму входу второго элемента И, выход дешифратора блока задания времени ожидания . соединен с первым входом элемента И 00 00 устройства, второй вход элемента И подключен к выходу генератора тактовых импульсов, а выход элемента И подключен к управляющему входу перо вого коммутатора, входу генератора случайного кода, к входу блока генераторов случайных интервалов, группа И)1ходов которого соединена соответственно с первой группой информационных входов второго комггутатора, группа выходов которого подклычена соответственно к вторым входам элементов И первой и второй групп блока задания времени ожидания, группе выходов первого коммутатора и соединена соответственно с группой

От блока Ц %

ФигМ

Qai {мша ft

лч

tf

W

j r D ff 6tones

К&юяуВ

Я

f5

«Й- :4.

w

5

/7m длтаб.

t6-

46

Л

0

I W

J « jl f J

i

Jrit

у f

01

Липу ft

.S

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР | |||

| Весовое приспособление к подъемным машинам | 1926 |

|

SU6451A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-04-23—Публикация

1983-02-28—Подача