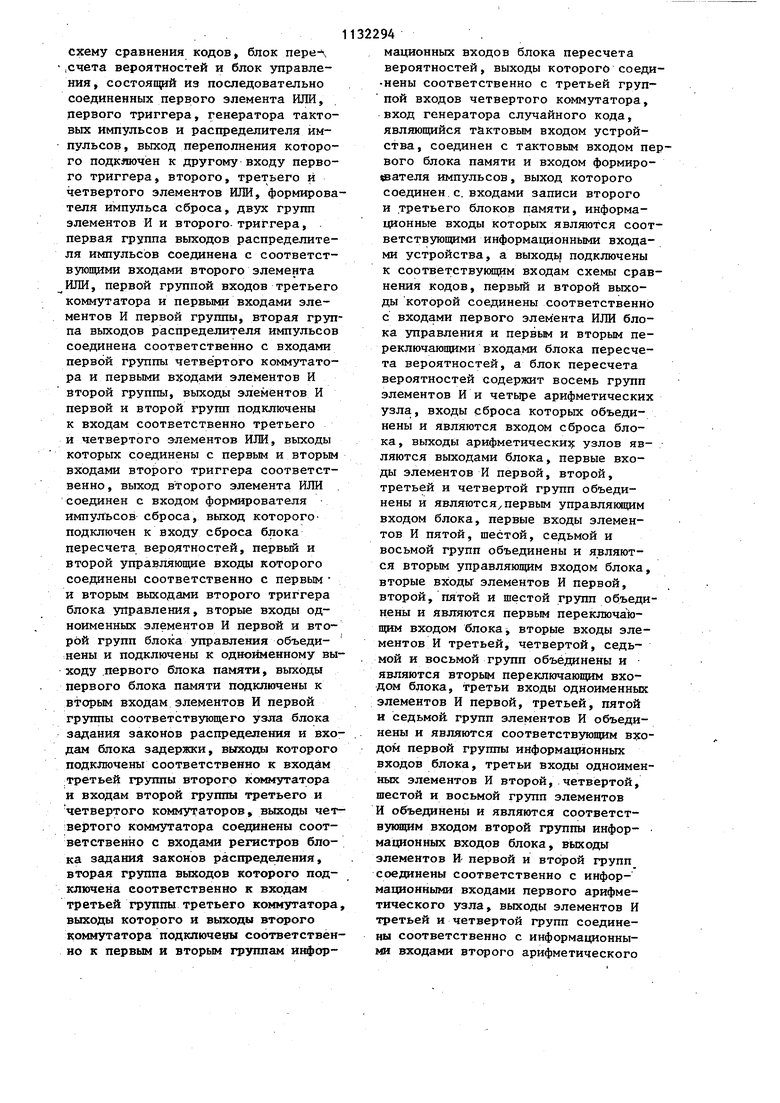

схему сравнения кодов, блок перел счета вероятностей и блок зтравления, состоящий из последовательно соединенных первого элемента ИЛИ, первого триггера, генератора тактовых импульсов и расгфеделителя импульсов, выход переполнения которого подключён к другому входу первого триггера, второго, третьего и четвертого элементов ИЛИ, формирователя импульса сброса, двух групп элементов И и второго-триггера, первая группа выходов распределитея импульсов соединена с соответствующими входами второго элемента ИЛИ, первой грзтппой входов третьего коммутатора и первыми входами элементов И первой группы, вторая группа выходов распределителя импульсов соединена соответственно с входами первой группы четвёртого коммутатора и первыми входами элементов И второй группы, выходы элементов И первой и второй групп подключены к входам соответственно третьего и четвертого элементов ИЛИ, выходы которых соединены с первым и вторым входами второго триггера соответственно , выход второго элемента ИЛИ . соединен с входом формирователя импульсов сброса, выход которогоподключен к входу сброса блока пересчета вероятностей, первый и второй управляющие входы которого соединены соответственно с первым и вторым выходами второго триггера блока управления, вторые входы одноименных элементов И первой и второй групп блока управления объединены и подключены к одноименному выходу .первого блока памяти, выходы первого блока памяти подключены к вторым входам элементов И первой группы соответствующего узла блока задания законов распределения и входам блока задержки, выгходы которого подключены соответственно к входам третьей грутшы второго коммутатора и входам второй группы третьего и четвертого коммутаторов, выходы четвертого коммзтатора соединены соответственно с входами регистров блока заданий законов распределения, вторая группа выходов которого подключена соответственно к входам третьей группы третьего коммутатора, выходы которого и выходы второго коммутатора подключены соответственно к первым и вторым группам информационных входов блока пересчета вероятностей, выходы которого соединены соответственно с третьей группой входов четвертого коммутатора, вход генератора случайного кода, являющийся тактовым входом устройства, соединен с тактовым входом певого блока памяти и входом формирователя импульсов, выход которого соединен.с. входами записи второго и третьего блоков памяти, информационные входы которых являются соответствзтощими информационными входами устройства, а выходы подключены к соответствукйцим входам схемы сравнения кодов, первый и второй выходы которой соединены соответственно с входами первого элемента ИЛИ блока управления и первьм и вторым переключающими входами блока пересчета вероятностей, а блок пересчета вероятностей содержит восемь групп элементов И и четыре арифметических узла, входы сброса которых объединены и являются входом сброса блока, выходы арифметически ;: узлов являются выходами блока, первые входы элементов И первой, второй, третьей и четвертой групп объединены и являются первым управлякщим входом блока, первые входы элементов И пятой, шестой, седьмой и восьмой групп объединены и являются вторым управляющим входом блока, вторые входы элементов И первой, второй, пятой и шестой групп объединены и являются первым переключающим входом блока, вторые входы элементов И третьей, четвертой, седьмой и восьмой групп объединены и являются вторым переключающим входом блока, третьи входы одноименных элементов И первой, третьей, пятой к седьмой групп элементов И объединены и являются соответствзгющим взсодом первой группы информационных входов блока, третьи входы одноименных элементов И второй,.четвёртой, шестой и восьмой групп элементов И объединены и являются соответствукйцим входом второй группы информационных входов блока, выходы элементов И- первой и второй групп соединены соответственно с информационными входами первого арифметического узла, выходы элементов И третьей и четвертой групп соединены соответственно с информационными входами второго арифметического узла, выходы элементов И пятой и шестой групп соединены соответствен но с информационными входами третьего- арифметического узла, а выходы элементов И седьмой и восьмой групп соединены соответственно с информационными входами четвертого арифметического узла. 2. Устройство по п. 1 , отличающееся тем, что первый и второй арифметические узлы блока пересчета вероятностей содержат последовательно соединенные первый регистр, умножитель, сумматор и делитель, выходы которого являются выходами арифметического узла, другой вход сумматора подключен к выходу второго регистра, входы сбро.са умножителя, сумматора и делителя объединены и являются входом сброса арифметического узла, информационные входы умножителя и дели4теля являются соответствующими информационными входами арифметического узла. 3. Устройство по пп. 1 и 2, отличающееся тем, что. третий и четвертый арифметические узлы блока пересчета вероятностей содержат последовательно соединенные первый регистр, первый умножитель , сумматор, делитель и второй умножитель, выходы которого являются выходами арифметического узла, другие входы сумматора и второго умножителя подключены соответственно к выходам второго и третьего регистров, входы сброса первого и второго змножителей, сумматора и делителя объединены и являются входом сброса арифметического узла, информационные входы первого умножителя и делителя являются соответствующими информационными входами арифметического узла.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для определения закона распределения | 1986 |

|

SU1388900A1 |

| Устройство для моделирования стохастических объектов | 1984 |

|

SU1251096A1 |

| Устройство для моделирования стохастических объектов | 1988 |

|

SU1585803A1 |

| Устройство для моделирования канала передачи дискретной информации | 1983 |

|

SU1088006A1 |

| Генератор случайных процессов | 1981 |

|

SU985786A1 |

| Устройство для определения закона распределения | 1987 |

|

SU1520545A1 |

| Устройство для реализации двумерного быстрого преобразования фурье | 1983 |

|

SU1142845A1 |

| Вероятностное устройство для решения краевых задач | 1982 |

|

SU1101838A1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

1. УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ КАНАЛА СВЯЗИ, содержащее последовательно соединенные генера тор случайного кода, блок задания законов распределенияi первый коммутатор и первый блок памяти, выходы которого являются выходами устройства и подключены соответственно к входам первой группы второго коммутатора, вторая группа входов которого подключена соответственно к второй rpyime выходов блока задания законов распределения, блок задания законов распределения состоит из идентичных .узлов, каждый из которых содержит группу регистров, группу сумматоров, первую и вторую группы элементовИ, группу схем сравнения, в каждом узле выходы первого регистра группы соединены с первыми входами соответствующих элементов И первой группы, выходы k-ro регистра группы ( К 2,N ) соединены соответственно с входами первой группы (k-l)-ro сумматора группы, вторая группа входов первого сумматора группы соединена соответственно с выходами первого регистра группы, вторая группа входов М -го сумматора группы ( М 2, N -1) соединена соответственно с выходами (М-1)-сумматора группы, выходы всех сумматоров группы подключены к первым входам соответствующих элементов И первой группы, выходы которых соединены с входами первой группы соответствующих схем сравнения группы, выход К -и схемы сравнения группы соединен с прямым входом ( К -1)-го элемента И второй группы, выход Р -и схемы сравнения группы ( Р 1, N -1) подключен к Р -м инверсным входам элементов И второй группы с номе(Л ром , большим Р, выход первой схемы сравнения группы и выходы элементов И второй группы являются COOT- . ветствующими выходами узла блока задания законов распределения, одноименные выходы всех узлов блока задания законов распределения объединены и являются соответствуюпшм выходом со ьо to со ь« первой группы блока .задания законов распределения, второй группой выходов которого являйтся выходы регистров группы всех узлов, а первой группой входов - блока задания законов распределения является вторая группа входов всех схем сравнения группы, отличающееся тем, что, с целью ра&ширения функциональных возможностей устройства путем обеспечения возможности идентификации характеристик канала связи, оно дополнительно содержит блок задержки, третий и четвертый коммутаторы, формирователь импульсов, второй и третий блоки памяти.

Изобретение относится к вычислительной технике и может быть использовано как специальное вычислительное моделирующее устройство для индентификации стохастических характеристик канала передачи дискретной информации.

Известно устройство, содержащее блок задания законов распределений, блок генерации случайного кода, . генератор тактовых импульсов, генератор случайного напряжения, элементы И и ИЛИ, блоки памяти, элементов И и блока задания времени ожидания, причем выход генератора тактовых импульсов соединен с первыми- входами элемента И и блока задния времени ожидания, второй вход которого соединен с выходом генератора случайного напряжения, а третий - с первым входом блока элементов И, выходом элемента И и первым входом блока генерации случайного кода, вьгходы которого соединены с первыми входами блока задания законов распределений, выходы которого соединены с вторьми входами блока элементов И, выходы которого.соединены с входами блока памяти, выходы которого соединены с вторыми входами блока задания закоча распределений и с четвертыми входами блока задания времени ожидания, выходыкоторого соединены с выходными шинами и входами элемента ИЛИ, выход которого соединен с вторыми входами элемента И и блока генерации случайного кода lj

Однако данное устройство характеризуется недостаточными функциональными возможностями для моделирования функциональных каналов передачи дискретной информации вследствие отсутствия возможностей анализа искажений кодовых комбинаций в процессе передачи и коррекции матрицы переходных вероятностей.

Наиболее близким к предлагаемому является устройство9 содержащее последовательно соединенные генератор тактовых импульсов, элемент И, блок генерации случайного кода, блок задания законов распределения, первый коммутатор, первый блок памяти, второй коммутатор и блок задания времени ожидания, выход которого

. 3 .

подключен к другому входу элемента И, выход генератора тактовых импульсов подключен к синхронизирующим входам блока задания времени ожидания и блока генерации соббщений, выходы которого соединены соответственно с входами блока анализа сообщений, вторыми входами соединенного с выходами первого блока памяти, « блока задания матрицы переходных вероятностей, выходы которого подклчены к другим входам блока задания закона рарпределения, выход элемента И соединен с управляющим входом первого коммутатора и блока генерации случайных интервалов времени, выходы которого соединены- с входами второй грзтпы второго коммутатора, третья группа входов которого подключена к соответствующей группе выходов блока задания законов распределения Т

В процессе работы происходит определение переходных вероятностей (априорно незаданных), которые характеризуют марковский процесс. Однако известное устройство в силу ограниченности функциональных возможностей не может идентифицировать стохастические характеристики ка-, нала передачи дискретной информации так как нет возможности анализа существующих искажений кодов в канале. В то же время процесс передачи и искажения кодовых комбинаций в канале является марковским и его можно описать матрицей переходных вероятностей, элемент которой характеризует переход из состояния передачи кодов с i оши.бками всосгтояние передачи кодов с j ошибками.

Цель изобретения - расширение функциональных возможностей путем идентификации характеристик каналов связи.

Указанная цель достигается тем, что в устройство для моделирова7 ния канала связи, содержащее последовательно соединенные генератор случайного кода, блок задания законов распределения, первый коммутатор и первый блок памяти, выхо.ды которого являются выходами устройства и подключены соответственно к входам первой группы второго коммутатора, вторая группа входов которого подключена соответственно

к второй группе выходов блока задания законов распределения, блок задания законов распределения состоит из идентичных узлов, каждьй из 5 которых содержит группу регистров, группу сумматоров, первую и вторую группы элементов И и группу схем сравнения, в каждом узле выходы «первого регистра группы соединены 0 с первыми входами соответствующих элементов И первой группы, выходы К-го регистра группы ( К 2,W ) соединены соответственно с входами первой группы (К Ото сумматора 5 группы, вторая группа входов первого сумматора группы соединена соответственно с выходами первого регистpia группы, вторая группа входов М-го сумматора группы ( М 2, N -1) 0 соединена соответственно с выходами (М-:1)-го сзлиматора группы, выходы всех сумматоров группы подключены к первым входам соответствующих элементов И первой группы, вы5 ходы которых соединены с входами первой группы соответствующих схем сравнения группы, выход К-й схемы сравнения группы соединен с прямым входом (К -1)-го элемента И второй группы, выход Р -и схемы сравнения группы (D 1,М -1)-подключен к Р-м инверсным входам элементов И второй группы с номером, большим Р, выход первой схемы сравнения группы и выходы элементов И второй группы являются соответствующими выходами узла блока задания законов распределения, одноименные, выходы всех узлов блока задания законов распределения объединены и являются 0 соответствующим выходом первой группы блока задания законов распреде. ления, второй группой выходов которого являются выходы регистров группы всех узлов, а первой группой вхйдов блока задания законов распределения является вторая группа входов всех схем сравнения группы, введены блок задержки, третий и четвертьй коммутаторы, формирова0 тель импульсов, второй и третий бло-ки памяти, схему сравнения кодов, блок пересчета вероятностей и блок управления, состоящий из последовйтельно соединенных первого элемен5 та ИЛИ, первого триггера, генератора тактовых импульсов и распределителя импульсов, выход переполнения которого подключен к другому в входу первого триггера, второго, третьего и четвертого элементов ИЛИ формирователя импульса сброса, двух групп элементов И и второго триггера , первая группа выходов распределителя импульсов соединена с соот ветствующими входами второго элемен та ИЛИ, первой группой входов третьего коммутатора и первыми входами элементов И первой группы, вторая группа выходов распределителя импульсов соединена соответственно iC входами первой группы четвертого коммутатора и первыми входами элементов И второй группы, выходы элементор И первой и второй групп подключены к входам соответственно третьего и четвертого элементов ИЛИ выходы которых соединены с первым и вторым входами второго триггера соответственно, выход второго элемента ИЛИ соединен с входом формирователя импульсов сброса, выход которого подключен к входу сброса блока пересчета вероятностей, первый и второй управляющий входы которого соединены соответственно с первым и вторым выходами второго триггера блока управления, вторые входы одноименных элементов И первой и второй групп блока управления объединены и подключены к одно именному выходу первого блока памя ти, выходы первого блока памяти подключены к вторым входам элементов И первой группы соответствующего узла блока задания законов распределения и входам блока задер ки, выходы которого подключены соответственно к входам третьей груп пы третьего коммутатора и входам второй группы третьего и четвертого коммутаторов, выходы четвертого коммутатора соединены соответствен но с входами регистров блока задания законов распределения, вторая группа выходов которого подключена соответственно к входам третьей группы третьего коммутатора, выходы которого и выходы второго комму татора подключены соответственно к первым и вторым группам информационных входов блока пересчета вероятностей, выходы которого соедииены соответственно с третьей груп пой входов четвертого коммутатора, вход генератора случайного кода, являющийся тактовым входом устройства , соединен с тактовым входом первого блока памяти и входом формирователя импульсов, выход кото- рого соединен с входами записи второго и третьего блоков памяти, информационные входы которых являются соответствующими информационными входами устройства, а выходы подключены к соответствующим входам схемы сравнения кодов, первьй и второй выходы которой соединены соответственно с входами первого элемента ИЛИ блока управления и первым и вторьм переключающим входами блока пересчета вероятностей, а блок пересчета вероятностей содержит восемь групп элементов И и четыре арифметических узла, входы сброса которых объединены и являются входом сброса блока, выходы арифметических узлов являются выходами блока, первые входы элементов И первой, второй, третьей и четвертой групп объединены и являются первым управляю1цим входом блока, первые входы элементов И пятой, шестой, седьмой и восьмой групп объединены и являются вторьм управ-, ляющим входом блока, вторые входы элементов И первой, второй, пятой и шестой групп объединены и являются первым переключающим входом блока , вторые входы элементов И третьей, четвертой, седьмой и восьмой групп объединены и являются вто- рым переключающим входом блока, третьи входы одноименных элементов И первой, третьей, пятой и седьмой групп элементов И объединены и являются соответствующим входом первой группы информационных входов блока, третьи входы одноименных элементов И второй,четвертой, шестой и восьмой групп элементов И объединены и являются соответствующим входом второй группы информационных входов блока, выходы элементов И первой и второй групп соединены соответственно с информационными входами первого арифметического узла, выхойы элементов И третьей и четвертой групп соединены соответственно с информационными входами второго арифметического узла, выходы элементов И пятой и шестой групп соединены соответственно с информационными входами третьего арифметического узла, а вы7 .

ходы элементов И седьмой и восьмой групп с(ёдинены соответственно с информационными входами четвертого арифметического узла.

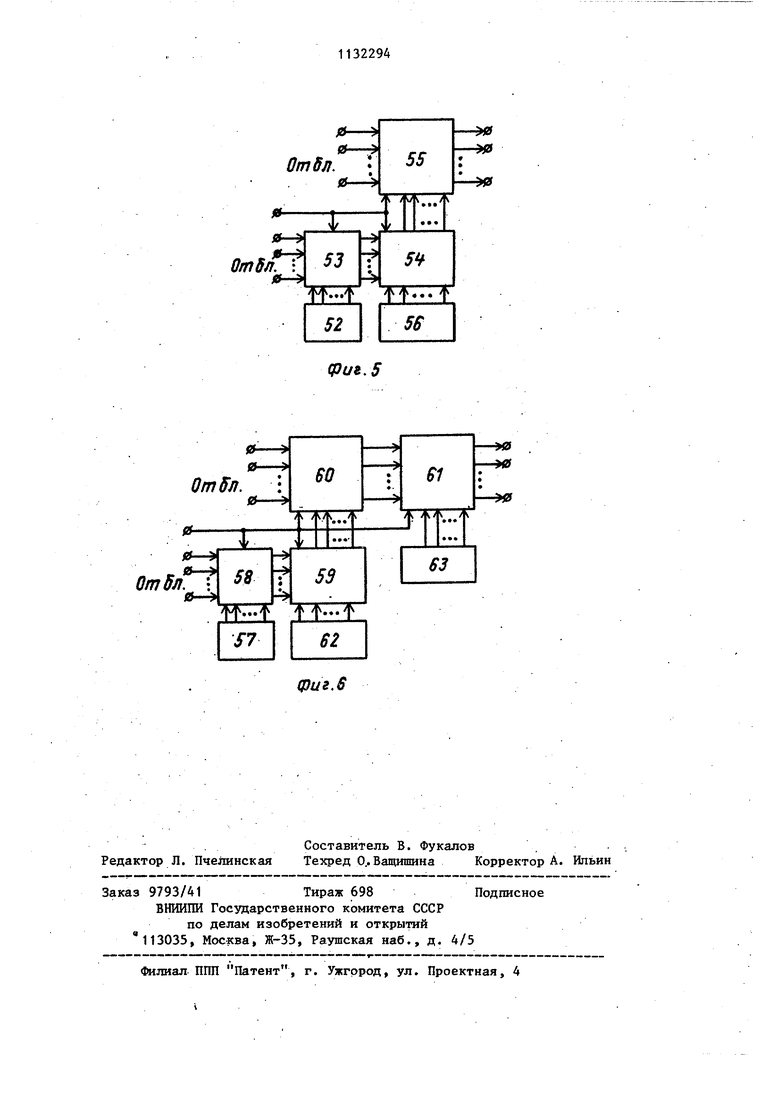

Первьй и второй арифметические - узлы .блока пересчета вероятностей содержат последовательно соединенные первый регистр, умножитель, сум.матор и делитель, выходы которого являются выходами арифметического узла, другой вход сумматора подключен к выходу второго регистра, входы сброса умножителя, сзт матора и делителя объединены и являются входами сброса арифметического узла, информационные входы умножителя и делителя являются соответствующими информационными входами арифметичес1сого узла.

Третий и четвертый арифметически узлы блока пересчета вероятностей содержат последовательно соединенные первый регистр, первый умножитель, сумматор, делитель и второй умножитель, выходы которого являются выходами арифметического узла, другие входы сзмматора и второго умножителя подключены соответственно к выходам второго и третьего регистров , входы сброса первого и второго умножителей, сумматора и делителя объединены и являются входом сброса арифметического узла, информационные входы первого умножителя и делителя являются соответствующиг ми информационными входами арифметического узла.

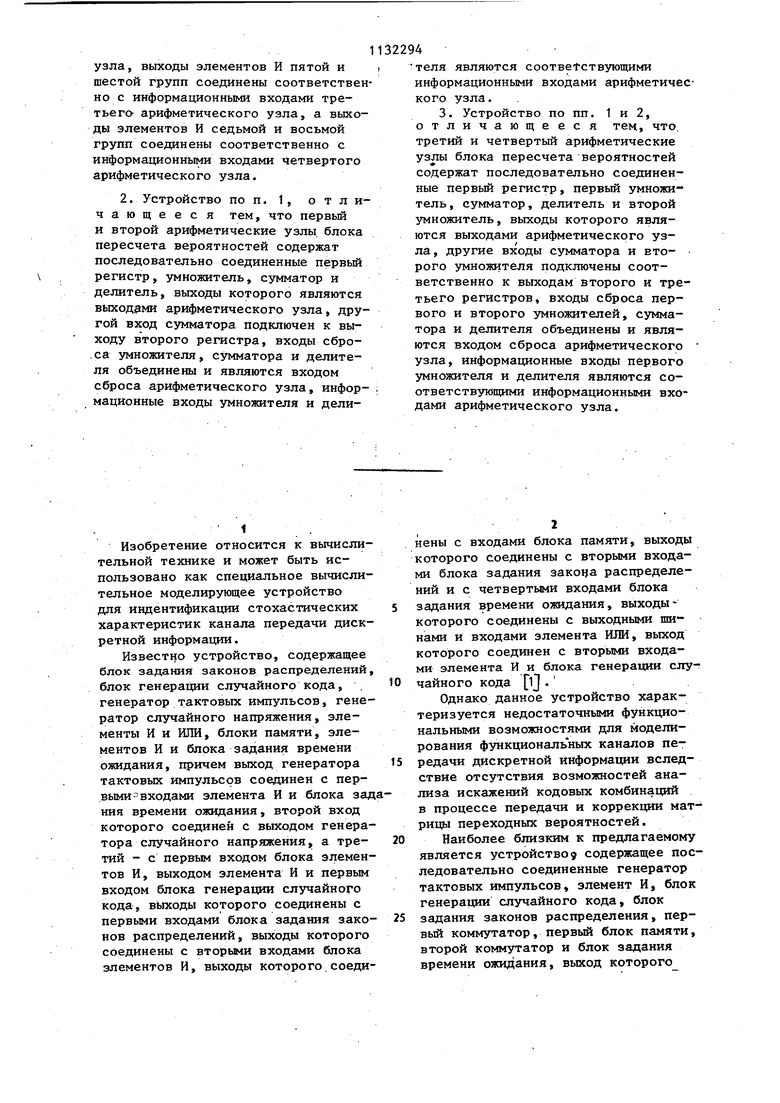

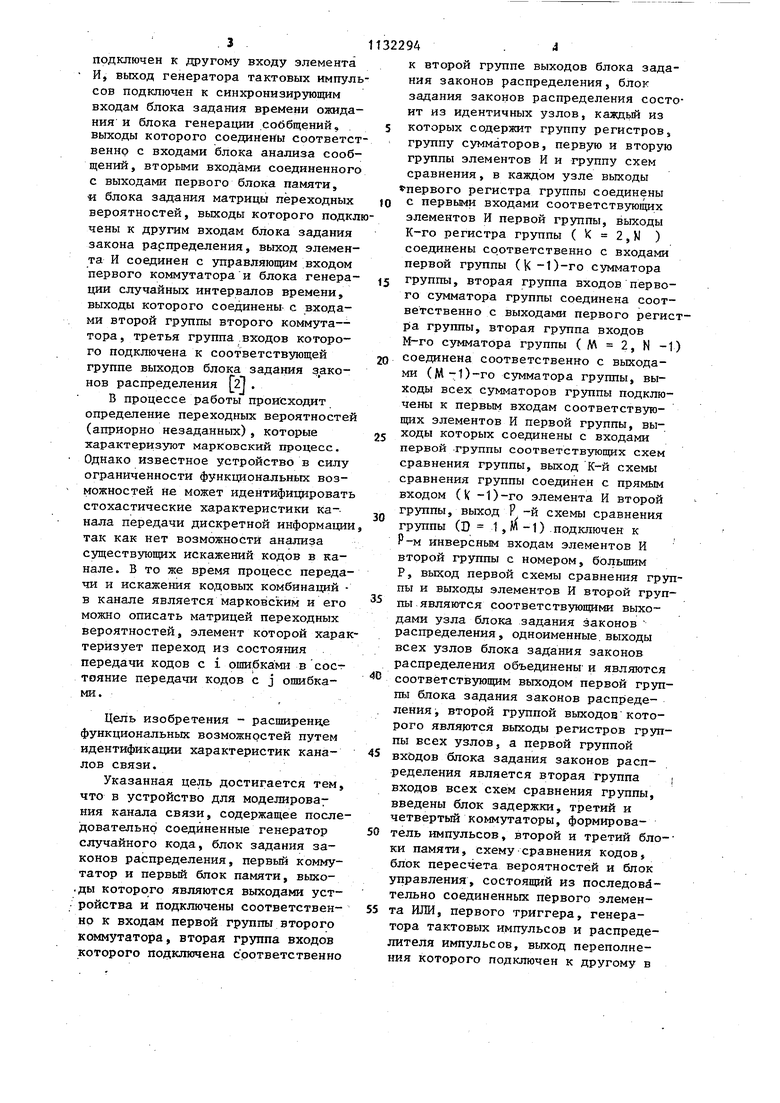

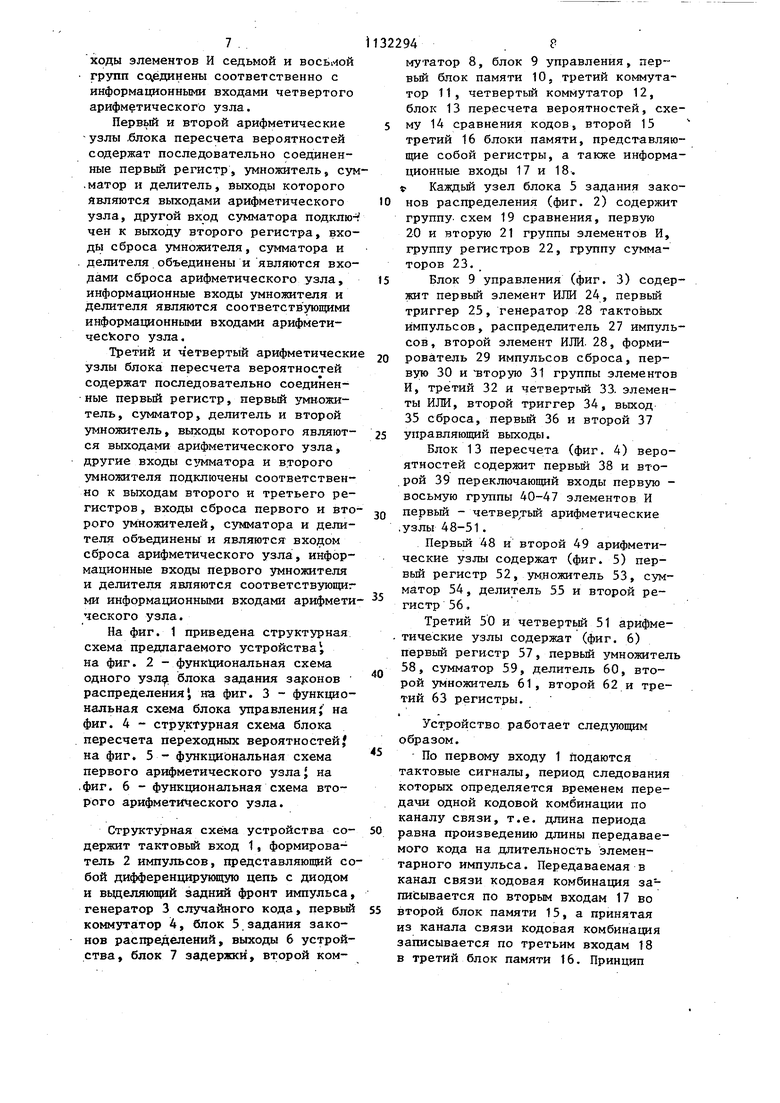

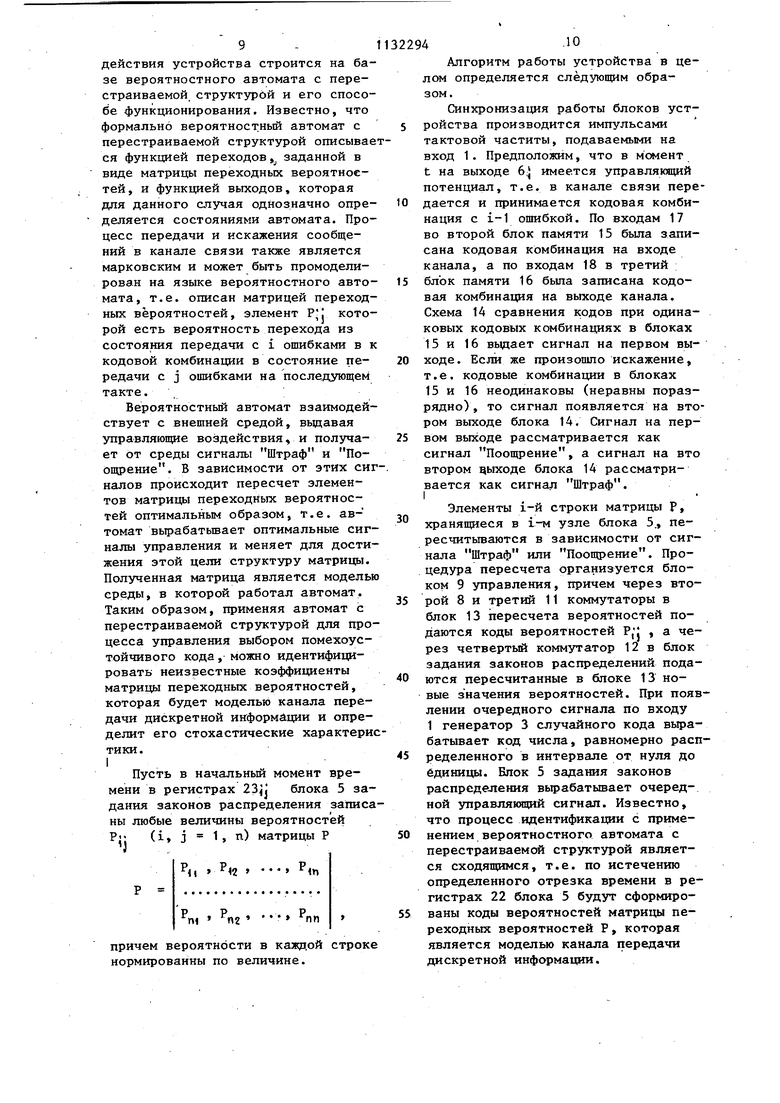

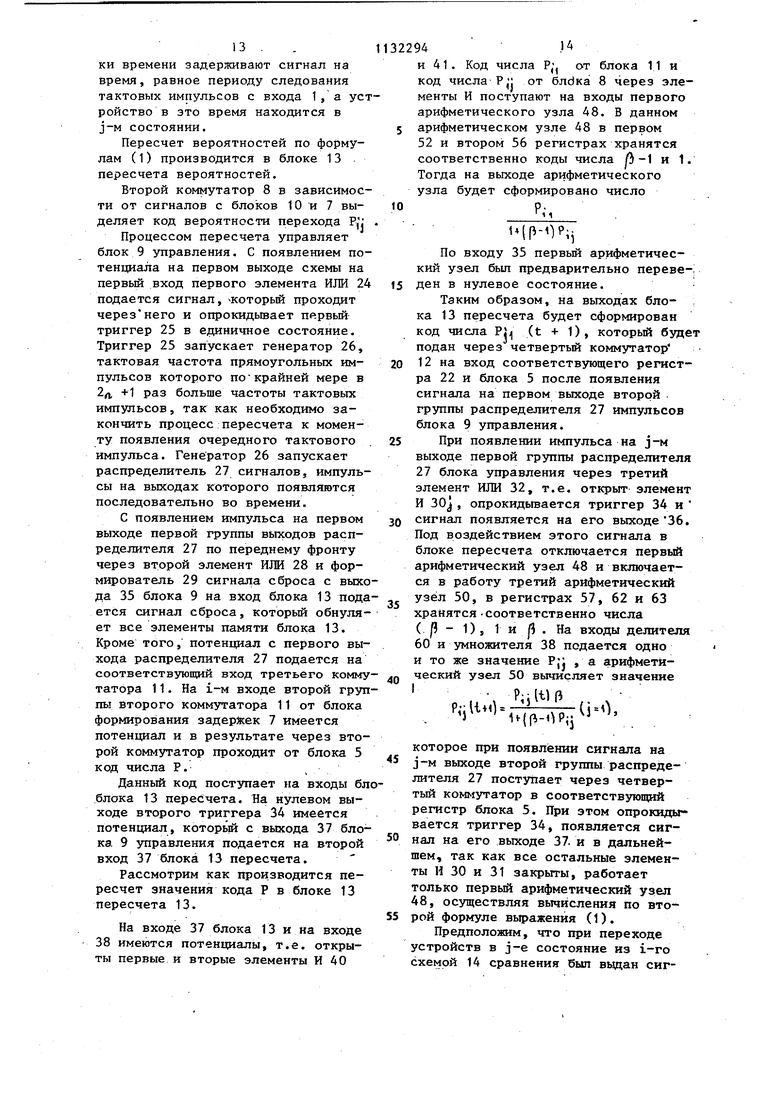

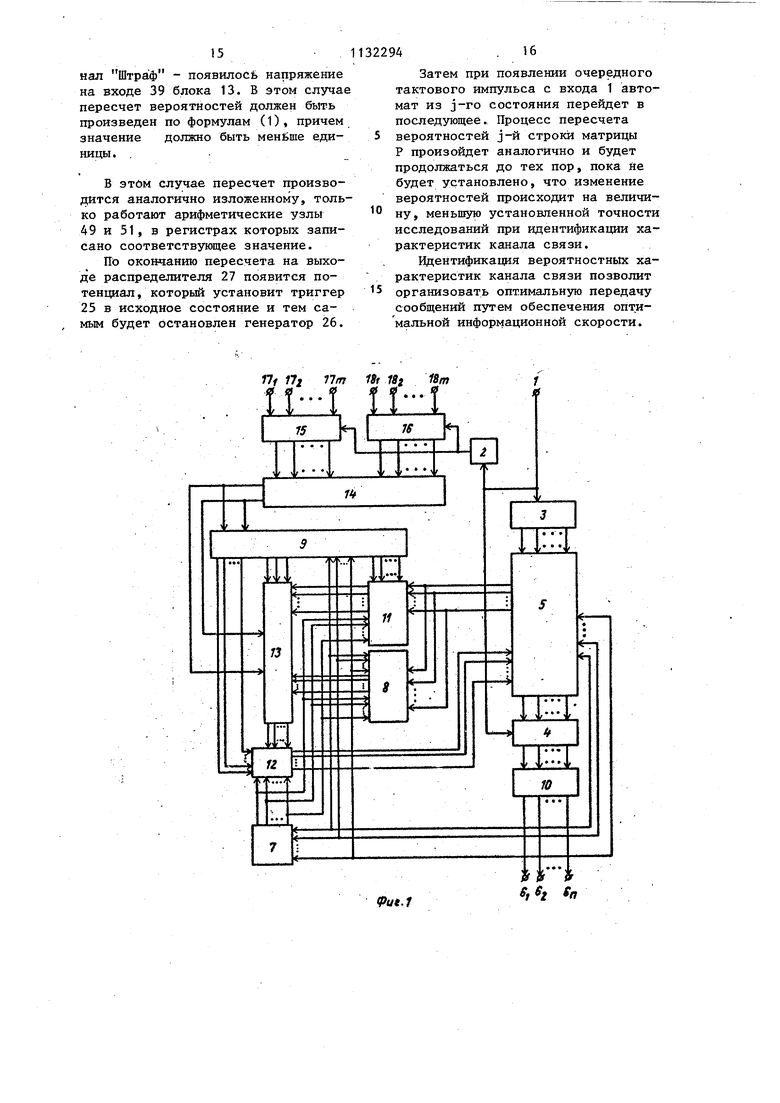

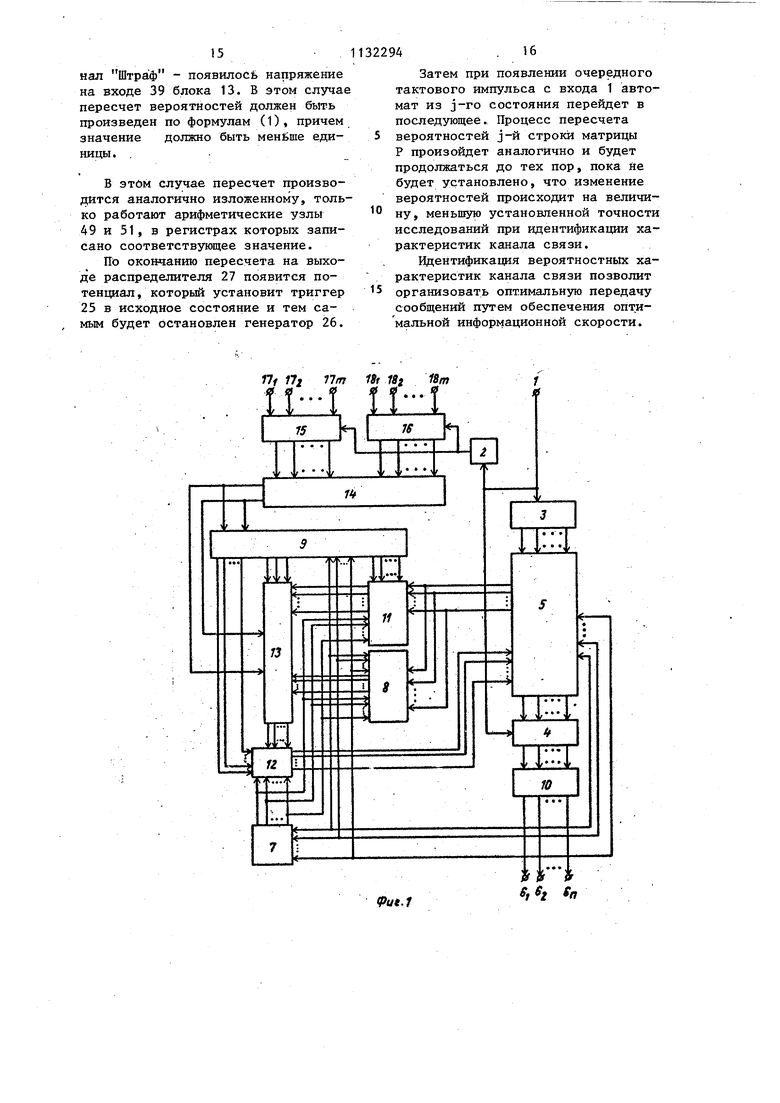

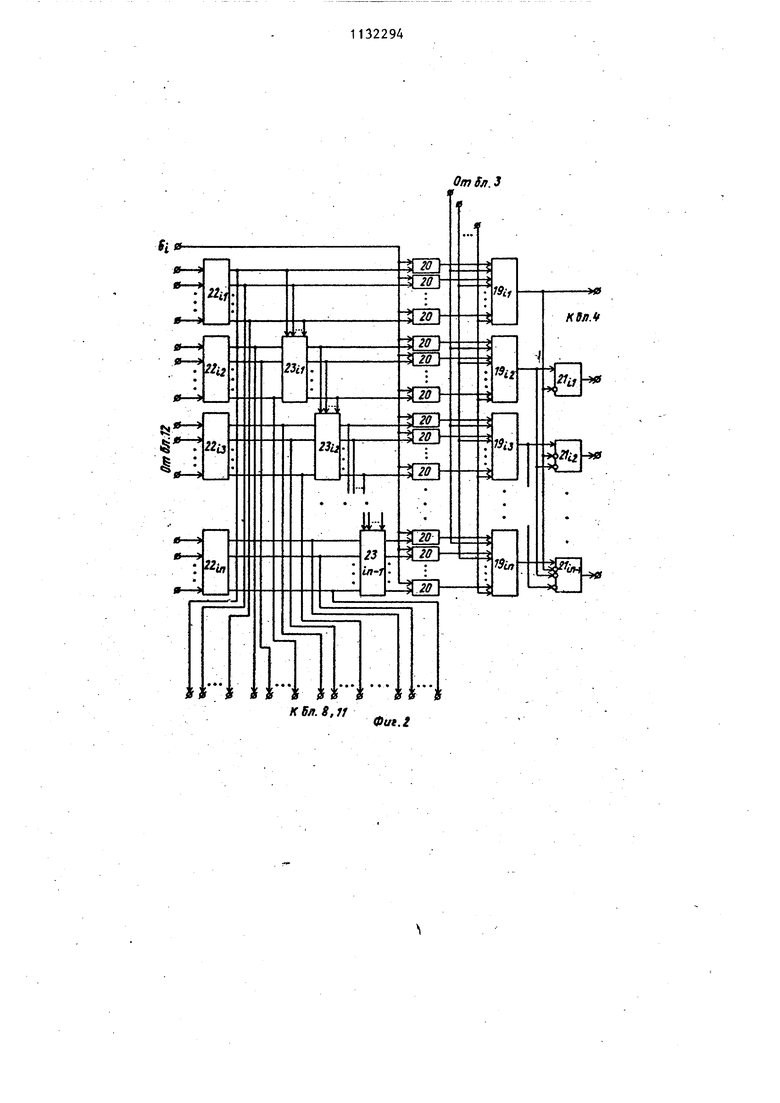

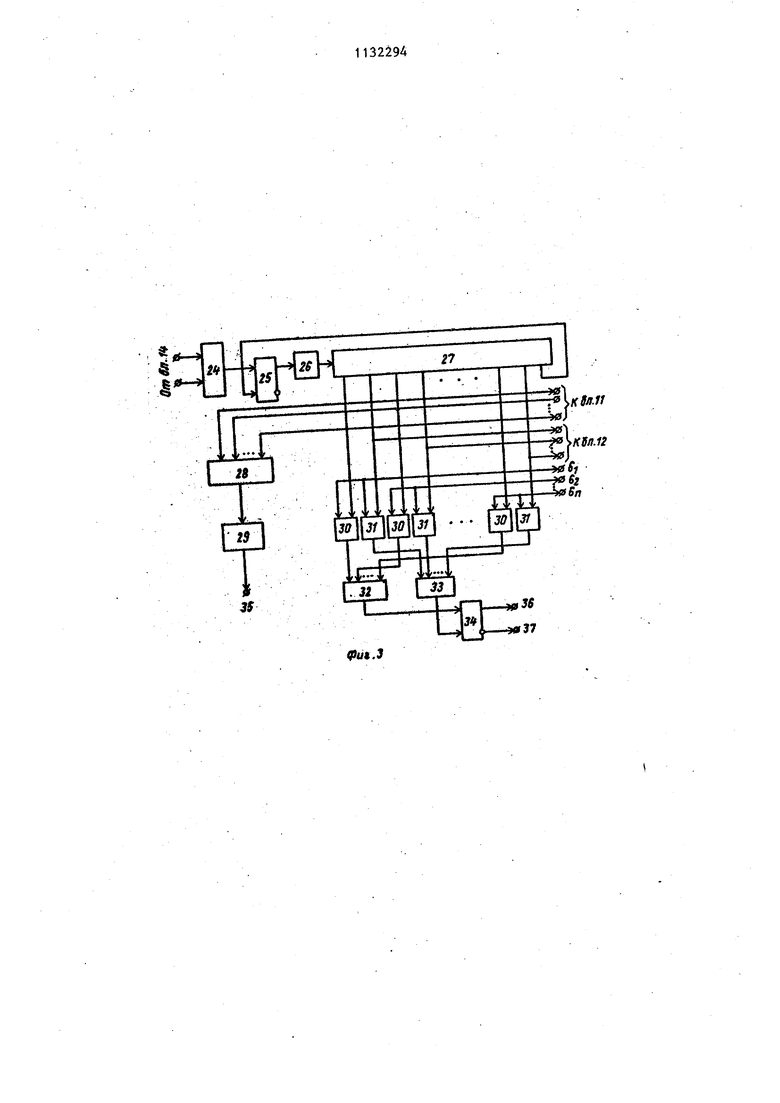

На фиг. 1 приведена структурная схема предлагаемого устройстваi на фиг. 2 - функциональная схема одного узл блока задания законов распределения, на фиг. 3 - функциональная схема блока управленияJ на фиг. 4 - структурная схема блока пересчета переходных вероятностейJ на фиг. 5 - фзнкциьнальная схема первого арифметического узла J на .фиг. 6 - функциональная схема второго арифмети еского узла.

Структурная схема устройства содержит тактовьй вход 1, формирователь 2 импульсов, представляющий собой дифференцирующую цепь с диодом и вьщеляющий задний фронт импульса генератор 3 случайного кода, первый коммутатор 4, блок 5.задания законов распределений, выходы 6 устройства, блок 7 задержки, второй ком32294 .

мутатор 8, блок 9 управления, первьй блок памяти 10, третий коммутатор 11, четвертый коммутатор 12, блок 13 пересчета вероятностей, схе5 му 14 сравнения кодов, второй 15 третий 16 блоки памяти, представляющие собой регистры, а также информационные входы 17 и 18. «. Каждьй узел блока 5 задания зако10 нов распределения (фиг. 2) содержит группу, схем 19 сравнения, первую 20 и вторую 21 группы элементов И, группу регистров 22, группу сумматоров 23.

15 Блок 9 управления (фиг. 3) содержит первьй элемент ИЛИ 24, первьш триггер 25, генератор 28 тактовых импульсов, распределитель 27 импульсов , второй элемент ИЛИ. 28, форми0 рователь 29 импульсов сброса, первую 30 и вторую 31 группы элементов И, третий 32 и четвертьй 33. элементы ИЛИ, второй триггер 34, выход 35 сброса, первьй 36 и второй 37

5 управляющий выходы.

Блок 13 пересчета (фиг. 4) вероятностей содержит первьй 38 и второй 39 переключающий входы первую восьмую группы 40-47 элементов И

0 первьй - четверд-ьй арифметические .узлы 48-51.

Первьй 48 и второй 49 арифметические узлы содержат (фиг. 5) первьй регистр 52, умножитель 53, сумматор 54, делитель 55 и второй регистр 56,

Третий 50 и четвертьй 51 арифме. тические узлы содержат (фиг. 6) первьй регистр 57, первьй умножитель

Q 58, сумматор 59, делитель 60, второй умножитель 61, второй 62 и третий 63 регистры.

Устройство работает следующим образом.

- По первому входу 1 подаются

тактовые сигналы, период следования которых определяется временем передачи одной кодовой комбинации по каналу связи, т.е. длина периода

0 равна произведению длины передаваемого кода на длительность элементарного импульса. Передаваемая в канал связи кодовая комбинация записывается по вторым входам 17 во

5 второй блок памяти 15, а принятая из канала связи кодовая комбинация записывается по третьим входам 18 в третий блок памяти 16. Принцип действия устройства строится на ба зе вероятностного автомата с перестраиваемой структурой и его спосо бе функционирования. Известно, что формально вероятностный автомат с перестраиваемой структурой описыва ся функцией переходов , заданной в виде матрицы переходных вероятностей, и функцией выходов, которая для данного случая однозначно опре деляется состояниями автомата. Про цесс передачи и искажения сообщений в канале связи также является марковским и может быть промоделирован на языке вероятностного авто мата, т.е. описан матрицей переход ных вероятностей, элемент P|j кото рой есть вероятность перехода из состояния передачи с i ошибками в кодовой комбинации в состояние передачи с j ошибками на последующем такте. Вероятностный автомат взаимодей ствует с внешней средой, вьщавая управляющие воздействия, и получает от среды сигналы Штраф и Поощрение. В зависимости от этих си налов происходит пересчет элементов матрицы переходных вероятностей оптимальным образом, т.е. автомат вырабатьшает оптимальные сиг налы управления и меняет для дости жения этой цели структуру матрищ.. Полученная матрица является модель среды, в которой работал автомат. Таким образом, применяя автомат с перестраиваемой структурой для про цесса управления выбором помехоустойчивого кода, можно идентифицировать неизвестные коэффициенты матрицы переходных вероятностей, которая будет моделью канала передачи дискретной информации и определит его стохастические характери тики. I Пусть в начальный момент времени в регистрах , блока 5 задания законов распределения записа ны любые величины вероятностей PJ: (i, j 1, п) матрицы Р причем вероятности в каждой строке нормированны по величине. Алгоритм работы устройства в целом определяется следующим образом. Синхронизация работы блоков устройства производится импульсами тактовой частиты, подаваемыми на вход 1. Предположим, что в момент t на выходе 6 имеется управлякядий потенциал, т.е. в канале связи передается и принимается кодовая комбинация с 1-1 ошибкой. По входам 17 во второй блок памяти 15 была записана кодовая комбинация на входе канала, а по входам 18 в третий блок памяти 16 быпа записана кодовая комбинация на выходе канала. Схема 14 сравнения кодов при одинаковых кодовых комбинациях в блоках 15 и 16 выдает сигнал на первом выходе. Если же произошло искажение, т.е. кодовые комбинации в блоках 15 и 16 неодинаковы (неравны поразрядно), то сигнал появляется на втором выходе блока 14. Сигнал на первом выходе рассматривается как сигнал Поощрение, а сигнал на вто втором цыходе блока 14 рассматривается как сигнал Штраф. Элементы i-й строки матрицы Р, хранящиеся в i-м узле блока 5., пересчитываются в зависимости от сигнала Штраф или Поощрение. Процедура пересчета организуется блоком 9 управления, причем через второй 8 и третий 11 коммутаторы в блок 13 пересчета вероятностей подаются коды вероятностей Р,; , а через четвертый коммутатор 12 в блок задания законов распределений подаются пересчитанные в блоке 13 новые значения вероятностей. При появлении очередного сигнала по входу 1 генератор 3 случайного кода вырабатывает код числа, равномерно распределенного в интервале от нуля до единицы. Блок 5 задания законов распределения вырабатывает очередной управляющий сигнал. Известно, что процесс идентификации с применением вероятностного автомата с перестраиваемой структурой является сходящимся, т.е. по истечению определенного отрезка времени в регистрах 22 блока 5 будут сформированы коды вероятностей матрищл переходных вероятностей Р, которая является моделью канала передачи дискретной информации. П На входы 17 и 18 устройства при ходят сигналы о элементахкода, поступающие в исследуемый канал св зи и приходящие из него соответств но. Во втором 15 и третьем 16 блоках памяти кодовые комбинации запоминаются и поэлементно поступают соответственно на входы схемы 14 сравнения кодов, в которой происходит сравнение соответствующих элементарных посьшок. С выходов схе мы 14 сравнения снимаются сигналы. Сигнал Штраф формируется в случа когда в исследуемом канале связи произошло искажение передаваемого символа, сигнал Поощрение формируется в случае, если такого искажения не произощло. Также импульсом по первому ВХОДУ; 1 открывается первый коммутатор 4, а генератор 3 случайного кода вьщает сигнал (число) , равномерно распределенный в интервале от нуля до единицы, на входы блока 5 задания законов распределения (фиг. 2). Устройство работает дискретно, переключая состояния своих выходов 6 в дискретные моменты времени tj, . Выбор нового состояния осуществляет ся в соответствии с Р матрицей пе реходных вероятностей, элементы которой (вероятности перехода) хранят ся в регистрах 22 блока 5 задания законов распределения. Пусть в момент времени автомат находится в i-M состоянии, т.е. на выходе 6;, имеется потенциал, в этом случае на соответствующий второй вход 6 блока 5 подается потенциал. Допустим, что процесс пересчета строки i переходных вероятностей матрицы Р закончен и новые значения вероятностей занесены в регистры 22 бло ка 5. В регистрах 22 блока 5 задания законов распределений хранятся коды переходных вероятностей матрицы

«

г

Р

. Р

rt2

П1

причем код Pjj хранится в регистре 22j, , а i-я строка матрицы хранится в регистрах 22 i-ro узла блока 5. На выходе сумматоров i-ro узла блока 5 хранится строчка

где и - коэффициент, значение которого больше единицы. Очевидно, что после пересчета условие нормирования удовлетворяется.

После перехода автомата в i-e состояние потенциал на выходах блока задержек 7 сохраняется на i-м выходе 6, так как элементы задерж9412 PI РI Fj,, .... М я P/J. + Р; + ... + Р: 1 гin Код, подаваемый от блока 3 в блок 5, обозначим Б. Код Б подается на первые входы схем 19 сравнения. Поскольку на входе 6/ имеется разрешающий потенциал с выхода устройства , то будут открыты первые элементы И 20, а AJ - коды чисел строки матрицы Р;, f Р;, + , ... i-ro узла блока 5, и коды чисел А из регистра 22,j и регистров 22 in поступят на вторые входы схем сравнения 19. Если код числа А; 5- Б, то на выходе схемы сравнения 1.9 будет единичный потенциал. Учитывая, что j 1, п, единичный потенциал будет на выходах и других схем 19 сравнения, для которых вьтолняется условие сравнения. Однако единичнъй потенциал будет лишь на j-м выходе i-узла блока 5. Со вторых выходов блока 5 снимаются коды пе- реходных вероятностей регистров 22. Потенциал с выхода блока 5 поступит на соответствующий вход первого коммутатора 4 и через него на i-и вход первого блока памяти 10, напряжение появится на выходе 6 устройства. Автомат перейдет,в j-e состояние из предьщущего i-ro. Допустим схема 14 сравнения на данное действие автомата вьщала Поощрение, т.е. на первом выходе 38блока оценки управления появится потенциал, а на втором выходе 39- нуль. В этом случае значение ероятностей перехода i-й строки атрицы Р должны быть пересчитаны огласно формулам P tbib- iiiili iiy 4fi-nPijli) Р, j.- - KJi кУ; iMf -OPiyU)

Пересчет вероятностей по формулам (1) производится в блоке 13 пересчета вероятностей.

Второй коммутатор 8 в зависимости от сигналов с блоков 10 и 7 выделяет код вероятности перехода Р,;

Процессом пересчета управляет блок 9 управления. С появлением потенциала на первом выходе схемы на первый вход первого элемента ИЛИ 24 подается сигнал, который проходит черезнего и опрокидьгоает первый триггер 25 в единичное состояние. Триггер 25 запускает генератор 26, тактовая частота прямоугольных импульсов которого покрайней мере в 2rt, +1 раз больше частоты тактовых импульсов, так как необходимо закончить процесс пересчета к моменту появления очередного тактового импульса. Генератор 26 запускает распределитель 27 сигналов, импульсы на выходах которого появляются последовательно во времени.

С появлением импульса на первом выходе первой группы выходов распределителя 27 по переднему фронту через второй элемент ИЛИ 28 и формирователь 29 сигнала сброса с выхода 35 блока 9 на вход блока 13 подается сигнал сброса, который обнуляет все элементы памяти блока 13. Кроме того, потенциал с первого выхода распределителя 27 подается на соответствующий вход третьего коммутатора 11. На i-M входе второй группы Второго коммутатора 11 от блока формирования задержек 7 имеется потенциал и в результате через второй коммутатор проходит от блока 5 код числа Р.

Данный код поступает на входы бл блока 13 пересчета. На нулевом выходе второго триггера 34 имеется потенциал, которьщ с выхода 37 блока. 9 управления подается на второй вход 37 блока 13 пересчета.

Рассмотрим как производится пересчет значения кода Р в блоке 13 пересчета 13.

На входе 37 блока 13 и на входе 38 имеются потенциалы, т.е. открыты первые и вторые элементы И 40

14

132294

и 41. Код числа Р;, от блока 11 и код числа от бпдка 8 через элементы И поступают на входы первого арифметического узла 48. В данном 5 арифметическом узле 48 в первом 52 и втором 56 регистрах хранятся соответственно коды числа ft-1 и 1. Тогда на выходе арифметического узла будет сформировано число

°РМ

мр-о%

По входу 35 первый арифметический узел был предварительно переве5 ден в нулевое состояние.

Таким образом, на выходах бло- ; ка 13 пересчета будет сформирован код числа PJj| (t + 1), который будет подан через четвертый коммутатор

0 12 на вход соответствующего регистра 22 и блока 5 после появления сигнала на первом выходе второй группы распределителя 27 импульсов блока 9 управления.

5 При появлении импульса на J-M выходе первой группы распределителя 27 блока управления через третий элемент ИЛИ 32, т.е. открыт элемент И 30J, опрокидьгеается триггер 34 и

0 сигнал появляется на его выходе36. Под воздействием этого сигнала в блоке пересчета отключается первый арифметический узел 48 и включается в работу третий арифметический

узел 50, в регистрах 57, 62 и 63 хранятся.соответственно числа (- 1) 1и/1. На входы делителя 60 и умножителя 38 подается одно и то же значение Р; , а арифметический узел 50 вычисляет значение

I

.o.

которое при появлении сигнала на J-M выходе второй группы распределителя 27 поступает через четвертый коммутатор в соответствующий регистр блока 5. При этом опрокиды вается триггер 34, появляется сигнал на его выходе 37. и в дальнейшем, так как все остальные элементы И 30 и 31 закрыты, работает только первый арифметический узел 48, осуществляя вычисления по второй формуле выражения (1).

Предположим, что при переходе устройств в j-e состояние из i-ro схемой 14 сравнения бьш вьщан сиг15нал Штраф - появилось напряжение на входе 39 блока 13. В этом случа пересчет вероятностей должен быть произведен по формулам (1), причем значение должно быть меньше единицы . , В этим случае пересчет производится аналогично изложенному, толь ко работают арифметические узлы Л9 и 51, в регистрах которых записано соответствующее значение. По окончанию пересчета на выходе распределителя 27 появится потенциал, который установит триггер 25 в исходное состояние и тем самым будет остановлен генератор 26. 4 Затем при появлении очередного тактового импульса с входа 1 автомат из j-ro состояния перейдет в последующее. Процесс пересчета вероятностей j-й строки матрицы Р произойдет аналогично и будет продолжаться до тех пор, пока не будет установлено, что изменение вероятностей происходит на величину, меньшую установленной точности исследований при идентификации характеристик канала связи. Идентификация вероятностных характеристик канала связи позволит организовать оптимальную передачу сообщений пзггем обеспечения оптимальной инфop faциoннoй скорости.

От Л. J

37 3S OmUJt.ff

39

(pui.5

фиг.в

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР по заявке № 3419861/18-24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3558257/18-24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-12-30—Публикация

1983-06-07—Подача