Изобретение относится к вычислительной технике, в частности к устройствам для получения псевдослучайных величин, и может быть использовано для статистического моделирования.

В вычислительной технике известно устройство формирования целочисленных случайных величин с равномерным законом распределения, лежащих в заданном диапазоне, в котором используется датчик случайных чисел, состоящий из физического генератора шума, амплитуда выходного сигнала которого изменяется во времени случайным образом, ограничителя уровня, счетчика, блока преобразования чисел в заданный диапазон и взятия целой части числа.

Недостатками устройства являются неустойчивая работа датчика в условиях нестабильности параметров элементов схемы генератора шума, а также невозможность точного воспроизведения результатов формирования случайных чисел, что затрудняет контроль и отладку моделей.

Известно также устройство формирования целочисленных псевдослучайных величин с равномерным законом распределения, лежащих в заданном диапазоне, в котором используются программный датчик псевдослучайных величин, распределенных равномерно на интервале (0, 1), и блок преобразования чисел в заданный диапазон, реализующий операции умножения, суммирования и взятия целой части числа.

Однако данное устройство также имеет недостатки. Практика эксплуатации датчиков равномерно распределенных псевдослучайных чисел, реализованных на элементах вычислительной техники, показала, что ввиду конечности числа разрядов представления чисел (т.е. ограниченности длины периода последовательности максимальной длины) целочисленные псевдослучайные величины в заданном диапазоне повторяются. Это явление для некоторых задач статистического моделирования является нежелательным. Кроме того, наблюдаются существенное отклонение закона распределения получаемых чисел от равномерного, а также большой разброс заданных числовых характеристик получаемых реализаций, что также ограничивает практическое применение устройства.

Наиболее близким техническим решением к изобретению является генератор равномерно распределенных псевдослучайных величин, который содержит первый и второй генераторы запускающих импульсов, первый, второй и третий элементы задержки, элемент ИЛИ, триггер, генератор тактовых импульсов, счетчик, группу элементов И, блок регистров памяти, блок из N групп по N элементов И в группе, N элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, схему сравнения и регистр памяти.

Однако известное устройство является генератором равномерно распределенных псевдослучайных величин и предназначено для формирования заданного количества псевдослучайных чисел заданной разрядности, которые распределены равномерно на интервале (0.1). В этом устройстве отсутствуют элементы, позволяющие генерировать распределенные равномерно целочисленные псевдослучайные величины, лежащие в заданном диапазоне. Кроме того, в силу традиционности используемого механизма получения псевдослучайных чисел в данном устройстве построенное на его основе устройство формирования целочисленных псевдослучайных величин (с добавлением блока преобразования чисел в заданный диапазон) имеет своими недостатками: повторяемость целочисленных псевдослучайных величин, а также отклонение закона распределения от равномерного.

Цель изобретения повышение точности распределения с одновременной реализацией возможности генерирования распределенных равномерно целочисленных псевдослучайных величин, лежащих в заданном диапазоне.

Для достижения цели в устройство формирования равномерно распределенных псевдослучайных величин, содержащее первый и второй генераторы запускающих импульсов, первый, второй и третий элементы задержки, элемент ИЛИ, триггер, генератор тактовых импульсов, счетчик, группу элементов И, блок регистров памяти, блок из N групп по N элементов И в группе, N элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, схему сравнения и регистр памяти, введены четвертый, пятый, шестой, седьмой, восьмой и девятый элементы задержки и шесть формирователей, причем вход четвертого элемента задержки устройства соединен с выходом третьего элемента задержки генератора равномерно распределенных псевдослучайных величин, выход четвертого элемента задержки соединен с входом первого формирователя и входом пятого элемента задержки устройства, выход пятого элемента задержки соединен с входом второго формирователя и входом шестого элемента задержки устройства, выход шестого элемента задержки соединен с входом третьего формирователя и входом седьмого элемента задержки устройства, выход седьмого элемента задержки соединен с входом четвертого формирователя и восьмого элемента задержки устройства, выход восьмого элемента задержки соединен с входом пятого формирователя, вход девятого элемента задержки устройства соединен с выходом схемы сравнения генератора, выход девятого элемента задержки соединен с входом шестого формирователя, n (n требуемое количество чисел) сумматоров, первый и второй регистры устройства, регистр упорядочиваемой последовательности, информационный вход которого соединен с выходами N элементов ИСКЛЮЧАЮЩЕЕ ИЛИ генератора, вход разрешения записи с выходом первого формирователя, вход начальной установки с выходом второго генератора запускающих импульсов, а вход разрешения выдачи числа с выходом второго формирователя, регистр последовательности номеров упорядочиваемых псевдослучайных чисел, информационный вход которого соединен с выходом счетчика генератора, вход разрешения записи с выходом первого формирователя, вход начальной установки с выходом второго генератора запускающих импульсов, а вход разрешения выдачи числа с выходом второго формирователя, n 1 блоков упорядочения и формирования рангов псевдослучайных чисел, каждый из которых содержит первый и второй регистры, коммутатор последовательности рангов, схему сравнения и коммутатор упорядочиваемой последовательности, причем первые входы схемы сравнения и коммутатора упорядочиваемой последовательности каждого блока упорядочения и формирования рангов соединены с выходом регистра упорядочиваемой последовательности устройства, а входы разрешения выдачи информации схемы сравнения каждого блока упорядочения и формирования рангов соединены с выходом четвертого формирователя, элемент И, один из входов которого соединен с выходом схемы сравнения, а другой вход с выходом пятого формирователя, информационный вход первого регистра первого блока упорядочения и формирования рангов соединен с выходом регистра упорядочиваемой последовательности устройства, вход разрешения записи первого регистра каждого блока упорядочения и формирования рангов соединен с выходом элемента И, вход начальной установки с выходом второго генератора запускающих импульсов, а вход разрешения выдачи числа с выходом третьего формирователя, выход первого регистра каждого блока упорядочения и формирования рангов соединен с вторыми входами схемы сравнения и коммутатора упорядочиваемой последовательности, управляющий вход которого соединен с выходом схемы сравнения, информационный вход второго регистра первого блока упорядочения и формирования рангов соединен с выходом регистра последовательности псевдослучайных чисел устройства, вход разрешения записи второго регистра каждого блока упорядочения и формирования рангов соединен с выходом элемента И, вход начальной установки с выходом второго генератора запускающих импульсов, а вход разрешения выдачи числа с выходом третьего формирователя, выход второго регистра каждого блока упорядочения и формирования рангов соединен с вторым входом коммутатора последовательности рангов и с первым входом соответствующего сумматора, первый вход коммутатора последовательности рангов каждого блока упорядочения и формирования рангов соединен с выходом регистра номеров упорядочиваемых чисел устройства, а управляющий вход соединен с выходом схемы сравнения, выходы коммутатора упорядочиваемой последовательности и коммутатора последовательности рангов, начиная с первого блока упорядочения и формирования рангов, соединены с информационными входами первого и второго регистров соответственно последующих блоков упорядочения и формирования рангов, а выходы коммутатора упорядочиваемой последовательности и коммутатора последовательности рангов (n 1)-го блока упорядочения и формирования рангов соединены с информационными входами первого и второго регистров устройства соответственно, входы управления записью которых соединены с выходом пятого формирователя, выход второго регистра устройства соединен с первым входом n-го сумматора, вторые входы всех сумматоров соединены соответственно диапазону вырабатываемых целочисленных псевдослучайных величин с выходом первого генератора запускающих импульсов, входы разрешения выдачи числа всех сумматоров соединены с выходом шестого формирователя, а выходы сумматоров являются выходами устройства.

Введенные элементы, позволяющие достичь цель повышение точности распределения с одновременной реализацией возможности генерирования распределенных равномерно целочисленных псевдослучайных величин, лежащих в заданном диапазоне, и отличающие заявляемое техническое решение от прототипа позволяют сделать вывод о соответствии критерию "новизна".

Свойства, отличающие заявляемое техническое решение от прототипа, не выявлены в других технических решениях при изучении данной и смежных областей техники и, следовательно, обеспечивают заявляемому решению соответствие критерию "существенные отличия", а именно обеспечение возможности получения распределенных равномерно целочисленных псевдослучайных величин, лежащих в заданном диапазоне, исключение повторяемости величин в заданном диапазоне и повышение точности их равномерного распределения.

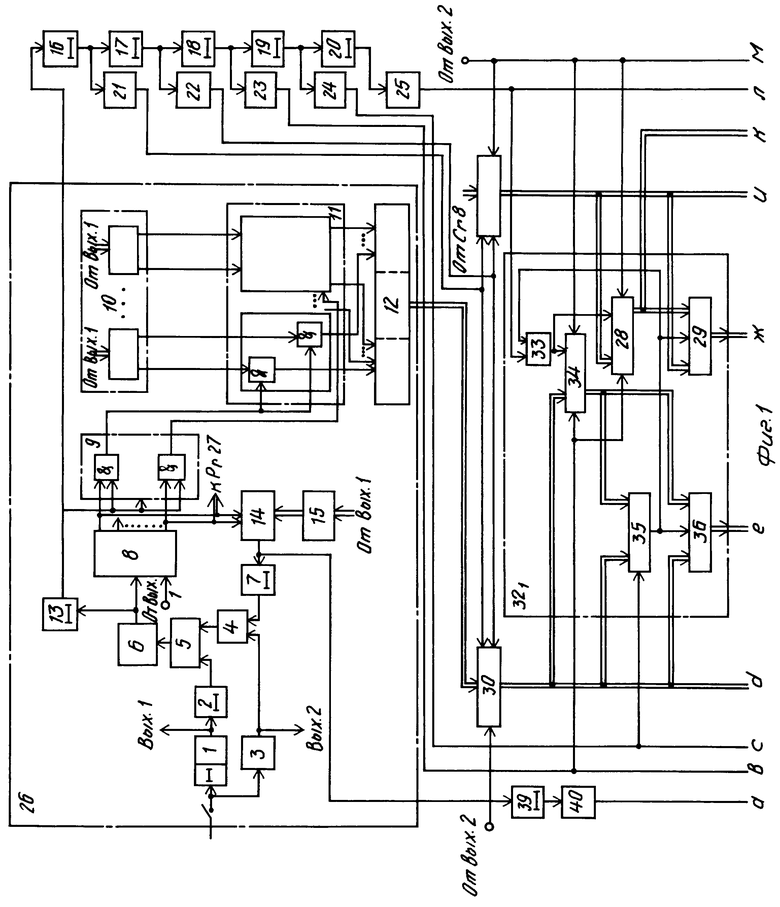

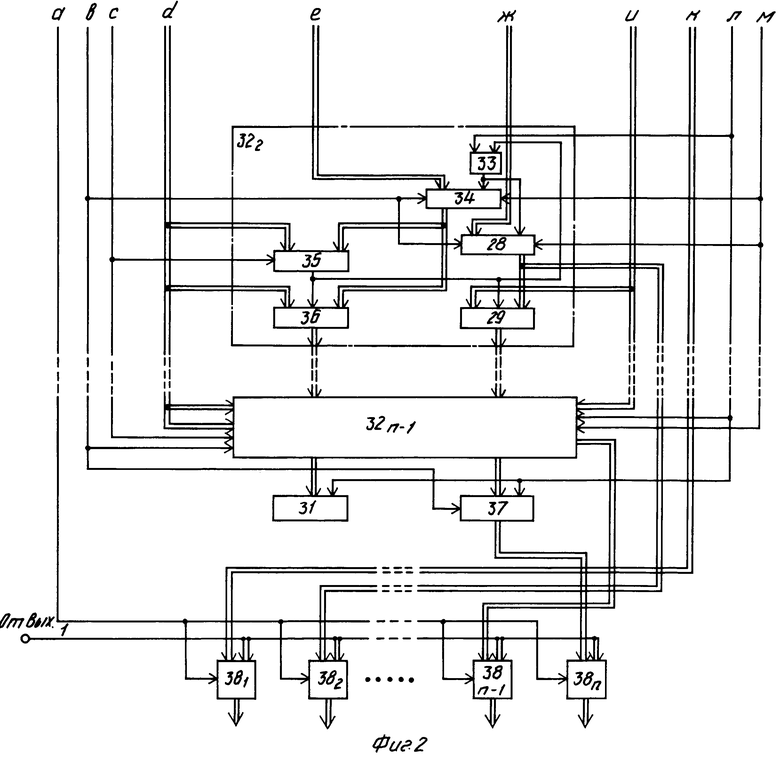

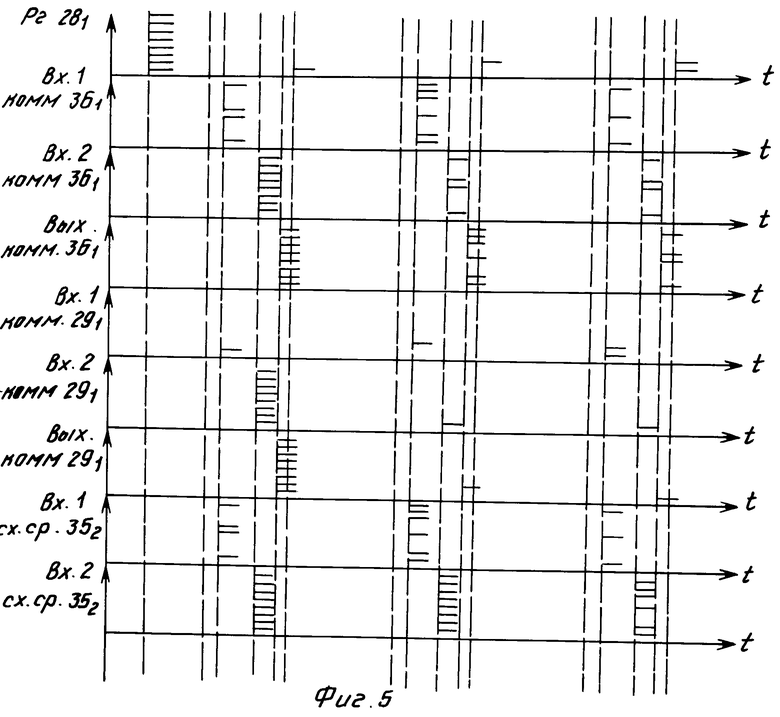

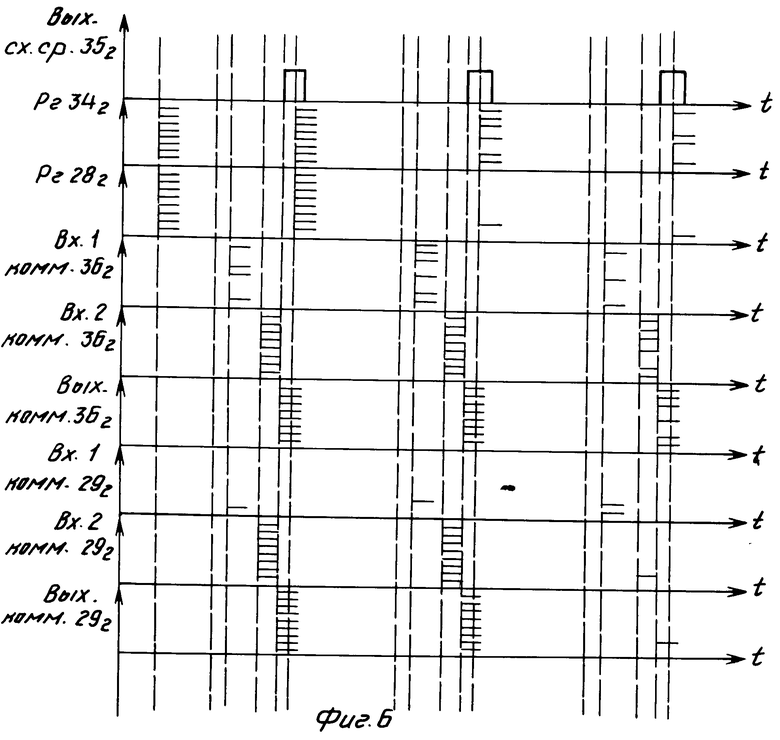

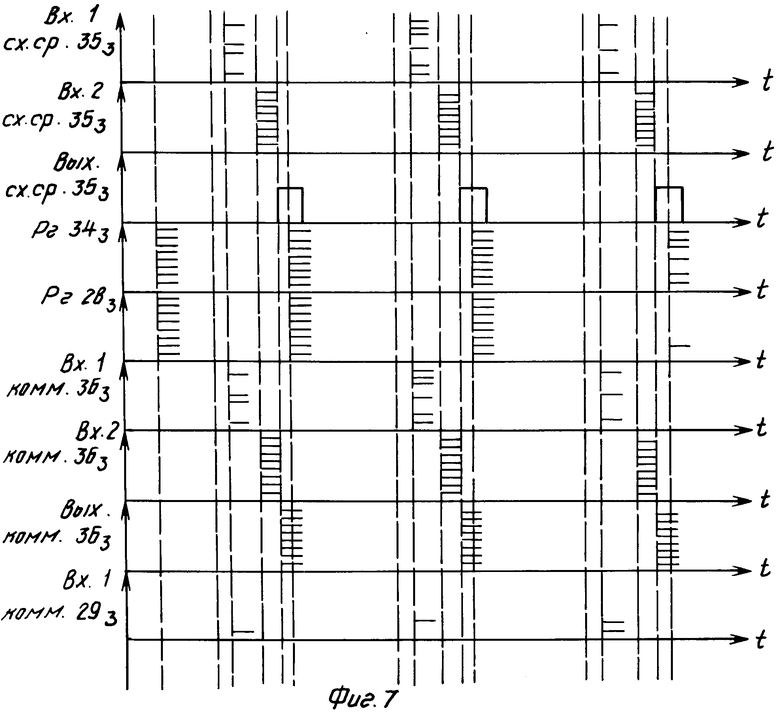

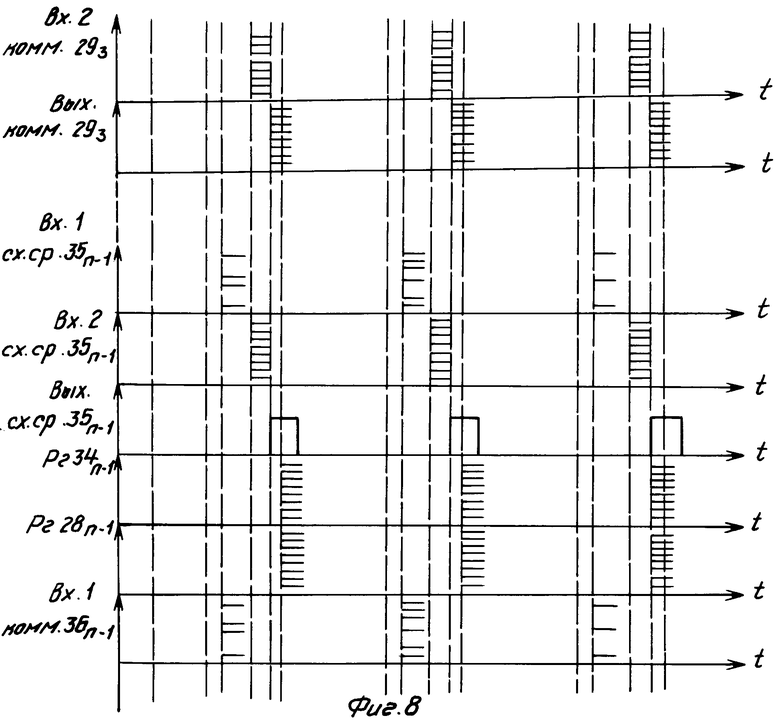

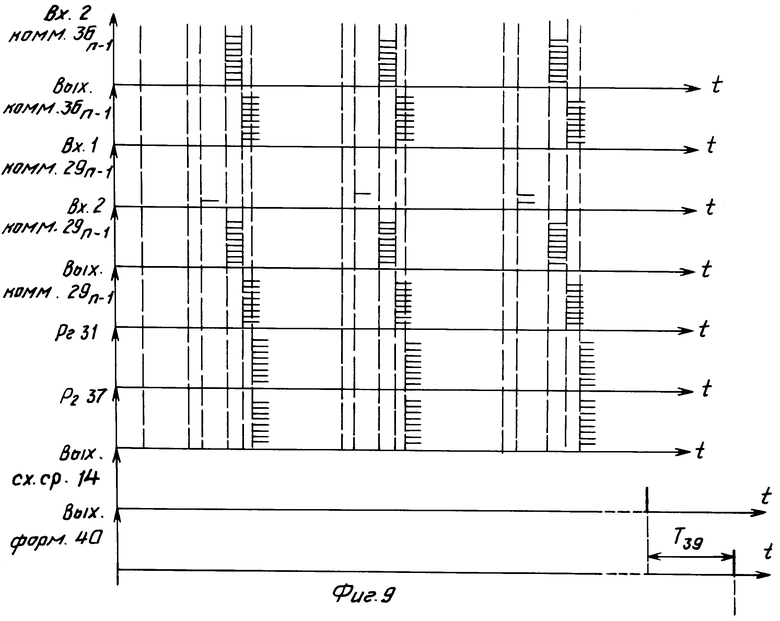

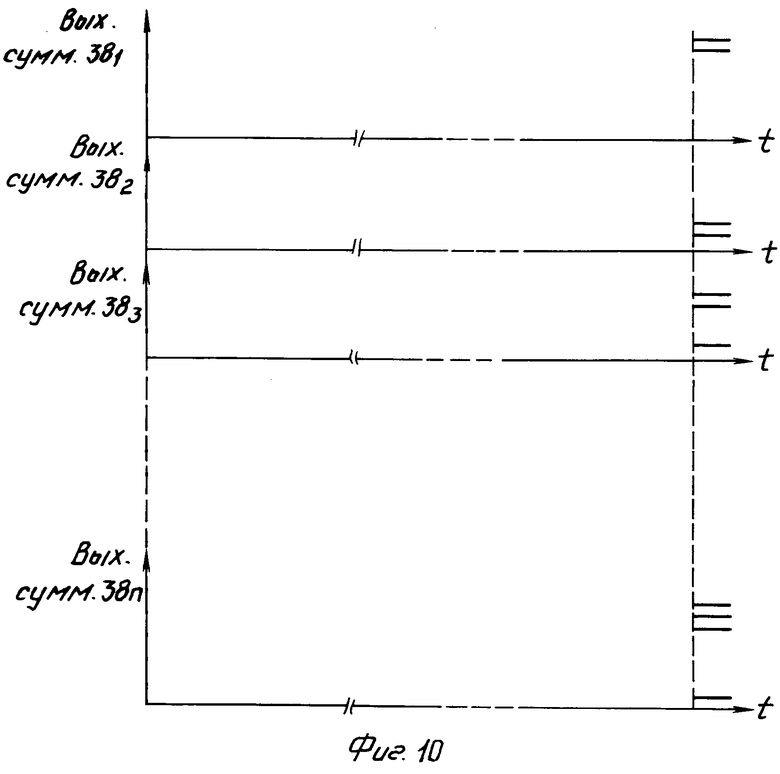

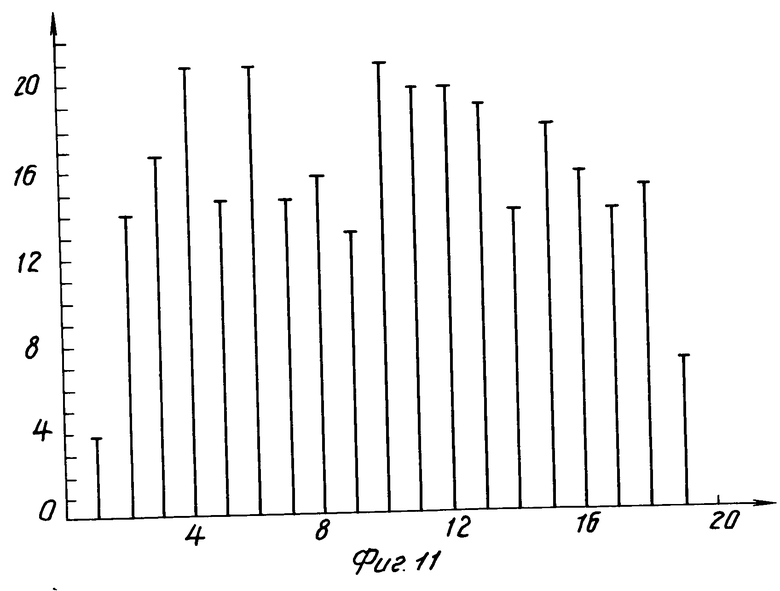

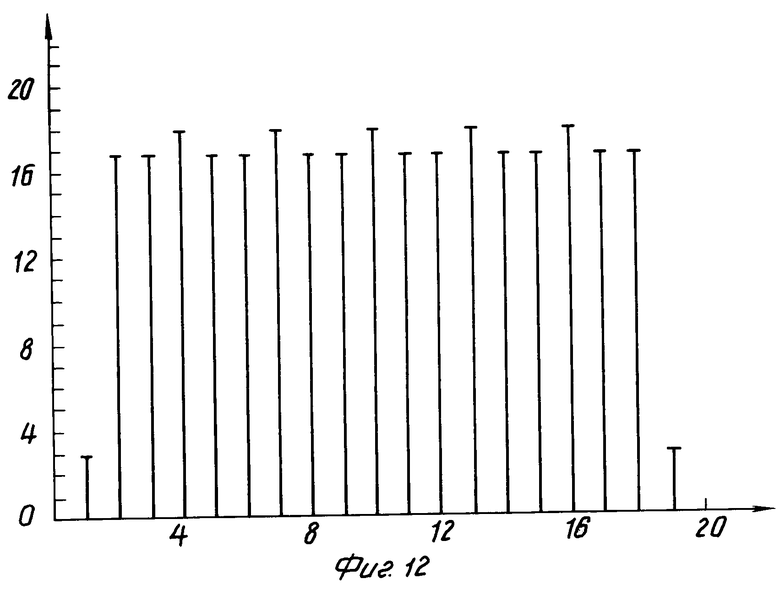

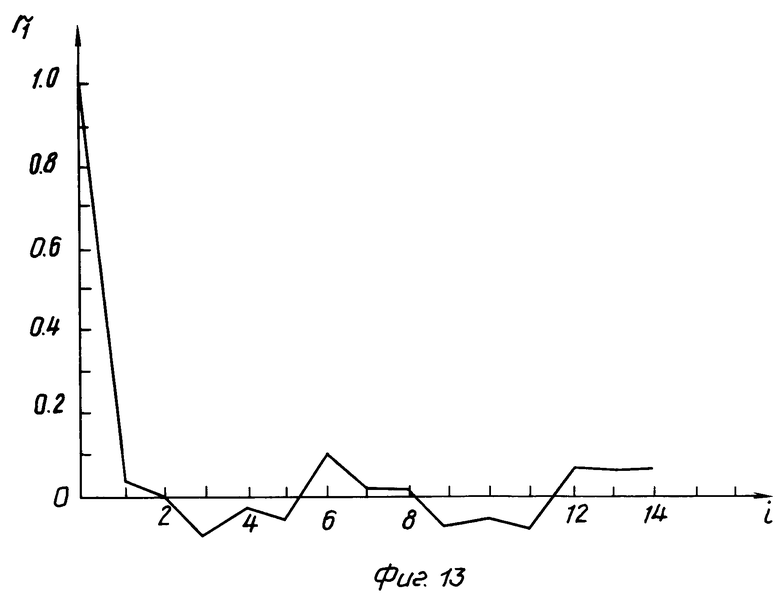

На фиг. 1 и 2 представлена блок-схема предлагаемого устройства для формирования равномерно распределенных целочисленных псевдослучайных величин, лежащих в заданном диапазоне; на фиг. 3-10 приведены временные диаграммы работы предлагаемого устройства; на фиг. 11 и 12 гистограммы равномерно распределенных целочисленных псевдослучайных величин, выработанных сопоставимыми моделями прототипа с блоком преобразования чисел в заданный интервал (фиг. 11) и заявляемого устройства (фиг. 12); на фиг. 13 и 14 графики оценки выборочных автокорреляционных функций псевдослучайных последовательностей, выработанных моделью прототипа (фиг. 13) и заявляемого устройства (фиг. 14).

Устройство содержит генератор 26 равномерно распределенных на интервале (0,1) псевдослучайных величин, в который входят первый и второй генераторы 1 и 3 запускающих импульсов, первый, второй и третий элементы 2, 7 и 13 задержки, элемент ИЛИ 4, триггер 5, генератор 6 тактовых импульсов, счетчик 8, группа 9 элементов И, блок 10 регистров памяти, блок 11 из N групп по N элементов И в группе, N элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 12, схему 14 сравнения и регистр 15 памяти, шесть элементов 16-20 и 39 задержки, шесть формирователей 21-25 и 40, n сумматоров 38, первый регистр 31 и второй регистр 37 устройства, регистр 30 упорядочиваемой последовательности, регистр 27 последовательности номеров упорядочиваемых псевдослучайных чисел, n 1 блоков 32 упорядочения и формирования рангов псевдослучайных чисел, каждый из которых содержит первый регистр 34, второй регистр 28, коммутатор 29 последовательности рангов, схему 35 сравнения, коммутатор 36 упорядочиваемой последовательности и элемент И 33.

Входы каждого из N элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 12 соединены с соответствующими выходами элементов И блока 11 из N групп по N элементов И в группе, первые входы элементов И каждой из групп которого соединены с выходом соответствующего элемента И группы 9. Первые входы элементов И группы 9 соединены с выходами соответствующих разрядов счетчика 8 и с первой группой входов схемы 14 сравнения, вторая группа входов которой соединена с выходами регистра 15 памяти. Соответствующие установочные входы триггеров регистра 15 соединены с установочным входом счетчика 8, установочным входом блока 10 регистров памяти, входом первого элемента 2 задержки и выходом первого генератора 1 запускающих импульсов, вход которого соединен с входом второго генератора 3 запускающих импульсов. Выход генератора 3 через элемент ИЛИ 4 соединен с первым входом триггера 5, второй вход которого соединен с выходом первого элемента 2 задержки. Выход схемы 14 сравнения через второй элемент 7 задержки соединен с вторым входом элемента ИЛИ 4, выход триггера 5 соединен с входом генератора 6 тактовых импульсов, выход которого соединен с входом синхронизации счетчика 8 непосредственно, а с вторыми входами элементов И группы 9 через третий элемент 13 задержки. Выходы регистров блока 10 регистров памяти соединены с вторыми входами элементов И соответствующей группы элементов И блока 11 из N групп по N элементов И в группе. Вход четвертого элемента 16 задержки устройства соединен с выходом третьего элемента 13 задержки генератора равномерно распределенных псевдослучайных величин, выход четвертого элемента 16 задержки соединен с входом первого формирователя 21 и входом пятого элемента 17 задержки устройства. Выход пятого элемента 17 задержки соединен с входом второго формирователя 22 и входом шестого элемента 18 задержки устройства, выход шестого элемента 18 задержки соединен с входом третьего формирователя 23 и входом седьмого элемента 19 задержки устройства. Выход седьмого элемента 19 задержки соединен с входом четвертого формирователя 24 и входом восьмого элемента 20 задержки устройства, выход восьмого элемента 20 задержки соединен с входом пятого формирователя 25. Вход девятого элемента 39 задержки устройства соединен с выходом схемы 14 сравнения генератора 26, выход девятого элемента 39 задержки устройства соединен с входом шестого формирователя 40. Информационный вход регистра 30 упорядочиваемой последовательности соединен с выходами N элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 12 генератора 26, вход разрешения записи соединен с выходом первого формирователя 21, вход начальной установки с выходом второго генератора 3 запускающих импульсов, а вход разрешения выдачи числа с выходом второго формирователя 22. Информационный вход регистра 27 последовательности номеров упорядочиваемых псевдослучайных чисел соединен с выходом счетчика 8 генератора 26, вход разрешения записи соединен с выходом первого формирователя 21, вход начальной установки с выходом второго генератора 3 запускающих импульсов, а вход разрешения выдачи числа с выходом второго формирователя 22.

Первые входы схемы 35 сравнения и коммутатора 36 упорядочиваемой последовательности каждого блока 32 упорядочения и формирования рангов соединены с выходом регистра 30 упорядочиваемой последовательности устройства, а входы разрешения выдачи информации схемы 35 сравнения каждого блока 32 упорядочения и формирования рангов соединены с выходом четвертого формирователя 24. Один из входов элементов И 33 соединен с выходом схемы 35 сравнения, а другой вход с выходом пятого формирователя 25. Информационный вход первого регистра 34 первого блока 32 упорядочения и формирования рангов соединен с выходом регистра 30 упорядочиваемой последовательности устройства, вход разрешения записи первого регистра 34 каждого блока 32 упорядочения и формирования рангов соединен с выходом элемента И 33, вход начальной установки с выходом второго генератора 3 запускающих импульсов, а вход разрешения выдачи числа с выходом третьего формирователя 23. Выход первого регистра 34 каждого блока 32 упорядочения и формирования рангов соединен с вторыми входами схемы 35 сравнения и коммутатора 36 упорядочиваемой последовательности, управляющий вход которого соединен с выходом схемы 35 сравнения. Информационный вход второго регистра 28 первого блока 32 упорядочения и формирования рангов соединен с выходом регистра 27 последовательности номеров псевдослучайных чисел устройства, вход разрешения записи второго регистра 28 каждого блока 32 упорядочения и формирования рангов соединен с выходом элемента И 33, вход начальной установки с выходом второго генератора запускающих импульсов, а вход разрешения выдачи числа с выходом третьего формирователя 23. Выход второго регистра 28 каждого блока 32 упорядочения и формирования рангов соединен с вторым входом коммутатора 29 последовательности рангов и с первым входом соответствующего сумматора 38. Первый вход коммутатора 29 последовательности рангов каждого блока 32 упорядочения и формирования рангов соединен с выходом регистра 27 номеров упорядочиваемых чисел устройства, а управляющий вход соединен с выходом схемы 35 сравнения. Выходы коммутатора 36 упорядочиваемой последовательности и коммутатора 29 последовательности рангов, начиная с первого блока 32 упорядочения и формирования рангов, соединены с информационными входами первого и второго регистров 34 и 28 соответственно последующих блоков упорядочения и формирования рангов, а выходы коммутатора 36 упорядочиваемой последовательности и коммутатора 29 последовательности рангов (n 1)-го блока 32 упорядочения и формирования рангов соединены с информационными входами первого и второго регистров 31 и 37 устройства соответственно, входы управления записью которых соединены с выходом пятого формирователя 25. Выход второго регистра 37 устройства соединен с первым входом n-го сумматора 38, вторые входы всех сумматоров 38 соединены соответственно диапазону вырабатываемых целочисленных псевдослучайных величин с выходом первого генератора 1 запускающих импульсов, входы разрешения выдачи числа всех сумматоров 38 соединены с выходом шестого формирователя 40, а выходы сумматоров 38 являются выходами устройства.

Суть изобретения заключается в достижении цели за счет применения к исходной последовательности, вырабатываемой генератором равномерно распределенных псевдослучайных величин, нелинейного преобразования. Именно, исходную последовательность равномерно распределенных на интервале (0, 1) псевдослучайных величин, сформированных известным устройством, упорядочивают по возрастанию и одновременно формируют последовательность рангов исходных величин. В качестве искомой последовательности равномерно распределенных целочисленных псевдослучайных величин, лежащих в заданном диапазоне, берется полученная последовательность рангов, каждый член которой суммируется с заданной константой.

Пусть с помощью генератора образуется выборка объема n и из исходной совокупности извлекается очередной элемент, которому предстоит занять свое место в упорядоченном ряду. Каким будет его ранг? Очевидно, если значение ζi (i n + 1), присущее элементу, еще не известно, или с другими элементами он не сравнивался, объективная возможность для него занять любое из мест в выборке одинакова. Это значит, что совокупность рангов случайная n-мерная дискретная величина и распределена равновероятно. Таким образом, применяя к исходной последовательности псевдослучайных величин операцию упорядочения и одновременно формируя их ранги, получают целочисленную выборку рангов, распределенную по равномерному закону на интервале [1, n] где n объем выборки, даже если у исходной выборки закон распределения отличается от равномерного. Если определить ранг как номер наблюдения в упорядоченном ряду, то исключается также эффект повторяемости целочисленных псевдослучайных величин. Применяя операцию сдвига к каждой из полученных псевдослучайных величин (а именно суммируя их с константой, равной разности левой (правой) границы требуемого диапазона и левой (правой) границы полученной последовательности рангов), получают равномерно распределенные целочисленные псевдослучайные величины, лежащие в заданном диапазоне.

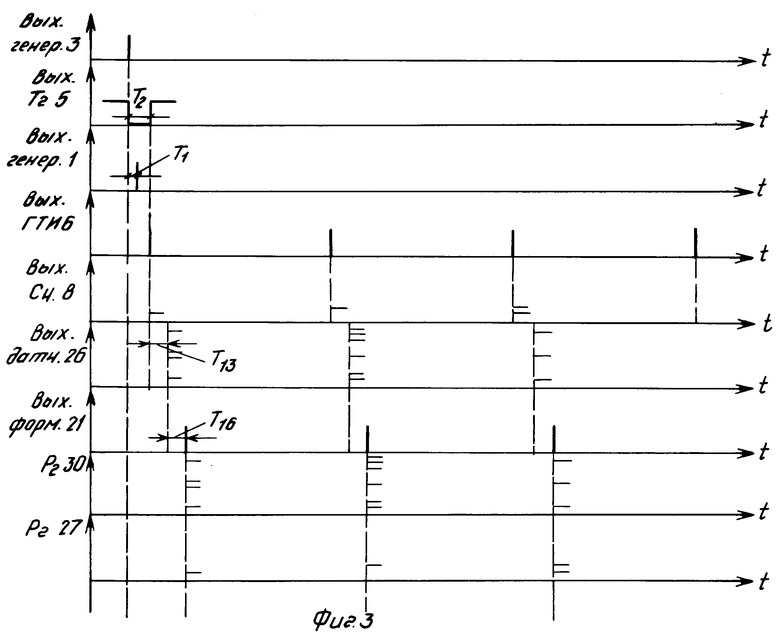

Устройство работает следующим образом (фиг. 3-10). С включением устройства управляющее напряжение подается на генераторы 1 и 3 запускающих импульсов. При этом генератор 3 вырабатывает импульс, который через элемент ИЛИ 4 поступает на вход установки в ноль триггера 5 и устанавливает его в нулевое состояние. Этим же импульсом производится установка в единицу регистров 34 и 28 каждого блока 32 упорядочения и формирования рангов, а также установка в ноль регистров 30 и 27 устройства. После задержки на время Т1 переходных процессов в триггере 5 генератор 1 также вырабатывает импульс, который обнуляет счетчик 8 и устанавливает в соответствующие состояния триггеры блока 10 регистров памяти, регистра 15 памяти и регистры сумматоров 38. При этом в регистре 15 памяти устанавливается число, соответствующее числу точек, которые должны быть сформированы генератором равномерно распределенных псевдослучайных величин, а в регистрах сумматоров 38 устанавливается число k 1 (либо l k), где k и l левая и правая границы соответственно заданного диапазона формирования целочисленных псевдослучайных величин, что обеспечивается соответствующим соединением выхода генератора 1 с входами триггеров регистра 15 памяти и регистров сумматоров 38. Кроме того, импульс с выхода генератора 1 запускающих импульсов после задержки в элементе 2 на время Т2 переходных процессов при записи чисел в регистры памяти 15, блока 10 и сумматоров 38 подается на второй вход триггера 5 и устанавливает его в единичное состояние. В результате начинает работать генератор 6 тактовых импульсов, сигналы которого поступают на счетный вход счетчика 8. Счетчик 8 формирует номера точек, каждого из которых соответствует определенное состояние разрядов счетчика. Импульс, который был подан на вход счетчика 8, после задержки в элементе 13 на время Т13 переходных процессов в счетчика поступает на входы элементов И группы 9. Тем самым производится опрос разрядов счетчика 8, и сигналы, соответствующие состоянию разрядов счетчика, поступают на входы групп блока 11 из N групп по N элементов И в группе. При этом сигнал с выхода элемента И группы 9, соответствующий первому разряду счетчика 8, поступает на первые входы элементов И первой группы, сигнал с выхода второго элемента И группы 9 на первые входы элементов И второй группы блока 11 из N групп по N элементов И в группе и т.д. Таким образом, если соответствующий разряд счетчика 8 находится в состоянии "1", то код соответствующего регистра блока 10 регистров памяти поступает на выход блока 11 из N групп по N элементов И в группе. В элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 12, на которые поступают коды из блока 11, производится логическое сложение сигналов, поступающих на их входы. В результате на выходах этих элементов формируется первое псевдослучайное число, которое поступает на информационный вход регистра 30 упорядочиваемой последовательности.

Тактовый импульс с выхода элемента 13 задержки поступает также на группу элементов 16-20 задержки и затем на формирователи 21-25. Формирователь 21 формирует импульс приема псевдослучайного числа и его номера в регистры 30 и 27, который поступает на входы разрешения записи регистров 30 и 27. Формирователь 22 формирует импульс выдачи числа (ВЧ), который поступает на входы разрешения считывания регистров 30 и 27. Формирователь 23 формирует импульс ВЧ регистров 34, 28 и 37 (ВЧ Рг 34, 28, 37), который поступает на входы разрешения считывания регистров 34, 28 и 37. Формирователь 24 формирует строб-импульс, поступающий на схемы 35 сравнения. Формирователь 25 формирует импульс приема числа (ПЧ) в регистры 34, 28, 31 и 37 (ПЧ Рг 34, 28, 31, 37), поступающий на один из входов схемы И 33, а также на входы разрешения записи регистров 34, 28, 31 и 37.

Таким образом, после поступления первого импульса с выхода генератора 6 тактовых импульсов (вернее после истечения промежутка времени Т13 с момента выработки первого тактового импульса) состояние узлов устройства следующее: на выходе элементов ИСКЛЮЧАЮЩЕЕ ИЛИ генератора 26 и на входе регистра 30 присутствует первое псевдослучайное число, на выходе счетчика 8 генератора 26 и на входе регистра 27 присутствует номер первого псевдослучайного числа единица.

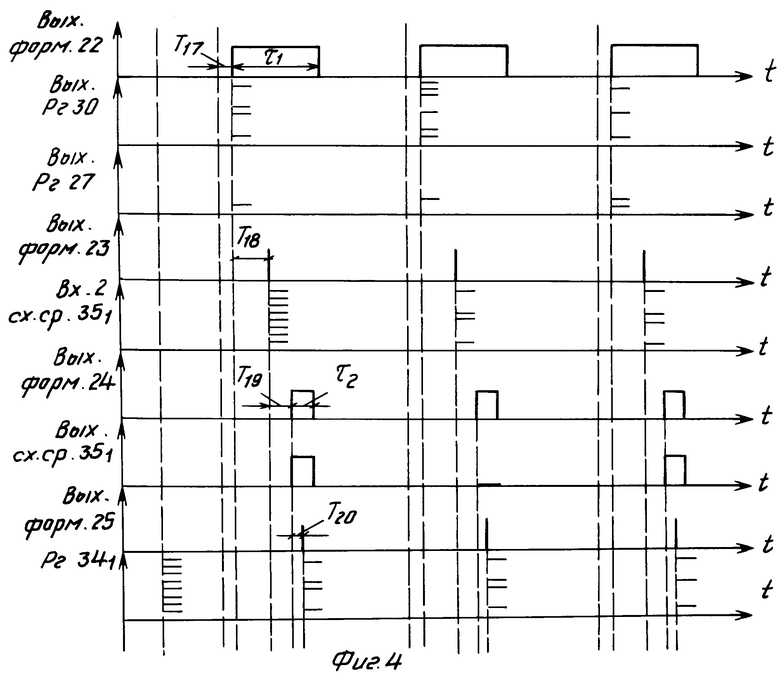

После истечения промежутка времени Т16 формирователь 21 формирует импульс приема псевдослучайного числа и его номера в регистры 30 и 27. После задержки на время Т17 переходных процессов в регистрах 30 и 27 формирователь 22 формирует импульс ВЧ длительностью τ1, поступающий на входы разрешения считывания регистров 30 и 27, с которых осуществляется съем кодов первого псевдослучайного числа и его номера. Код первого псевдослучайного числа поступает на первые входы схем 35 сравнения и коммутаторов 36 каждого блока 32 упорядочения и формирования рангов, а также на первый вход регистра 34 первого блока 32 упорядочения и формирования рангов. Код номера первого псевдослучайного числа поступает на первые входы коммутаторов 29 каждого блока 32 упорядочения и формирования рангов, а также на первый вход регистра 28 первого блока 32 упорядочения и формирования рангов.

После истечения промежутка времени Т18 формирователь 23 формирует импульс ВЧ регистров 34, 28, 37. Этот импульс поступает на входы считывания регистров 34, 28 каждого блока 32 упорядочения и формирования рангов, а также регистра 37 устройства, разрешая выдачу кодов чисел, хранящихся в этих регистрах. При этом на вторые входы схем 35 сравнения и коммутаторов 36 и 29 каждого блока 32 упорядочения и формирования рангов поступают коды чисел, хранящихся в регистрах 34 и 28 соответственно, т.е. коды единиц, а на первые входы n сумматоров 38 устройства коды чисел, хранящихся в регистрах 28 каждого блока 32 упорядочения и формирования рангов и в регистре 37 устройства (т.е. также коды единиц).

После истечения промежутка времени Т19 формирователь 24 формирует строб-импульс длительностью τ2(фиг. 4), поступающий на входы разрешения выдачи информации схем 35 сравнения каждого блока 32 упорядочения и формирования рангов. На выходе всех схем 35 сравнения формируется импульс положительной полярности (логической "1"), который, воздействуя на управляющие входы коммутаторов 36 и 29 всех блоков 32, устанавливает их в положение, когда на выход коммутаторов 36 поступает информация с выхода регистров 34, а на выход коммутаторов 29 информация с выхода регистров 28 (для данного случая первого импульса с выхода генератора 6 тактовых импульсов коды единиц).

После истечения промежутка времени Т20 формирователь 25 формирует импульс ПЧ в регистры 34, 28, 31 и 37 (фиг. 4), поступающий на один из входов элементов И 33 каждого блока 32, на втором входе которых (в данном случае) в течение длительности строб-импульса τ2 присутствует логическая "1". Импульс с выхода элементов И 11 разрешает запись информации в регистры 34 и 28 каждого блока 32. При этом в регистр 34 первого блока 32 переписывается из регистра 30 устройства первое псевдослучайное число, в регистр 28 первого блока 32 (из регистра 27 устройства) его номер (единица), а в регистры 34 и 28 остальных блоков 32 и регистры 31 и 37 устройства переписывается информация с выхода коммутаторов 36 и 29 соответствующих блоков 32.

Благодаря временному рассовмещению импульсов с выхода генератора 6 тактовых импульсов, а также импульсов с формирователей 21-25 ложное срабатывание схем 35, а также прохождение ложного кода на выход коммутаторов 36 и 29 исключаются.

С поступлением второго импульса с выхода генератора 6 тактовых импульсов осуществляются формирование и съем кода второго псевдослучайного числа, которое записывается в регистр 30 устройства, а его номер (двойка) фиксируется счетчиком 8 и запоминается в регистре 27. Импульсом ВЧ осуществляется съем кодов второго псевдослучайного числа и его номера с регистров 30 и 27 устройства соответственно, которые поступают на схемы 35 сравнения и коммутаторы 36 и 29 каждого блока 32 и на входы регистров 34 и 28 первого блока 32. Импульсом ВЧ регистров 34, 28, 37 производится выдача кодов чисел, хранящихся в этих регистрах (см. фиг. 4-9), которые поступают на схемы 35 сравнения, коммутаторы 36 и 29 каждого блока 32, а также сумматоры 38. С поступлением с формирователя 24 на входы разрешения выдачи информации схем 35 сравнения каждого блока 32 строб-импульса происходит сравнение второго числа с содержимым регистра 34 каждого блока 32. Так как второе число в нашем примере больше первого, то на выходе схемы 35 сравнения первого блока 32 формируется сигнал логического "0". На выходе схемы 35 сравнения остальных блоков 32 формируется сигнал логической "1". Сигнал логического "0" с выхода схемы 35 сравнения первого блока 32, воздействуя на управляющие входы коммутаторов 36 и 29 первого блока 32, устанавливает их в положение, когда на выход коммутатора 36 поступает информация с выхода регистра 30, т.е. второе псевдослучайное число, а на выход коммутатора 29 его номер, т.е. число два. Сигнал логической "1" с выхода схемы 35 сравнения остальных блоков 32, воздействуя на управляющие входы коммутаторов 36 и 29, устанавливает их в положение, когда на выход коммутаторов 36 поступает информация с выходов соответствующих регистров 34, а на выход коммутаторов 29 информация с выхода соответствующих регистров 28 (для данного случая второго импульса с выхода генератора 6 тактовых импульсов коды единиц, начиная с коммутаторов 36 и 29 второго блока 32. После поступления с формирователя 25 импульса ПЧ регистров 34, 28, 31 и 37 в регистр 34 второго блока 32 из регистра 30 устройства переписывается второе псевдослучайное число, а в регистр 28 второго блока 32 (из регистра 27 устройства) его номер (два), в регистры 34 и 28 третьего и последующих блоков 32 и регистры 31 и 37 устройства переписывается информация с выхода коммутаторов 36 и 29 соответствующих блоков 32. В регистрах 34 и 28 первого блока 32 остаются первое псевдослучайное число и его номер соответственно.

С поступлением третьего импульса с выхода генератора 6 тактовых импульсов в соответствии с изложенной логикой работы в регистрах 34 и 28 первого блока 32 записаны третье псевдослучайное число и его номер (если оно меньше первого), в регистрах 34 и 28 второго блока 32 первое псевдослучайное число и его номер, в регистрах 34 и 28 третьего блока 32 второе (максимальное из трех) псевдослучайное число, состояние регистров 34 и 28 остальных блоков 32, а также регистров 31 и 37 остается без изменений (см. фиг. 4-8).

С поступлением n импульсов псевдослучайные числа упорядочены в порядке возрастания, а их ранги хранятся в сумматорах 38.

В течение всего процесса работы устройства код с выхода счетчика 8 сравнивается в схеме 14 сравнения с кодом, записанным в регистре 15 памяти. При равенстве кодов на выходе схемы 14 сравнения формируется импульс, который после задержки в элементе 7 на время переходных процессов в счетчике 8 через элемент ИЛИ 4 поступает на вход установки в ноль триггера 5, что приводит к прекращению работы устройства. Одновременно импульс с выхода схемы 14 сравнения после задержки в элементе 39 на время Т39 > Т13 + Т16 + Т17 + τ1 поступает на формирователь 40. Импульс с выхода формирователя 40 поступает на вход разрешения считывания всех сумматоров 38. С поступлением этого импульса в сумматорах 38 производятся сложение хранящихся в их регистрах чисел k 1 либо l k, где k и l левая и правая границы соответственно заданного диапазона формирования целочисленных псевдослучайных величин и рангов упорядоченной последовательности псевдослучайных чисел, и выдача результата искомой последовательности целочисленных псевдослучайных величин, лежащих в заданном диапазоне.

На фиг. 11 и 12 параметры, характеризующие выборку, имеют следующие значения: n 300, k 1, l 300. Число интервалов разбиения диапазона изменения случайных величин при построении гистограммы p30. Для выборки целочисленных псевдослучайных величин, выработанных моделью прототипа, получены следующие числовые характеристики: диапазон изменения 0-299, 82 числа в этом диапазоне были повторены от двух до четырех раз; оценка среднего значения  146,04; оценка стандартного отклонения

146,04; оценка стандартного отклонения  = 83,4. Для выборки целочисленных псевдослучайных величин, выработанных моделью заявляемого устройства, числовые характеристики имели следующие значения: диапазон изменения 1-300, повторяемость отсутствует; оценка среднего значения

= 83,4. Для выборки целочисленных псевдослучайных величин, выработанных моделью заявляемого устройства, числовые характеристики имели следующие значения: диапазон изменения 1-300, повторяемость отсутствует; оценка среднего значения  150,5; оценка стандартного отклонения

150,5; оценка стандартного отклонения  = 86,6.

= 86,6.

Теоретические значения математического ожидания mo и стандартного отклонения σо равны соответственно mo 150, σо= 86,1.

На фиг. 13 и 14 приведены графики оценки выборочных автокорреляционных функций r1(i), rм(i) последовательности, выработанных моделью прототипа (фиг. 13) и заявляемого устройства (фиг. 14) соответственно.

Сопоставительный анализ приведенных графических данных и числовых характеристик показывает высокую эффективность заявляемого устройства. Эмпирическая плотность распределения выборки, полученной при помощи заявляемого устройства, а также числовые характеристики практически не отличаются от теоретической равномерной плотности и теоретических числовых характеристик в отличие от эмпирической плотности и числовых характеристик выборки, полученной при помощи модели прототипа. Кроме того, в выборку, полученную согласно заявляемому устройству, дополнительная корреляция не вносится.

Таким образом, использование предлагаемого устройства формирования равномерно распределенных целочисленных псевдослучайных величин, лежащих в заданном диапазоне, обеспечивает по сравнению с существующим устройством следующие преимущества. Предлагаемое устройство обеспечивает получение распределенных равномерно целочисленных псевдослучайных величин, лежащих в заданном диапазоне. Нелинейное преобразование, которому подвергается первоначальная выборка распределенных равномерно на интервале (0, 1) величин, а именно упорядочение и одновременное формирование ее рангов как искомой последовательности, позволяет исключить повторяемость величин в заданном диапазоне. Вследствие равновероятного распределения совокупности рангов получают целочисленную выборку, распределенную по равномерному закону, даже если у исходной выборки закон отличается от равномерного.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор псевдослучайных чисел | 1984 |

|

SU1239844A1 |

| Генератор случайных чисел | 1979 |

|

SU860070A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройство для моделирования радиотелеграфного канала связи | 1981 |

|

SU1034053A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Генератор псевдослучайных чисел | 1986 |

|

SU1324091A1 |

| Устройство для упорядочивания чисел | 1981 |

|

SU1012239A1 |

| Генератор псевдослучайных испытательных последовательностей | 1986 |

|

SU1354401A2 |

| Устройство для формирования псевдослучайной временной последовательности импульсов | 1979 |

|

SU917316A1 |

| Коррелометр | 1983 |

|

SU1091173A1 |

Изобретение относится к вычислительной технике и может быть использовано для статистического моделирования. Цель изобретения расширение класса решаемых задач за счет формирования псевдослучайных величин, лежащих в заданном диапазоне. Устройство содержит узел сортировки, регистры, накапливающие сумматоры, синхронизатор и генератор равномерно распределенных случайных величин. 14 ил.

УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ РАСПРЕДЕЛЕНИЯ РАВНОМЕРНО ЦЕЛОЧИСЛЕННЫХ ПСЕВДОСЛУЧАЙНЫХ ВЕЛИЧИН, содержащее синхронизатор, узлы сортировки чисел, каждый из которых состоит из первого регистра, элемента И, блока сравнения и первого коммутатора, и два регистра, причем в каждом узле сортировки выход элемента И соединен с входом разрешения считывания первого регистра этого узла сортировки, выход которого подключен к первому входу блока сравнения и к первому информационному входу первого коммутатора, выход первого регистра соединен с информационным входом первого регистра первого узла сортировки, вторыми входами блоков сравнения и вторыми информационными входами первых коммутаторов всех узлов сортировки, выход первого коммутатора каждого узла сортировки, кроме последнего, соединен с информационным входом первого регистра последующего узла сортировки, выход первого коммутатора последнего узла сортировки подключен к информационному входу второго регистра, первый выход синхронизатора соединен с первыми входами элементов И всех узлов сортировки и входом разрешения записи второго регистра, второй и третий выходы синхронизатора подключены соответственно к синхровходу первого регистра и синхровходам блоков сравнения, отличающееся тем, что, с целью расширения класса решаемых задач за счет формирования псевдослучайных величин, лежащих в заданном диапазоне, в него введены генератор равномерно распределенных случайных последовательностей, два регистра, накапливающие сумматоры и в каждый узел сортировки второй регистр и второй коммутатор, причем первый выход генератора равномерно распределенных случайных последовательностей подключен к информационному входу первого регистра, входы разрешения записи и считывания которого подключены к одновременным входам третьего регистра и четвертому и пятому выходам синхронизатора, второй выход которого соединен с синхровходом третьего регистра и синхровходами регистров всех узлов сортировки, второй выход генератора равномерно распределенных случайных последовательностей соединен с информационным входом третьего регистра, выход которого подключен к первым информационным входам вторых коммутаторов и информационному входу второго регистра первого узла сортировки, шестой выход синхронизатора подключен к входам разрешения записи регистров всех узлов сортировки, в каждом узле сортировки выход элемента И соединен со входом разрешения считывания второго регистра своего узла, выход которого подключен к второму информационному входу второго коммутатора, выход блока сравнения соединен с вторым входом элемента И и управляющими входами коммутаторов, выход второго коммутатора каждого узла сортировки, кроме последнего, соединен с информационным входом второго регистра последующего узла сортировки, выход второго коммутатора последнего узла сортировки подключен к информационному входу четвертого регистра, вход разрешения записи и синхровход которого соединены соответственно с первым и седьмым выходами синхронизатора, восьмой выход которого подключен к синхровходам накапливающих сумматоров, информационный вход каждого из которых, кроме последнего, соединен с выходом второго регистра одноименного узла сортировки, выход четвертого регистра подключен к информационному входу последнего сумматора, входы установки которых соединены с входами задания диапазона устройства, а выходы являются выходами устройства.

| Авторское свидетельство СССР N 1185326, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-08-20—Публикация

1990-09-14—Подача