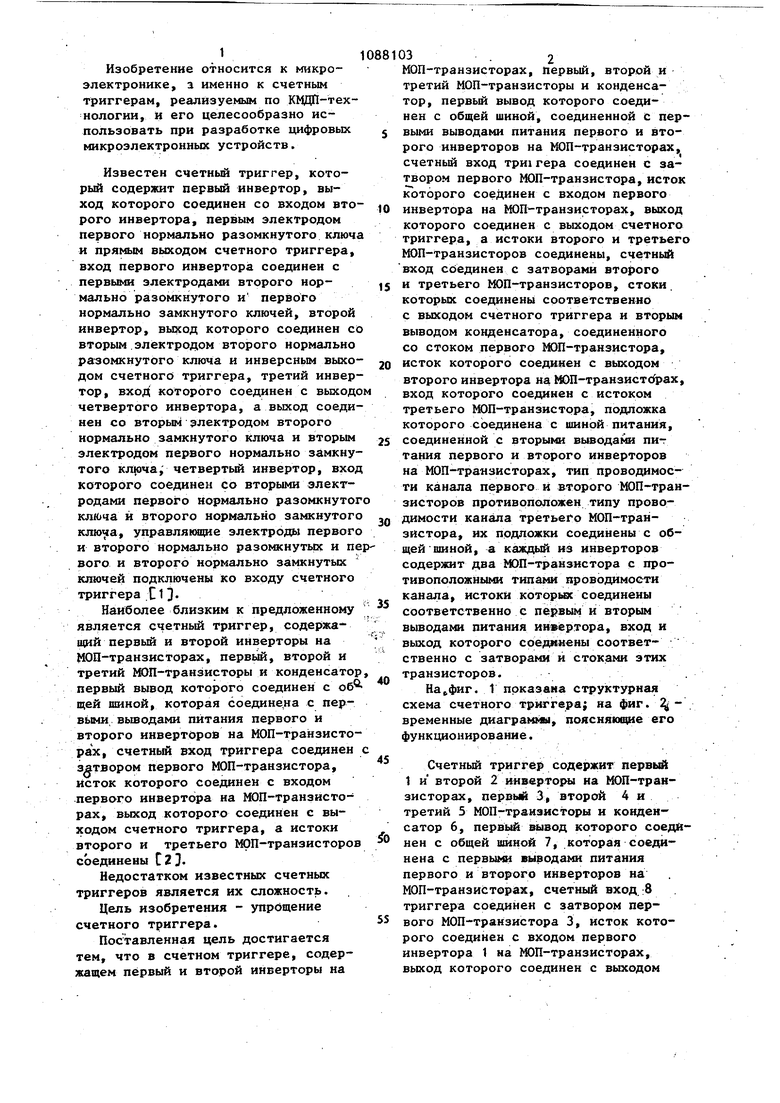

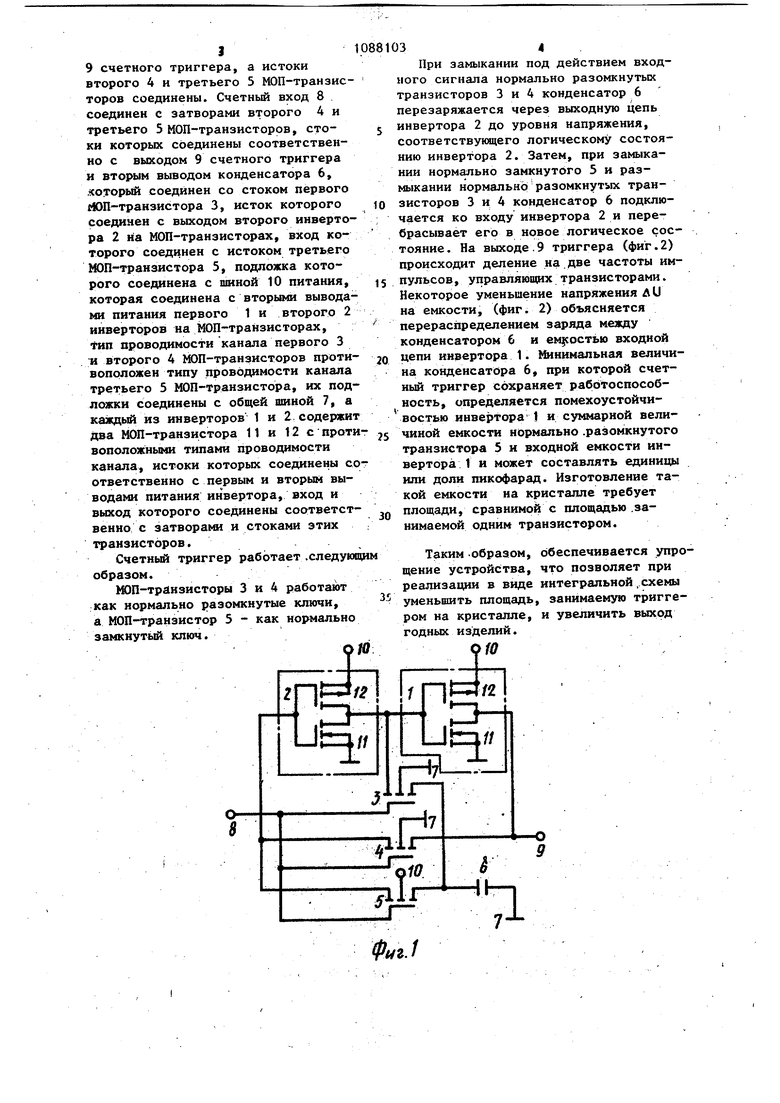

Изобретение относится к микроэлектронике, а именно к счетным триггерам, реализуемым по КМДП-технологии, и его целесообразно использовать при разработке цифровых микроэлектронных устройств. Известен счетный триггер, который содержит первый инвертор, выход которого соединен со входом вто рого инвертора, первым электродом первого нормально разомкнутого ключ и прямым выходом счетного триггера, вход первого инвертора соединен с первыми электродами второго нормально разомкнутого и первого нормально замкнутого ключей, второй инвертор, выход которого соединен со вторым электродом второго нормально разомкнутого ключа и инверсным выходом счетного триггера, третий инвертор, вхо которого соединен с выходо четвертого инвертора, а выход соединен со вторым электродом второго нормально замкнутого ключа и вторым электродом первого нормально замкнутого ключа; четвертьй инвертор, вход которого соединен со вторыми электродами первого нормально разомкнутог и второго нормально замкнутого , управлякщие электроды первого и второго нормально разомкнутьк и пе вого и второго нормально замкнутых ключей подключены ко входу счетного триггера .СОНаиболее близким к предложенному является счетный триггер, содер жащий первый и второй инверторы на поп-транзисторах, первый, второй и третий МОП-транзисторы и конденсатор первый вывод которого соединен с об щей шиной, которая соедине,на с первь1мивьтодами питания первого и второго инверторов на МОП-транзисторах, счетный вход триггера соединен затвором первого ЮП-транзистора, исток которого соединен с входом .первого инвертора на МОП-транзисторах, выход которого соединен с выходом счетного триггера, а истоки второго и третьего ШП-транзисторов соединены С 2}. Недостатком известных счетных триггеров является их сложность. Цель изобретения - упрощение счетного триггера. Поставленная цель достигается тем, что в счетном триггере, содержащем первый и второй инверторы на 3 . 2 МОП-транзисторах, первый, второй и третий МОП-транзисторы и конденсатор, первый вывод которого соединен с общей шиной, соединенной с первыми выводами питания первого и второго инверторов на МОП-транзисторах, счетный вход три1 гера соединен с затвором первого МОП-транзистора, исток которого соединен с входом первого инвертора на МОП-транзисторах, выход которого соединен с выходом счетного триггера, а истоки второго и третьего МОП-Транзисторов соединены, счетный вход сЬединен с затворами второго и третьего ИЮП-транзисторов, стоки, которых соединены соответственно с выходом счетного триггера и вторым выводом конденсатора, соединенного со стоком первого ШП-транзистора, исток которого соединен с выходом второго инвертора на ШП-транзист6рах, вход которого соединен с истоком третьего МОП-транзистора, подложка которого соединена с шиной питания, соединенной с вторыми выводами пит тания первого и второго инверторов на МОП-траязисторах, тип проводимости канала первого и второго МОП-транэисторов противоположен типу проводимости канала третьего МОП-транзистора, их подложки соединены с общей шиной, а каждый из инверторов содержит два МОП-транзистора с противоположными типами проводимости канала, истоки которюс соединены соответственно с первым и вторым выводами питания инвертора, вход и выход которого соеда1«ены соответственно с затворами и стоками этих транзисторов. . 1 показана структурная схема счетного триггера; на фиг.временные диаграммы, поясняю1цие его функционирование. Счетный триггер содержит первый 1 и второй 2 инверторы на ШП-транзисторах, первый 3, второй 4 и третий 5 МОП-транзисторы и конденсатор 6, первый вывод которого соединен с общей шиной 7, которая соединена с первыми выводами питания первого и второго инверторов на МОП-транзисторах, счетный вход. :8 триггера соединен с затвором первого МОП-транзистора 3, исток которого соединен с входом первого инвертора 1 на ЮП-транзисторах, выход которого соединен с выходом 9 счетного триггера, а истоки второго 4 и третьего 5 МОП-транзисторов соединены. Счетный вход 8 соединен с затворами второго 4 и третьего 5 МОП-транзисторов, стоки которых соединены соответственно с выходом 9 счетного триггера и вторым выводом конденсатора 6, .который соединен со стоком первого йЮП-транзистора 3, исток которого соединен с выходом второго инвертора 2 на МОП-транзисторах, вход которого соединен с истоком третьего МОП-транзистора 5, подложка которого соединена с шиной 10 питания, которая соединена с вторыми выводами питания первого 1 и второго 2 инверторов на iMOn-транзисторах, тип проводимости канала первого 3 и второго 4 ШП-транзисторов противоположен типу проводимости канала третьего 5 МОП-транзистора, их подложки соединены с общей шиной 7, а каждый из инверторов 1 и 2 содержит два МОП-транзистора 11 и 12 с проти воположными типами проводимости канала, истоки которых соединены со ответственно с первым и вторым выводами питания; инвертора, вход и выход которого соединены соответственно с затвораьо и стоками этих тфанзисторов.. Счетный триггер работает .следующ образом. Ж)П-тр 1нзисторы 3 и 4 работают как нормально разомкнутые ключи, а МОП-транзистор 5 - как нормально замкнутый ключ. При замыкании под действием входного сигнала нормально разомкнутых транзисторов 3 и 4 конденсатор 6 перезаряжается через выходную цепь инвертора 2 до уровня напряжения, соответствуняцего логическому состоянию инвертора 2. Затем, при замыкании нормально замкнутого 5 и размыкании нормально разомкнутых транзисторов 3 и 4 конденсатор 6 подключается ко входу инвертора 2 и перебрасывает его в новое логическое состояние . На выходе.9 триггера (фиг.2) происходит деление на две частоты импульсов, управля1бщих транзисторами. Некоторое уменьшение напряжения AU на емкости, (фиг.2) объясняется перераспределением заряда между конденсатором 6 и ем|состью входной цепи инвертора 1. Минимальная величина конденсатора 6, при которой счетный триггер сохраняет раб отоспособность, определяется помехоустойчивостью инвертора ) и суммарной величиной емкости нормально .разомкнутого транзистора S и входной емкости инвертора 1 и может составлять единицы или доли пикофарад. Изготовление такой емкости на кристалле требует площади, сравнимой с площадью .занимаемой одним транзистором. Таким образом, обеспечивается упрощение устройства, что позволяет при реализации в виде интегральной,схемы уменьшить площадь, занимаем)ш триггером на кристалле, и увеличить выход годных изделий.

-.1.

4Д(/

| название | год | авторы | номер документа |

|---|---|---|---|

| Ключ | 1983 |

|

SU1119170A2 |

| Синхронный выходной каскад | 1983 |

|

SU1119173A1 |

| Кварцевый генератор | 1983 |

|

SU1109855A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КОМПАРАТОР С ВЫБОРКОЙ ВХОДНОГО СИГНАЛА | 2008 |

|

RU2352061C1 |

| ВЫСОКОВОЛЬТНЫЙ ПРЕОБРАЗОВАТЕЛЬ ПОСТОЯННОГО НАПРЯЖЕНИЯ В ПОСТОЯННОЕ НАПРЯЖЕНИЕ | 2013 |

|

RU2642839C2 |

| Мультивибратор | 1979 |

|

SU866710A1 |

| Электронное реле | 1990 |

|

SU1765886A1 |

| СТАТИЧЕСКАЯ ЗАПОМИНАЮЩАЯ ЯЧЕЙКА С ДВУМЯ АДРЕСНЫМИ ВХОДАМИ | 2011 |

|

RU2470390C1 |

| Многоканальный коммутатор | 1989 |

|

SU1723667A1 |

| Логический элемент сравнения комплементарной металл-оксид-полупроводниковой структуры ассоциативного селектора запоминающего устройства | 2016 |

|

RU2621011C1 |

СЧЕТНЫЙ ТРИГГЕР, содержащий первый и второй инверторы.на МОП-транзисторах, первый, второй и третий МОП-тра.нзисторы и конденсатор, первый вывод которого соединен с общей шиной, соединенной с первыми выводами питания первого и второго инверторов на МОП-транзисторах, счетный вход триггера соединен с затвором первого МОП-транзистора, исток которого соединен с входом первого инвертора на МОПтранзисторах, выход которого соединен с выходом счетного триггера, а истоки второго и третьего (ЮП-транзисторов соединены, отличающийся тем, что, с целью его упрощения, счетный вход соединен с затворами второго и третьего { -транзисторов, стоки которых соединены соответственно с выходом счетного триггера и вторым выводом конденсатора, соединенного со стоком первого МОПтранзистора, исток которого соединен с выходом второго инвертора на МОПтранзисторах, вход которого соединен с истоком третьего ШП-транзистора, по;1щожка которого соединена с шиной питания, соединенной с вторыми выводами питания первого и 9 второго инверторов на МОП-транзисторах, тип проводимости канала первого и второго МОП-транзисторов противоположен типу проводимости канала третьего МОП-транзистора, их подложки соединены с общей шиной, а каждый из инверторов содержит два ЮП-транзистора с противоположными ор: типами проводимости канала, которых соединены соответственно с 00 первьм и вторым выводами питания инвертора, вход и выход которого соединены соответственно с эатво00 pafoi и стоками этих транзисторов.

Фиг. 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Кобболд Р | |||

| Теория и применение полевых транзисторов | |||

| Л | |||

| Энергия, 1975 с | |||

| Телефонно-трансляционное устройство | 1921 |

|

SU252A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США К 3691402, кл | |||

| Приспособление для выпечки формового хлеба в механических печах с выдвижным подом без смазки форм жировым веществом | 1921 |

|

SU307A1 |

Авторы

Даты

1984-04-23—Публикация

1983-02-04—Подача