Изобретение относится к области вычислительной техники и может быть использовано в блоках ассоциативных селекторов запоминающих устройств (ЗУ).

Основой ассоциативных селекторов запоминающего устройства являются логические элементы сравнения (ячейки селекции) данных, одни данные в которые записываются и хранятся в триггерах таких ячеек селекции, и с этими данными осуществляется сравнение потока других данных, поступающих на входы сравнения таких логических элементов сравнения (ячеек селекции), содержащих кроме триггера и комбинационные логические элементы. Воздействие отдельных ядерных частиц на триггеры логических элементов сравнения приводит к возникновению импульсов помех и сбою логического состояния триггеров (single event upsets - SEU) таких элементов. Снижение проектно-технологических норм КМОП СБИС до уровня менее 100 нм сопровождается ростом частоты одиночных сбоев (soft error rate - SER) таких комбинированных логических элементов, совмещающих элементы последовательностной и комбинационной логик, под действием одиночных ядерных частиц. Необходимо исключить возможность внесения погрешностей в выходные логические уровни логических элементов сравнения ассоциативного селектора запоминающего устройства при воздействии ядерных частиц на триггер в его составе.

Вариантами КМОП логического элемента сравнения в составе ассоциативного селектора запоминающего устройства в настоящее время являются КМОП логический элемент сравнения на основе четырехтранзисторного D-триггера и комбинационных элементов "ИСКЛЮЧИТЕЛЬНОЕ ИЛИ" с управлением динамического типа (патент US №5703803 А, кл. G11C 15/04, опубл. Dec. 30. 1997, фиг. 2) и статический логический элемент сравнения (патент US №6977831 В2, кл. G11C 15/04, опубл. Dec. 20.2005, фиг. 3).

Наиболее близким по технической сущности и достигаемому результату является логический элемент сравнения комплементарной металл-оксид-полупроводниковой структуры ассоциативного селектора ЗУ, включающий два инвертора с третьим состоянием и порт записи данных, размещенных на кристалле интегральной микросхемы, первый и второй входы инверторов с третьим состоянием соединены соответственно с первой и второй входными шинами, а выходы инверторов с третьим состоянием соединены с выходной шиной элемента, входы порта записи данных соединены с битовыми линиями, вход выборки порта записи данных соединен с линией выборки (патент US №5699288 А, кл. G11C 15/04, опубл. Dec. 16. 1997, фиг. 4).

Недостатком описанного решения является недостаточная помехоустойчивость элемента (надежность выполнения логической функции) при воздействии одиночной ядерной частицы на внутренние узлы логического элемента сравнения.

Техническим результатом, ожидаемым от использования изобретения, является повышение надежности выполнения логической функции за счет повышения помехоустойчивости логического элемента сравнения при воздействии одиночных ядерных частиц.

Указанный технический результат достигается тем, что логический элемент сравнения комплементарной металл-оксид-полупроводниковой структуры ассоциативного селектора ЗУ, включающий два инвертора с третьим состоянием и порт записи данных, размещенных на кристалле интегральной микросхемы, первый и второй входы инверторов с третьим состоянием соединены соответственно с первой и второй входными шинами, а выходы инверторов с третьим состоянием соединены с выходной шиной элемента, входы порта записи данных соединены с битовыми линиями, вход выборки порта записи данных соединен с линией выборки, согласно изобретению логический элемент снабжен триггером, состоящим из двух групп транзисторов, каждая из которых включает две пары РМОП и NМОП транзисторов, затвор РМОП транзистора в каждой паре соединен с стоком NМОП транзистора этой пары, затвор которого соединен с стоком РМОП транзистора этой пары, затворы РМОП и NМОП транзисторов группы соединены соответственно с первым и вторым выводами группы транзисторов триггера, а затворы NМОП транзисторов первой и второй пар группы соединены соответственно со вторым и третьим выводами группы транзисторов триггера, истоки РМОП и истоки NМОП транзисторов соединены соответственно с шиной питания и общей шиной элемента, при этом второй и третий входы первого инвертора с третьим состоянием соответственно соединены с первым и вторым выводами первой группы транзисторов триггера, второй и третий входы второго инвертора с третьим состоянием соответственно соединены со вторым и первым выводами второй группы транзисторов триггера, третий вывод которой соединен с первым выводом первой группы транзисторов триггера, третий вывод которой соединен со вторым выводом второй группы транзисторов триггера, при этом выходы порта записи данных соединены с соответствующими выводами двух групп транзисторов триггера, причем две группы транзисторов триггера размещены на кристалле интегральной микросхемы одна от другой на расстоянии, исключающем одновременное воздействие одиночной ядерной частицы на обе группы транзисторов с уровнем больше порогового.

А также тем, что каждый инвертор с третьим состоянием включает пару РМОП и пару NМОП транзисторов, стоки первых РМОП и NMOU транзисторов соединены соответственно с истоками вторых РМОП и NМОП транзисторов, стоки которых объединены и соединены с выходом инвертора с третьим состоянием, затворы первых РМОП и NМОП транзисторов соединены с первым входом, а затворы вторых NМОП и РМОП транзисторов соединены соответственно со вторым и третьим входами инвертора с третьим состоянием, истоки первого РМОП и первого NПОП транзисторов соединены соответственно с шиной питания и общей шиной элемента.

А также тем, что каждый инвертор с третьим состоянием включает пару РМОП и пару NМОП транзисторов, стоки первых РМОП и NМОП транзисторов соединены соответственно со стоками вторых РМОП и NМОП транзисторов, истоки которых объединены и соединены с выходом инвертора с третьим состоянием, затворы первых РМОП и NМОП транзисторов соединены с первым входом, а затворы вторых NМОП и РМОП транзисторов соединены соответственно со вторым и третьим входами инвертора с третьим состоянием, истоки первого РМОП и первого NМОП транзисторов соединены соответственно с шиной питания и общей шиной элемента.

А также тем, что первая группа транзисторов триггера и первый инвертор с третьим состоянием составляют первый блок логического элемента, вторая группа транзисторов триггера и второй инвертор с третьим состоянием составляют второй блок логического элемента, которые размещены на кристалле интегральной микросхемы один за другим, при этом i-й и (i+K)-й блоки образуют i-й логический элемент сравнения, где i=1; 2; …; K.

А также тем, что указанное расстояние, исключающее одновременное воздействие одиночной ядерной частицы на обе группы транзисторов триггера с уровнем больше порогового, равно минимальному расстоянию между транзисторами двух групп триггера, выбранному в соответствии с требованиями исключения сбоев состояния триггера логического элемента при воздействии одиночных ядерных частиц с заданными максимальными линейными потерями энергии и максимальным наклоном трека частиц относительно нормали к поверхности кристалла.

Указанная совокупность признаков позволяет снизить вероятность сбоя состояния триггера элемента и повысить надежность за счет повышения помехоустойчивости логического элемента сравнения при воздействии одиночной ядерной частицы.

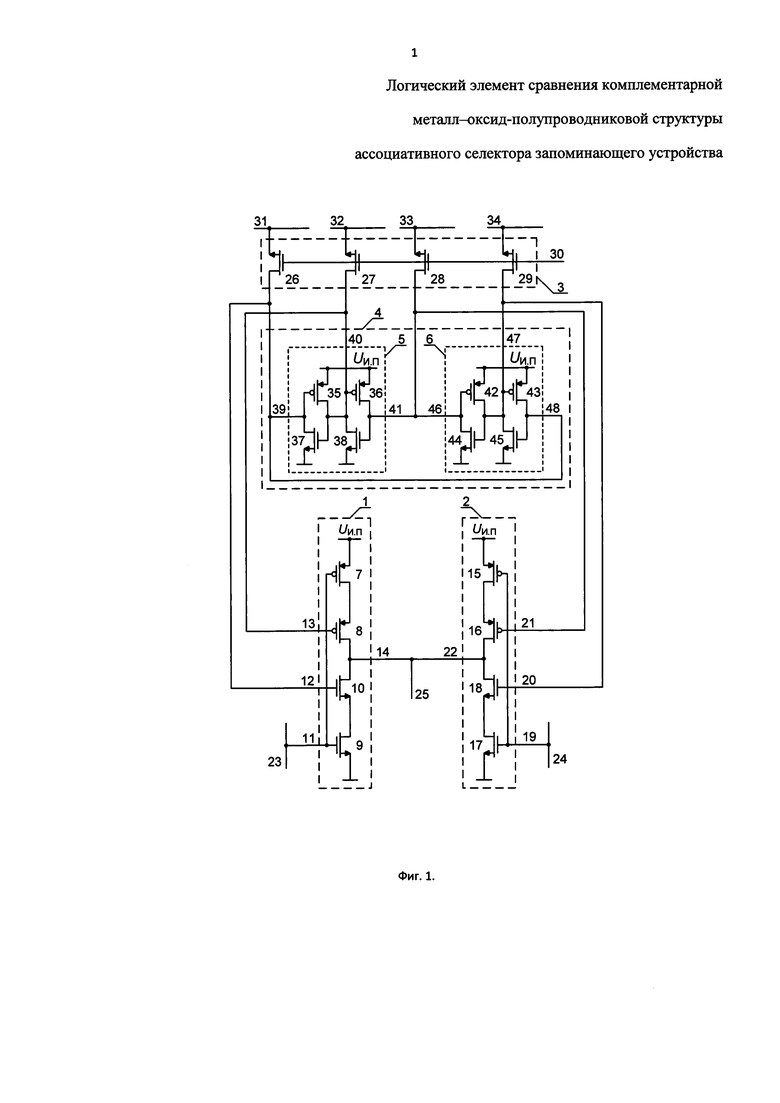

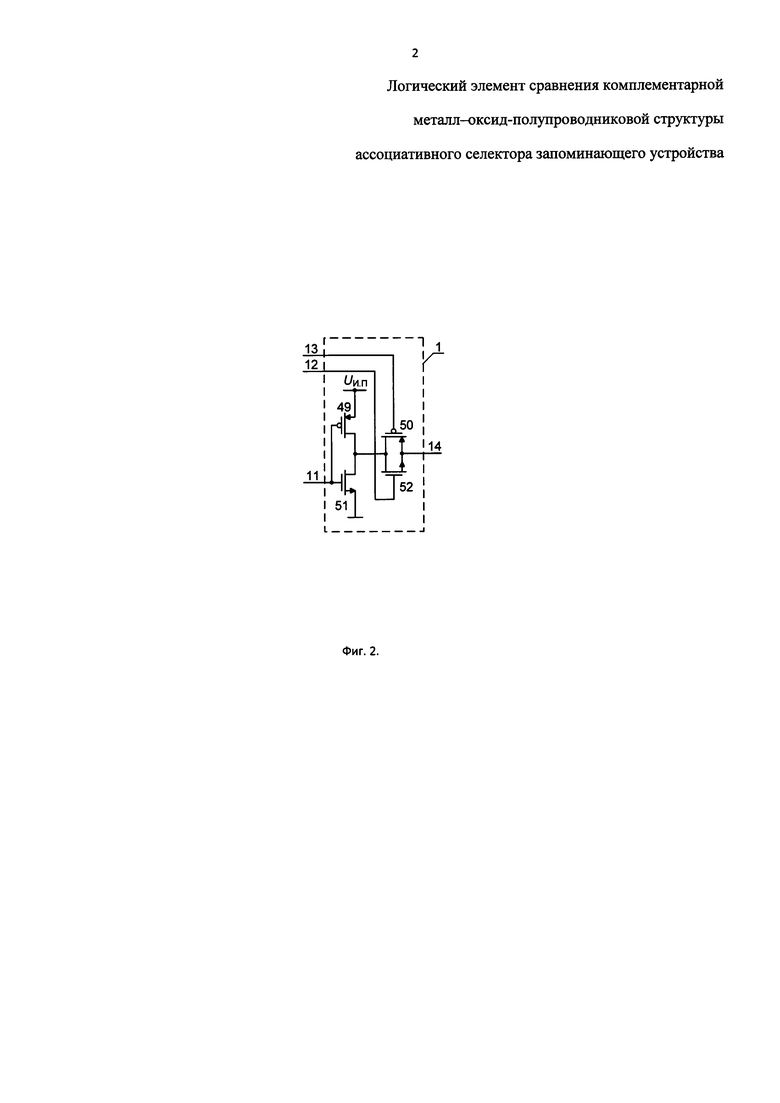

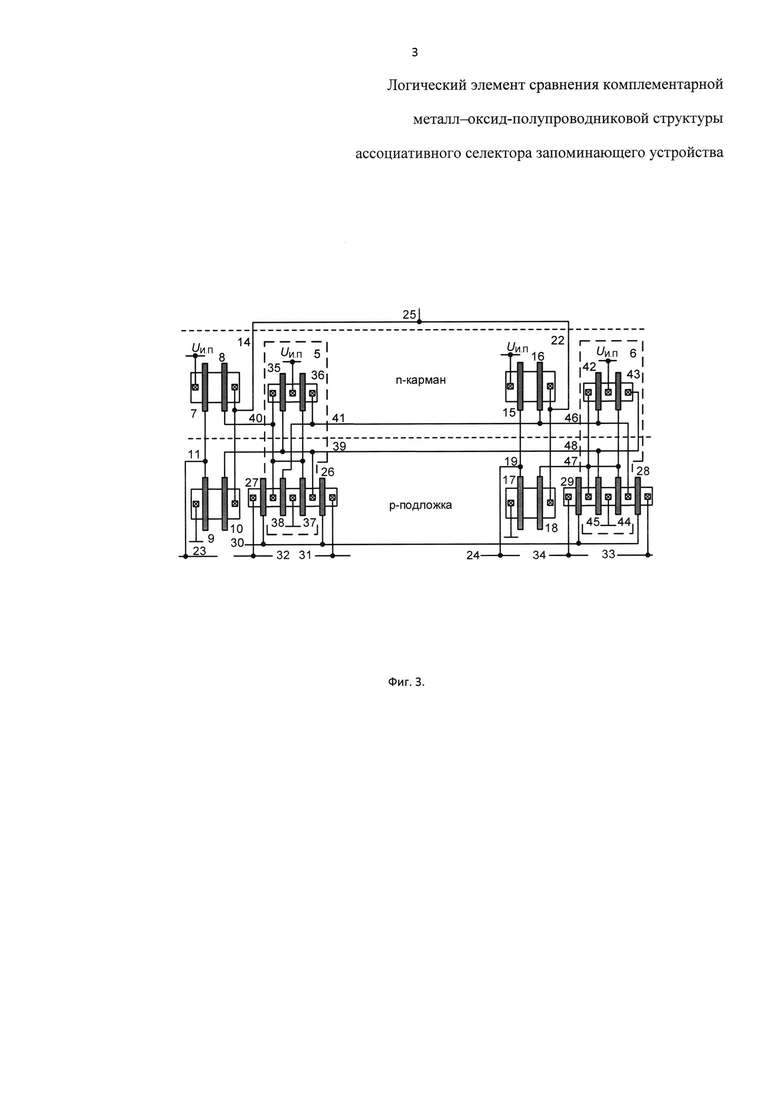

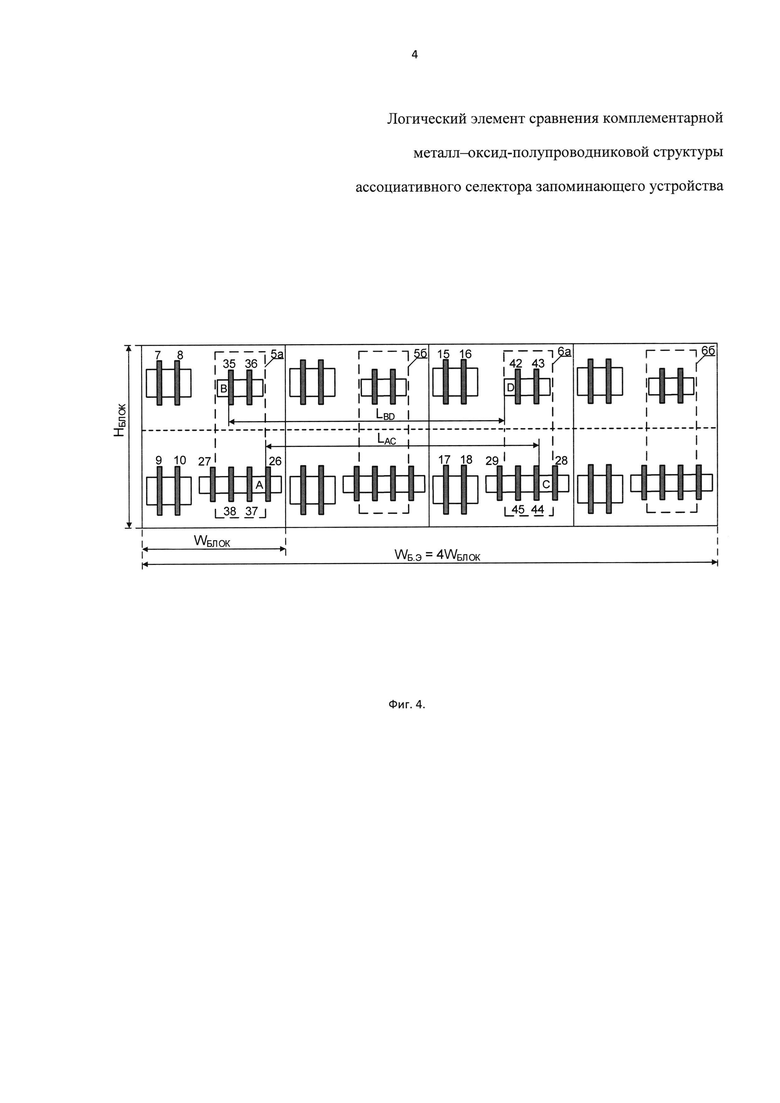

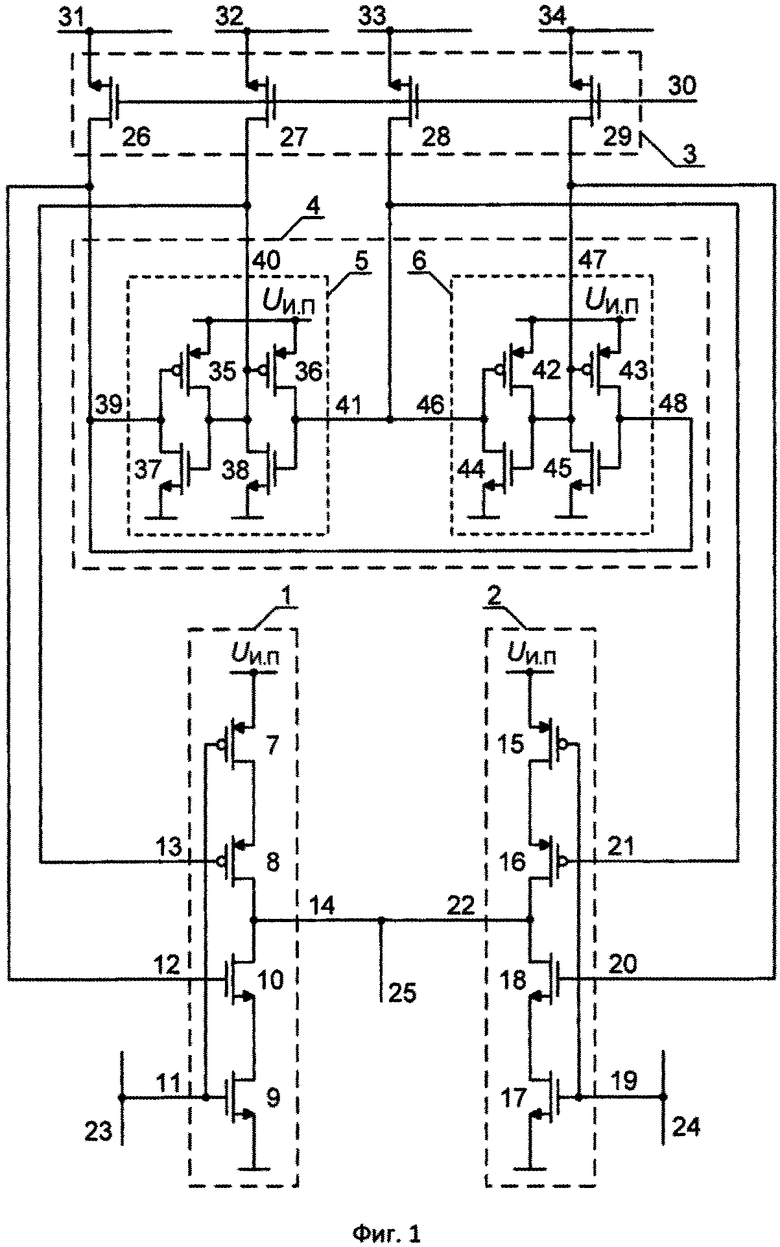

Изобретение поясняется чертежами, где на фиг. 1 изображена электрическая принципиальная схема логического элемента сравнения с первым вариантом инверторов с третьим состоянием, на фиг. 2 изображена электрическая принципиальная схема второго варианта инвертора с третьим состоянием, на фиг. 3 изображена схема взаимного расположения транзисторов одного логического элемента сравнения, на фиг. 4 изображена схема взаимного расположения транзисторов в базовом элементе ассоциативного селектора ЗУ, содержащем два логического элемента сравнения.

Использованы обозначения: РМОП транзистор - это транзистор со структурой металл-оксид-полупроводник и каналом дырочной проводимости, то есть Р-типа; NМОП транзистор - транзистор со структурой металл-оксид-полупроводник и каналом электронной проводимости, то есть N-типа.

Логический элемент сравнения содержит два инвертора 1, 2 с третьим состоянием, порт 3 записи данных, триггер 4, состоящий из первой и второй групп 5, 6 транзисторов. Первый инвертор 1 с третьим состоянием на РМОП транзисторах 7, 8 и NМОП транзисторах 9, 10 имеет три входа 11, 12, 13 и выход 14, второй инвертор 2 с третьим состоянием на РМОП транзисторах 15, 16 и NМОП транзисторах 17, 18 имеет три входа 19, 20, 21 и выход 22. Первые входы 11, 19 первого и второго инверторов 1, 2 с третьим состоянием соединены соответственно с первой и второй входными шинами 23, 24 элемента, а выходы 14, 22 первого и второго инверторов 1, 2 с третьим состоянием соединены с выходной шиной 25 элемента, порт 3 записи данных содержит четыре проходных ключа на NМОП транзисторах 26, 27, 28, 29, затворы которых соединены с линией 30 выборки, один из выводов каждого из проходных ключей на NМОП транзисторах 26, 27, 28, 29 соединен с одной из четырех битовых линий 31, 32, 33, 34, другие выводы проходных ключей на NМОП транзисторах 26, 27 соответственно соединены со вторым и третьим 12, 13 входами первого инвертора 1 с третьим состоянием, а выводы проходных ключей на NМОП транзисторах 29, 28 соединены со вторым и третьим 20, 21 входами второго инвертора 2 с третьим состоянием. Первая группа 5 на РМОП транзисторах 35, 36 и NМОП транзисторах 37, 38 триггера 4 имеет три вывода 39, 40, 41, вторая группа 6 на РМОП транзисторах 42, 43 и NМОП транзисторах 44, 45 триггера 4 имеет три вывода 46, 47,48. Второй и третий входы 12, 13 первого инвертора 1 с третьим состоянием соответственно соединены с первым и вторым выводами 39, 40 первой группы 5 транзисторов триггера 4, второй и третий входы 20, 21 второго инвертора 2 с третьим состоянием соответственно соединены со вторым и первым выводами 47, 46 второй группы 6 транзисторов, третий вывод 48 которой соединен с первым выводом 39 первой группы 5 транзисторов, третий вывод 41 которой соединен с первым выводом 46 второй группы 6 транзисторов триггера 4.

При этом в первом варианте инверторе 1 с третьим состоянием на РМОП транзисторах 7, 8 и NМОП транзисторах 9, 10 стоки первых РМОП и NМОП транзисторов 7, 9 соединены соответственно с истоками вторых РМОП и NМОП транзисторов 8, 10, стоки которых объединены и соединены с выходом 14 инвертора 1, затворы первых РМОП и NМОП транзисторов 7, 9 соединены с первым входом 11, а затворы вторых NМОП и РМОП транзисторов 8, 10 соединены соответственно со вторым и третьим входами 12, 13 инвертора 1, истоки первого РМОП и первого NМОП транзисторов 7, 9 соединены соответственно с шиной питания и общей шиной элемента.

Кроме того, во втором варианте инвертора 1 с третьим состоянием на РМОП транзисторах 49, 50 и NМОП транзисторах 51, 52 стоки первых РМОП и NМОП транзисторов 49, 51 соединены соответственно со стоками вторых РМОП и NМОП транзисторов 50, 52, истоки которых объединены и соединены с выходом 14 инвертора 1 с третьим состоянием, затворы первых РМОП и NМОП транзисторов 49, 51 соединены с первым входом 11, а затворы вторых NМОП и РМОП транзисторов 50, 52 соединены соответственно со вторым и третьим входами 12, 13 инвертора 1 с третьим состоянием, истоки первого РМОП и первого NМОП транзисторов 49, 51 соединены соответственно с шиной питания и общей шиной элемента.

Описанное устройство работает следующим образом.

Логический элемент сравнения может работать в одном из двух режимов: запись одной переменной в триггер 4 и сравнение с этой переменной (селекция) данных из последовательности, поступающей на нормальный и инверсный входы 11, 19 логического элемента с первой и второй входных шин 23, 24 элемента.

Запись данных в триггер 4 осуществляется в четыре узла триггера 4 через выводы 39, 40 и выводы 46, 47 групп 5 и 6 транзисторов триггера 4. Запись производится через проходные ключи 26, 27, 28, 29 порта 3 записи данных. При записи данных в триггер 4 элемента (первой из двух сравниваемых переменных) на битовые линии 31, 32, 33, 34 порта 3 записи данных подают записываемые данные в дифференциальной форме, а именно на выводы 39 и 46 групп 5 и 6 транзисторов в нормальном виде, а на выводы 40 и 47 в инверсном. Установкой активного уровня на линии 30 выборки открывают проходные ключи 26, 27, 28, 29, пропуская записываемые данные (первую из двух переменных) на выводы 39, 40, 46, 47 групп 5 и 6 транзисторов триггера 4. Затем на линии 30 выборки устанавливают неактивный уровень, что поддерживает все проходные ключи 26, 27, 28, 29 в закрытом состоянии. На выводах 39, 40, 46, 47 групп 5 и 6 транзисторов сохраняются уровни сигналов, соответствующие записанным данным. Логический уровень записанной переменной в триггер 4 соответствует логическим уровням, поданным через порт 3 записи данных на выводы 39 и 46 групп 5 и 6 транзисторов.

В режиме сравнения (селекции) данных, поступающих одновременно с входных шин 23, 24 в дифференциальной форме (с шины 23 в прямом виде, а с шины 24 в инверсном виде), на выводах 39, 40, 46, 47 групп 5 и 6 транзисторов сохраняются уровни, соответствующие записанным в триггер 4. На входные шины 23, 24 элемента подается последовательность сигналов (данных) в нормальном (входная шина 23) и инверсном (входная шина 24) виде, логические уровни которых сравнивается с логическими уровнями данных, записанных в две группы 5 и 6 транзисторов триггера 4, а именно сохраняемых на выводах 39, 40, 46, 47, и в итоге на выходную шину 25 элемента поступает последовательность логических уровней сигналов, являющихся результатом такого сравнения данных.

Сравнение производится в логической части элемента с использованием двух инверторов 1,2 с третьим состоянием, выходы 14, 22 которых объединены и соединены с выходной шиной 25 логического элемента сравнения. Выход инвертора с третьим состоянием находится в высокоомном состоянии, когда на его втором входе низкий логический уровень (т.е. 0), на третьем входе - высокий логический уровень (т.е. 1). В таком состоянии прохождение сигнала с первого входа на выход блокируется парой запертых РМОП и NМОП транзисторов, управляемых по второму и третьему входам. В таком состоянии выход инвертора не шунтирует выход другого инвертора с третьим состоянием. В таком высокоомном состоянии инвертор 1 находится, когда в триггере 4 записан 0, т.е. логические уровни на его выводах Х39Х40Х46Х47=0101, а инвертор 2, когда в триггере 4 записана 1, т.е. на его выводах Х39Х40Х46Х47=1010. Соответственно, при хранении 0 в триггере на выходную шину 25 с выхода 22 инвертора 2 поступает инвертированный логический уровень данных с входной шины 24 и на выходной шине 25 будет Y25=0 в том случае, когда Х24=1, а Х23=0, что соответствует требуемому алгоритму селекции. Соответственно, при хранении 1 в триггере на выходную шину 25 с выхода 14 инвертора 1 поступает инвертированный логический уровень данных с входной шины 23 и на выходной шине 25 будет Y25=0 в том случае, когда Х23=1, что также соответствует требуемому алгоритму селекции данных со входных шин 23, 24.

Такой же функцией инвертора с блокировкой передачи сигнала с первого входа на выход и высокоомным выходом в таком состоянии характеризуется второй вариант инвертора с третьим состоянием, электрическая схема которого приведена на фиг. 2. РМОП и NМОП транзисторы 49, 51 образуют инвертор, управляемый по первому входу, а РМОП и NМОП транзисторы 52, 50, управляемые по второму и третьему входам, образуют блокирующий проходной ключ с высокоомным выходом в запертом состоянии.

Длительность интервала времени сравнения (селекции) данных определяется длительностью заданной последовательности данных (сигналов), поступающих на входные шины 23, 24 элемента. Соответственно, в интервале времени сравнения (селекции) данных недопустима потеря данных, хранимых триггером 4, то есть сбой его логического состояния из-за воздействия одиночных ядерных частиц. Для существенного снижения вероятности сбоя логического состояния триггера, что позволяет повысить надежность логического элемента сравнения в процессе селекции данных при воздействии одиночных ядерных частиц, логический элемент снабжен триггером, состоящим из двух групп транзисторов (патент РФ №2554849 С2, кл. G11C 11/40, опубл. 27.06.2015).

Логический элемент сравнения на основе двух инверторов 1, 2 с третьим состоянием, порта 3 записи данных, триггера 4, состоящего из первой и второй групп 5, 6 транзисторов, причем первые входы 11, 19 первого и второго инверторов 1, 2 с третьим состоянием соединены соответственно с первой и второй входными шинами 23, 24 элемента, а выходы 14, 22 первого и второго инверторов 1, 2 с третьим состоянием соединены с выходной шиной 25 элемента, второй и третий входы 12, 13 первого инвертора 1 с третьим состоянием соответственно соединены с первым и вторым выводами 39, 40 первой группы 5 транзисторов триггера 4, второй и третий входы 20, 21 второго инвертора 2 с третьим состоянием соответственно соединены со вторым и первым и выводами 47, 46 второй группы 6 транзисторов, третий вывод 48 которой соединен с первым выводом 39 первой группы 5 транзисторов, третий вывод 41 которой соединен с первым выводом 46 второй группы 2 транзисторов триггера 4, описывается логической функцией сравнения следующего вида:

Y25=Х23⋅XB+Х24⋅XA,

где XA=Х39=Х46 - одинаковые логические уровни на выводах 39, 46 в стационарном состоянии триггера 4 элемента (данные, записанные в триггер в нормальном (прямом) виде); XB=Х40=Х47 - одинаковые логические уровни на выводах 40, 47 в стационарном состоянии триггера 4 элемента (данные, записанные в триггер в инверсном виде); Х23 - нормальный (прямой) логический уровень сигнала на входной шине 23 элемента; Х24 - инверсный логический уровень сигнала на входной шине 24 элемента; Y25 - логический уровень на выходной шине 25 элемента. Логической функцией элемента сравнения является логическая функция "ИСКЛЮЧИТЕЛЬНОЕ ИЛИ".

Воздействие одиночной ядерной частицы только на одну из групп транзисторов триггера, состоящего из двух групп транзисторов, не вызывает сбоя логического состояния триггера, а приводит лишь к временному изменению уровней напряжения (хранимых данных) на двух из четырех выводах триггера. Если одновременное воздействие оказывается и на транзисторы второй группы транзисторов и это воздействие больше порогового, то вероятен сбой логического состояния триггера 4 и искажение результата сравнения данных логическим элементом сравнения.

Критичными при оценке надежности логического элемента сравнения (селекции) данных с входных шин 23, 24 с данными, записанными в триггер 4, являются эффекты воздействия одиночной ядерной частицы на кристалл микросхемы, когда трек ядерной частицы проходит под углом θ=60°-75° относительно нормали к поверхности кристалла микросхемы (это принятое определение направления трека), что соответствует углам наклона трека частицы 15°-30° к поверхности кристалла микросхемы. Это критичные случаи воздействий одиночных ядерных частиц, приводящих к сбоям триггером и ячеек памяти, если сравнивать все возможные направления треков воздействия внутри шарообразной сферы всех направлений треков воздействия на кристалл микросхемы, на котором выполнен логический элемент сравнения (селекции) данных. Наиболее жестким случаем оценки является случай, когда трек частицы проходит, например, в непосредственной близости или просто через область обратно смещенного pn-перехода сток-подложка одного (или обоих) запертых транзисторов первой группы 5 транзисторов, а на один (или оба) запертых транзисторов второй группы 6 транзисторов действует заряд неосновных носителей, диффундирующих к нему от ближайшей к нему области трека частицы с его наклоном θ=60°-75° относительно нормали к поверхности кристалла микросхемы. При описанном воздействии на первую группу 5 транзисторов триггера происходит инверсия логических значений, хранимых на двух узлах группы (это вывод 40 первой группы и один из смежных выводов первой группы в зависимости от записанных данных 0101 или 1010). Чтобы сбой триггера из двух групп 5 и 6 не произошел, расстояния L5,6 между парами запертых МОП транзисторов, принадлежащим разным группам 5 и 6 транзисторов, должны быть больше порогового значения L5,6>LПОР. В этом случае собираемый стоковыми pn-переходами запертых транзисторов заряд неосновных носителей, диффундирующих к второй 6 группе транзисторов от ближайшей к нему области трека, не достигнет порогового значения, при сборе которого мог бы произойти сбой логического состояния триггера 4 (когда одновременно и на первую группу 5 транзисторов действует заряд с трека) и, соответственно, при дальнейшей обработке потока данных с входных шин 23, 24 на выход 25 стала бы поступать ложная недостоверная информация о результатах сравнения. Симметричным критическим вариантом воздействия является прохождение трека частицы в направлении от второй группы 6 транзисторов к первой группе 5 при преобладающем воздействии на область обратно смещенного pn-перехода сток-подложка запертых транзисторов второй группы 6 транзисторов. Для исключения сбоя логического состояния триггера, состоящего из двух групп транзисторов, должно быть выполнено требование, чтобы между парами одновременно запертых МОП транзисторов, принадлежащим разным группам 5 и 6 транзисторов, расстояния должны быть больше порогового значения L5,6>LПОР.

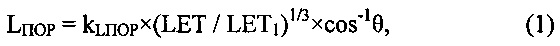

Пороговые значения расстояния LПОР между pn-переходами сток-подложка запертых транзисторов двух групп транзисторов зависят от линейных потерь энергии частицей LET, угла наклона трека θ, параметров кремния и характеристик транзисторов триггера. Оценку порогового значения расстояния можно рассчитать по следующему выражению:

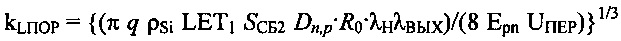

где  - масштабный коэффициент, характеризующий связь параметров воздействующей частицы и параметров чувствительных к сбору заряда областей транзисторов; LET - линейные потери энергии воздействующей частицей; LET1=1 МэВ×см2/мг - нормирующий коэффициент линейных потерь энергии; θ - угол наклона трека относительно нормали к поверхности кристалла микросхемы.

- масштабный коэффициент, характеризующий связь параметров воздействующей частицы и параметров чувствительных к сбору заряда областей транзисторов; LET - линейные потери энергии воздействующей частицей; LET1=1 МэВ×см2/мг - нормирующий коэффициент линейных потерь энергии; θ - угол наклона трека относительно нормали к поверхности кристалла микросхемы.

Следующие параметры входят в выражение (1) для расчета коэффициента сбора заряда kLПОР, а именно:

q - заряд электрона;

ρSi - плотность кремния;

Ep,n - энергия образования одной электронно-дырочной пары;

SСБ2=ΔlСБ×wСБ - площадь сбора заряда во второй группе 6 транзисторов;

ΔlСБ - размер области сбора заряда (pn-перехода сток-подложка) в одном направлении с направлением трека, a wСБ - в поперечном направлении;

Dn,p - коэффициент амбиполярной диффузии носителей заряда;

R0 - выходное сопротивление (усредненное значение) открытого МОП транзистора, соединенного его собственным стоком со стоком транзистора, собирающего заряд во второй группе 6 транзисторов;

UПЕР - напряжение переключения транзистора второй группы 6 триггера;

λН=(τН/τСП)а, а=τН/(τСП-τН) - коэффициент формы импульса фототока, переносящего заряд с трека.

Постоянные времени нарастания τН и спада τСП импульса фототока, образованного диффузией заряда от трека частицы, зависят от значения постоянной времени диффузии неравновесных носителей τD из области трека до собирающей заряд области второй группы транзисторов ячейки, и их связь известна (см. Fulkerson D.E. A physics-based engineering methodology for calculating soft error rates of bulk CMOS and SiGe heterojunction bipolar transistor integrated circuits // IEEE Transaction on Nuclear Science. 2010. V. 57. №1. pp. 348):

τСП=τD=4r2/(π2Dn,p) и τН=τСП/9.

Коэффициент λВЫХ определяется как λВЫХ=(τВЫХ/τСП)а, а=τВЫХ/(τСП-τВЫХ), где τВЫХ=RВЫХ.ОТКР.2×СУЗЛА - постоянная времени перезаряда узла триггера; СУЗЛА - емкость узла, заряд на которой образует импульс помехи с амплитудой UПЕР, переключающей триггер.

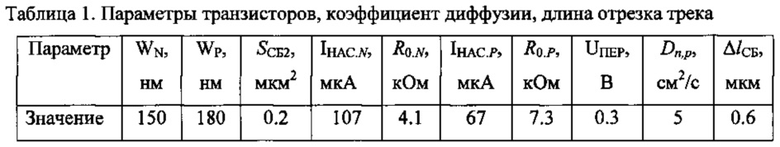

В таблице 1 приведены значения параметров транзисторов триггера по проектной норме КМОП 65 нм, значения коэффициента диффузии носителей заряда в кремнии и длина отрезка трека, из области которого диффундируют неравновесные носители заряда, которые были использованы при расчетах порогового значения расстояния LПОР.

Значение масштабного коэффициента составляет kLПОР=0.2 мкм при сборе заряда обратно смещенным pn переходом запертого РМОП транзистора и kLПОР=0.22 мкм при сборе заряда обратно смещенным pn переходом запертого NМОП транзистора. Более жесткие оценки соответствуют сбору заряда NМОП транзисторами, поскольку компенсирующий сброс части заряда, осуществляемый в данном случае открытым РМОП транзисторов, меньше,

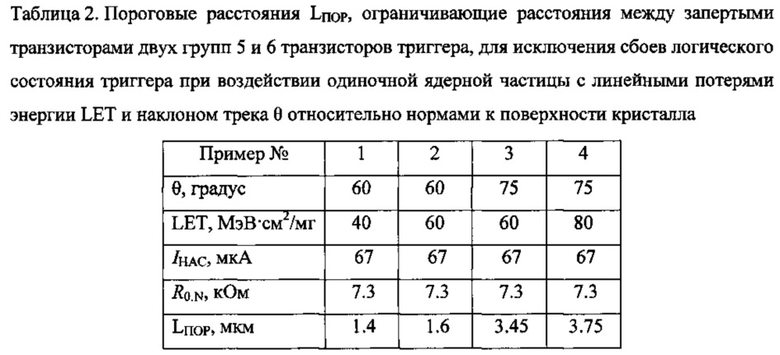

В таблице 2 приведены результаты моделирования пороговых расстояний LПОР в зависимости от параметров воздействующей частицы для триггера по проектной норме КМОП 65 нм, обеспечивающих стойкость к воздействию одиночных ядерных частиц с линейными потерями LET=40 МэВ⋅см2/мг или 60 МэВ⋅см2/мг для углов падения одиночной частицы θ=60° и θ=75° в зависимости от параметров транзисторов для более жесткого случая, когда выходное сопротивление R0.P=7.3 кОм соответственно для РМОП транзисторов при IHAC.P=67 мкА и емкость узла СУЗЛА=4 фФ.

Триггер на основе двух групп транзисторов по проектной норме КМОП 65 нм, которым снабжен логический элемент сравнения, обеспечивает бессбойную работу при воздействии одиночных частиц при углах наклона трека до 75° для частиц с линейными потерями энергии LET=60 МэВ×см2/мг при расстоянии между стоками запертых транзисторов двух групп L5,6>LПОР=3.45 мкм, а для более тяжелых частиц со значением коэффициента линейных потерь энергии LET=80 МэВ×см2/мг при расстоянии между стоками L5,6>LПОР=3.75 мкм.

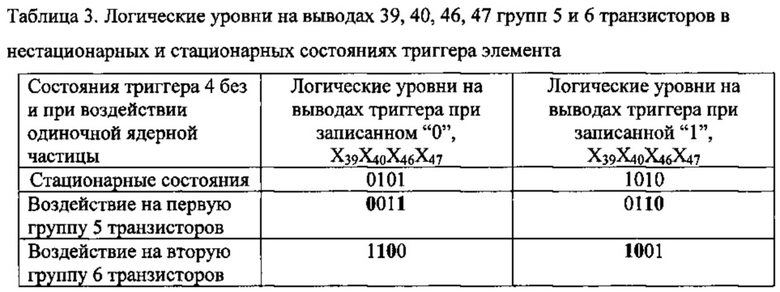

Воздействие одиночной ядерной частицы только на одну из групп транзисторов триггера, состоящего из двух групп транзисторов, не вызывает сбоя логического состояния триггера, а приводит лишь к временному изменению уровней напряжения (хранимых данным) на двух из четырех выводах триггера. При этом в группе транзисторов, не подвергнутой воздействию частицей, сохраняются исходные уровни (данные) на внутреннем узле (выводе) группы (это вывод 40 для первой группы 5 или вывод 47 для второй группы 6) и на одном из двух смежных выводах, который зависит от исходного логического состояния триггера 4. Особенностью триггера 4 на двух группах транзисторов является то, что после рассасывания в полупроводниковой кристалле заряда, вызванного воздействием частицы, переходный процесс завершается и уровни напряжений на всех выводах триггера восстанавливаются в соответствии исходным записанным в него данным. Для триггеров 4 с разделенными на две группы 5 и 6 транзисторами (которые разнесены на кристалле на расстояние, снижающее вероятность сбоя триггера логического элемента) в составе микросхем, изготавливаемых по современной объемной кремниевой КМОП технологии с проектными нормами 65 нм и менее, длительность такого нестационарного состояния не превышает 250 пс (Gadlage M.J. et al. Scaling trends in SET pulse widths in sub-100 nm bulk CMOS processes // IEEE Transactions in Nuclear Science. 2010. V. 57. №6. P. 3336-3341, Fig. 1). Так что значительного негативного влияния на результаты селекции данных всей последовательности выходных сигналов на выходной шине 25 логического элемента не будет происходить в сравнении с возможными существенными потерями в надежность выполнения логической функции сравнения, которые происходят при сбое традиционного КМОП D-триггера, который использован в прототипе и аналогах. В таблице 3 приведены варианты сочетания логических уровней на выводах группах 5 и 6 триггера 4 в исходном стационарном состоянии и во время вариантов переходного процесса (в нестационарных состояниях) при воздействии частицы на одну из групп транзисторов. Жирным шрифтом в таблице 3 отмечены уровни на выводах 39, 40, 46, 47 триггера 4 элемента, сохраняющих в нестационарном состоянии значения, соответствующие исходным уровням при хранении "0" (Х39Х40Х46Х47=0101) и "1" (Х39Х40Х46Х47=1010).

При нахождении триггера логического элемента в нестационарном состоянии, вызванном воздействием одиночной частицы только на одну из групп 5 или 6 транзисторов, согласно данным в таблице 3 логические уровни Х39Х40Х46Х47 на выводах 39, 40, 46, 47 групп 5 и 6 для двух выводов триггера временно инвертируются до окончания переходного процесса, а уровни двух выводов сохраняются и соответствуют значениям, изначально записанным в узлы триггера. При размерах транзисторов, соответствующих проектным нормам КМОП 65 нм и менее, воздействие одиночной тяжелой ядерной частицей захватывает площадь не 1-2 мкм2, поэтому типичным является воздействие на несколько транзисторов. При воздействии частицы одновременно на два обратно смещенных стоковых pn-перехода двух запертых транзисторов одной группы транзисторов триггера 4 (например, пары транзисторов 35, 37 в первой группе 5 или пары 42, 44 во второй группе 6 в логическом состоянии триггера "1") возможны только два варианта комбинаций логических состояний Х39Х40Х46Х47 выводов двух групп 5 и 6. Для исходной логической "1" эти комбинации состояний будут: 0110, 1001 и для исходного логического "0" - 0011, 1100

Результаты моделирования электрических характеристик логического элемента сравнения по проектно-технологической норме объемный КМОП 65 нм.

Селекция в режиме получения логического "0" на выходной шине 25 элемента при нахождении триггера 4 элемента в стационарных состояниях (0101 или 1010) при всех вариациях значений напряжений логических нуля и единицы на выводах 39, 40, 46, 47 триггера элемента из-за разброса параметров в пределах U0=0-0.3 В и U1=0.6-1.0 В дает правильный результат на выходной шине 25 значение UВЫХ25=U0=0.

Селекция в режиме получения логической "1" на выходной шине 25 элемента при нахождении триггера 4 элемента в стационарных состояниях (0101 или 1010) при всех вариациях значений напряжений логических нуля и единицы на выводах 39, 40, 46, 47 триггера элемента из-за разброса параметров в пределах U0=0-0.3 В и U1=0.6-1.0 В дает правильный результат на выходной шине 25 значение UВЫХ25=U0=UИП=1.0 В.

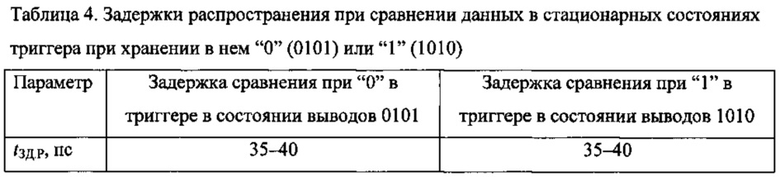

Динамические искажения в режиме чтения характеризует задержка распространения tЗД.Р дифференциальных сигналов состояний с входных шин 23, 24 элемента на выходную шину 25, которая не зависит от состояния уровней на выводах двух групп 5 и 6 транзисторов, введенных в состав логического элемента. В таблице 4 приведены значения задержки распространения сигнала - tЗД.Р при сравнении (селекции) данных в стационарных и нестационарных состояниях для логического элемента сравнения по проектно-технологической норме объемный КМОП 65 нм. Задержки с такими значениями при реальных тактовых частотах до 2 ГГц не влияют на результаты сравнения.

Пример реализации изобретения

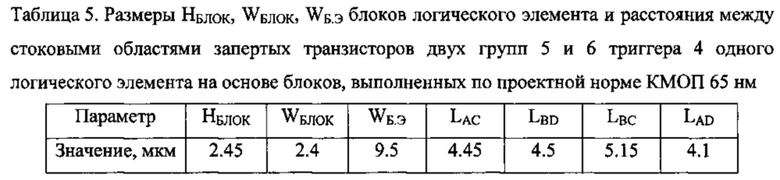

Устройство по изобретению реализовано в виде блока ассоциативного селектора ЗУ в составе КМОП СБИС микропроцессорной системы по проектной норме 65 нм. Блок содержит 32×64 предложенных логических элементов. Эскизное изображение конструкции одного логического элемента приведено на фиг. 3. Эскизное изображение конструкции базового элемента ассоциативного селектора, состоящего из двух логических элементов, взаимное расположение блоков которых обеспечивает необходимое расстояние между взаимно чувствительными узлами запертых транзисторов, приведено на фиг. 4. Для достижения технического результата - повышения надежности (помехоустойчивости) выполнения логической функции селекции при воздействии одиночной ядерной частицы, когда триггер 4 на основе двух групп 5 и 6 транзисторов находится в стационарном состоянии - транзисторы 7, 8, 9, 10 первого инвертора 1 с третьим состоянием размещены на кристалле интегральной микросхемы рядом с транзисторами 35, 36, 37, 38 первой группы 5 транзисторов триггера 4 и образуют первый блок логического элемента, транзисторы 15, 16, 17, 18 второго инвертора 2 с третьим состоянием размещены на кристалле интегральной микросхемы рядом с транзисторами 42, 43, 44, 45 второй группы 6 транзисторов триггера 4 и образуют второй блок логического элемента, при этом первый и второй блоки элемента, включающие группы 5 и 6 транзисторов триггера 4 элемента (см. фиг. 3), размещены на расстоянии, обеспечивающем расстояние между взаимно чувствительными узлами запертых транзисторов двух групп 5 и 6 транзисторов триггера 4 больше порогового расстояния LПОР=3.75 мкм для исключения одновременного воздействия заряда с трека одиночной ядерной частицы на обе группы 5 и 6 транзисторов триггера 4 для всех тяжелых ядерных частиц (ионов) с линейными потерями энергии в диапазоне до LET=80 МэВ×см2/мг и при углах наклоном трека частиц от θ=0° до θ=75°.

Основой топологической конструкции статического ассоциативного селектора является базовый элемент на фиг. 4, состоящий из двух предложенных логических элементов на основе четырех блоков, образующих эти два логических элемента. Каждый из двух логических элементов состоит из двух блоков, отмеченных индексами «а» и «б» соответственно для первого и второго логических элементов сравнения на основе соответствующих групп 5 и 6 транзисторов и инверторов с третьим состоянием (всего четыре блока, которые чередуются). Первый логический элемент содержит группы 5а и 6а транзисторов, второй логический элемент - группы 5б и 6б транзисторов. Расположение транзисторов в каждой из элементов на фиг. 3 соответствует расположению транзисторов в элементе на фиг. 3.

В таблице 5 приведены размеры базовых блоков, а именно высота НБЛОК и ширина WБЛОК каждого из четырех блоков и общая ширина WБ.Э всего базового элемента из двух предложенных логических элементов сравнения. В таблице 5 приведены и значения расстояний между областями обратно смещенных стоковых pn-переходов, обозначенных на фиг. 4 буквами А, В, С, D для транзисторов 35, 37, 42, 44, расположенных в двух разных группах 5 и 6 одного логического элемента и одновременно находящихся в запертом состоянии при хранении "1" в триггере 4. Эти расстояния LAC; LBD; LBC; LAD>LПОР=3.75 мкм больше порогового значения, что обеспечивает требуемый уровень устойчивости предложенных логических элементов сравнения, изготовленных по проектно-технологической норме объемный КМОП 65 нм. Минимальное из этих расстояний LAD=4,1 мкм ≥ LПОР=3.75 мкм больше порогового расстояния, что исключает одновременное воздействия заряда с трека одиночной ядерной частицы на обе группы 5 и 6 транзисторов триггера 4 для всех частиц с линейными потерями энергии до LET=80 МэВ×см2/мг при углах наклоном трека частиц от θ=0° до θ=75°.

Изобретение относится к области вычислительной техники и может быть использовано в блоках ассоциативных селекторов запоминающих устройств. Техническим результатом является повышение помехоустойчивости логического элемента при воздействии одиночных ядерных частиц. Устройство содержит два инвертора с третьим состоянием, порт записи данных, триггер, состоящий из двух групп транзисторов, каждая из которых включает две пары РМОП и NMOП транзисторов. 4 з.п. ф-лы, 4 ил., 5 табл.

1. Логический элемент сравнения комплементарной металл-оксид-полупроводниковой структуры ассоциативного селектора запоминающего устройства, включающий два инвертора с третьим состоянием и порт записи данных, размещенных на кристалле интегральной микросхемы, первый и второй входы инверторов с третьим состоянием соединены соответственно с первой и второй входными шинами, а выходы инверторов с третьим состоянием соединены с выходной шиной элемента, входы порта записи данных соединены с битовыми линиями, вход выборки порта записи данных соединен с линией выборки, отличающийся тем, что логический элемент снабжен триггером, состоящим из двух групп транзисторов, каждая из которых включает две пары РМОП и NМОП транзисторов, затвор РМОП транзистора в каждой паре соединен со стоком NМОП транзистора этой пары, затвор которого соединен с стоком РМОП транзистора этой пары, затворы РМОП и NМОП транзисторов группы соединены соответственно с первым и вторым выводами группы транзисторов триггера, а затворы NМОП транзисторов первой и второй пар группы соединены соответственно со вторым и третьим выводами группы транзисторов триггера, истоки РМОП и истоки NМОП транзисторов соединены соответственно с шиной питания и общей шиной элемента, при этом второй и третий входы первого инвертора с третьим состоянием соответственно соединены с первым и вторым выводами первой группы транзисторов триггера, второй и третий входы второго инвертора с третьим состоянием соответственно соединены со вторым и первым выводами второй группы транзисторов триггера, третий вывод которой соединен с первым выводом первой группы транзисторов триггера, третий вывод которой соединен со вторым выводом второй группы транзисторов триггера, при этом выходы порта записи данных соединены с соответствующими выводами двух групп транзисторов триггера, причем две группы транзисторов триггера размещены на кристалле интегральной микросхемы одна от другой на расстоянии, исключающем одновременное воздействие одиночной ядерной частицы на обе группы транзисторов с уровнем больше порогового.

2. Логический элемент сравнения по п. 1, отличающийся тем, что каждый инвертор с третьим состоянием включает пару РМОП и пару NМОП транзисторов, стоки первых РМОП и NМОП транзисторов соединены соответственно с истоками вторых РМОП и NМОП транзисторов, стоки которых объединены и соединены с выходом инвертора с третьим состоянием, затворы первых РМОП и NМОП транзисторов соединены с первым входом, а затворы вторых NМОП и РМОП транзисторов соединены соответственно со вторым и третьим входами инвертора с третьим состоянием, истоки первого РМОП и первого NМОП транзисторов соединены соответственно с шиной питания и общей шиной элемента.

3. Логический элемент сравнения по п. 1, отличающийся тем, что каждый инвертор с третьим состоянием включает пару РМОП и пару NМОП транзисторов, стоки первых РМОП и NМОП транзисторов соединены соответственно со стоками вторых РМОП и NМОП транзисторов, истоки которых объединены и соединены с выходом инвертора с третьим состоянием, затворы первых РМОП и NМОП транзисторов соединены с первым входом, а затворы вторых NМОП и РМОП транзисторов соединены соответственно со вторым и третьим входами инвертора с третьим состоянием, истоки первого РМОП и первого NМОП транзисторов соединены соответственно с шиной питания и общей шиной элемента.

4. Логический элемент сравнения по п. 1, отличающийся тем, что первая группа транзисторов триггера и первый инвертор с третьим состоянием составляют первый блок логического элемента, вторая группа транзисторов триггера и второй инвертор с третьим состоянием составляют второй блок логического элемента, которые размещены на кристалле интегральной микросхемы один за другим, при этом i-й и (i+K)-й блоки образуют i-й логический элемент сравнения, где i=1; 2; …; K.

5. Логический элемент сравнения по п. 1, отличающийся тем, что указанное расстояние, исключающее одновременное воздействие одиночной ядерной частицы на обе группы транзисторов триггера с уровнем больше порогового, равно минимальному расстоянию между транзисторами двух групп триггера, выбранному в соответствии с требованиями исключения сбоев состояния триггера логического элемента при воздействии одиночных ядерных частиц с заданными максимальными линейными потерями энергии и максимальным наклоном трека частиц относительно нормали к поверхности кристалла.

| US 5699288 A, 16.12.1997 | |||

| JPH 11149366 A, 02.06.1999 | |||

| Устройство для стабилизации горения | 1972 |

|

SU438797A1 |

| ЯЧЕЙКА ПАМЯТИ КОМПЛЕМЕНТАРНОЙ МЕТАЛЛ-ОКСИД-ПОЛУПРОВОДНИКОВОЙ СТРУКТУРЫ ОЗУ | 2015 |

|

RU2580071C1 |

| ЯЧЕЙКА ПАМЯТИ КОМПЛЕМЕНТАРНОЙ МЕТАЛЛ-ОКСИД-ПОЛУПРОВОДНИКОВОЙ СТРУКТУРЫ ОЗУ | 2013 |

|

RU2554849C2 |

Авторы

Даты

2017-05-30—Публикация

2016-05-25—Подача