1И Изобретение относится к импульсной технике и может быть использова но в цифровых устройствах,- выполнен шлх на интегральных схемах. Известен син..ронный логический злемент на МОП-транзисторах, содержащий два МОП-транзистора дополняющего типа, истоки которых подключены к соответствующим шинам питания , а затворы объединены и являются тактовым входом устройства, и параллельно включенные МОП-транзисторы п-типа, стоки которых подключены к стоку дополняющего МОП-транзистора р-типа и к выходу устройства, истоки - к стоку дополняющего МОП-транзистора п-типа, а затворы являются информадионны1«1 входами ус ройства. Синхронный логический элемент мо жет быть использован в качестве выходного логического каскада, которы при объединении его выхода с выхода ми аналогичных синхронных логически элементов позволяет реализовать логическую функцию Монтажное И (и при изменении типа МОП- транзисторов - Монтакное ИЛИ С П. Известное устройство имеет сущес венный недостаток - низкое значение числа информационных входов. Действительно, для получения дос таточной нагрузочной способности пр работе устройства в качестве выходного каскада МОП-транзисторы, входя щие в состав устройства, должны имет ртносительно большие размеры, что при большом числе информационных вх дов, т.е. при большом числе МОП-тра зисторов , приведет к существенному усложнению интегральной МОП-структу ры, снижению надежности устройства повышению потребляемой мощности. Наиболее близким к предлагаемому по технической сущности является синхронный выходной каскад на ЮПтранзисторах, содержащий синхронный, логический элемент, входы которого являются входаьм устройства, и вертор, вход которого подключен к выходу синхронного логического элемента, и дна фиксирующих МОП-транзистора одного типа, включенных последовательно между шиной питания и входом инвертора, выход которого подключен к затвору первого фиксирующего МОП-транзистора, затвор второго 4«ксирующего МОП-транзистор подключен к тактовому входу устрой3аства. При объединении выхода синхронного выходного каскада с выходами аналогичных устройств и при соответствующем выборе сопротивлений открытых каналов МОП-транзисторов инвертора можно реализовать логическую функцию Монтажное И или Монтажное ИЛИ C2J. Недостатком синхронного выходного каскада является большая потребляемая мощность. Это обусловлено большими сквозными токами, проходящими через каналы МОП-транзисторов инвертора, как в процессе переключения каскада, когда в течении короткого промежутка времени оба МОП-транзистора инвертора открыты, так и в течении всего времени при реализации на выходе каскада функции Монтажное И или Монтажное ИЛИ, когда в инверторе одного каскада открыт, например, МОП-транзистор р-типа, а в инверторе Д зугого каскада открыт МОП-транзистор h-типа.. Целью изобретения является снижение потребляемой мощности и увеличение нагрузочной способности. Для достижения поставленной цели в синхронный выходной каскад на МОП-транзисторах, содержащий синхронный логический элемент, входы которого являются входами устройства, инвертор, вход которого подключен к выходу синхронного логического элемента, и два фиксирующих ЮП-транзйстора одного типа, включенных пог следовательно между первой шиной питания и входом инвертора, выход которого подключен к затвору первого фиксирующего МОП-транзистора, введены первый и второй элементы задержки, первый и второй логические элементы, дополнительный инвертор и два выходных ЮП-транзистора дополняющего типа, истоки которых подключены соответственно ко второй шине питания и общей щине, стоки объединены и являются выходом устройства, а затворы подключены, соответственно, к выходам первого и второго логических злементов, первые входы логических элементов подключены к тактовому входу устройства и ко входу первого элемента задержки, выход которого подключен ко входу второго элемента задержки ,и к тактовому входу синхронного логического элемента, второй вход первого логического элемента подклю3j

чен к выходу второго элемента задержки и ко входу дополнительного

.инвертора, выход которого подключен к затвору второго фиксирующего ШПтранзистора, второй вход второго логического элемента подключен к выходу инвертора.

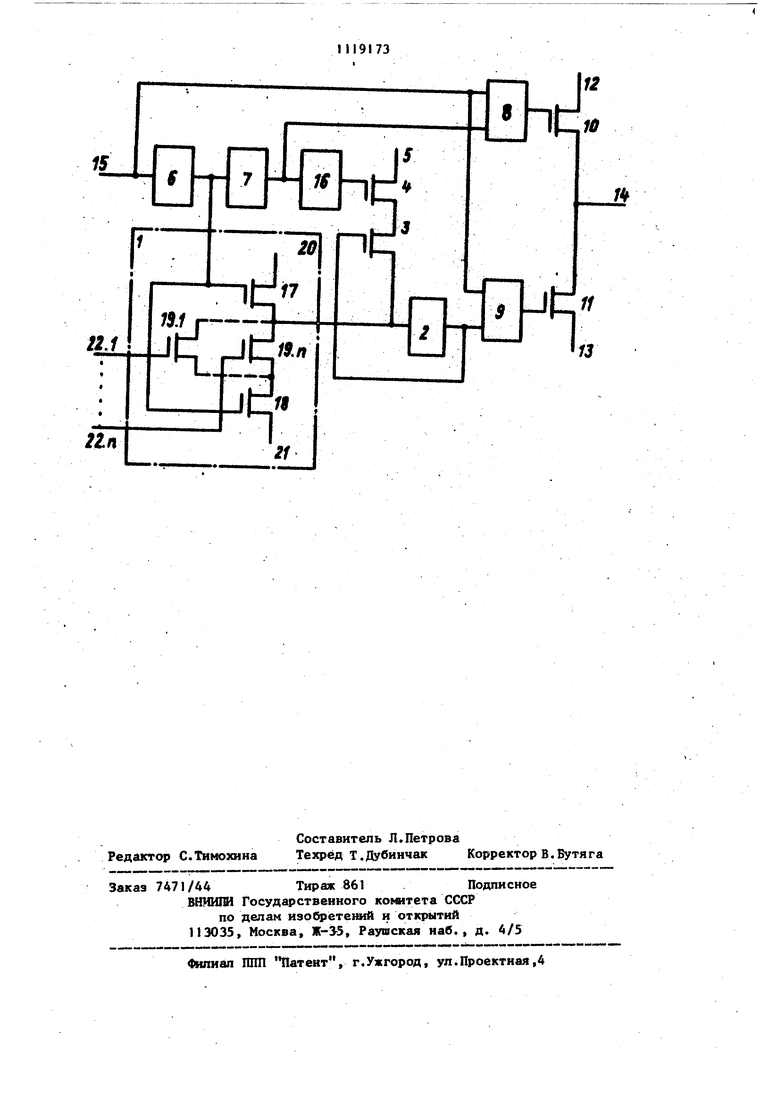

На чертеже представлена принципиальная электрическая схема устройства.

Выход синхронного логического элемента 1 подключен ко входу инвертора 2 , два фиксирующих МОП-транзистора одного типа 3 и 4 последовательно включены мезвду входом инвертора 2 и шной питания 5, затвор первого 4мксирующего МОП-транзистора подключен к выходу инвертора 2, выход первого элемента задержки 6 подключен к тактовому входу синхронного логического элемента 1 и ко входу второго элемента задержки 7, выходы первого и второго логических элементов 8 и 9 подключены соответственно к затворам первого и второго выходных МОП-транзисторов дополняющего тнпа 10 и II, истоки которых подключены соответственно ко второй шине питания 2 и общей шине 13, а стоки объединены и являются выходом 14 устройства. Первые вхо73

ды логических элементов 8 и 9 подключены к тактовому вkoдy 15 устройства и ко входу первого элемента задержки 6, второй вход первого логического элемента 8 подключен к выходу второго элемента задержки 7 а ко входу дополнительного инвертора 16, выход которого подключен к затвору второго фиксирующего ШП-транэистора 4, второй вход второго логического элемента 9 подключен к выходу инвертора.

Синхронный логический элемент 1 реализован на ШП-транзисторах 17 и 18 дополняющего типа и на МОП-транзисторах 19. 1-19.г, тип которых аналогичен типу МОП-транзистора 18. Истоки дополняющих МОП-транзисторов 17 и 18 подключены соответственно к шине питания 20 и общей шине 2I. Затворы МОП-транзисторов 19.1-19.Р подключены соответственно ко входам 22.1-22.и устройства.

Устройство работает следующим образом.

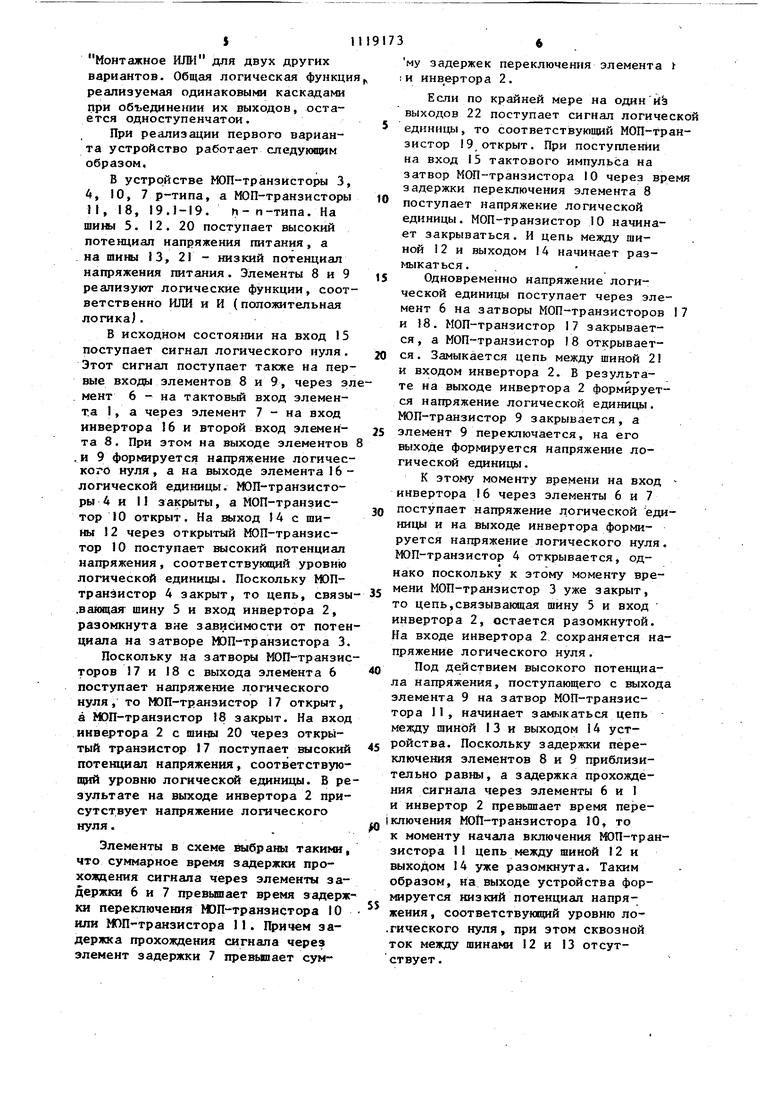

В соответствии с таблицей синхронный выходной каскад может реализо- , вать четыре логические функции в зависимости от типа используемых элементов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКОЕ КОНВЕЙЕРНОЕ УСТРОЙСТВО | 2000 |

|

RU2175811C1 |

| КАСКАДНОЕ ПАРАФАЗНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2008 |

|

RU2349028C1 |

| КАСКАДНОЕ ПАРАФАЗНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2012 |

|

RU2515225C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ И ВОССТАНОВЛЕНИЯ МОДИФИЦИРОВАННОГО КОДА ХЕММИНГА ДЛЯ 16-РАЗРЯДНЫХ ДВОИЧНЫХ ЧИСЕЛ | 2024 |

|

RU2824472C1 |

| Делитель частоты импульсной последовательности | 1982 |

|

SU1133666A1 |

| ДВУХТАКТНЫЙ СДВИГАЮЩИЙ РЕГИСТР | 2014 |

|

RU2549136C1 |

| КОМПАРАТОР ДВОИЧНЫХ ЧИСЕЛ | 2021 |

|

RU2762061C1 |

| КАСКАДНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА КМДП ТРАНЗИСТОРАХ | 1998 |

|

RU2132591C1 |

| Усилитель считывания на моп-транзисторах /его варианты/ | 1980 |

|

SU883968A1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ КМОП СУММАТОР | 2011 |

|

RU2454703C1 |

СИНХРОННЫЙ ПЫХОДНОЙ КАСКАД на МОП Транзисторах, содержащий синхронный логический элемент, входы которого являются входами устройства, инвертор, вход которого подключен к выходу синхронного логического элемента, и два фиксирующих МОП-транзистора одного типа, включенных последовательно между первой шиной питания и входом инвертораj выход которого подключен к затвору первого фиксирующего МОП-транзистора, отличающийся тем, что, с целью снижения потребляемой мощности и увеличения нагрузочной способности, в него введены первый и второй элв менты задержки, первый и второй логические элементы, дополнит ьный инвертор и два выход}г 1х МОП транзистора дополняющего типа, истоки которых подключены соответственно к второй шине питания и общей шине, стоки объединень и являются выходом устройства, а затворы подключены соответственно к выходам первого и второго логических элементов, первые входы логических элементов подключены к тактовому входу устройства и к входу первого элемента задержки, выход которого подключен к входу второго элемента задержки и к тактовому входу синхронного логического элемента, второй вход первого логического элемента подключен к выходу второго элемента задержки и к входу дополнительного инвертора, выход которого подключен к затвору второго фиксирующего МОП-транзистора, второй вход логического элемента подключен к СО выходу инвертора. со

ПоложительнаяПоложительная

р-тип

ПоложительнаяОтрицательная

п-тип

ОтрицательнаяПоложительная

р-тип

ОтрицательнаяОтрицательная

п-тип

Примечани е: МОП-транзисторы 3, 4, 17 одного типа;

МОП-транзисторы 18, 19 другого типа; , МОП-транзисторы 10 и I1 дополняющего типа; шины 5 и 20 одной полярности.

При подключении к выходу синхрон- 55также реализация на общей выходе

ного выходного каскада выходов ана-логической функции Монтажное И,

jлогичных устройств (и при объеди-для первого и третьего вариантов

нении их тактовых входов) возможнареализации каскада, или функции

ИЛИИИЛИ-НЕ

ИЛИ-НЕИ-НЕИЛИ

И-НЕИЛИ-НЕИ

ИИЖИ-НЕ S1 Монтажное ИЛИ для двух других вариантов. Общая логическая функци реализуемая одинаковыми каскадами при объединении их выходов, остаётся одноступенчатой. При реализации первого варианта устройство работает следующим образом, В устройстве МОП-транзисторы 3, 4, 10, 7 р-типа, а МОП-транзисторы П, 18, 19.1-19. h-n-типа. На шины 5. 12. 20 поступает высокий потенциал напряжения питания, а на шины 13, 21 - низкий потенциал напряжения питания. Элементы 8 и 9 реализуют логические функции, соот ветственно ИЛИ и И (положительная логика). В исходном СОСТОЯ1ШИ на вход 15 поступает сигнал логического Нуля. Этот сигнал поступает также на первые входы элементов 8 и 9, через эл мент 6 - на тактовый вход элемента 1 , а через элемент 7 - на вход инвертора 16 и второй вход элемента 8. При этом на выходе элементов .и 9 формируется напряжение логического нуля, а на выходе элемента 16 логической единицы. МОП-транзисторы 4 и 11 закрыты, а МОП-транзистор Ш открыт. На выход 14 с шины 12 через открытый МОП-транзистор 10 поступает высокий потенциал напряжения, соответствующий уровню логической единицы. Поскольку МОПтранзистор 4 закрыт, то цепь, связы .вающая шину 5 и вход инвертора 2, разомкнута вне зависимости от потен циала на затворе МОП-транзистора 3. Поскольку на затворы МОП-транзис торов 17 и 18с выхода элемента 6 поступает напряжение логического нуля, то МОП-транзистор 17 открыт, а МОП-транзистор 18 закрыт. На вход инвертора 2 с шины 20 через открытый транзистор 17 поступает высокий потенциап напряжения, соответствующий уровню логическсй единицы. В ре зультате на выходе инвертора 2 присутствует напряжение логического нуля. Элементы в схеме выбраны такими что суммарное время задержки прохождения сигнала через элементы задержки 6 и 7 превышает время задерж ки переключения МОП-транзистора 10 или МОП-транзистора 11. задержка прохождения сигнала через элемент задержки 7 превышает сум3му задержек переключения элемента t и инвертора 2. : Если по крайней мере на один Из выходов 22 поступает сигнал логической единицы, то соответствующий МОП-Транзистор 19 открыт. При поступлении на вход 15 тактового импульса на затвор МОП-транзистора 10 через время задержки переключения элемента 8 поступает напряжение логической единицы. МОП-транзистор 10 начинает закрываться. И цепь между шиной 12 и выходом 14 начинает размыкаться. Одновременно напряжение логической единицы поступает через элемент 6 на затворы МОП-транзисторов I7 и 18. МОП-транзистор 17 закрывается , а МОП-транзистор 18 открывается . Замыкается цепь между шиной 21 и входом инвертора 2. В результате на выходе инвертора 2 формируется напряжение логической единицы. МОП-транзистор 9 закрывается, а элемент 9 переключается, на его выходе формируется напряжение логической единицы. К этому моменту времени на вход инвертора 16 через элементы 6 и 7 поступает напряжение логической единицы и на выходе инвертора формируется напряжение логического нуля. ЮП-транзистор 4 открывается, однако поскольку к этому моменту времени МОП-транзистор 3 уже закрыт, то цепь,связывающая шину 5 и вход инвертора 2, остается разомкнутой. На входе инвертора 2 сохраняется напряжение логического нуля. Под действием высокого потенциала напряжения, поступающего с выхода элемента 9 на затвор МОП-транзистора 11, начинает замыкаться цепь между шиной f 3 и выходом 14 устройства. Поскольку задержки переключения элементов 8 и 9 приблизительно , а задержка прохождения сигнала через элементы 6 и 1 и инвертор 2 превьш1ает время переключения МОП-транзистора 10, то к моменту начала включения ШП-транзистора 11 цепь между шиной 12 и выходом 14 уже разомкнута. Таким образом, на выходе устройства формируется низкий потенциал напряжения , соответствующий уровню логического нуля, при этом сквозной ток между шинами 12 и 13 отсутствует .

7Ч

После окончания тактового импульса на первые входы элементов 8 и 9 поступает напряжение логического нуля. Элемент 9 переключается и на затвор №)П-транзистора 11 поступает низкий потенциал напряжения. Цепь между шиной 13 и выходом 14 размыкается. Элемент 8 начинает переключаться и формировать на своем выходе напряжение логического куля с задержкой относительно элемента 9, равной времени прохождения сигнала через элементы 6 и 7. Эта задержка превышает время переключения МОП-транзистора II. В результате цепь между шиной 12 и выходом 14 начинает зш4ыкаться в момент времени, когда транзистор I I уже закрыт. Таким образом, и в момент времени после окончания тактового импульса в цепях выходных дополняющих МОП-транзисторов 10 и И сквозной ток отсутствует..

Если на все выходы 22 элемента 2 поступает сигнал .логического нуля, тогда все МОП-транзисторы 19 закрыты. Очерёдной тактовый импульс со входа 15 поступает на первые входы элементов 8 и 9. На выходе элемента 8 формируется напряжение логической еданиды. МШтранзисторЮ закрывается, и цепь, связывающая шину 12 с выходом )4, размыкается.

Одновременно тактовый импульс через элемент 6 поступает на тактовый вход элемента 1. МОП-транзистор 18 открывается, а ИШ-транзистор 17 закрывается, Цепь между шиной 20 и входом инвертора 2 размикается. Однако посольку все МОП-транзисторы 19 закрыты, то и цепь между шиной 21 и входом инвертора 2 остается также разомкнутой.

К этому моменту времени задержанный на элементах 6 и 7 тактошй импульс поступает на вход инвертора 16, и на выходе инвертора формируется напряжение логического

38

нуля. МОП-транзистор 4 открывается, высокий потенциал напряжения с шины 5 через открытые ШП-транзисторы 4 и 3 поступает на вход инвертора 2 и на его выходе сохраняется уровень напряжения логического нуля.,

В результате элемент 9 остается в исходном состоянии, МОП-транзистор 11 остается закрытым, а цепь между шиной 13 и выходом 14 - разомкнутой. На выходе 14 устройства сохраняется К 1сокий потенцнал напряжения , соответствующнй уровню

логической единицы.

Если при этом к выходу 14 устройства подключен аналогичного каскада, однако такой, в котором МОП-транзистор 1 I в этот момент времени открыт (т.е. по крайней мере на одном из входов 22 аналогичного каскада присутствует напряжение логической единицы), то на общем выходе каскадов формируется ,низкий потенциал напряжения, соответствующий уровню логического нуля. При объединении каскадов реализуется функция Монтажное И, а общая логическая функция каждого

каскада остается одноступенчатсхй ИЛИ-НЕ..

Выбирая соответствующим образом значение величины задержки элемента 6, можно учесть разброс параметров различных синхронных К1ХОДНЫХ каскадов, исключив прохождение сквозных токов через выходные дополняюIWe МОП-транзисторы разных каскадок при объединении их тактовых входов и выходов.

Расчеты на ЭВМ показывают, что исключение сквозных токов в мощных выходюлх дополняющих трш1зисторах на 15-20% снижает потребляемую мощность синзфонного выходного каскада.

Таким образом, технико-экономический эффект от нспсльзованияизобретения заключается в уменьшении

потребляемы мощности.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ запрессовки не выдержавших гидравлической пробы отливок | 1923 |

|

SU51A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Патент США № 3985955, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-10-15—Публикация

1983-06-21—Подача