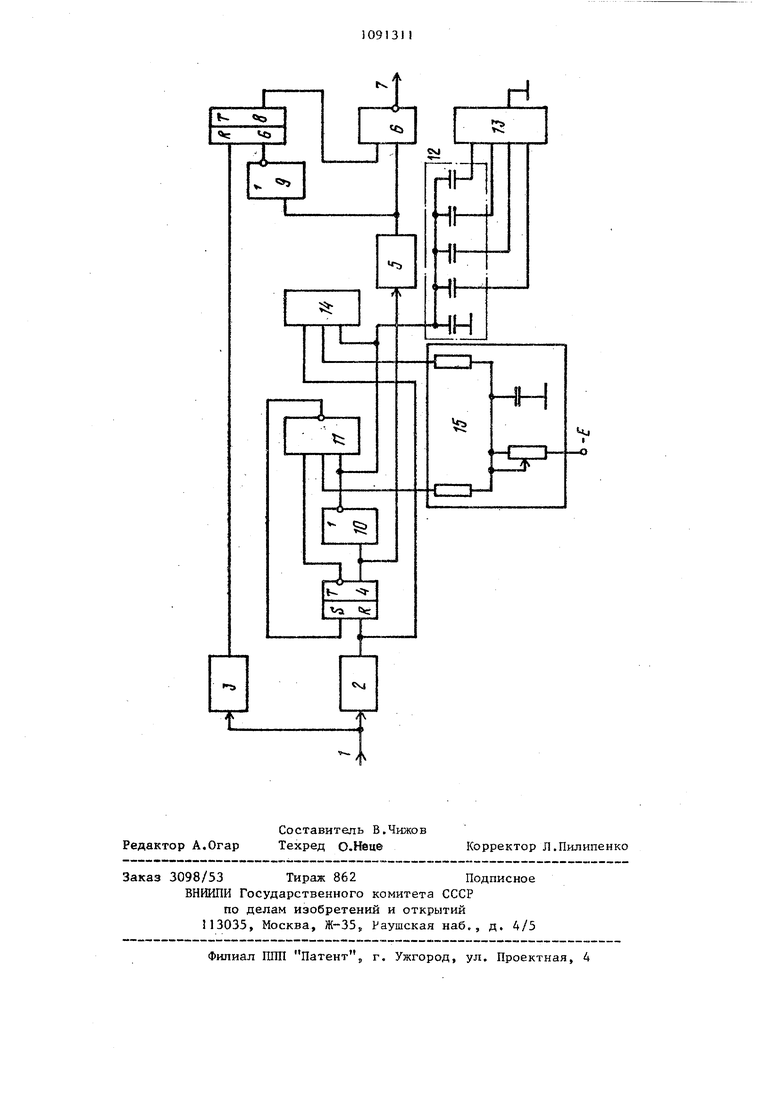

i Изобретение относится к ядерной электронике и может быть использовано при измерении амплитуд статистически распределенных импульсов в медицине, биологии и других областях науки и техники. Известен амплитудный дифференциальный дискриминатор, в котором выходной сигнал формируется с произ вольным сдвигом относительно входного, а временный сдвиг уменьшается за счет введения схемы временной привязки (например, к вершине входного сигнала), сигнал с выхода которой задерживается и стробирует выходной сигнал дискриминатораС1J. Однако такое выполнение дискрими натора приводит к значительному уве личению оборудования, поскольку схе ма временной привязки является слож ным аналоговым устройством по сравнению с собственно дифференциальным дискриминатором и имеет нелинейный усилитель, дифференциатор, еще один дискриминатор и дополнительную логику. Кроме того, дискриминатор не позволяет получить главную задержку выходного сигнала, что ограничивает его применение. Наиболее близким техническим решением к изобретению является ампли тудный дифференциальный дискриминатор, которьй состоит из дискриминаторов нижнего и верхнего уровней, формирователя со схемой И и инвертором, а также триггером, блокирующим схему И при срабатывании дискри минатора верхнего уровня. В дискрим наторе выходной сигнал формируется прюизвольным сдвигом относительно выходного, так как генерация этого сигнала производится от заднего фронта дискриминатора нижнего уровня 12 3 . Недостатком известного амплитудного дифференциального дискриминатора является низкая точность временной привязки выходного сигнала, заключающаяся в том, что выходной сигнал имеет большую неопределенность относительно входного. Это не позволяет использовать дискриминатор в устройствах со схемами совпадений, многомерном анализе и др. Цель изобретения - повышение точ ности временной привязки выходного сигнала. Поставленная цель достигается тем, что в амплитудный дифференциал ный дискриминатор для спектрометрического анализа, содержащий дискриминаторы верхнего и нижнего уровней, входы которых соединены с входной шиной, тригг.ер, первый вход которого соединен с выходом дискриминатора верхнего уровня, а второй вход через логический элемент НЕ соединен с выходом формирователя импульсов и первым входом выходного логического элемента И, второй вход которого подключен к выходу триггера, введены дополнительный триггер RS-типа, дополнительные логические элементы НЕ и И, генератор тока, блок конденсаторов с переключателем и источник зарядного тока, первый выход которого соединен с первым входом дополнительного логического элемента И, выходом дополнительного логического элемента НЕ и точкой соединения конденсаторов блока конденсаторов, вторая обкладка одного из которых соединена с общей шиной непосредственно, а вторые обкладки остальных конденсаторов соединены с общей шиной через переключатель, причем выходы генератора тока Соединены с вторым входом дополнительного логического элемента И и первым входом источника зарядного тока, второй вход которого соединен с выходом дискриминатором нижнего уровня и R-входом дополнительного триггера RS-типа, S-вход которого подключен к выходу дополнительного логического элемента И, третий вход которого подключен к одному выходу дополнительного триггера RS-типа, второй выход которого соединен с входом дополнительного логического элемента НЕ и входом формирователя импульсов. На чертеже представлена блоксхема амплитудного дифференциального дискриминатора. Амплитудный дифференциальный дискриминатор содержит входную шину 1, дискриминаторы нижнего 2 и верхнего 3 уровней, триггер 4, формирователь 5 импульсов и выходной логический элемент И 6, соединенный с выходом 7, Выход дискриминатора 3 верхнего уровня через триггер 8 подключен к второму входу выходного логического элемента И 6, а выход формирователя 5 импульсов через логический элемент НЕ 9 - к второму входу триггера 8. Один выход триггера 4 через логический элемент НЕ О и логический элемент И 11 сое динен со своим вторым входом, а второй выход подключен к второму входу логического элемента И 11.

Выход логического элемента НЕ 10 через блок 12 конденсаторов и переключатель I3 соединен с общей шиной, а также подключен к первому выходу источника 14 зарядного тока. Выходы генератора 15 тока соединены с вторым входом логического элемента И 11 и первым входом источника 14 зарядного тока.

Амплитудный дифференциальный дискриминатор работает следующим образом.

Входной сигнал поступает на входную шину 1 и оба дискриминатора, а выходной сигнал появляется только в случае, если срабатывает дискриминатор 2 нижнего уровня и не срабатывает дискриминатор 3 верхнего уровня, т.е. импульс попадает в окно. При этом сигнал проходит по цепи: дискриминатор 2 нижнего уровня, дополнительный триггер 4, формирователь 5, выходной логический элемент И 6. Если срабатывает дискримнатор 3 верхнего уровня, то он при помощи триггера 8 запрещает прохождение сигнала через выходной логический элемент И 6, причем сбрасывается задним фронтом этого сигнала в исходное состояние через логический элемент НЕ 9.

Импульс на дополнцтельном триггере 4, от заднего фронта которого генерируется выходной сигнал, формируется следующим образом. В исходном состоянии выходной транзис.тор логического элемента НЕ 0 находится в насыщенном состоянии и : напряжение на первом конденсаторе

блока 12 равно нулю. При срабатывании дискриминатора 2 нижнего уровня перебрасывается дополнительный триггер 4, его выходной транзистор запирается и указанный конденсатор начинает заряжаться входным током дополнительного элемента И II. Входной ток источника 14 зарядного тока не заряжает первый конденсатор блока 12, так как на второй его вход подается отпирающий сигнал непосредственно с дискриминатора 2 нижнего уровня. После ркончания импульса с дискриминатора 2 нижнего уровня ток заряда конденсатора

5 увеличится вдвое за счет включения входного тока источника 14 зарядг ного тока. Процесс заряда продолжается до тех пор, пока не будет достигнут порог срабатывания логичес0кого элемента И П, который сбрасывает дополнительны триггер 4 в исходное состояние и запускает формирователь 5.

Поскольку форма импульса в спект5рометрическом тракте около вершины симметрична, то изменение амплитуды входного сигнала в пределах ширины окна не приводит к сдвигу выходного сигнала. Регулировка задержки выходного сигнала осуществляется дискретно при помощи подключения дополнительных конденсаторов блока 2 через переключатель 13 и плавно при помощи сдвоенного регулирующего генератора 15 тока, который отбирает часть вход}1ых токов логического элемента И 11 и источника 14 зарядного тока, не нарушая их равенства. Равенство входных токов логического элемента И 11 и источника 14 зарядного тока обеспечивается выполнением этих схем на интегральной технологии на одном кристалле.

| название | год | авторы | номер документа |

|---|---|---|---|

| Линейный преобразователь импульсных сигналов по длительности | 1983 |

|

SU1149392A1 |

| Времяимпульсный амплитудный преобразователь | 1986 |

|

SU1435131A1 |

| СЧЕТЧИК ЭЛЕКТРИЧЕСКОЙ ЭНЕРГИИ | 2001 |

|

RU2190860C2 |

| Устройство временной привязки | 1987 |

|

SU1465973A1 |

| Генератор пилообразного напряжения | 1988 |

|

SU1615865A1 |

| Преобразователь длительности фронта импульса в амплитуду | 1988 |

|

SU1557672A1 |

| Преобразователь амплитуд импульсов в цифровой код | 1976 |

|

SU605316A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1988 |

|

SU1594699A1 |

| МАЛОГАБАРИТНЫЙ ШИРОТНО-ИМПУЛЬСНЫЙ МОДУЛЯТОР, УСТОЙЧИВЫЙ К ВОЗДЕЙСТВИЮ ИОНИЗИРУЮЩИМ ИЗЛУЧЕНИЕМ | 2013 |

|

RU2557479C2 |

| ПИКОВЫЙ ДЕТЕКТОР | 2012 |

|

RU2506598C1 |

А П1ПИТУДНЫЙ ДИФФЕРЕНЦ11АЛЬНЫЙ ДИСКРИМИНАТОР для спектрометрического анализатора, содержащий дискриминаторы анализатора, содержащий дискриминаторы верхнего и нижнего уровней, входы которых соединены с входной пшной, триггер, первый вход которого соединен с выходом дискриминатора верхнего уровня, а второй вход через логический элемент НЕ соединен с выходом формирователя импульсов и первым входов выходного логического элемента И, второй вход которого подключен к выходу триггера, отличающийся тем, что, с целью повышения точности временной привязки выходного сигнала, в него введены дополнительньш триггер RS-типа, дополнительные логические элементы НЕ и И, генератор тока, блок конденсаторов с переключателем и источник зарядного тока, первьш выход которого соединен с первым входом дополнительного логического элемента И, выходом дополнительного логического элемента НЕ и точкой соединения конденсаторов бло.ка конденсаторов, вторая обкладка одного из которых соединена с общей шиной непосредственно, а вторые обкладки остальных конденсаторов соединены с общей шиной через переключатель, причем выходы генератора С S тока соединены с вторым входом дополнительного логического элемента И (Л и первьш входом источника зарядного тока, второй вход которого соединен с вькодом дискриминатора нижнего уровня и R-входом дополнительного триггера, RS-типа, S-вход которого подключен к выходу дополнительного о логического элемента И, третий вход со которого подключен к одному выходу п1 дополнительного триггера RS-типа, со второй выход которого соединен с входом дополнительного логического элемента НЕ и входом формирователя импульсов.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Анализатор амплитуды импульсов | 1973 |

|

SU558229A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Bernard Р | |||

| and others | |||

| Joum | |||

| TJnstrum and Methods, V | |||

| Способ получения смеси хлоргидратов опийных алкалоидов (пантопона) из опийных вытяжек с любым содержанием морфия | 1921 |

|

SU68A1 |

Авторы

Даты

1984-05-07—Публикация

1978-04-21—Подача