Изобретение относится к контрольно-измерительной технике и может быть использовано в качестве вторичного преобразователя для датчиков с широтно-импульсным выходом, а также в схемах прямого сравнения двух или многих временных интервалов малой длительности, представленных длительностями импульсов напряжения.

Известно устройство преобразования импульсных сигналов по длительности, содержащее накопительный элемент, дискриминатор и зарядно-разрядную цепь, переключаемую входным импульсом. В качестве накопительного элемента используется диффузионная емкость транзистора 1.

Недостатком этого устройства является принципиальная невозможность обеспечения широкого диапазона преобразования вследствие малого времени жизни неосновных носителей заряда в базе транзистора. Малый динамический диапазон преобразования, малый коэффициент преобразования и невысокая надежность обусловлены также нелинейностью процессов рекомбинации и их температурной нестабильностью.

Наиболее близким к изобретению по технической сущности является линейный преобразователь импульсных сигналов по длительности, содержащий разрядный и зарядный источники тока, выходы которых соединень с первой обкладкой накопительного конденсатора, управляющий вход разрядного источника тока, величина которого больще зарядного тока, соединен с входной шиной, и дискриминатор, вход которого соединен с первой обкладкой накопительного конденсатора, вторая обкладка накопительного конденсатора соединена с щиной нулевого потенциала 2.

Недостатком известного устройства является низкая стабильность преобразования, вызванная флуктуациями на начальном участке преобразования и шунтированием накопительного конденсатора входным сопротивлением дискриминатора.

Целью изобретения является повышение стабильности преобразования.

Поставленная цель достигается тем, что в линейный преобразователь импульсных сигналов по длительности, содержащий разрядный и зарядный источники тока, выходы которых соединены с первой обкладкой накопительного конденсатора, управляющий вход разрядного источника тока, величина которого больше зарядного тока, соединен с входной щиной, и дискриминатор, введены цепь задержки и выходной RS-триггер, причем входная щина через элемент задержки соединена с входом установки выходного RS-триггера, а вторая обкладка накопительного конденсатора через дискриминатор соединена с входом сброса выходного RS-триггера.

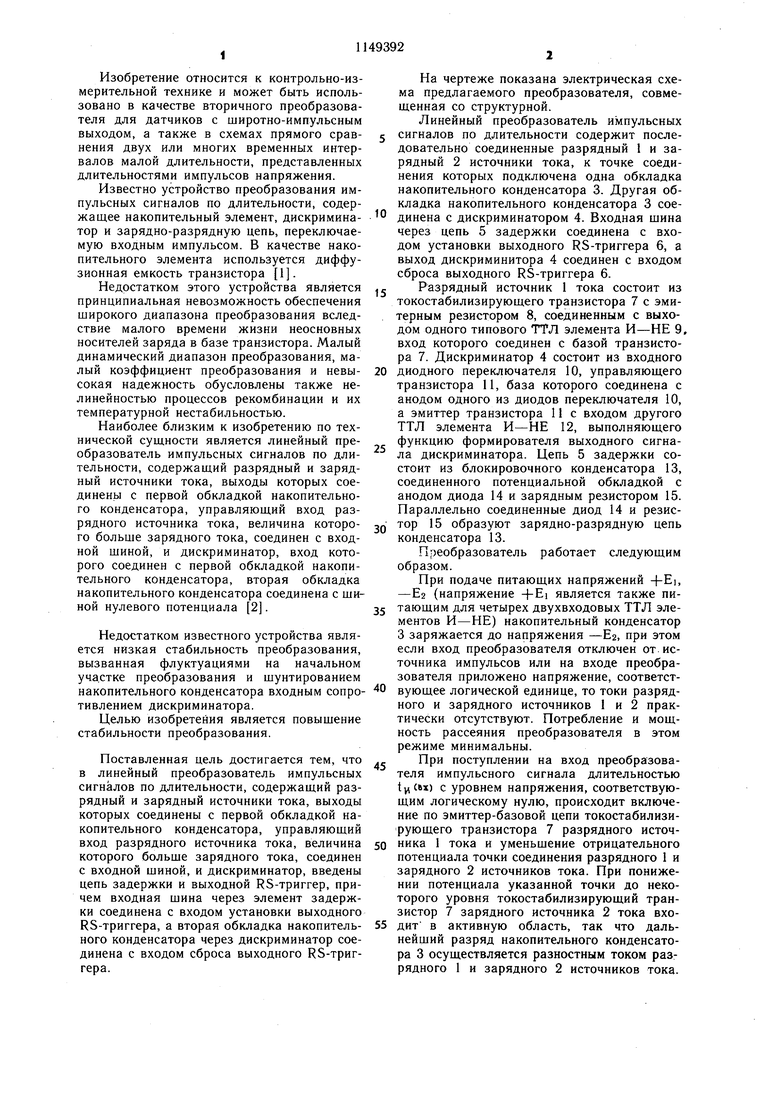

На чертеже показана электрическая схема предлагаемого преобразователя, совмещенная со структурной.

Линейный преобразователь импульсных

сигналов по длительности содержит последовательно соединенные разрядный 1 и зарядный 2 источники тока, к точке соединения которых подключена одна обкладка накопительного конденсатора 3. Другая обкладка накопительного конденсатора 3 соединена с дискриминатором 4. Входная щина через цепь 5 задержки соединена с входом установки выходного RS-триггера 6, а выход дискриминитора 4 соединен с входом сброса выходного RS-триггера 6.

j Разрядный источник 1 тока состоит из токостабилизирующего транзистора 7 с эмитерным резистором 8, соединенным с выходом одного типового ТТЛ элемента И-НЕ 9. вход которого соединен с базой транзистора 7. Дискриминатор 4 состоит из входного

0 диодного переключателя 10, управляющего транзистора 11, база которого соединена с анодом одного из диодов переключателя 10, а эмиттер транзистора 11 с входом другого ТТЛ элемента И-НЕ 12, выполняющего функцию формирователя выходного сигнала дискриминатора. Цепь 5 задержки состоит из блокировочного конденсатора 13, соединенного потенциальной обкладкой с анодом диода 14 и зарядным резистором 15. Параллельно соединенные диод 14 и резисQ тор 15 образуют зарядно-разрядную цепь конденсатора 13.

Преобразователь работает следующим образом.

При подаче питающих напряжений +Ei, -Е2 (напряжение +Ei является также питающим для четырех двухвходовых ТТЛ элементов И-НЕ) накопительный конденсатор 3 заряжается до напряжения -Ег, при этом если вход преобразователя отключен от источника импульсов или на входе преобразователя приложено напряжение, соответствующее логической единице, то токи разрядного и зарядного источников 1 и 2 практически отсутствуют. Потребление и мощность рассеяния преобразователя в этом режиме минимальны.

г При поступлении на вход преобразователя импульсного сигнала длительностью ty(CBx) с уровнем напряжения, соответствующим логическому нулю, происходит включение по эмиттер-базовой цепи токостабилизирующего транзистора 7 разрядного источника 1 тока и уменьшение отрицательного потенциала точки соединения разрядного 1 и зарядного 2 источников тока. При понижении потенциала указанной точки до некоторого уровня токостабилизирующий транзистор 7 зарядного источника 2 тока вхо5 дит в активную область, так что дальнейший разряд накопительного конденсатора 3 осуществляется разностным током разрядного 1 и зарядного 2 источников тока.

Разрядный ток является большим в том смысле, что меньший зарядный ток имеет величину порядка одного процента от уровня разрядного тока. Одновременно с началом разряда накопительного конденсатора 3 происходит разряд блокирующего конденсатора 13 в цепи 5 задержки на источник входного импульса и переключение выходного RS-триггера 6 в состояние логической единицы по выходу преобразователя. После окончания действия входного импульса начинается переходной процесс отсечки тока разряда накопительного конденсатора 3 и по окончании этого процесса накопительный конденсатор 3 начинает заряжаться относительно малым током через зарядный токостабилизирующий источник 2 тока. Ток заряда накопительного конденсатора 3, протекая через входной диодный переключатель 10 дискриминатора 4, открывает управляющий транзистор 11 дискриминатора 4, обеспечивая на выходе дискриминатора 4 уровень напряжения логической единицы на время заряда накопительного конденсатора 3 до исходного уровня напряжения.

На время переходного процесса отсечки тока разряда накопительного конденсатора 3 на выходе дискриминатора 4 отсутствует

уровень напряжения логической единицы, необходимый для надежного удержания выходного RS-триггера 6 в переключенном состоянии, поэтому на вход S указанного триггера 6 с выхода цепи задержки после окончания действия входного импульса продолжает поступать условный уровень напряжения логического нуля, иммитирующий последействие входного импульса на время большее, чем время упомянутого переходного процесса отсечки тока разряда. Время окончания заряда накопительного конденсатора 3 фиксируется переходом выходного сигнала дискриминатора 4 с уровня напряжения логической единицы на уровень напряжения логического нуля, что приводит к переключению выходного RS-триггера 6 в исходное состояние и формированию заднего фронта выходного импульса длительностью 1ц(ы,1х.

Таким образом, за счет введения задержки переключения выходного RS-триггера удается уменьшить влияния начального участка преобразования, а соединение дискриминатора с второй обкладкой накопительного конденсатора исключает его разряд через параллельное входное сопротивление дискриминатора, что в конечном итоге позволяет повысить стабильность преобразования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь временного интервала в напряжение | 1983 |

|

SU1109898A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU832601A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНТЕРВАЛОВ ВРЕМЕНИ МЕЖДУ ДВУМЯ ИМПУЛЬСАМИ | 1969 |

|

SU249783A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU771729A1 |

| Устройство для зарядки емкостного накопителя | 1989 |

|

SU1780150A1 |

| Стабилизированный импульсный преобразователь переменного напряжения | 1982 |

|

SU1026260A1 |

| Преобразователь переменного напряжения в постоянное | 1987 |

|

SU1422331A1 |

| ЗАРЯДНОЕ УСТРОЙСТВО ЕМКОСТНОГО НАКОПИТЕЛЯ ЭНЕРГИИ | 2015 |

|

RU2601437C1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНТЕРВАЛОВ ВРЕМЕНИ МЕЖДУ ДВУМЯ | 1973 |

|

SU365026A1 |

| Стабилизатор импульсного напряжения | 1982 |

|

SU1040478A1 |

ЛИНЕЙНЫЙ ПРЕОБРАЗОВАТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ ПО ДЛИТЕЛЬНОСТИ, содержащий разрядный и зарядный источники тока, выходы которых соединены с первой обкладкой накопительного конденсатора, управляющий вход разрядного источника тока, величина которого больше зарядного тока, соединен с входной шиной, и дискриминатор, отличающийся тем, что, с целью повышения стабильности преобразования, в него введены цепь задержки и выходной RS-триггер, причем входная шина через элемент задержки соединена с входом установки выходного RS-триггера, а вторая обкладка накопительного конденсатора через дискриминатор соединена с входом сброса выходного RS-триггера. (Л 4: СО СО СО to f fSb/jf) Н

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО для ИЗМЕРЕНИЯ ДЛИТЕЛЬНОСТИ ФРОНТОВ ИМПУЛЬСОВ и ИНТЕРВАЛОВ ВРЕМЕНИ | 0 |

|

SU166757A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| УСТРОЙСТВО ДЛЯ ТРАНСФОРМАЦИИ ДЛИТЕЛЬНОСТИ ПРЯМОУГОЛЬНЫХ ИМПУЛЬСОВ | 0 |

|

SU206637A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-04-07—Публикация

1983-01-26—Подача