вым входом третьего элемента И, выход пятого детектора - с вторым входом второго элемента И, вькод пятого компаратора - с вторыми входами первого я третьего элементов И, вькод третьего элемента И с третьим входом элемента HJM, выход которого соедирген через последовательно включенные третий, второй и первый компараторы с первым входом распределителя, второй вход которого подключен к выходу первого регистра сдвига, а третий вход - к выходу триггера упраления, притрем вход первого регистра сдвига является первым входом блока селекции страниц, вход триггера управления - вторым входом, вход второго регистра сдвига, - третьим входом, а первьй и второй выходы распре делителя - соответственно первым и вторым выходами блока с&пекции страниц .

3. Система по п. 1, отличающаяся тем, что корректор сигнала ошибки состоит из регистра сдвига на элементах памяти, распре:делителя на элементах памяти, решающего устройства, детектора и блоков ввода информации, причем детектор, первый элемент памяти регистра сдвига, первый элемент памяти распределителя, второй элемент памяти регистра сдвига, второй элемент памяти распределителя, третий элемент памяти регистра сдвига, третий элемент

памяти распределителя и четвертый элемент памяти регистра сдвига соединены последовательно, выходы первых трех элементов памяти регистра сдвига соединены с входами соответствующих компараторов, выходы которых подклют тены к входам решающего устройства, первый выход которого подключен к первому входу первого блока ввода информации, второй вход которого объединен с первым входом второго блока ввода информации и соединен с выходом второго элемента памяти регистра сдвига, а выход - с другим входом первого элемента памяти распределителя, второй выход решающего устройства подключен к второму входу второго блока ввода информации, выход которого соединен с другим входом второго элемента памяти распределителя, а третий выход решаю1цего устройства - с тлравляюи им входом третьего элемента памяти рас- пределителя и с первым входом третьего блока ввода информации, второй вход которого подключен к выходу четвертого элемента памяти регистра сдвига, а выход - к другому входу третьего элемента памяти распределителя, причем вход детектора является входом корректора сигнала ошибки, выход регистра сдвига - первь:м выходом, а четвертый выход решающего устройства вторым выходом корректора сигнала ошибки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для перекодирования видеографических матриц 12 @ 10 в матрицы 8 @ 10 | 1983 |

|

SU1479015A3 |

| Телевизионная система | 1981 |

|

SU1306492A3 |

| Система асинхронной двусторонней передачи данных между передающей и приемной станциями | 1983 |

|

SU1521297A3 |

| Устройство воспроизведения текстовых и графических знаков на экране электронно-лучевой трубки (элт) | 1979 |

|

SU1012809A3 |

| Система видеотекста | 1980 |

|

SU1172456A3 |

| Устройство для отображения телетекста на экране телевизионного приемника | 1980 |

|

SU1181568A3 |

| Устройство для оценки контура изображения | 1981 |

|

SU1076002A3 |

| Генератор кодирующих или декодирующих байтов | 1983 |

|

SU1207407A3 |

| Устройство для формирования адресных сигналов | 1980 |

|

SU1048996A3 |

| Устройство для отображенияТЕКСТОВОй иНфОРМАции HA эКРАНЕэлТ | 1977 |

|

SU828989A3 |

1. СИСТЕМА ПЕРЕДАЧИ И ВОСПРОИЗВЕДЕНИЯ ИНФОРМА1ШИ, содержащая на передающей стороне последовательно включ.енные пульпы управления, блок обработки цифровой информации, мультиплексор и модулятор, а на приемной стороне демодулятор, первый выход которого подключен через блок обработки видеосигнала, к одному входу видеоконтрольного блока, а другой выход через блок обработки цифрового сигнала - к другому входу видеоконтрольного блока, при этом блок обработки цифрового сигнала на приемной стороне состоит из последовательно соединенных разделителя видеосигнала, вход которого является входом блока обработки цифрового сигнала, селектора и интерфейса, из последовательно соединенных дешифратора, блока памяти страниц и генератора знака, выходы которого являются выходом блока обработки цифрового сигнала, отличающаяся тем, что, с целью повышения достоверности передачи информации, на приемной стороне в блок обработки цифрового сигнала введены блок селекции страниц, корректор сигнала ошибки и устройство блокировки сигнала ошибки, причем первый вход блока селекции страниц подключен к выходу интерфейса, первый вькод - к входу корректора сигнала ошибки, первьй выход которого соединен с вторым входом блока селекции страниц, а второй выход - с входом устройства блокировки сигнала ошибки, выход которого объединен с вторым входом корректора сигнала ошибки и подключен к входу деиифратора, другой выход которого соединен с третьим входом блока селекции страниц. 2. Система поп.1, отличаюG S щаяся тем, что блок селекции страниц с остоит из двух регистров сдвига на триггерах, памяти компараС торов, пяти детекторов, триггера управления, распределителя, трех ;элементов И и элемента PiJlH, причем выходы трех первых триггеров первого регистра сдвига через соответсто со вующие детекторы подключены к первым входам трех соответствующих компараторов, вторые входы которых соеди00 нены с выходами соответствующих 05 триггеров второго регистра сдвига, to выход четвертого триггера первого регистра сдвига соединен с входом четвертого компаратора и с входом четвертого детектора, выход пятого триггера первого регистра сдвига с входом пятого компаратора и с входом пятого детектора, выход четвертого клмпаратора соединен с первыми входами первого и второго элементов И, выходы которых подключены к двум входам элемента ИЛИ, выход четвертого детектора соединен с пер

1

Изобретение относится к передаче и индикации информации в приемной апгшратуре телевидения.

Известна система передачи и воспроизведения информации, содержащая на передающей стороне последовательно включенные пульты управления, блок обработки цифровой информаш-и, интерфейс, мультиплексор и модулятор, а на приемной стороне - демодулятор, . первый выход которого подключен через блок обработки видеосигнапа к входу видеоконтрольного блока, а другой выход через блок обработки цифрового сигнала - к другому входу

видеоконтрольного блока, при этом блок обработки цифрового сигнала на приемной стороне состоит из последовательно соединенных разделителя видеосигнала, вход которого является входом блока обработки ;р1фрового сигнала, селектора, интерфейса, дешифратора, блока памяти страниц и генератора знака, вькоды которого являются выходом блор;а обработки цифрового сигнала.

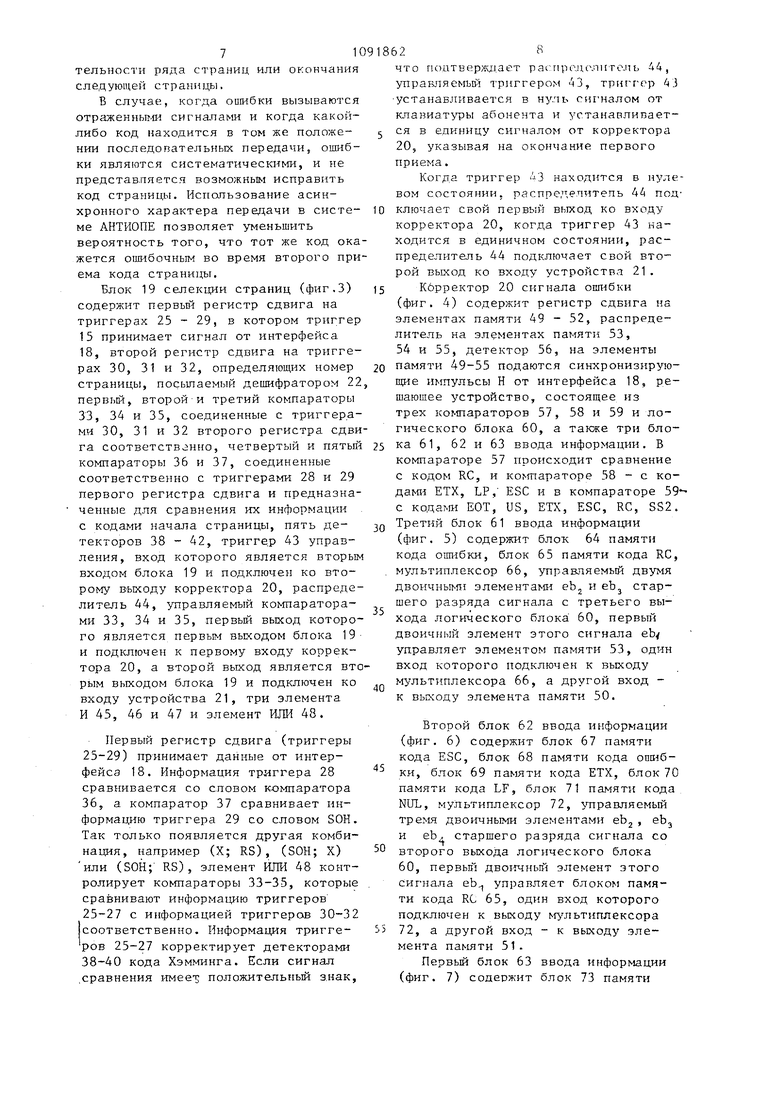

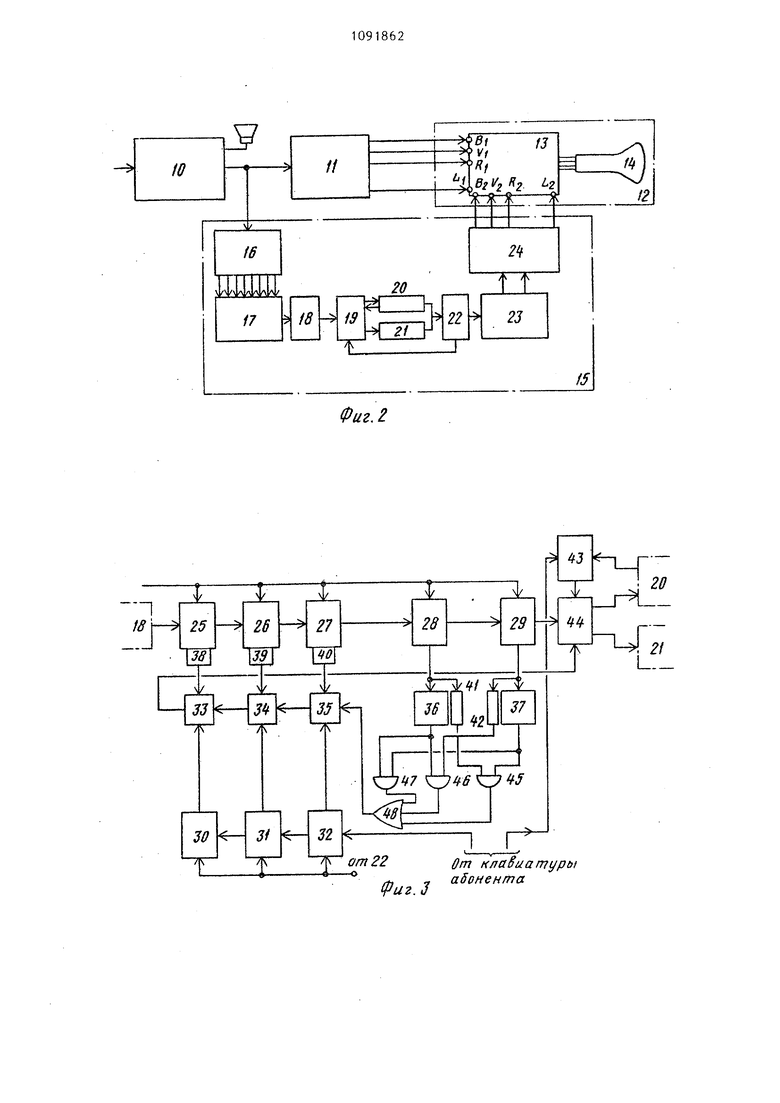

Однако известная система не обеспечивает достоверности передачи информации . Цель изобретения - повышение достоверности передачи информации. I Поставленная пель достигается тем что в систему передачи и воспроизведения информации, содержащую на пере дающей стороне последовательно включенные пульты уттравпеиия, блок обработки цифровой информации, мультиплексор и модулятор, а на приемной стороне демодулятор, первый выход которого подключен через блок обработки видеосигнала к одному входу видеоконтрольного блока, а другой выход через блок обработки цифрового сигнала - к другому входу видеоконтрольного блока, при этом блок обработки цифрового сигнала на приемной стороне состоит из последовательно соединенных разделителя видеосигнала вход которого является входом блока обработки цифрового сигнала, селектора и интерфейса, из последовательно соединенных дешифратора,блока памяти страниц и генератора знака, выходы которого являются выходом блока обработки цифрового сигнала, на приемной стороне в блок обработки цифрового сигнала введены блок селекции страниц, корректор сигнала ошибки и устройство блокировки сигнала ошибки, причем первый вход блок селекции страниц подютючен к выходу интерфейса, первый выход - к входу корректора сигнала ошибки, первый выход которого соединен с вторым входом блока селекции страниц, а вто рой выход - с входом устройства блок ровки сигнала оишбки, выход которого объединен со вторым входом корректор сигнала ошибки и подключен ко входу дешифратора, другой.выход которого соединен с третьим входом блока селе ции страниц, блок селекции страниц состоит из двух регистров сдвига на триггерах, пяти компараторов, пяти детекторов, триггера управления, рас пределителя, трех элементов И и элемента ИЛИ, причем выходы трех первых триггеров первого регистра сдвига через соответствующие детекторы подключены к первым входам трех соответствующих компараторов, вторые вх:оды которых соединены с выходами соответствующих триггеров второго ре гистра сдвига, выход четвертого триг гера первого регистра сдвига соединен с входом четвертого компаратора и с входом чет:вертого детектора, выхсхц пятого триггера ncpooio регистра сдвига - с входом пятого KoMiiapnтора и с входом пятого детектора, ныход четвертого компаратора соодипси с nepBHNfn входами первого и второго элементов И, выходы которых подк.пючены к двум входам элемента ИЛИ, выход четвертого детектора сое,динен с первъпч входом третьего элемента И, выход пятого детектора - с вторым входом второго элеме гта И, выход пятого компаратора - с вторыми входами первого и третьего элементов И, выход третьего элемента И - с третьим входo i элемента ИЛИ, выход которого соединен через последовательно вкпюченные третий, второй и первый компараторы с пep. входом распределителя, второй вход которого подключен к выходу первого регистра сдвига, а третий вход - к выходу триггера управления, причем вход первого регистра сдвига является первым входом блока селекции страниц, вход триггера управления - вторым входом, вход второго регистра сдвига - третьим входом, а первый и второй выходы распределителя - соответственно первым и вторым выходами блока селекции :страниц. 1 Причем корректор сигнала ошибки состоит из регистра сдвига на элементах памяти, распределителя на элементах памяти, решающего устройства, детектора и блоков ввода информации, причем детектор, первый элемент памяти регистра сдвига, первый элемент памяти распределителя, второй элемент памяти регистра сдвига, второй элемент памяти распределителя, третий элемент памяти регистра сдвига, третий элемент памяти распpeдeл iтeля и четвертый элемент памяти регистра сдвига соединены последовательно, выходы первых трех элементов памяти регистра сдвига соединены с входами соответствующих компараторов, выходы которых подключены ко входам решающего устройства, первьй вькод которого подкл очен к первому входу первого блока ввода информации, второй вход которого обьединеь с первым входом второго блока ввода ин | ормапии и соединен с выходом второго элемента памяти регистра сдвига, а выход - с другим входом первого элемента памяти распределителя, второй выход peiii;Houieго устроиства подключен ко второму входу второго блока ввода информации, выход которого соединен с друг входом второго элемента памяти распределителя, а третий выход решающе го устройства - с управллю1цим входо третьего элемента памяти распределителя и с первым входом третьего блока ввода информации, второй вход которого подклнтчен к выходу четвертого элемента памяти регистра сдви а выход - к другому входу третьего элемента памяти распределителя, при чем вход детектора является входом корректора сигнала ошибки, выход ре гистра сдви1 а первым выходом, а четвертый.выход решающего устройства - вторым выходом корректора сигн ла ошибки. На фиг. 1 предстанпена структурная электрическая схема передающей стороны системы передачи и воспроизведения информации; на фиг. 2 то же, приемной стороны системы передачи и воспроизведения информации.; на фиг. 3 - то же, блока селек дии страниц; на фиг. 4 - то же, корректора сигнала оцотбки; на фиг.5 то же, пергзого блока ввода информа1щи на фиг. 6 - то же, второго блока ввода информагщи; на . 7 то же, третьего блока ввода информации; на фиг. 8 - то же, логического блока; на фиг. 9 - то же, устройства блокировки сигнала ошибк Система передачи и воспроизведе,НИЛ информации содержит на передаю|щей стороне (фиг-. 1) пульты управления (1-1)-(1-п), кажд.ый из которых состоит из контрольного экрана (2-1)-(2-п) и клавиатуры (3-1)(3-п), блок 4 обработки цифровой информации состоит из блока 5 установки формата страницы документа, блока 6 памяти и преобразозатепя 7. Выход блока 4 подключен через мультиплексор 8 по входу модулятора 9, выход которого является выходом при емной стороны. Пульты управления (1-1)-(1-п) позволяют оператору наб рать страницы, проверяя на контроль ном экране характеристики известног изображения: размер символов, мигание, различные графические особенности. Каждая клавиатура 3-i (,2 ,..,п) представляет собой тип пишущей машинки и предназначена для набора и приведения в соответствуюгций порядок документов. Блок 5 формируе 26 via6biTo4HbiC: последовательности кодов, а блок 6 памяти хранит длительности передаваемых кодов, которые периодически считываются и передаются через мультиплексор 8 на вход модулятора 9 для передачи. На приемной стороне (фиг.. 2) система содержит демодулятор 10, блок 11 обработки видеосигнала, представляюищй собой, например, депшфратор цвета и генератор развертки, видеоконтрольный блок 12, состоящей из видеоком - утатора 13 и электроннолучевой трубки (ЭЛТ) 14, а также блок 15 обработки цифрового сигнала, состоящий из разделителя 16 видеосиг нала, селектора 17, интерфейса 18, блока 19 селекции страниц, корректора 20 сигнала о т-1бки, устройства 21 блокиров си сигнала ошибки, дешифратора 22, блока 23 памяти страниц и генератора 24 знака. Демодулятор 10 подает звук на громкоговоритель и видеосигнал на блок 11, который передает цветовые видеосигналы В-,, V., и R, а также сигнал яркости L через видеокоммутатор 13 на ЭЛТ 14. В блоке 15 выходы генератора 24 соединены со входами цветности R, V и В и входом яркости Lj видеоком {утатора 13. Селектор 17 выбирает цифровой канал и представляет возможность цроходить полезному сообщению по их номеру канала. Выборка страниц и декодирование выбранных страниц происходит в дешифраторе 22, который декодирует страницу за страницей и заполняет блок 23 памяти страниц. Блок 19 селекции страниц предназначен для распознавания кодов заголовка страниц и номера страницы и подключает свой первый выход ко входу корректора 20 во время первого приема одной страницы и второй выход ко входу устройства 21 во время последутотцих приемов. Корректор 20 сигнала ошибки корректирует ошибочные коды и подает сР1гналы об ошибочных, но не исправленных кодах, а также распознает код окончания страницы, во время которого со своего второго выхода подает сигнал на второй вход блока 19 об окончании страницы. Устройство 21 последовательно устраняет ошибки, сугиествугоише в странице после тгервого ее приема, блокируя любую передачу информации в случае наличия о1иибки г; последовательносли ряда страниц или окончания следующей страницы.

В случае, когда ошибки вызываются отраженньп-ш сигнапами и когда какойлибо код находится в том же положеНИИ поеледопетельных передачи, ошибки являются систематическими, и не представляется возможным исправить код страницы. Испаяьзование асинхронного характера передачи в системе АНТИОПЕ позволяет уменьшить вероятность того, что тот же код окажется ошибочным во время второго приема кода страницы.

Блок 19 селекции страниц (фиг.З) содержит первьв регистр сдвига на триггерах 25-29, в котором триггер 15 принимает сигнал от интерфейса 18, второй регистр сдвига на триггерах 30, 31 и 32, определяющих номер страницы, посылаемый дешифратором 22 первый, второй и третий компараторы 33, 34 и 35, соединенные с триггерами 30, 31 и 32 второго регистра сдвига соответственно, четвертый и пятът компараторы 36 и 37, соединенные соответственно с триггерами 28 и 29 первого регистра сдвига и предназначенные для сравнения их информации с кодами начала страницы, пять детекторов 38 - 42, триггер 43 управления, вход которого является вторым входом блока 19 и подключен ко второму выходу корректора 20, распределитель 44, управляемый компараторами 33, 34 и 35, первый выход которого является первым выходом блока 19 и подключен к первому входу корректора 20, а второй выход является вторым выходом блока 19 и подключен ко входу устройства 21, три элемента И 45, 46 и 47 и элемент ИЛИ 48.

Первый регистр сдвига (триггеры 25-29) принимает данные от интерфейса 18. Информация триггера 28 сравнивается со словом компаратора 36, а компаратор 37 сравнивает информацию триггера 29 со словом SOH. Так только появляется другая комбинация, например (X; RS), (ЗОН; X) или (SOH; RS) , элемент ИЛИ 48 контролирует компараторы 33-35, которые сравнивают информацию триггеров 25-27 с информацией триггеров 30-32 соответственно. Информация триггеров 25-27 корректирует детекторами 38-40 кода Хэмминга. Если сигнал ,сравнения имеет; положительный з.нак.

что подтверждает рас працсяигсль 44, управляемы триггером 43, трщ-г-ор 4J устанавливается в нуль сигналом от клавиатуры абонента и устанавливается в единицу cигнaлo f от корректора 20, указывая на окончание первого приема.

Когда триггер находится в нулевом состоянии, распределитель 44 подключает свой первый выход ко входу корректора 20, когда триггер 43 находится в единичном состоянии, распределитель 44 подключает свой второй выход ко входу устройства 21 .

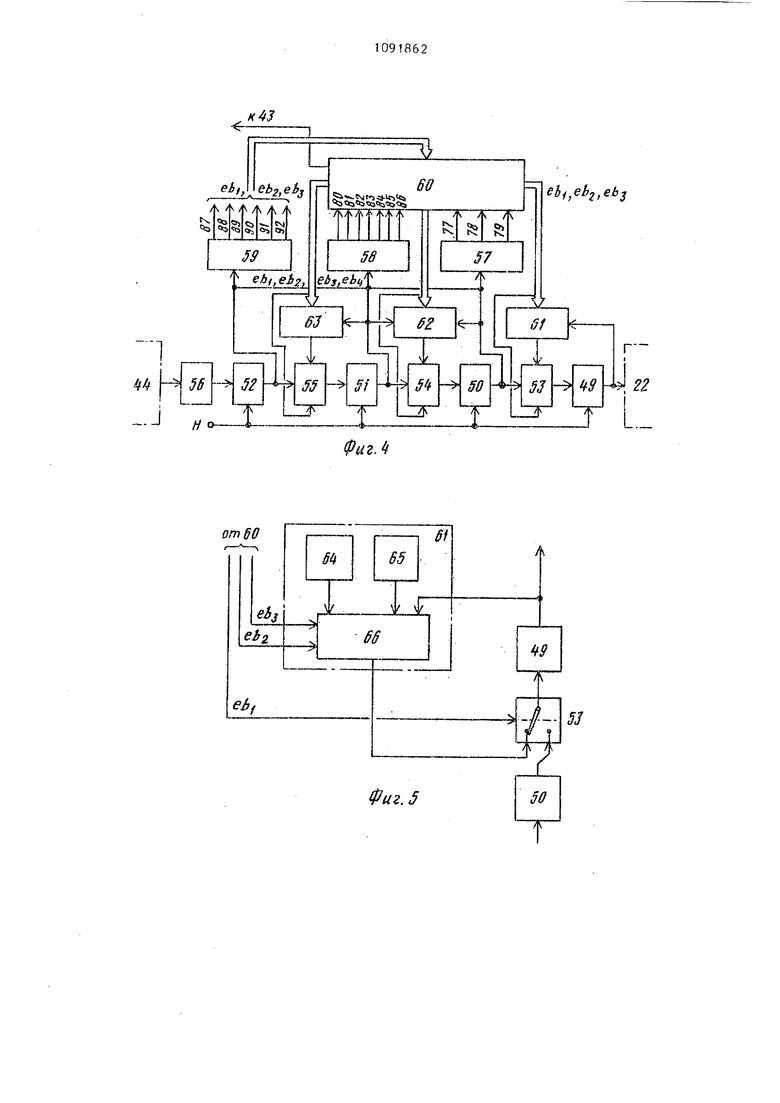

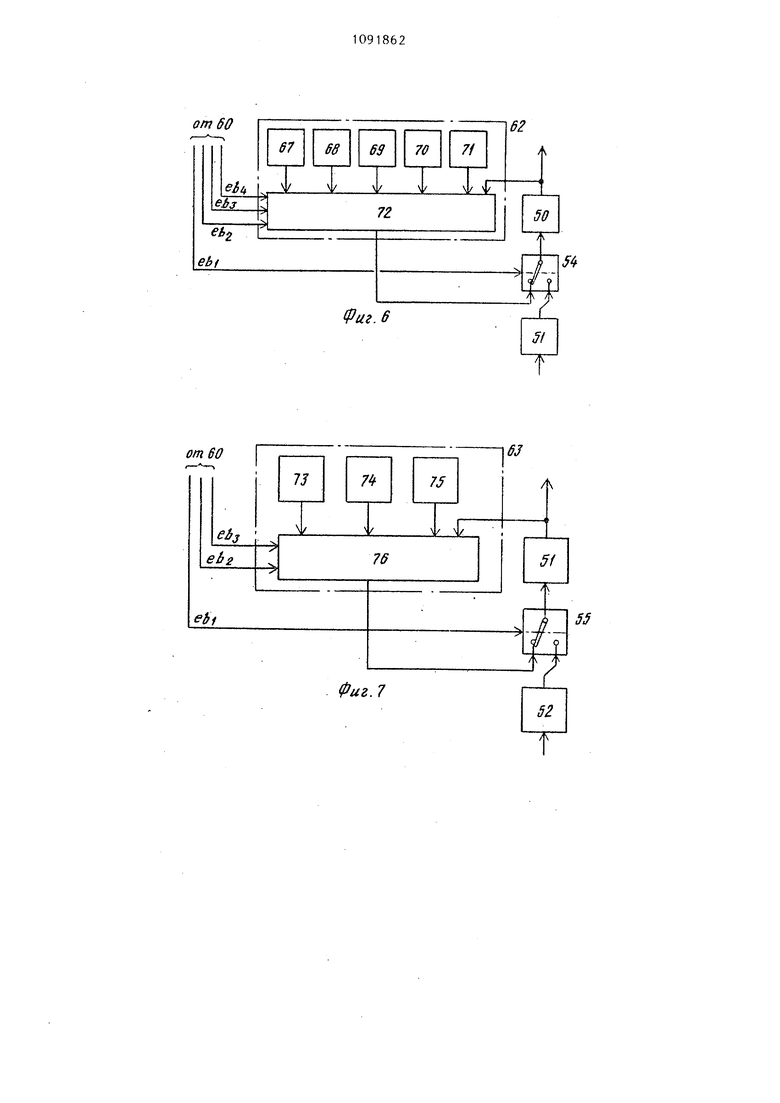

Корректор 20 сигнала ошибки (фиг. 4) содержит регистр сдвига на элементах памяти 49 - 52, распределитель на элементах памяти 53, 54 и 55, детектор 56, на элементы памяти 49-55 подаются синхронизирующие импульсы Н от интерфейса 18, решающее устройство, состоящее из трех KONmapaTOpoB 57, 58 и 59 и логического блока 60, а также три блока 6 1 , 62 и 63 ввода информации. В компараторе 57 происходит сравнение с кодом RC, и кo mapaтope 58 - с кодами ЕТХ, LP, ESC и в компараторе 59с кодами EOT, US, ЕТХ, ESC, RC, SS2 Третий блок 61 ввода информации (фиг. 5) содержит блок 64 памяти кода ошибки, блок 65 памяти кода RC, мультиплексор 66, управляемый двумя двоичными элементами еЬ и ebj старшего разряда сигнала с третьего выхода логического блока 60, первый двоичный элемент этого сигнала еЬ управляет элементом памяти 53, один вход которого подключен к выходу мультиплексора 66, а другой вход к выходу элемента памяти 50.

Второй блок 62 ввода информации (фиг. 6) содержит блок 67 памяти кода ESC, блок 68 памяти кода опшбки, блок 69 памяти кода ЕТХ, блок 70 памяти кода LF, блок 71 памяти кода NUL, мультиплексор 72, 1,тгравляемый тремя двоичными элементами еЪ , ebj и еЬ, старшего разряда сигнала со второго выхода логического блока 60, первьш ДВО1ГЧНЫЙ элемент этого Сигнала еЬ управляет блоком памяти кода RC 65, один вход которого подключен к выходу ьтультиплексора 72, а другой вход - к выходу элемента памяти 51.

Первьм блок 63 ввода информации (фиг. 7) содержит блок 73 памяти кода EOT, блок 74 памяти кода US, блок 75 памяти кода NUL, мультиплексор 76, управляемый двумя двоичиыми элементами ebj и cbj старшепервый двоичньш го разряда сигнала, элемент еЬ которого управляет элементом памяти 55, один из входов которого гшдклюген к выходу мультиплексора 76, а второй вход - к выхо ду элемента памяти 52. Таким образом, сигнал с первого выхода блока 19 подается на вход детектора 56, который добавляет дво ичный, элемент к серии импульсов в элементах памяти 49-55. Элемент пам ти 49 записывает либо информацию элемента ггамяти 50,либо информацию б.шка 61,чтс- определяется элементом памяти 53. Информация э.пёментов памяти 50-5 контролируется компараторами 57-59 согласно табл, 1. Эти результаты обрабатываются логическим блоком 60 решающего устройства с тремя группа ми выходов. Первьп двоичный элемент сигнала с ;а)щого выхода обГ)Гчно пре ставляет нуль, в гзтом случае элементы памяти 53, 54, 55 находятся 3 таком cocTOfiHiiH, что элементы памяти 49-52 функционируют. В противном случае, например, если первый дпоичиый элемент равен единице, эле мент памяти 55 разрешает запись в элемент памяти 51 сигналов из блока 63 других двоичных элементов. Т а б л и ц а 1 Сравнение содержания элемента памяти 50 с со держанием элемента памя ти 51 с точностью доби Сравнепие с RC Бит недействительности Сравнепие с содержанием элементов памяти 49 или Сравнение с ЕТХ Сравнепие с LF Сравнение с ESC Сравнение с ESC с точ постью до бита Сравнение с нулем симв лов бит 6 и 7 1091862 10 Продолжение л. 5л , 1 87Бит недействительности 88Сравнение с I 7-го бита с О 6-го бита 89Сравнение с EOT 9С Сравнение с US 91Сравнение с содержанием элемента павдгти 51 с точностью до бита 92Сравнение с ЕТХ или ESC или RC или SS2 Компаратор 57 имеет выходы 77-79, компаратор 58 имеет выходы 80-86, а компаратор 59 имеет выходы 87-92, подключенные ко входам логического блока 60. Логика работы логического блока 60 представлена ниже. Сигналы на выходах 80, 85, 88, равные 1, со второго выхода в блок 67 памяти кода ESC; сигналы на выходах 80 и 88, равные 1, и 85, равный 0; а такл1:е сигналы на выходах 80 и 92, равные 1; или 83,, равный 1, и 77 или 87, равнь е нулю; или 81, равный 1, 77, равный нулю, а 91 подтверждают достоверность сигнала со второго выхода я блок 68 памяти кода ошибки. Последний случай подтверждает достоверность сигнала с первого выхода с адресом, соответствуга цр м содержанию элемента памяти 51. Сигналы на выходах 80 и 89, равные 1, подтверж,дак)Т достоверность сигнала со второго выхода в блок 69 памяти кода ЕТХ; сигналы на выходах 79, 80 и 90, равные 1, подтверждают достоверность сигнала с первого вькода в блок 70 памяти кода; сигналы на выходах 79, 80 и 87, равные 1, подтверясдают достоверность сигналов с первого и второго выходов соответственно в блок 70 памяти кода LF и в блок 74 памяти кода US; сигналы на выходах 77, 78 и 81, равные 1, подтверждают достоверность сигнала с третьего выхода с адресом, соответ;твую1цим содержанию памяти 51; сигналы на выходах 77 и 81, равные 1, но 78, равный , подтверждают достоверность сигнала с третьего выхода в блок 64 памяти кода ошибки сигналы на выходах 82 и 87, равные 1j подтверждают достоверность сигнала с первого выхода в блок 73 памяти кода EOT; сигнапы на выходах 77, 87 и 83 подтверждают достоверность сигналов с первого и третьего выходов соответственно в блок 65 памяти кода RC и в блок 74 памяти кода US. В то же время как 90, 83, равные 1, с 77, равным нулю, подтвер жают достоверность сигнала с третьего выхода в блок 65 памяти кода RC; сигналы на выходах 79 и 83, равные 1 подтверждают достоверность сигнала с первого выхода в блок 74 памяти кода US; сигналы на вькодах 79,равные 80, 83, 90, равные нулю, подтверждают достоверность сигнала с третьего выхода в блок 64 памяти кода ошибки; сигналы на выходах 87 и 84, равные 1, подтверждают достоверность сигналов с первого и второго выходов соот ветственно в блок 71 памяти кода NUL и в блок 75 памяти кода NUL. Код US, который следует за номером ряда в двух цифрах, ведет к тому, что логический блок 60 блокируется во время двух синхронизирующих интервалов счетчиком после детектирования сигнала с выхода 90, а сигна лы с выводов 89 или 82 вызывают пере ключение триггера 43 в нуль, указыва окончание приема страницы. Реализация логического блока 60 (фиг. 8), формирующего сигнал на первом выходе, представлена логическими элементами И 93-98, элементами ИЛИ 99, 100 и 101. Логика работы логического блока 60 представлена в табл. 2. Таблица 2

79 80 87

93

82 87

95 10

Сравнение содержания элемента памяти 103 с RS

Сравнение содержания элемента памяти 104 с LF

Сравнение содержания элемента памяти 105 с US

Бит недействительности байта;,

содержащегося в элементе памяти 103

Бит недействительности байта, содержащегося в элементе памяти 104

Бит недействительности байта, содержащегося в элементе памяти 105 табл. 2 ПрОДО.гТЖСПИс Сигналы со второго и третьего ыходов логического блока 60 формируются аналоптчным образом. Устройство 21 блокировки сигнала ошибки (фиг. 9) вьщеляет последовательности начала ряда RC, LP, US и блокирует любую передачу информации в случае ошибки, устройство содержит элементы памяти 102-105 регистра сдвига, элементы памяти 106, 107 и 108 распределителя, блоки 109, 110 и 111 ввода информации, решающее устройство из компараторов 112, 113 и 114 и логического блока 115 с триггером 116. Первый блок 111 содержит мультиплексор 117 и блок 118 второй блок 110 мультиплексор 1 19 и блок 120 памяти кода LF, третий блок 109 сопамяти кппя T.F. тоетий блок 109 держит мультиплексор 121, блок 122 памяти кода уплотнения NUL и блок 123 памяти кода RC. Логика работы представлена в табл. 3. Таблица 3 Операции

Логика работы логического блока 115 аналогична логике работы логического блока 60 и представлена в табл, 4. При этом компаратор 112 имеет выходы 124-126 компаратор 113 ifMEBT выходы 127-130 компаратор 114 HMeeV выходы 131-134, подключенные ко входам логического блока 115. Таблица4

120

LF

1 10

1

120

LF US -j

1 10

118 111

4

Продолжение таблг, 4

В логический блок 115 включен триггер 116, который подтверждает наличие сигнала с третьего выхода логического блока 115 в блок 122 памяти кода уплотнения.

Таким образом, в системе передачи и воспроизведения информации повышается достоверность передачи информации .

4

г. /

Фиг. г

ipuz.J

Iffy ..J

22

Фиг.

-/- 5J

Авторы

Даты

1984-05-07—Публикация

1981-01-15—Подача