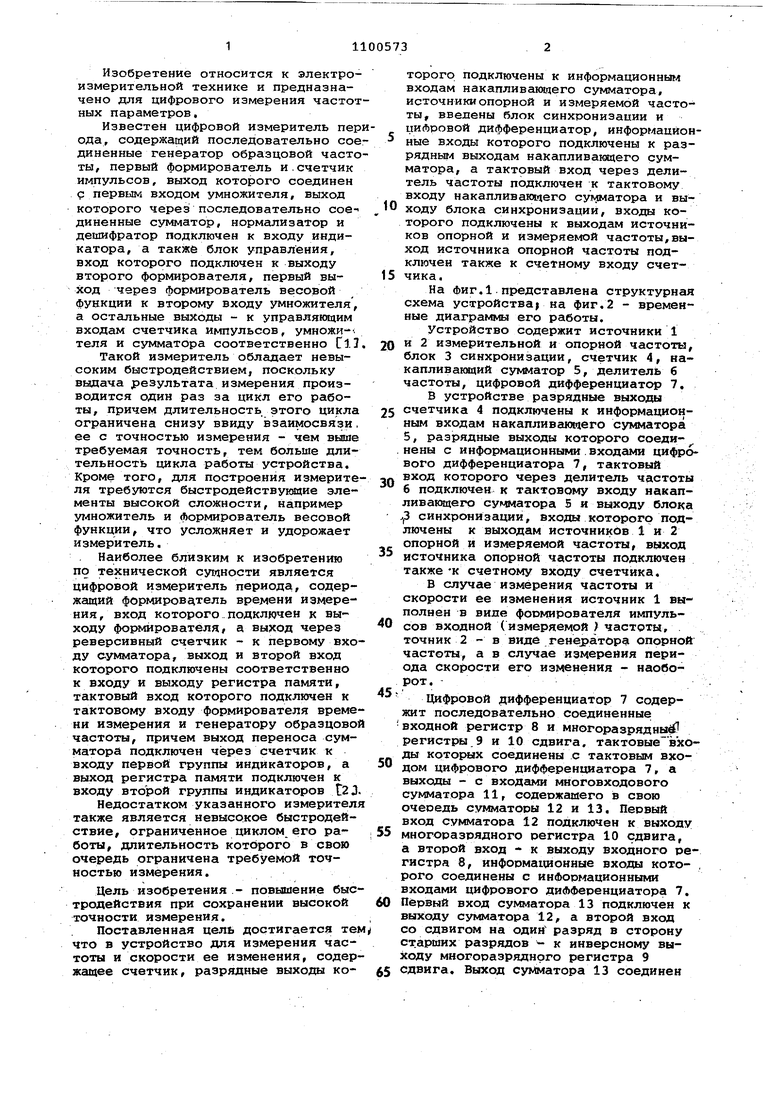

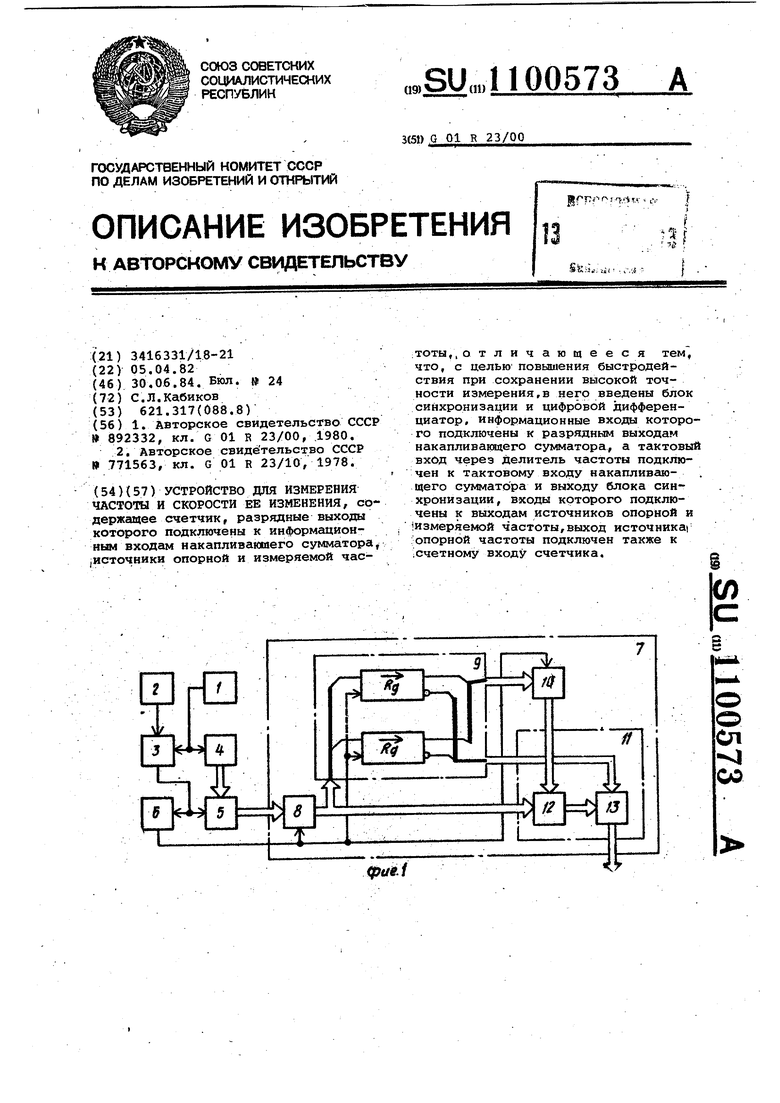

Изобретение относится к электроизмерительной технике и предназначено для цифрового измерения частот ных параметров. Известен цифровой измеритель пер ода, содержащий последовательно сое диненные генератор образцовой часто ты, первый формирователь и.счетчик импульсов, выход которого соединен (р перВЕЛм входом умножителя, выход которого через последовательно соединенные сумматор, нормализатор и дешифратор подключен к входу индикатора, а также блок управления, вход которого подключен к выходу второго формирователя, первый выход через формирователь весовой функции к второму входу умножителя, а остальные выходы - к управлянлдим входам счетчика импульсов, умножи- теля и сумматора соответственно ClJI Такой измеритель обладает невысоким быстродействием, поскольку выдача результата измерения производится один раз за цикл его работы, причем длительность этого цикла ограничена снизу ввиду взаимосвязи, ее с точностью измерения - чем выше требуемая точность, тем больше длительность цикла работы устройства. Кроме того, для построения измерите ля тpeбs тcя быстродействукяцие элементы высокой сложности, например углножитель и формирователь весовой функции, что усложняет и удорожает измеритель. Наиболее близким к изобретению по технической сущности является цифровой измеритель периода, содержащий формировдтель времени измерения, вход которого подключен к выходу формирователя, а выход через реверсивный счетчик - к первому вхо ду сумматора, выход и второй вход которого подключены соответственно к входу и выходу регистра памяти, тактовый вход которого подключен к тактовому входу формирователя време ни измерения и генератору образцово частоты, причем выход переноса сумматора подключен через счетчик к входу первой группы индикаторов, а выход регистра памяти подключен к входу второй группы индикаторов С2Л Недостатком указанного измерител также является невысокое быстродействие, ограниченное циклом его работы, длительность которого в свою очередь ограничена требуемой точностью измерения. Цель изобретения - повышение быс тродействия при сохранении высокой точности измерения. Поставленная цель достигается те что в устройство для измерения частоты и скорости ее изменения, содер жащее счетчик, разрядные выходы которого подключены к информационным входам накапливакадего сумматора, источникиопорной и измеряемой частоты, введены блок синхронизации и цифровой дифференциатор, информационные входы которого подключены к разрядныг 1 выходам накаплива1Ш1его сумматора, а тактовый вход через делитель частоты подключен к тактовому входу накапливающего суи матора и выходу блока синхронизации, входы которого подключены к выходам источников опорной и измеряемой частоты,выход источника опорной частоты подключен также к счетному входу счетчика. На фиг.1.представлена структурная схема устройстваI на фиг,2 - временные диаграммы его работы. Устройство содержит источники 1 и 2 измерительной и опорной частоты, блок 3 синхронизации, счетчик 4, накапливающий сумматор 5, делитель б частоты, цифровой дифференциатор 7. В устройстве разрядные выходы счетчика 4 подключены к информационным входам накапливаю1чего сумматора 5, разрядные выходы которого соединены с информационными .входс1ми цифрового дифференциатора 7, тактовый вход которого через делитель частоты 6 подключен к тактовому входу накапливакадего сумматора 5 и выходу блока синхронизации, входы которого подлючены к выходам источников 1 и 2 опорной и измеряемой частоты, источника опорной частоты подключен также -к счетному входу счетчика. В случае измерения частоты и скорости ее изменения источник 1 выполнен в виде формирователя импульсов ВХОДНОЙ (измеряемой частоты, точник 2 - в виде генератора опорной частоты, а в случае измерения периода скорости его изменения - наоборот . Цифровой дифференциатор 7 содержит последовательно соединенные входной регистр 8 и многоразрядны регистры 9 и 10 сдвига, тактовые входы котоЕ«лх соединены с тактовым входом цифрового дифференш1атора 7, а выходы - с входг1ми многовходового сумматора 11, содержащего в свою очеоедь сумматоры 12 и 13. Первый вход сумматора 12 подключен к выходу многоразрядного регистра 10 сдвига, а ВТОРОЙ вход - к выходу входного регистра 8, информа1шонные входы кото- , рого соединены с информационными входами цифрового дифференциатора 7. Первый вход сумматора 13 подключен к выходу сумматора 12, а второй вход со сдвигом на один разряд в сторону ст.арших разрядов к инверсному выходу многоразрядного регистра 9 сдвига. Выход сумматора 13 соединен

с выходом цифрового дифференциатора 7.

Устройство работает следующим образом.V . . Блок 3 синхронизации в ответ на каждый HMnyjfibc с выхода источника 2 вырабатывает свой выходной импульс, синхронный во времени со следующим за этим импульсом с выхода источника 1. Таким образом, на выходе блока 3 имеет место импульсная последовательность с частотой, равной частрте на выходе источник 2, но синхронная с импульсной последовательностью на выходе источника 1, Для нормальу ной работы блока 3 выходная частота источника 1 должна быть выше выходной частоты источника 2. Для этого в случае измерения частоты частоту генератора опорной частс)ты выбирают ниже минимальной входной частоты, а в случае измерения периода - выше максимальной входной частоты.

Блок 3 можно в простейшем случае Представить содержгццим триггер и элемент И, первый вход и выход которого соединены соответственно с выходом и входом сброса триггера,второй вход элемента И подключен к выходу источяика 1, вход установки триггера - к выходу источника 2, а выход элемента И соединен с выходом блока 3. Очередной импульс с выхода источника 2 устанавливает триггер блока 3 в состояние 1 и тем самым разрешает прохождение на выход блока 3

следующего за ним во времени импуль са с выхода источника 1 через элемент И блока 3, на первом входе которого установлен разрешающий потенциал. Прошедший импульс срабатывает триггер блока 3 и тем самым запрещает прохождение следующих импульсов с выхода источника 1 на выход блока 3 до прихода следующего импульса с выхода источника 2, по приходу которого цикл работы блока 3 начинается

заново. Таким образом, на каждый выходной импульс источника 2 блок 3 отвечает одним импульсом, привязанным по времени к выходным импульсам источника 1.

Предположим, что к моменту прихода некоего (обозначим его нулевым) импульса с выхода источника 2 состояние счетчика 4, накапливаю11его сум матора 5 и делителя б было нулевым.

Это предположение некритично и принято исключительно для удобства описания устройства.

По приходу нулевого импульса с выкода источника 2 блок 3 вырабатывает свой выходной импульс, по которому: накапливающий сумматор 5 сложит содержимое своегр внутреннего регистра с входным кодом. Поскольку, предположим, обе эти величины , в регистр накапливгиощего сумматора 5 запишется новое содержимое, также равное нулю, делитель б частоты, например, в виде суммирующегр счетчика увеличит содержимое этого счетчика на единицу.

В течение времени между приходом нулевого и первого импульсов с выхода источника 2 счетчик 4 пересчитывает выходные импульсы источника. ,.

0 Обозначим число импульсов с выхода источника 1, прошедвшх за время между к-ым и (к+1) -ым импульсгили с выхода источника 2 через М. Тогда к моменту прихода первого импульса

5 с выхода источника 2 .счетчик 4 насчитывает М шшульсов. По соответствующему импульсу с выхода блока 3 это число будет в накапливающем сумматоре 5 сложено с его (сумматора f предыдущим содержимЕФ(, т.е. попросту код М перепишется во внутренний регистр накапливающего сумматора 5, Содержимое делителя частоты б увеличится еще на единицу. ,

К моменту прихода второго импуль5са с выхода источника 2 код, написанный в счетчике 4, равен М.,+М. Соответственно, по импульсу с выхода блока 3 в регистр накапливающего cyNttiaTopa запишется код, равный М

0 f( |. Содержимое делителя б увеличится по тому же импульсу еще на единицу.

Распространяя приведенные рассуждения на произвольное количество

5 импульсов с выхода источника 2, можно записать обобщенные формулы для .выходных кодов счетчика 4 и накапливающего сумматора 5:

M.(1c| SlMi

«-1

с-(

k-i

(i)2. -Mj (k-f) . Ы iti 1

45

В моменты времени, соответствующи появлению на выходе блока 3 импульсор, номер которых кратен коэффициенту деления делителя б, выходной код накёщливающего сумматора 5 счи50тывается цифровым дифференциатором 7, где подвергается дальнейшей .цифровой обработке. В простейшем случае выполняемое цифровым дифференциатором 7 численное дифференцирова55:ние моЖет быть сведено к взятию ко-, нечных разностей соответствукядего порядку. Так в случае измерения частоты/периода нербходимое численное дифференцирование второго поряд60ка может быть сведено к взятию конечных разностей второго порядка по формуле

()+х(п-2|-2х(п-1. (1

В случае измерения скорости изменения частоты/периода необходимое

65 численное дифференцирование третьепорядка может быть сведено к взятию конечных разностей третьего порядка по формуле y(r«)X(r.)-X(n-3)+3X( (п-1К(2; Цифровой дифференциатор 7 в приведе йом на фиг.1 выполнении реализует формулу (1). Возможно путем соответствующего выполнения дифференциатора 7 добиться как одновременнЪй реа лизации обеих приведенных формул, так и реализации более сложных и более эффективных с точки зрения то ности измерения вариантов численног Дифференцирования, При условии срав нительно низкого темпа выдачи результатов измерения (до 100 раз в секунду) становится предпочтительной реализация цифрового дифференци атора 7 на микро-ЭВМ. Рассмотрим результат, достигаемы при работе цифрового Дифференциатора 7 (фиг.1), когда многоразрядные регистры сдвига обеспечивают задерж ку выходного кода по отношению к входному на в тактов, а коэффициент деления делителя равен t . Допустим, что с момента включения устройства с выхода источника 2 прошло . импульсов, где С7Д2е1+Ц Тогда последний прошедший с выхода источника 2 импульс вызвал соответт ствующий импульс на выходе блока 3 И, соответственно, импульс на выход делителя 6 поскольку Tt кратно Ъ. По импульсу с выхода делителя б во входной регистр 8 перепишется выхоД ной код накапливающего сумматора 5 равный Ьс-г N ((bc-1) (tc-1-i)Mi. ial На выходе многоразрядного регист ра сдвига 9 в соответствии с вышеиз сложенными определениями появится код, равный выходному коду накапливахязего сумматора аЪ импульсов назад, т.е. Na(thN..( (Ъс«сИн)МГ Соответственно, выходной код многоразрядного регистра 10 сдвига Iравен ВЁбсодному коду накапливсшщего сумматора 5 2аЬ импульсов назад, т.е. Ьс-гас-/ / (Ьс-2ас-1-1|М1. U-f Многовхбдовнй сумматор 11 внполн ет взвешенное суммирование указанны величин в соответствии с формулой (11, причем коэффициент Л-2) получа ется в двоичной системе счисления взятием кода с инверсного выхода (знак - I со сдвигом на один разряд всторону старших разрядов (эквивалент умножения на 2 ). Таким обрйзом, выходной код многовходового сумматора 11 равен: . ьс-г и, (c)iN( {с)(с)-2Мз(ф21 ( Ьс-2ас-2Ьс-ас-2 + 51 (bc-2ac- -i|«i-25I (fcc-«c-f-i|Wi j c-ctbfec-qc-2 (tc-i-ilWi + Rfec-i-i)1 bc-ac-iiabc-2ac-ibc-2ec-2 -a(fcc-ac- -i)мi+ ()-2{t)C-ac-1-i)+ v{bt-2c()Mi (bc-i-f; i4 Ubc-ac-f te-«c-2о( + X(UMc(b-fec) 21 M.,. , . гЪС-2«(С-1 .iso с1 J bC-2«fb Таким образом, выходной код цифрового дифференциатора 7 может быть описан выражением ,pO,4Z , где - усредненное значение огнсшения частот источников 1 и 2/ ог - количество тактов, на которое выходной код многоразрядных регистров сдвига 9 и 10 задержан относительно их же входного крда| Ъ - коэффициент деления делит теля б частоты. В случае измерения частоты эта ормула трансформируется к виду VM7fo/o.42 , а в случае измерения периода-к виду v tj«ii ;., Из приведенных формул видно, что при работе в десятичной системе счисления для получения отсчета в единицах частоты/периода, удобных для непосредственного восприятия человеком (герцы или секунды соответственно), достаточно принять опорну частоту равной lof Гц, а с помощью соответствующего выбора конструктивных параидатров устройства обеспечить равенство аЬиЮ . Из приведенных выкладок видно, что если учесть тождественность Мц грубой оценке отношения частот источников 1 и 2, то выходной код цифрового дифференциатора 7 соответствует отношению частот источников

1 и 2, полученному с помошью взвешенного статистического усреднения .мнжества грубых оценок этого соотношения по весовой Функции треугольного вида, что полностью совпадает с результатом работы известного устройства.

При этом длина весовой функции предлагаемого устройства равна 2 аЬ т.е. .в 2а раз превышает период выдачи результатов измерения, совпадающий с периодом выходного сигнала делителя 6. Следовательно, появляется возможность при сохранении вы сокой точности измерения, обуслов-ленной длиной весовой функции, в

2 а раз повысить темп выдачи результатов измерения, определякиций быстроействие устройства. V

Возможно также и обратное решение - сохранить быстродействие на прежнем уровне и в 2а раз удлинить весовую функцию статистического усреднения, что позволит в 40 раз повысить точность измерения.

Возможны также и другие варианты компромиссного выбора конструктивных характеристик устройства, представляющие одновременно и повышение быстродействия и повышение точности измерения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ магнитной записи асинхронных потоков цифровой информации и устройство для его осуществления | 1990 |

|

SU1788520A1 |

| СПОСОБ ИЗМЕРЕНИЯ ФАЗОВОГО СДВИГА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1996 |

|

RU2099721C1 |

| ИЗМЕРИТЕЛЬНЫЙ ГЕНЕРАТОР ПАРНЫХ ИМПУЛЬСОВ | 2022 |

|

RU2788980C1 |

| Цифровой многофазный генератор | 1990 |

|

SU1750032A1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1992 |

|

RU2042269C1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ ФАЗОВОГО СДВИГА | 1995 |

|

RU2089920C1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 2013 |

|

RU2534971C1 |

| Устройство для вычисления эквивалентного уровня звуковой экспозиции | 1988 |

|

SU1640556A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ | 2002 |

|

RU2229157C2 |

| Аналого-цифровой преобразователь | 2021 |

|

RU2760906C1 |

УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЧАСТОТЫ И СКОРОСТИ ЕЕ ИЗМЕНЕНИЯ, содержащее счетчик , разрядные выходы которого подключены к информационным входам накапливакшего сумматора jиcтoчники опорной и измеряемой час:тоты,, отличающееся тем, что, с целью повышения быстродействия при сохранении высокой точности измерения,в него введены блок синхронизации и цифровой дифференциатор, информационные входы которого подключены к разрядным выходам накапливанндего сумматора, а тактовый вход через делитель частоты подключен к тактовому входу накапливающего сумматора и выходу блока синхронизации, входы которого подключены к выходам источников опорной и (измеряемой частоты,выход источника) опорной частоты подключен также к счетному входу счетчика. СП W

/1 п fl I Я Я п п Я п II п п я п я fl н п п п я п п d п я д я я о п о я и II п я и

/e.f

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой частотомер | 1980 |

|

SU892332A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Цифровой измеритель периода | 1978 |

|

SU771563A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-06-30—Публикация

1982-04-05—Подача