Изобретение относится к области автоматики и вычислительной техники и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством.

Известен преобразователь временных интервалов в код, содержащий формирователи ST и SP импульсов, генератор импульсов, счетчик, реверсивный счетчик, дешифратор, триггеры, элементы И, работающий в режиме усреднения временных интервалов [1]. Недостатком такого преобразователя является его невозможность работы в режиме измерения мгновенных значений временных интервалов и формирования импульсов приращения грубого отсчета.

Наиболее близким техническим решением к данному изобретению является преобразователь угла поворота вала в код, реализующий известный способ измерения угла поворота вала [2]. Преобразователь содержит генератор импульсов, подключенный к входу ДЧ. Выход n-разряда ДЧ подключен к блоку преобразования угла поворота вала в последовательность временных интервалов от ST до SP импульсов, первый и второй выходы которого подключены к одним входам соответствующих ФТИ, другие входы ФТИ соединены с выходом генератора импульсов, а выходы ФТИ подключены к тактовым входам формирователей грубого отсчета (ФГО). Выходы старших разрядов ДЧ подключены к дешифратору, выходы которого предназначены для управления длительностью интервалов записи/чтения информации о ST и SP импульсах. Оба ФТИ и дешифратор в известном преобразователе объединены в блок синхронизации. Известный преобразователь содержит (n+1)-разрядные регистры для записи кодов точного отсчета ST и SP импульсов и времени их формирования и формирователи грубого отсчета (ФГО) ST и SP импульсов. Выход (n+1)-го разряда ДЧ подключен к входам (n+1)-х разрядов обоих регистров.

Кроме того, известный преобразователь содержит измеритель скорости, состоящий из трех блоков памяти, трех сумматоров, делителя кодов с памятью, экстраполяторы временных сдвигов ST и SP импульсов, сумматоры и блоки памяти для формирования полных кодов ST и SP импульсов на моменты начала интервалов чтения и сумматор с блоком памяти для формирования разности полных временных сдвигов ST и SP импульсов. В преобразователе, реализующем известный способ, функции измерителя скорости, экстраполяторов, сумматоров для формирования полных кодов ST и SP импульсов, сумматора для формирования разности кодов ST и SP импульсов и блоков памяти выполняет вычислительный блок (микроконтроллер).

Недостатком известного преобразователя является невозможность его работы в режиме усреднения временных интервалов, а также ограничение скорости изменения временных интервалов при формировании грубого отсчета, вызванное отсутствием информации на входах ФГО в интервалах чтения.

Предложенный преобразователь угла поворота вала в код, также, как и известный, содержит генератор импульсов, подключенный к входу ДЧ. Выход n-разряда ДЧ подключен к блоку преобразования угла поворота вала в последовательность временных интервалов от ST до SP импульсов, первый и второй выходы которого подключены к одним входам соответствующих ФТИ, другие входы ФТИ соединены с выходом генератора импульсов, а выходы ФТИ подключены к тактовым входам формирователей грубого отсчета (ФГО). Выходы старших разрядов ДЧ подключены к одной группе входов дешифратора, другая группа входов которого является шиной задания режима работы. Входы (n+1)-го разряда регистров соединены с выходом (n+1)-го разряда ДЧ. Выходы младших n разрядов регистров подключены к младшим разрядам соответственно одной и другой группы входов вычислительного блока. Выходы (n+1)-го разряда регистров подключены к первым входам вычислительного блока.

В предложенном преобразователе в отличие от известного в каждый канал формирования кодов ST и SP импульсов введены по одному дополнительному регистру, одному сумматору, блоку элементов И, счетчику импульсов и по три элемента И. Выходы младших n-разрядов ДЧ подключены к входам младших разрядов одной группы входов сумматоров. Выходы n-разряда и (n-1)-разряда ДЧ подключены к соответствующим информационным входам обоих ФГО, выходы которых подключены к входам старших разрядов одной группы входов сумматоров. Выходы младших и старших разрядов сумматоров подключены к входам регистров и дополнительных регистров соответственно. Выходы дополнительных регистров подключены к старшим разрядам одной и другой группы входов вычислительного блока. Выходы n-разрядов регистров и выходы дополнительных регистров через соответствующие блоки элементов И подключены к другим группам входов сумматоров. Первые выходы ФТИ через первые элементы И подключены к тактовым входам регистров, третьи выходы через вторые элементы И подключены к тактовым входам дополнительных регистров и одним входам третьих элементов И, выходы которых подключены к информационным входам счетчиков импульсов. Выходы счетчиков импульсов подключены к установочным входам триггеров. Одни выходы триггеров подключены к управляющим входам первых и вторых элементов И, другие выходы триггеров подключены к вторым входам вычислительного блока. Первый выход дешифратора подключен к управляющим входам третьих элементов И и блоков элементов И. Второй выход дешифратора подключен к счетным входам триггеров. Шина сброса подключена к входам сброса регистров, дополнительных регистров, ФГО, счетчиков импульсов и триггеров.

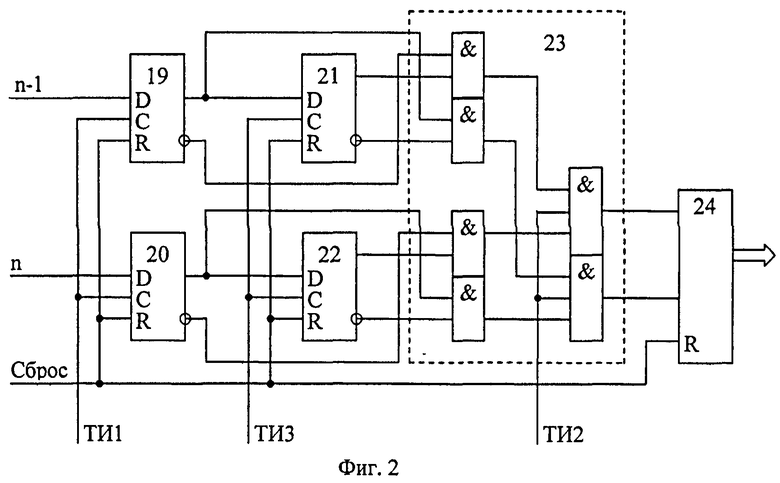

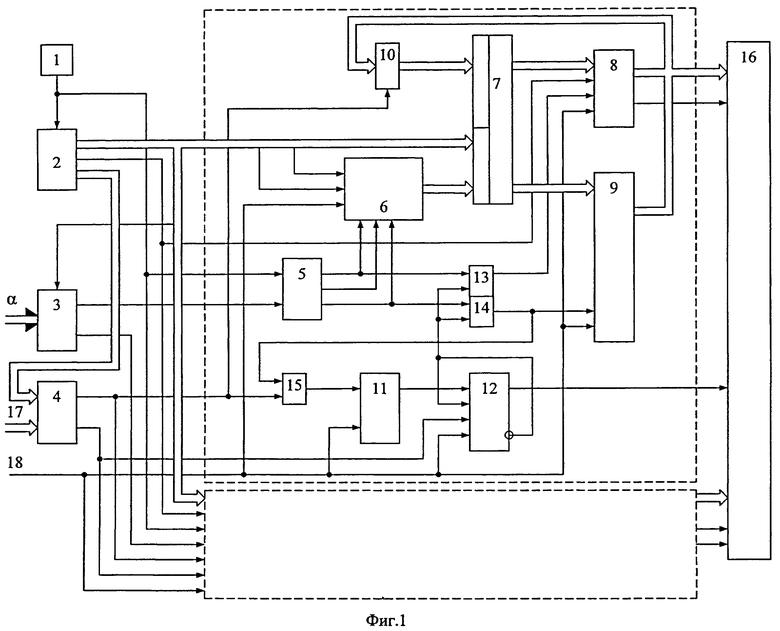

Структурная схема преобразователя угла поворота вала в код представлена на фиг.1, а структурная схема возможного варианта выполнения ФГО представлена на фиг.2.

Преобразователь на фиг.1 содержит генератор 1 импульсов, делитель 2 частоты, блок 3 преобразования угла поворота вала в последовательность временных интервалов, дешифратор 4, ФТИ 5, ФГО 6, сумматор 7, регистр 8, дополнительный регистр 9, блок 10 элементов И, счетчик 11, триггер 12, элементы И 13, 14, 15 с первого по третий, вычислительный блок 16, шину 17 управления, шину 18 сброса.

ФГО 6 (фиг.2) содержит четыре триггера 19, 20, 21 и 22, прямые и инверсные выходы которых подключены к входам дешифратора 23, состоящего из шести элементов И, а выходы дешифратора 23 подключены к входам сложения и вычитания реверсивного счетчика 24.

ФТИ 5 может быть выполнен в виде последовательного сдвигающего регистра ST (SP) импульсов тактовыми импульсами генератора 1 с использованием при необходимости дешифратора для формирования последовательности коротких тактовых импульсов (ТИ).

На фиг.1 совокупность элементов, предназначенных для формирования кода ST импульсов, раскрыта и обозначена пунктиром. Идентичная совокупность элементов для формирования кода SP импульсов не раскрыта и представлена квадратом с обозначением внешних связей.

Преобразователь работает в двух режимах: измерение угла по мгновенным значениям временных интервалов с позиционным точным и накапливающим грубым отсчетами и измерение угла по усредненным значениям временных интервалов в цикле усреднения. Режим работы преобразователя задается кодом шины 17. В начале каждого режима работы на шину 18 поступает сигнал сброса, устанавливающий преобразователь в исходное положение. Выходные импульсы генератора 1 частотой fги поступают на делитель 2, на выходах разрядов которого формируется сигнал цифровой развертки. Сигнал частотой f=fги/2n с выхода n-разряда делителя 2 является опорным сигналом для блока 3. Периодические последовательности ST и SP импульсов частоты f на выходах блока 3 сдвинуты по фазе пропорционально углам α и -α относительно опорного сигнала. В формирователях ФТИ 5 ST и SP импульсы синхронизируются импульсами генератора 1 так, чтобы фронты выходных импульсов ФТИ 5 не совпадали с моментами смены информации в делителе 2.

В режиме измерения угла по мгновенным значениям временных интервалов цикл измерения подразделяют на интервалы записи и чтения, кратные целому числу периодов опорного сигнала. Длительность интервалов записи устанавливают не менее двух периодов опорного сигнала из расчета обязательного попадания ST и SP импульсов в текущий интервал записи при заданной скорости изменения угла. Длительность интервалов записи/чтения задается на вход дешифратора 4 по кодовой шине 17. В дешифраторе 4 выбирается один из выходных сигналов делителя 2, который поступает на счетные входы триггеров 12. При записи триггеры 12 открывают элементы 13 и 14. По первым тактам соответствующих ФТИ 5 производится запись текущего значения всех n+1 разрядов делителя 2 через сумматор 7 в регистр 8 и значений (n-1)-го и n-го разрядов в триггеры 19, 20 ФГО 6. По вторым тактам производится опрос состояния дешифраторов 23. Если оба триггера 19 и 20 находятся в состоянии 0 (текущее значение), а триггеры 21 и 22 находятся в состоянии 1 (предыдущее значение), то произошел переход ST (SP) импульса через границу периода опорного сигнала в сторону увеличения фазового сдвига и с выхода дешифратора 23 поступает импульс на вход суммирования реверсивного счетчика 24. Если оба триггера 19 и 20 находятся в состоянии 1, а триггеры 21 и 22 находятся в состоянии 0, то произошел переход ST (SP) импульса через границу периода опорного сигнала в сторону уменьшения фазового сдвига и с выхода дешифратора 23 поступает импульс на вход вычитания реверсивного счетчика 24. По третьим тактам производится запись кодов реверсивных счетчиков 24 через сумматор 7 в регистр 9, а кодов триггеров 19 и 20 в триггеры 21 и 22. В этом режиме элемент 15 и блок 10 закрыты выходным сигналом дешифратора 4.

По каждому новому ST (SP) импульсу в интервале записи информация в регистрах 8 и 9 обновляется. В результате в регистрах 8 и 9 запоминают последние измеренные значения фазовых сдвигов ST и SP импульсов и моменты их формирования в интервалах записи. С началом интервала чтения триггер 12 устанавливается в 0. Элементы 13 и 14 закрываются. Пулевые сигналы с выходов триггеров 12 сигнализируют в вычислительный блок 16 о начале обработки записанной в регистры 8 и 9 информации.

Коды младших n разрядов регистров 8 являются одновременно позиционными кодами NT точного отсчета соответственно ST и SP импульсов измеряемого угла и кодами Nt точного отсчета моментов их формирования относительно развертки ДЧ 3. Старшие (n+1)-е разряды регистра 8 предназначены для исключения ошибки определения моментов формирования ST и SP импульсов величиной в период опорного сигнала в динамике, когда фактический период между ST (SP) импульсами превышает номинальное значение и формирование ST (SP) импульсов совпадает с переходом через границы опорного сигнала. Коды регистра 9 являются накапливающими кодами NГ грубого отсчета (старшими разрядами полного кода NП=NТ+NГ) ST и SP импульсов измеряемого угла.

В вычислительном блоке 16 определяют текущую скорость изменения фазовых сдвигов ST (или SP) импульсов. Для этого определяют приращение полных значений фазовых сдвигов ST импульсов в виде разности ΔNП между текущим и предыдущим измеренными значениями. Далее определяют разность (n+1)-разрядных кодов N∗t между моментами формирования фазового сдвига в текущем и предыдущем измерениях. Полученную разность AN∗t суммируют с числом k2n при k периодах опорного сигнала в цикле измерения между началами двух соседних интервалов чтения. Текущую скорость определяют в виде частного V=ΔNП/(k2n+ΔN∗t).

Измеренные фазовые сдвиги ST и SP импульсов экстраполируют на момент начала чтения. Для этого определяют дополнения Δt моментов N∗t формирования ST и SP импульсов до начала чтения Δt=2n-N∗t. Экстраполяционная поправка ΔN для ST и SP импульсов определяется в виде ΔN=VΔt. Скорости V изменения фазовых сдвигов ST и SP импульсов равны по модулю и противоположны по знаку, что следует учесть при определении экстраполяционных поправок ΔN для ST и SP импульсов. Полные значения кодов фазовых сдвигов ST и SP импульсов на момент начала чтения определяются по одинаковой формуле N=NП+ΔN с соответствующими вычисленными значениями NП и ΔN. Код углового положения вала определяется в виде разности полных значений кодов фазовых сдвигов ST и SP импульсов на момент начала чтения. По окончанию интервала чтения триггер 12 выходным сигналом дешифратора 4 перебрасывается в режим записи и начинается следующий цикл измерения.

Выполненный в виде микропроцессора блок 16 работает по программе, составленной в соответствии с рассмотренным алгоритмом вычисления кода угла по выходной информации регистров 8 и 9. Для устойчивой работы ФГО 6 необходимо, чтобы смещение двух соседних ST (SP) импульсов в процессе работы при всех погрешностях преобразователя угла не превышало одной четверти периода опорного сигнала.

При работе преобразователя в режиме усреднения выходной сигнал дешифратора 4 открывает элементы 15 и блоки 10 элементов И. Сигнал на счетные входы триггеров 12 в этом режиме не поступает. Выходы младших n разрядов регистров 8 и выходы разрядов регистров 9 через блоки 10 подключаются к другой группе входов сумматоров 7. В начале каждого цикла суммирования подается сигнал сброса. Триггеры 12 устанавливаются в 0, открывая элементы 13 и 14. По первым тактам ФТИ 5 суммы текущего кода младших n разрядов делителя 2 и выходных кодов регистр 8 записываются в регистр 8, а коды n-го и (n-1)-го разрядов делителя 2 записываются в ФГО 6. По вторым тактам ФТИ 5 в ФГО 6 формируются коды грубого отсчета. По третьим тактам ФТИ 5 суммы выходных кодов ФГО 6 и выходных кодов регистров 9 записываются в регистры 9, а коды триггеров 19 и 20 записываются в триггеры 21 и 22. Третьи такты ФТИ 5 проходят через элементы 15 и увеличивают на 1 содержимое счетчиков 11. С приходом очередных ST (SP) импульсов операции суммирования повторяются. Сумматоры 7 работают в режиме накопления мгновенных значений кодов угла с выходов делителя 2 (младшие разряды) и с выходов ФГО 6 (старшие разряды). По достижению расчетного количества суммируемых значений выходные сигналы счетчиков 11 устанавливают триггеры 12 в 1. Элементы 13 и 14 закрываются и цикл суммирования заканчивается, о чем свидетельствуют сигналы триггеров 12, поступающие на входы вычислительного блока 16. По окончанию цикла суммирования в каналах ST (SP) импульсов блок 16 вычисляет среднее в цикле значение угла в виде разности выходных кодов регистров 8 и 9 каналов ST и SP импульсов. Для начала очередного цикла суммирования следует подать сигнал сброса.

Технический эффект предложенного преобразователя состоит в расширении области применения, что позволяет его использовать для измерения мгновенных значений угла и в режиме усреднения. Кроме того, в предложенном преобразователе увеличивается допустимая скорость изменения угла в процессе измерения мгновенных значений угла, поскольку входы ФГО всегда подключены к источникам информации и тактовым импульсам.

Источники информации

1. Авторское свидетельство СССР №1829870, Кл. H03M 1/50, 1992 г.

2. Патент РФ №2465723, Кл. H03M 1/64, 2012 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПРОВЕРКИ МНОГООТСЧЕТНЫХ ПРЕОБРАЗОВАТЕЛЕЙ ВРЕМЕННЫХ ИНТЕРВАЛОВ В КОД | 2008 |

|

RU2355105C1 |

| СПОСОБ ИЗМЕРЕНИЯ УГЛА ПОВОРОТА ВАЛА | 2011 |

|

RU2465723C1 |

| СПОСОБ ПРОВЕРКИ МНОГООТСЧЕТНЫХ ПРЕОБРАЗОВАТЕЛЕЙ ВРЕМЕННЫХ ИНТЕРВАЛОВ В КОД | 2007 |

|

RU2349029C1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| Вычислительный блок матричного устройства для решения дифференциальных уравнений в частных производных | 1989 |

|

SU1605253A1 |

| Многоканальный преобразователь код-частота | 1985 |

|

SU1267621A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ТЕЛЕВИЗИОННОГО ИЗОБРАЖЕНИЯ С ИЗМЕНЕНИЕМ МАСШТАБА УПРАВЛЯЕМОГО ФРАГМЕНТА | 1993 |

|

RU2065206C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДВУМЕРНЫХ РАСПРЕДЕЛЕНИЙ СЛУЧАЙНЫХ ПРОЦЕССОВ | 2003 |

|

RU2253892C1 |

| ИМИТАТОР РЕАЛИЗАЦИИ СЛУЧАЙНЫХ ИЗМЕНЕНИЙ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 1995 |

|

RU2099863C1 |

| Устройство декодирования модифицированного кода БЧХ | 1990 |

|

SU1791961A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством. Техническим результатом является обеспечение возможности измерения мгновенных значений угла и работы в режиме усреднения временных интервалов. Устройство содержит генератор импульсов, делитель частоты, блок преобразования угла поворота вала в последовательность временных интервалов, дешифратор, формирователи тактовых импульсов, формирователи грубого отсчета, регистры, вычислительный блок, дополнительные регистры, сумматоры, блоки элементов И, счетчики, триггеры и элементы И. 2 ил.

Преобразователь угла поворота вала в код, содержащий генератор импульсов, подключенный к входу делителя частоты (ДЧ), выход n-разряда ДЧ подключен к блоку преобразования угла поворота вала в последовательность временных интервалов, первый и второй выходы которого подключены к одним входам соответствующих формирователей тактовых импульсов (ФТИ), другие входы ФТИ соединены с выходом генератора импульсов, а выходы ФТИ подключены к тактовым входам формирователей грубого отсчета (ФГО), выходы старших разрядов ДЧ подключены к одной группе входов дешифратора, другая группа входов которого является шиной задания режима работы, входы (n+1)-го разряда регистров соединены с выходом (n+1)-го разряда ДЧ, выходы младших n разрядов регистров подключены к младшим разрядам соответственно одной и другой группы входов вычислительного блока, выходы (n+1)-го разряда регистров подключены к первым входам вычислительного блока, отличающийся тем, что в него введены дополнительные регистры, сумматоры, блоки элементов И, счетчики импульсов, первые, вторые и третьи элементы И, выходы младших n разрядов ДЧ подключены к входам младших разрядов одной группы входов сумматоров, выходы n-разряда и (n-1)-разряда ДЧ подключены к соответствующим информационным входам обоих ФГО, выходы которых подключены к входам старших разрядов одной группы входов сумматоров, выходы младших и старших разрядов сумматоров подключены к входам регистров и дополнительных регистров соответственно, выходы дополнительных регистров подключены к старшим разрядам одной и другой группы входов вычислительного блока, выходы n разрядов регистров и выходы дополнительных регистров через соответствующие блоки элементов И подключены к другим группам входов сумматоров, первые выходы ФТИ через первые элементы И подключены к тактовым входам регистров, третьи выходы через вторые элементы И подключены к тактовым входам дополнительных регистров и одним входам третьих элементов И, выходы которых подключены к информационным входам счетчиков импульсов, выходы счетчиков импульсов подключены к установочным входам триггеров, одни выходы триггеров подключены к управляющим входам первых и вторых элементов И, другие выходы триггеров подключены к вторым входам вычислительного блока, первый выход дешифратора подключен к управляющим входам третьих элементов И и блоков элементов И, второй выход дешифратора подключен к счетным входам триггеров, шина сброса подключена к входам сброса регистров, дополнительных регистров, ФГО, счетчиков импульсов и триггеров.

| СПОСОБ ИЗМЕРЕНИЯ УГЛА ПОВОРОТА ВАЛА | 2011 |

|

RU2465723C1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ УГЛА ПОВОРОТА ВАЛА В КОД | 1993 |

|

RU2108663C1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 2007 |

|

RU2356162C1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 1991 |

|

RU2020752C1 |

| WO9106152 A1, 02.05.1991 | |||

| WO 2009060329 A1, 14.05.2009 | |||

| JP 2008219756 A, 18.09.2008 | |||

Авторы

Даты

2014-12-10—Публикация

2013-07-03—Подача