перекрестий которого подключена к группе входов управления выбора перекрестий ячейки соответственно, выход формирователя сигнала разрешения работы подключен к входу разрешения работы блока памяти направлений, вход разрешения работы ортогоналсй ячейки подключен к входам настройки первого приемного блока и ортогональных формирователей сигналов обратной связи и возбуждения, вход разрешения работы диагоналей ячейки подключен к входам настройки второго приемного блока и диагональных формирователей сигналов обратной связи .и возбуждени входы ячейки диагональных сигналов возбуждения соединены с информационными входами второго приемного блока .соответственно, входы ячейки диагональных сигналов обратной связи соеднены с входами блока памяти направлений соответственно, выходы ячейки сигналов запоминания диагональных найравлений соединены с первой группой выходов блока памяти направлений и информационными входами диагонального формирователя сигналов обра ной связи соответственно, выходы ячейки диагональных сигналов возбуждения и обр.атной связи подключены к вьЬсодам диагональных формирователей сигналов обратной связи и возбуждени соответственно, выходы диагонального формирователя сигналов обратной связ соединены с входами диагональных сигналов обратной связи формирователя маркера соответственно, выход сигнала о переходе в возбужденное сотояние ячейки соединен с одноименным вых.одом блока памяти направлений, вход тактирующего импульса которого соединен с входом тактирукнцего импулса ячейки, входы ортогональных сигналов обратной связи блока памяти направлений соединены с одноименными входами ячейки соответственно, входы сигналов запрета, начального возбуж Дения и источника обратной связи блока памяти направлений соединены с

одноименными выходами блока запоминания начальных условий соответст епно; вход сигнала признакавозбуждения которого соединен с одноименным выходом блока памяти направлений и входами признака ортогонального и диагонального формирователей сигналов возбуждения, выход блока памяти направлений сигнала признака обратной связи подключен -к входам призна0616

ка ортогонального и диагонального формирователей сигналов обратной связи, вторая группа диагона/1ьных выходов блока Пс1мяти направлений соединена с информационными входами диагонального формирователя сигналов возбуждения, выход блока памяти.направлений сигнала открытия подключён к входам признака первого и второго приемных блоков. i

2.Устройство поп,1,отличаю щ е ее я тем, что первый и второй приемные блоки содержат кажда|й четыре элемента И,.причем их первые

входы соединены с информационными входами блока, выходы соединены с информационными выходами блока, вторые входы элементов И соединены с входом .настройки блока, третьи входы элементов И подключены к входу признака блока.

3.Устройство по п.t, о т ,л и чающееся тем, что ортогональные и диагональные .формирователи сигналов обратной связи и возбуждения содержат каждый четыре элемента И, причем их первые входы соединены с информационными входами формирователя, выходы соединены с информационными выходами формирователя, вторые входы элементов И соединены с входом настройки на направление формирователя, третьи входы элементов И подключены к входу признака формирователя.

4.Устройство по п.1, о т л и чающееся тем, что блок памяти направлений содержит регистр запоминания ортогональных направлений, регистр запоминания диагональных направлений, три элемента ИЛИ, два элемента И, элемент НЕ и элемент задержки, причем входы установки в единичное состояние разрядов регистров запоминания ортогональных и диагональных

.направлений соединены с ортогональными и диагональными входами сигналов возбуждения блока соответственно, входы установки разрядов регистров в нулевое состояние соединены с входом сигнала сброса блока, нулевые выходы разрядов регистров соединены с выходами сигналов обратного кода ортогональных и диагональных направлений блока соответственно, единичные выходы .разрядов регистров соединены с .выходами сигналов прямого кода ортогональных и диагональных направлений блока соответственно, входы первого

элемента ИЛИ соединены с группами входов установки в единичное состояние разрядов регистров запоминания ортогональных и диагональных направлений, выход первого элемента ИЛИ соединен с въкодом сигнала о переходе в возбужденное состояние блока, входы с первого по восьмой второго элемент ИЛИ соединены с единичными выходами разрядов регистров запоминания ортогональных и диагональных направлений девятый вход элемента ИЛИ соединен с входом сигнала начального возбуждения блока, а выход первого элемента ИЛИ соединен с входами элемента задержки и первого элемента И, второй вход которого соединен с входом тактирующего импульса блока, выход первого элемента И соединен с выходом признака возбуждения блока, выход элемента задержки через элемент НЕ подключен к первому входу второго элемента И, второй и третий входы которого соединены с входами запуска и запрета блока, а выход соединен- с рыходом сигнала открытия блока, входы третьего элемента ИЛИ соединены с ортогональными и диагональными входами сигналов обратной связи блока, выход третьего элемента ИЛИ соединен с выхЬдом признака обратной Связи блока.

5.Устройство по П.1, о т л и чающееся тем, что формирователь маркера состоит из элемента ИЛИ и триггера, причем первый и второй входы элемента ИЛИ соединены с входами сигналов начального возбуждения и источника обратной связи формирователя, входы с третьего по шестой

и с седьмого по десятый подключены к входам ортогональных и диагональных сигналов обратной связи формирователя соответственно, выход элемента ИЛИ соединен с входом установки в единичное состояние триггера, второй вход которого подключен к входу сигнала , сброс а формирователя, а выход триггера подключен к выходу сигнала маркера формирователя.

6.Устройство по П.1, о т л и ч а ю щ е е с я тем, что формирователь сигнала разрешения работы состоит из сумматора, дешифратора, первого, второго и--третьего элементов ИЛИ, первого, второго и третьего элементов И, причем входы сумматора соединены с информационными входами формирователя, выходы сумматора соеинены с входами дешифратора, первый выход которого соединен с первым, входом третьего элемента ИЛИ, второй, третий и четвертый выходы дешифратора соединены с первыми входами первого, второго и третьего элементов И, вторые входы первого и второго элементов И подключены к выходам первого и второго элементов ИЛИ соответственно, первый вход выбора перекрестий формирователя подключен к первому входу первого элемента ИЛИ, второй вход выбора перекрестий формирователя соединен с вторым входом первого элемента ИЛИ и первым входом второго элемента ИЛИ, третий вход выбора перекрестий формирователя соединен с третьим входом первого элемента ИЛИ, вторым входом второго элемента ИЛИ и вторым входом третьего элемента И, выходы первого, второго и третьего элементов И подключены к второму, третьему и четвертому входам третьего элемента ИЛИ, выход которого соединен с выходом сигнала разрешения фо рмир о в ат еля.

7. Устройство по П.1, о т л и чающееся тем, что блок запоминания начальных условий состоит из первого, второго, третьего и четвертого триггеров и элементов И, ИЛИ, НЕ, причем входы для установки в единичное состояние первого, второго и третьего триггеров соединены с входами установки признака начального возбуждения, индивидуального запрета, признака конца распространения блока соответственно, входы установки в нулевое состояние всех триггеров соединены с входом сигнала сброса блока, вход установки в единичное состояние четвертого триггера подключен к выходу элемента И, единичный выход первого триггера соединен с выходом сигнала начального возбуждения блока, единичный выход второго триггера подключен к первому входу элемента ИЛИ, единичный выход третьего триггера соединен с первым входом элемента И, единичный выход четвертого триггера соединен с выходом сигнала источника обратной связи блока, второй вход элемента ИЛИ подключен к входу сигнала общего запрета блока, второй .вход элемента И соединен с входом признака возбуждения блока, выход элемента ИЛИ через элемент НЕ соединен с выходом сигнала запрета блока. Изобретение относится к области цифровой вычислительной техники и предназначено для использования в системах автоматизированного проекти рования монтажно-коммутационных соединений . Известна ячейка однородных сетей содержащая блок обработки входных сигналов, блок запоминания признака конечной точки, блок запрета распро странения волны, блоки элементов И И-НЕ и Ш1И-НЕ lj . Недостатками известной ячейки являются зависимость качества результатов работы трассирующего устройств от случайного распределения скоростей работы элементов ячейки и ориентации ячейки на определенный вид технологии. Наиболее близкой по технической сущности к изобретению является ячей ка однородной сети, содержащая элементы ИЛИ, группу элементов ИЛИ, пер вую, вторую и .трег;ью группы элементов И, используемая в качестве элемента трассирующей сети. Ячейка состоит из блоков приема входных сигналов возбуждения, запоминания источника возбуждения, формирования выход ных сигналов возбуждения, передачи сигналов обратной связи, определения принадлежности к множеству трасс, запоминания начальных условий трассировки. Первая группа входов блока приема входных сигналов возбуждения сое динена с первой группой входов ячей второй и третий входы блока подключены к первому и второму выходам бл ка запоминания начальных условий трассировки, четвертая группа входо соединена с первой группой выходов блока запоминания источников возбуж дения, второй группой выходов ячейки и первой группой входов блока фо мирования выходных сигналов возбуждения. Первая группа выходов блока приема входных сигналов подключена к первой группе входов блока запоминания источников возбуждения, вто ргой выход блока приема входных сигналов соединен с третьим выходом ячейки. Второй вход ячейки запоминания источников возбуждения соединен с пятым входом ячейки, вторым входом блока запоминания начальных условий 162 и третьим входом блока определения принадлежности к множеству трасс. Вторая группа выходов блока за поминания начальных условий соединена с первой группой входов блока передачи сигналов обратной связи. Второй и третий входы блока формирования выходных сигналов возбуждения подключены соответственно к второму и третьему выходам блока запоминания начальных условий, четвертый вход - к третьему входу ячейки, а группа выходов -.к первой группе выходов ячейки. Второй вход блока передачи сигналов обратной связи подключен к четвертому выходу блока запоминания начальных условий и шестому выходу ячейки, третьягруппа входов блока передачи сигналов обратной-связи соединена с второй группой входов ячейки, а группа выходов - с первой группой входов блока определения принадлежности к множеству трасс и четвертой группой выходов ячейки. Второй вход блока определения принадлежности к множеству трасс соединен с третьим входом блока запоминания начальных условий, а выход - с пятым выходом ячейки. , Входы блока запоминания начальных условий с первого по пятый подключены соответственно к входам ячейки с четвертого по восьмой 2 . Недостатками известного решения являются возможность проведения через ячейку только одной трассы, в то вре мя как ряд технологий (многослойный печатньй монтаж, тонкопроволочный монтаж и т.д.) дают возможность проводить через один дискрет платы с заданными координатами два и более проводников, электрически не связанных между собой, и невозможность перестройки ячейки при смене технологических параметров (работа на ортогональной идиагональной сетках, изменение ограничений на число проводников, проходящих через дискрет рабочего поля). Цель изобретения - расширение обасти применения путем оперативной перестройки схемы ячейки для работы различными сетками разрешенных наравлений и с переменными значенияи ограничений на число перекрестий, риводящей к моделированию волновых процессов с учетом различных конструктивно-технологических условий. Поставленная цель достигается тем что в ячейку однородной трассирующей сети, содержащую первый приемный блок блок памяти тчаправлений, формирователь маркера, ортогональный формирователь сигналов обратной связи, ортогональный формирователь сигналов возбуждения, блок запоминания начальных условий, причем.информационные входы первого приемного блока соединены с группой ортогональных входов-ячейки сигналов возбуждения, выходы первого приемн.ого блока соединены с орт гональными входами .возбуждения блока памяти направлений соответственно, вход сигнала сбррса блока памяти направлений соединен с входом сброса ячейки, входом сброса блока запоминания начальных условий и входом сброса формирователя маркера, первая и вторая группы ортогональных выхо. дов блока памяти направлений соедине ны с информационными входами ортогональных фо1 1ирователей сигналов возбуждения и обратной связи соответственно, вторая группа выходов блока п мяти направлений соединена с группой выходов ячейки запоминания ортогональных направлений, группы выходов ортогональных формирователей сигналов обратной связи и возбуждени подключены к группам выходов ячейки ортогональных сигналов обратной связ и сигналов возбуждения соответственно, группа выходов ортогонального формирователя сигналов обратной, связи подключена к групце входов ортогональных сигналов обратной связи формирователя маркера соответственно, выход которого соединен с выходом ячейки сигнала маркера, выходы блока запоминания начальных условий сигналов начального возбуждения и йс точника обратной связи соединены с одноименными входами формирователя маркера, выход сигнала источника обратной связи блока запоминания начальных условий подключен к выходу ячейки сигнала источника обратной связи, выходы ячейки сигналов общего запрета и установок признака начального возбуждения, признака конца распространения сигналов возбуждения и индивидуального запрета соединены с одноименными входами блока запоми нания начальных условий, введены регистр, второй приемный блок, диагональные формирователи сигналов обратной связи и возбуждения, формирователь сигнала разрешения работы, причем входы регистра подключены к группе информационных входов фиксации трасс ячейки, выходы регистра подключены к информационным входам формирователя разрешения работы соответственно, группа управлякяцих входов вы.бора перекресний которого подключена к группе входов управления выбора перекрестий ячейки .соответственно, выход формирователя сигнала разрешения работы подключен к входу разрешения работы блока памяти направлений, вход разрешения работы ортогоналей ячейки подключен к входам настройки первого приемного блока и ортогональных формирователей сигналов обратной связи и возбуждения, вход разрешения работы диагоналей ячейки подключен к входам настройки второго приемного блока и диагональных формирователей сигналов обратной связи и возбуждения, входы ячейки диагональных сигналов возбуждения соединены с информационными входами второго приемного блока соответственно, входы ячейки диагональных сигналов обратной связи соединены с входами блока памяти направлений соответственно, выходы ячейки сигналов запоминания диагональных направлений соединены с первой группой выходов блока памяти направлений и информационными входами диагонального формирователя сигналов обратной связи соответственно, выходы ячетйки диагональных сигналов возбуж ения и обратной связи подключены-к выходам диагональных формирователей сигналов обратной связи и возбуждения соответственно, выходы диагонального формирователя сигналов обратной связи соединены с входами диагональных сигналов обратной связи формирователя маркера соответственно, выход сигнала о переходе в возбужденное состояние ячейки соединенс одноименным выходом блока памяти направлений, вход тактирующего импульса которого соединен с входом тактирующего импульса ячейки, входы ортогональных сигналов обратной связи блока памяти направлений соединены с одноименньп14И входами ячейки соответственно, входы сигналов запрета, начального возбуждения и источника обратной связи блока памяти направлеНИИ соединены с одноименными выходами блока запоминания начальных условий сортветственно, вход сигнала при нака возбуждения которого соединен с одноименным выходом блока памяти направлений и входами признака ортогонального и диагонального формирователей сигналов возбуждения, выход блока памяти направлений сигнала при нака обратной связи подключен, к входам признака ортогонального и диагонального формирователей сигналов обратной связи, вторая группа ди гонал ных выходов блока памяти направлений соединена с информационными входами диагонального формирователя сигналов возбуждения, выход блока памяти направлений сигнала открытия подключен к входам признака первого и второго приемных блоков. Первьй и второй приемные блоки ячейки содержат каждый по четыре эле мента. И, причем их первые входы в каждом блоке соединены с информацион ными входами блока, выходы соединены с информационными выходами блока, вторые входа элементов И соединены с входом настройки блока, третьи входы элементов И подключены к входу признака блока. Ортогональные и диагональные формирователи сигналов обратной связи и возбуждения содержат каждый по четыре элемента И, причем их первые входы соединены с информационными входами формирователя, выходы соединены с информационными выходами формирователя, вторые входь элементов И соединены с входом настройки на направление формирователя, третьи входы элементов И подключены к входу признака формирователя. Блок памяти направлений ячейки содержит регистр запоминания ортогональ ных направлений, регистр запоминания диагональных направлений, три эле.мента ИЛИ, два элемента И, элемент НЕ и элемент задержки, причем входы установки в единичное состояние разря дов регистров запоминания ортогональных и диагональных направлений соединены с ортогональными и диагональными входами сигналов возбуждения блока соответственно, входы установки разря дов регистров в нулевое состояние соединены с входом сигнала сброса блока, нулевые выходы разрядов регистров соединены с выходами сигналов обратного кода ортогональных и диагональных направлений блока соответст- . венно, единичные выходь разрядов регистров соединены с выходами сигналов прямого кода ортогональных и диагональных направлений блока соответственно, входы первого элемента ИЛИ соединены с группами входом установки в единичное состояние разрядов регистров запоминания ортогональных и диагональных направлений, выход первого элемента ИЛИ соединен с выходом сигнала о переходе в возбужденное состояние блока, входы с первого по восьмой второго элемента ИЛИ соединены с единичными выходами разрядов регистров запоминания ортогональных и диагональных направлений, девятый вход элемента ИЛИ соединен с входом сигнала начального возбуждения блока, а выход первого элемента ИЛИ соединен с входами элемента задержки и первого элемента И, второй вход которого соединен с входом тактирующего импульса блока, выход первого элемента И соединен с выходом признака возбуждения блока, выход элемента задержки через элемент НЕ подключен к первому входу, второго элемента И, второй и третий входы которого соединены с входами запуска и запрета блока, а выход соединен с выходом сигнала открытия блока, входы третьего элемента ИЛИ соединены с ортогональными и диагональными входами сигналов обратной связи блока, выход третьего элемента ИЛИ соединен с выходом признака обратной связи блока. Формирователь маркера ячейки состоит из элемента ИЛИ и триггера, причем первый и второй входы элемента ИЛИ соединены с входами сигналов начального возбуждения и источника обратной связи формирователя, входы с третьего по шестой и с седьмого по десятый подключены к входам ортогональных и диагональных сигналов обратной связи формирователя соответственно, выход элемента ИЛИ соединен с входом установки в единичное состояие триггера, второй вход которого одключен к входу сигнала сброса ормирователя, а выход триггера подлючен к выходу сигнала маркера форирователя . Формирователь сигнала разрешения аботы из сумматора, дешифраора, первого, второго и третьего

элементов ШШ, первого, второго и третьего элементов И, причем вХоды сумматора соединены с информационными входами формирователя, выходы сумматора соединены с входами дешифратора, первый выход которого сЬединен с первым входом третьего элемента HIDi, второй, третий и четвертый выходы дешифратора соединены с первыми входами первого, второго и третьего элементов И, вторые входы первого и второго элементов И подключены к выходам первого и второго элементов ИЛИ соответственно, первый вход выбора перекрестий формирователя подключек к первому входу первого элемента ИЛИ, второй вход выбора перекрестий формирователя соединен с вторым входом первого элемента ИЛИ и первым входом второго элемента ИЛИ, третий вход выбора перекрестий формирователя соединен с третьим входом первого элемента ИЛИ, вторым входом второго элемента ИЛИ и,вторым входом третьего элемента И, выходы jiepaoro, второго и третьего элементов И подключены к второму, третьему и четвертому входам третьего элемента ИЛИ, выход котррбго соединен с выходом сигнала/ разрешения формирователя.

Блок запоминания начальных условий ячейки состоит из первого, второго, третьего и четвертого триггеров и элементов И, ИЛИ, НЕ, причем входы для установки в единичное соетояние первого, второго и третьего триггеров соединены с входами установки признака начального возбуждения, индивидуального запрета, признака конца распространения блока соответственно, входы установки в нулевое состояние всех триггеров соединены с входами сигнала сброса блока, вход установки в единичное состояние четвертого триггера подключен к выхрду элемента И, единичный выход первого триггера соединен с выходом сигнала начального возбуждения блока, eJ иничныft выход второго триггера полключен к первому входу элемента ИЛИ, единичный выход третьего триггера соединен с первым входом элемента И, единичный выход четвертого триггера соединен с выходом сигнала источника обратной связи блока,второй вход эле- мента ШШ подключен к входу сигнала общего запрета блока, второй вход элемента И соединен с входом признака возбуждения блока, выход элейента ИЛИ через элемент НЕ соединен с выходом, сигнал запрета блока.

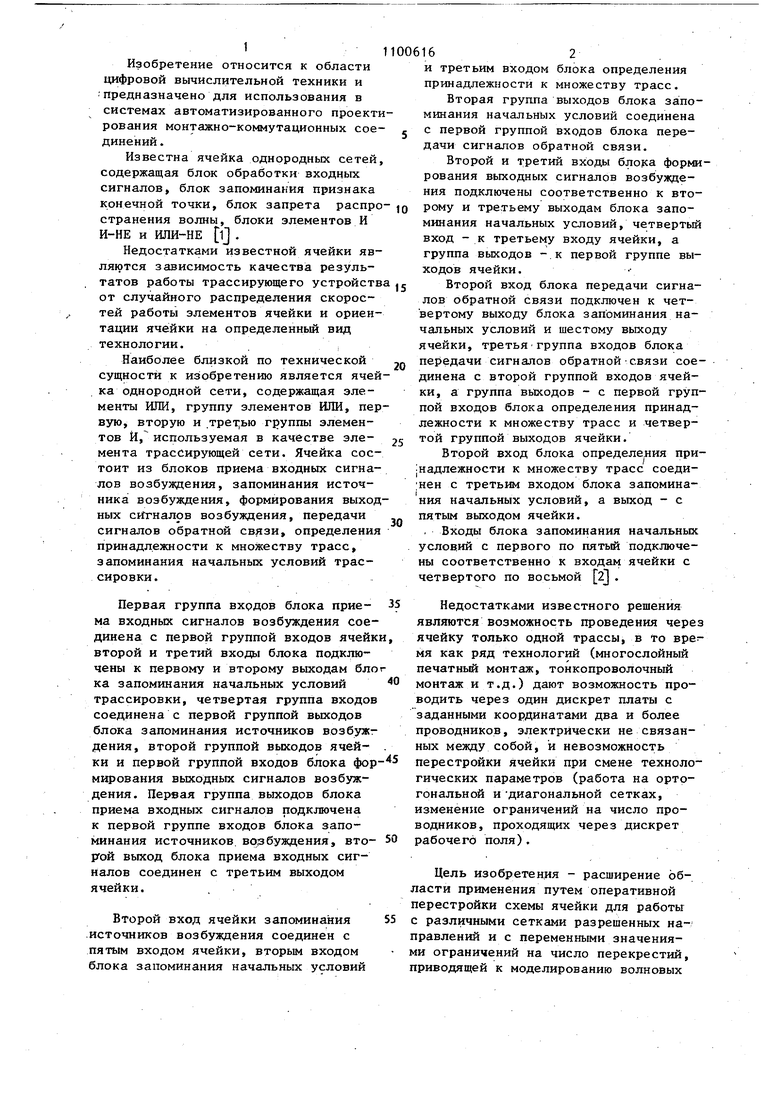

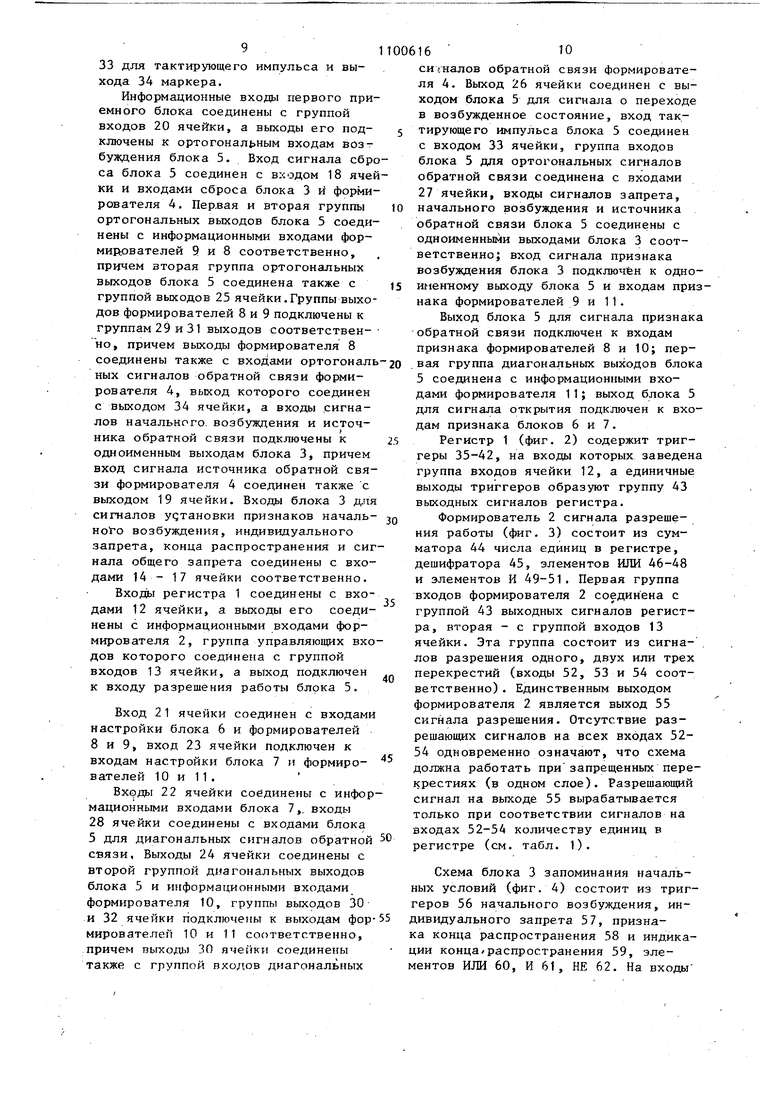

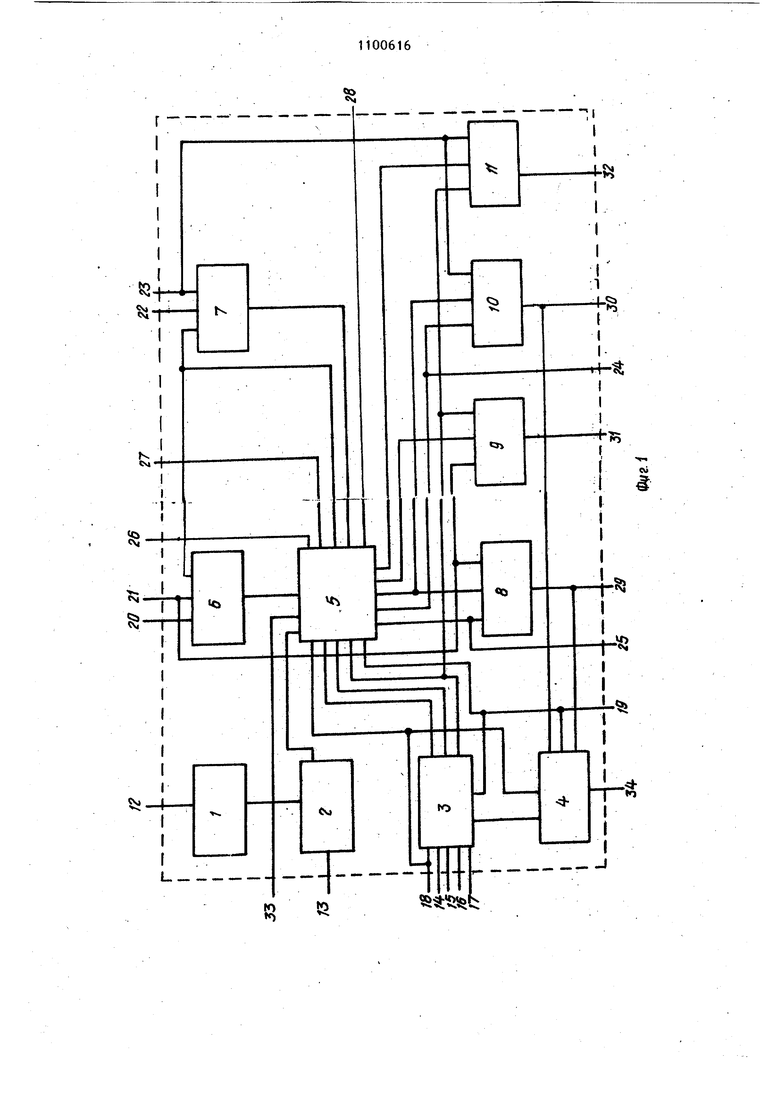

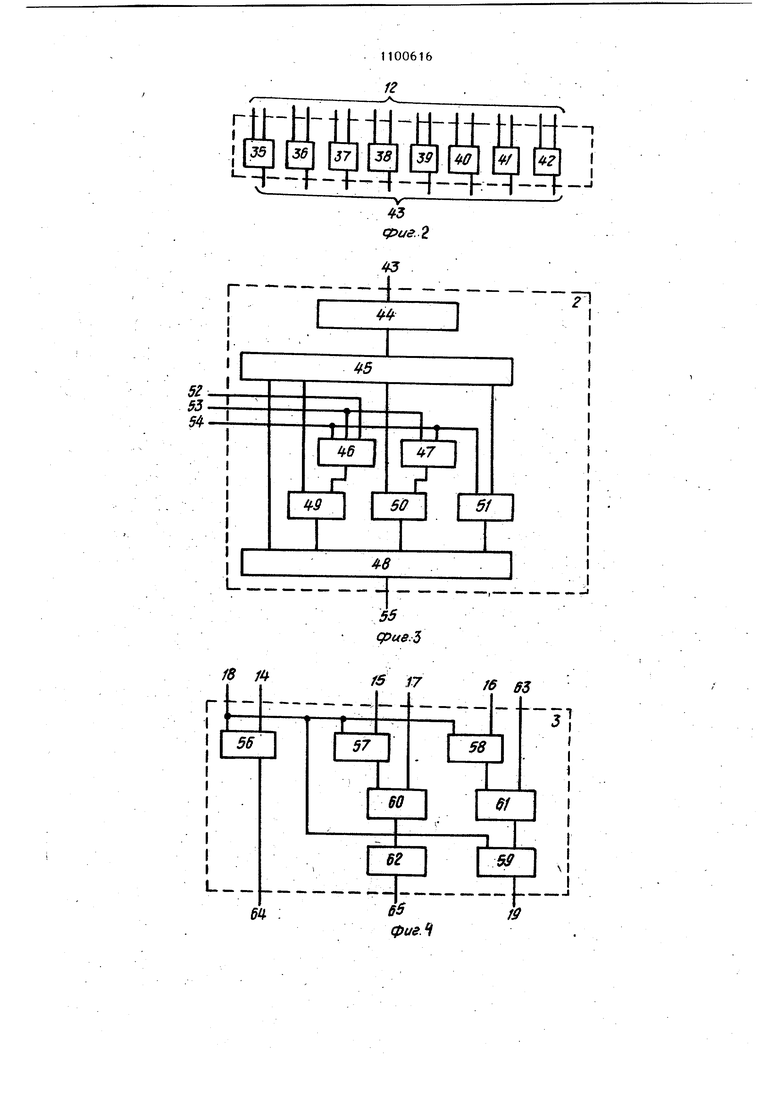

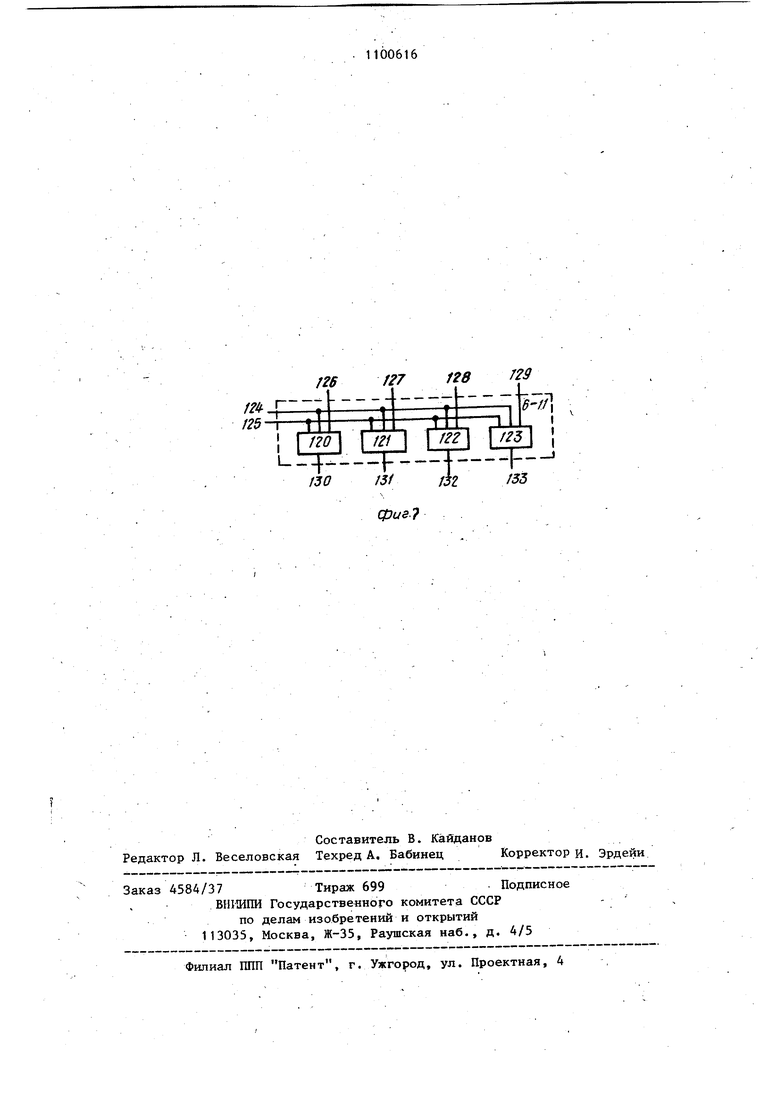

На фиг. 1 представлена блок-схема ячейки; на фиг. 2 - схема регистра; на фиг. 3 - формирователь сигнала разрешения работы; на фиг. 4 - блок запоминания начальных условий; на фиг. 5 - формирователь маркера; на фиг. 6 - блок памяти направлений; на фиг. 7 - пример реализации ортогональных и диагональных формирователей сигналов возбуждения и обратной связи, а также первого и второго приемных блоков.

Структурная схема ячейки (фиг.1) содержит регистр 1, формирователь 2 сигнала разрешения работы, блок 3 запоминания начальных условий, формирователь 4 маркера, блок 5 памяти направлений, первый 6, второй 7 приемные блоки, ортогональный формирователь 8 сигналов обратной связи, ортогональный формирователь 9 сигналов возбуждения, диагональный формирователь 10 сигналов обратной связи, диагональный формирователь. 11 сигналов возбуждения. г

Соединение ячейки с соседними Ячейками сети и устройством управления сетью осуществляется с помощью групповых и одиночньгх входов и выходов: групп 12 и 13 входов фиксации трасс и выбора перекрестий соответственно входов 14 для установки признака начального возбуждения, индивидуального .запрета 15, признака конца распространения 16, BXOJIJOB 17 общего запрета, сброса 18, выхода 19 источника сигналов обратной связи группы ортогональных входов 20 сигналов возбуждения , входа 21 сигнала разрешения работы ортогоналей, группы диагональных входов 22 сигналов возбуждения, входа 23 сигнала разрешения работы диагоналей, групп 24 и 25 выходов для диагональных и ортогональных 25 скгнало-в запоминания направлений соответственно, выхода 26 для сигнала о переходе ячейки в возбужденное состояние, группы входов для ортогональных 27 и диагональных 28 сигналов обратной связи, групп выходов для ортогональных 29 и диагональных 30 сигналов обратной связи, групп выходов для ортогональных 31 и диагональных 32 сигналов возбуждения, входа 33 для тактирующего импульса и выхода 34 маркера. Информационные входы первого при емного блока соединены с группой входов 20 ячейки, а выходы его подключены к ортогональным входам возбуждения блока 5. Вход сигнала сбр са блока 5 соединен с входом 18 яче ки и входами сброса блока 3 и форми рователя 4. Пер.вая и вторая группы ортогональных выходов блока 5 соеди нены с информационными входами формирователей 9 и 8 соответственно, причем вторая группа ортогональных выходов блока 5 соединена также с группой выходов 25 ячейки.Группы выхо дов формирователей 8 и 9 подключены к группам 29 и 31 выходов соответственно, причем выходы формирователя 8 соединены также с входами ортогонал ных сигналов обратной связи формирователя 4, выход которого соединен с выходом 34 ячейки, а входы сигналов начального, возбуждения и источника обратной связи подключены к одноименным выходам блока 3, причем вход сигнала источника обратной свя зи формирователя 4 соединен также с выходом 19 ячейки. Входы блока 3 для сигналов удтановки признаков началь Holro возбуждения, индивидуального запрета, конца распространения и си нала общего запрета соединены с входами 14 - 17 ячейки соответственно. Входы регистра 1 соединены с вхо дами 12 ячейки, а выходы его соединены с информационными входами формирователя 2, группа управляющих вхо дов которого соединена с группой входов 13 ячейки, а выход подключен к входу разрешения работы блока 5. Вход 21 ячейки соединен с входами настройки блока 6 и формирователей 8 и 9, вход 23 ячейки подключен к входам настройки блока 7 и формирователей 10 и 11. Входы 22 ячейки соединены с инфор мационными входами блока 7,. входы 28 ячейки соединены с входами блока 5 для диагональных сигналов обратной связи, Выходы 24 ячейки соединены с второй группой диагональных выходов блока 5 и информационными входами формирователя 10, группы выходов 30 и 32 ячейки подключены к выходам фор мирователей 10 и 11 соответственно, причем выхода) 30 ячейки соединены также с группой вхолов диагональных 16 10 сигналов обратной связи формирователя 4. Выход 26 ячейки соединен с выходом блока 5 для сигнала о переходе в возбужденное состояние, вход тактирующего импульса блока 5 соединен с входом 33 ячейки, группа входов блока 5 для ортогональных сигналов обратной связи соединена с входами 27 ячейки, входы сигналов запрета, начального возбуждения и источника обратной связи блока 5 соединены с одноименными выходами блока 3 соответственно; вход сигнала признака возбуждения блока 3 подключён к одноименному выходу блока 5 и входам признака формирователей 9 и 11. Выход блока 5 для сигнала признака обратной связи подключен к входам признака формирователей 8 и 10; первая группа диагональных выходов блока 5 соединена с информационными входами формирователя 11; выход блока 5 для сигнала открытия подключен к входам признака блоков 6 и 7. Регистр 1 (фиг. 2) содержит триггеры 35-42, на входы которых заведена группа входов ячейки 12, а единичные выходы триггеров образуют группу 43 выходных сигналов регистра. Формирователь 2 сигнала разрешения работы (фиг. 3) состоит из сумматора 44 числа единиц в регистре, дешифратора 45, элементов ИЛИ 46-48 и элементов И 49-51. Первая группа входов формирователя 2 соединена с группой 43 выходных сигналов регистра, вторая - с группой входов 13 ячейки. Эта группа состоит из сигна- . лов разрешения одного, двух или трех перекрестий (входы 52, 53 и 54 соответственно) . Единственным выходом формирователя 2 является выход 55 сигнала разрешения. Отсутствие разрешающих сигналов на всех входах 5254 одновременно означают, что схема должна работать призапрещенных перекрестиях (в одном слое). Разрешающий сигнал на выходе 55 вырабатывается только при соответствии сигналов на входах 52-54 количеству единиц в регистре (см. табл. 1). Схема блока 3 запоминания начальных условий (фиг. 4) состоит из триггеров 56 начального возбуждения, инивидуального запрета 57, признаа конца распространения 58 и индикаии конца/распространения 59, элеентов ИЛИ 60, И 61, НЕ 62. На входы

блока заведения сигналы с входов 1418 ячейки и сигнал 63 с выхода блока 5. Первый выход блока 6А соединен с первым входом формирователя 4. Второй выход блока 65 соединен с вхо- j дом блока 5 .- Третий выход блока соединен с выходом 19 ячейки.

Формирователь 4 маркера (фиг. 5) состоит из элемента ИЛИ 66 и триггера индикации маркера 67. На первый tO вход элемента ИЖ заведен сигнал с выхода 64 блока 3. Входы с второго по пятый и с шестого по девятый соединены соответственно с группами выходов 29 и 30 ячейки, десятый 5 вход подключен к выходу 19 ячейки. Вход гашения триггера 67. соединен с входом 18 ячейки, единичный выход триггера соединен с выходом 34 ячейки. Блок 5 памяти направлений (фиг.6) 20 содержит триггеры 68-75 дхы восьми направлений, элементы ИЛИ 76, 77 и 78, элементы И 79 и 80, элемент 81 задержки, элемент НЕ 82. В блок поступают и из блока выводятся общие сигналы ячейки 18, 19, 26, 27 и 28. Кроме того, в блок поступают группы сигналов с выходов блоков 6 и 7 (входы 83-86 и 87-90 соответственно), Нулевые вьЛоды 91-94 и 95-98 ортогональных 68-71 и диагональных 72-75 триггеров образуют группы выходов .блока 5, сигналы с которых поступают на информационные входы формирователей 8 и 10. Единичные выходы 99-102 и 103-106 триггеров 68-71 и 72-75 со диняются с группами выходов ячейки 25 и 24 соответственно. На входы 107 и 108 блока 5 заведены сигналы с выхода 55 формирователя 2 и выхода 65 блока 3. Выход 109 блока 5 соединен с входами признака блоков 6 и 7. Выход 110 блока 5 соединен с входом 63 блока 3 и входами настройки формирователей 9 и 11. Первый вход элемента ИЛИ 78 соединен с выходом ячей ки 19. Остальные входы 111-114 и 115-118 подключены соответственно к группам входов 27 и 28 ячейки. Выход f 19 элемента ИЛИ 78 соединен с входами настройки формирователей 8 и 10. Блоки 6-11 выполнены по одной схе ме (фиг. 7) и состоят из четырех эле ментов И 120-123. Вьщелены управляющие входы: 124 - вход признака и 125 - вход настройки, - группа входо 126-129 и группа выходов 130-133.

Способ соединения блоков 6-11 с блоком 5 и общими входами и выходами ячейки описывается табл. 2.

Ячейка, входящая в состав однородной сети, составленной из однотипных ячеек, находящихся под общим управлением, при выполнении процесса распространения волны работает следующим образом.

Перед началом цикла работ на входы 13, 21 и 23 подаются управляющие сигналы, остающиеся постоянными на протяжении всего циклаi Кроме того через входы 12 производится сброс в нулевое состояние регистров всех ячеек сети.

Подготовка сети к распространению волны требует подачи сигнала сброса на входы 18 всех ячеек сети, подачи сигналов установки признаков начального возбуждения индивидуального запрета и конца распространения на входы 14, 15 и 16 определенных ячеек сети, выбранных из условий процесса распространения волны. Кроме того, через входы 12 в заранее определенные ячейки может быть занесена информация об участках трасс, построенных в предыдущих циклах работы устройства трассировки (накопление загрузки ячейки). В формирователе 2 обрабатьшается информация с выходов регистра и входов 13 ячейки. Выходной сигнал формирователя 2 является разрешающим только в том случае, если суммарное число единиц в триггерах регистра не . превышает значения, установленного с помощью сигналов на входах 13. Выходной сигнал формирователя 2 обрабатывается в блоке 5 при формировании сигнала открытия блоков 6 и 7, являющегося одним из условий прохождения через них сигналов возбуждения с входов 20 и 22. Распространение волны начинается при подаче тактирующих импульсов на входы 33 всех ячеек сети. В ячейке выбранной в качестве начальной (предварительной установкой признака на- чального возбуждения), тактирующий импульс проходит через блок 5 и формирователи 9 и 11 на выходы 31 и 32 ячейки (с учетом постоянных уровней на входах 21 и 23 - разрешения работы ортогоналей и диагоналей). Так .как выходы 31 и 32 данной ячейки соединены с соответствующими входами сигналов возбуждения 20 н 22 соседних по сети ячеек, то выходные импульсы ячейки-источника поступают на входы блоков 6 и 7 соседних ячеек сети. Прохождение си1Ч1алов возбузкдения через блоки 6 и 7 возможно только при наличии разрешающего сигнала фо мирователя 2 и отсутствии зафиксиро ванных ранее (в предыдущих тактах) в триггерах направлений блока 5 сиг налов возбуждения. Все направления, с которых были приняты через блоки 6 и 7 сигналы возбуждения.запоминают в триггерах блока 5. После приема информации в блок 5 с одного или нескольких одновременно направлений с выхода сигнала открытия блока 5 на входы признака блоков 6 и 7 подается сигнал, заКрываняций эти блоки (для предотвращения вторичного приема) , а на выход 26 ячейки передается сигнал о переходе в возбужденное сос тояние. Сигналы с вькодов блока 5 управля ет генерацией сигналов возбуждения в формирователях 9 и 11, соединенных с выходами 31 и 32 ячейки. Выходной сигнал возбуждения может быть выдан только в тех направлениях, с которых в предьщущем такте не были приняты входные сигналы возбуждения. При достижении очередным фронтом волны ячейки, в блоке 3 которой пред варительно .был установлен признак конца распространения, в блоке 3 фор мируется сигнал, свидетельствующий о том, что процесс распространения волны закончен и данная ячейка стала источником сигналов обратной связи (информация об этом выдается через выход 19 ячейки). По этому сигналу устройство управления сетью прекращают работу сети, подавая на все ячейки (через входы 17) сигнал общего -запрета. Сигналы обратной связи от ячейкиисточника ввдаются в направлении тех соседних ячеек сети, с которых на чанную ячейку поступил входной сигнал возбуждения и был зафиксирован в триггерах блока 5. В ячейках сети, не являющихся конечными для волны, принятые через входы 27 и 28 сигналы обратной связи эт соседних ячеек передаются через 5локи 5, 8 и 10 на выходы 29 и 30 ячейки, а также в формирователь 4. Зигнал маркера на выходе формирователя 4 и выходе 34 ячейки свидетельствует о том, что эта ячейка является элементом допустимого пути (одного или нескольких) между источником и стоком волны. Выходными сигналами каждой ячейки сети, служащими для ввода волновой картины в память устройства обработки сцелью выбора пути, удовлетаоряющего заданньм критериям качества (число перегибов, число перекрестий на разных слоях. Допустимое расстояние между соседними перегибами и т.д.), являются выходные сигналы 19, 24, 25, 26 и 34 ячейки. Применение предлагаемой ячейки в составе однородной сети - центральной устройства трассировки межсоединений paдйoэлekтpoннoй аппаратуры при высокой скорости моделирования волновых процессов дает возможность оперативной перестройки сети в различных конструктивно-технологических условиях проектирования соединений. Трассирующая сеть, состоящая из ячеек, построенных по предлагаемой схеме, позволяет моделировать волновые процессы в трехмерном пррстранстве (а не на плоскости), в результате чего она может использоваться при проектировании соединений, изготавливаемых, по технологиям многослойного печатного монтажа, т.е. в тех случаях, когда чербз один узел координатной сетки допускается прокладка двух и более не связанных между собой проводников. Схема ячейки позволяет оперативно изменять вид трассировочной сетки (она может быть ортогональной, диагональной, ортогонально-диагональной) , а также максимально разрешенное число перекрытий в каждом узле сетки (или число слоев). Все это ,с учетом возможности исключения части ячеек из процесса трассировки путем установки признака индивидуального запрета позволяет использовать трассирующую сеть при проектировании разнородных по технологии и конструкции монтажных плат. Преимуществом изобретения является улучшение качества и увеличение скорости процесса монтажно-коммутаионного проектирования радиоэлектроной аппаратуры.

Таблица 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка однородной трассирующей сети | 1986 |

|

SU1411729A2 |

| Устройство трассировки межсоединений радиоэлектронных схем | 1977 |

|

SU679987A1 |

| Ячейка однородной сети для моделирования процесса распространения волны при трассировке межсоединений радиоэлектронных схем | 1977 |

|

SU670934A1 |

| Устройство для обработки информации датчиков | 1980 |

|

SU955093A1 |

| Система коммутации | 1986 |

|

SU1403071A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1688229A1 |

| Устройство для преобразования временных интервалов в цифровой код | 1975 |

|

SU531124A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЭЛЕКТРОННОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1992 |

|

RU2066877C1 |

| Система коммутации | 1986 |

|

SU1410047A1 |

| Устройство для контроля электропотребления | 1988 |

|

SU1566371A1 |

1. ЯЧЕЙКА ОДНОРОДНОЙТРАССИРУЩЕЙ СЕТИ, содержащая первый приемньй блок, блок памяти направлений, формирователь маркера, ортогональный формирователь сигналов обратной е-вязи, ортогональный формирователь сигналов возбуждения, блцк запоминания начальных условий, причем информационные входы первого приемного блока соединены с группой ортогональных входов ячейки для сигналов возбуждения, выходы первого приемного блока соединены с ортогональными входами возбуждения блока памяти направлений соответственно, вход сигнала сброса блока памяти направлений сое; -кен с входом сброса ячейки, входом сброса блока запоминания -начальных условий и входом сброса формирователя маркера, первая и вторая группы ортогональных.выходов блока памяти направлений соединены с информационными входами ортогональных формирователей сигналов возбуждения и обратной связи соответственно, вторая группа выходов блока памяти направлений соединена с группой выходов ячейки запоминания ортогональных направлений, группы выходов ортогональных формирователей сигналов обратной связи и возбуждения подключены к группам вьшодов ячейки ортогональных сигналов обратной связи и сигналов возбуждения соответственно, группа выходов ортогонального формирователя сигналов обратной связи подключена к группе входов ор.тогональных сигналов обратной связи формирователя маркера соответственно, выход которого соединен с выходом ячейки сигнала маркера, выходы блока запоминания начальных условий сигналов начального возбуждения и источника обратной связи соединены с одноименными входами формирователя маркера, выход сигнала источника обратной связи блока запоминания начальных условий подключен к выходу ячейки 9 сигнала источника обратной связи,входы |сл ячейки сигналов общего запрета и установок признака начального возбуждения, признака конца распространения сигналов возбуждения и индивидуаль- . ного запрета соединены с одноименными входами блока запоминания начальных условий, отличающаяся тем, что, с целью расширения области применения за счет возможности оперативной перестройки схемы для работы с различными сетками разрешенных О5 О) направлений и переменными значениями, ограничений на число перекрестий, ячейка содержит регистр, второй nptieMHbtfi блок, диагональные формирователи сигналов обратной связи и возбуждения, формирователь сигналов разрешения работы, причем входы регистра подключены к группе информационных входов фиксации трасс ячейки, выходы регистра подключены к информационным входам формирователя сигнала разрешения работы соответственно, группа управляющих входов выбора

Примечание. В таблице указа 1Ы источники или получатели сигналов, связанных с блоками 6-11, причем цифра 5 в .ск )бках обозначает, что соединение выполняется с входом или выходом блока 5. Цифры без скобок и нумерованные группы обозначают одиночные или групповые входные и выходные сигналы ячейки.

. N. «м

Ч

«о

Сч)

-T--W-ьгч « te «

и

«э

п

t

ю

в, JL

Hti1-H-H-i -qpue.5

ff3 8i gs gs -87 68 89 ffff

F

J4.

76

26

ff4

W Ы

m105Wf03102 10}, fffG99j 9 дЗ 9 95 96 g7 дв jg

-Г&

77

108

19 /// /// //5 /At //5 ff6 //7 /f$J3

80

T,

фи.&

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Ячейка однородной трассирующей среды | 1975 |

|

SU583438A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Ячейка однородной сети для моделирования процесса распространения волны при трассировке межсоединений радиоэлектронных схем | 1977 |

|

SU670934A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-06-30—Публикация

1982-02-11—Подача