Изобретение относится к автоматике и вычислительной технике и может быть использовано в автоматизированных системах для программного управления технологическими процессами, например в системах числового программного управления производственных комплексов, роботов-манипуляторов и т.д.

Цель изобретения - сокращение объема памяти констант за счет дина мической адаптации данных, описывающих конъюнкции вычисляемой системы булевых функций.

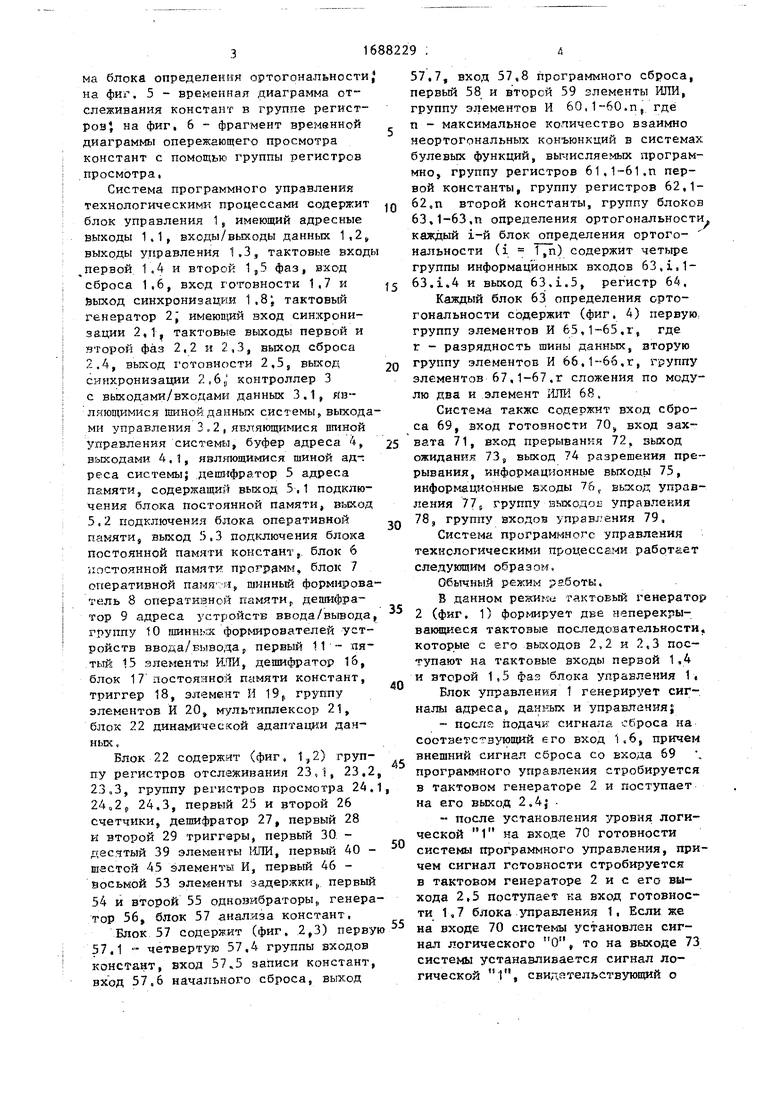

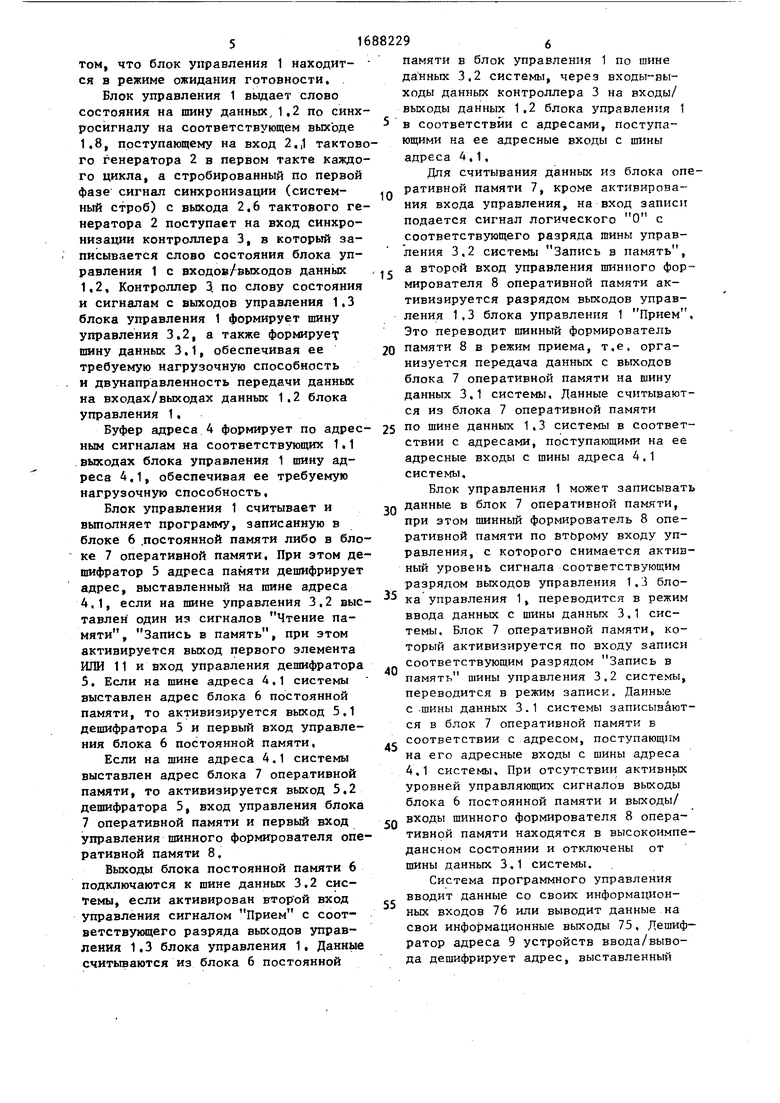

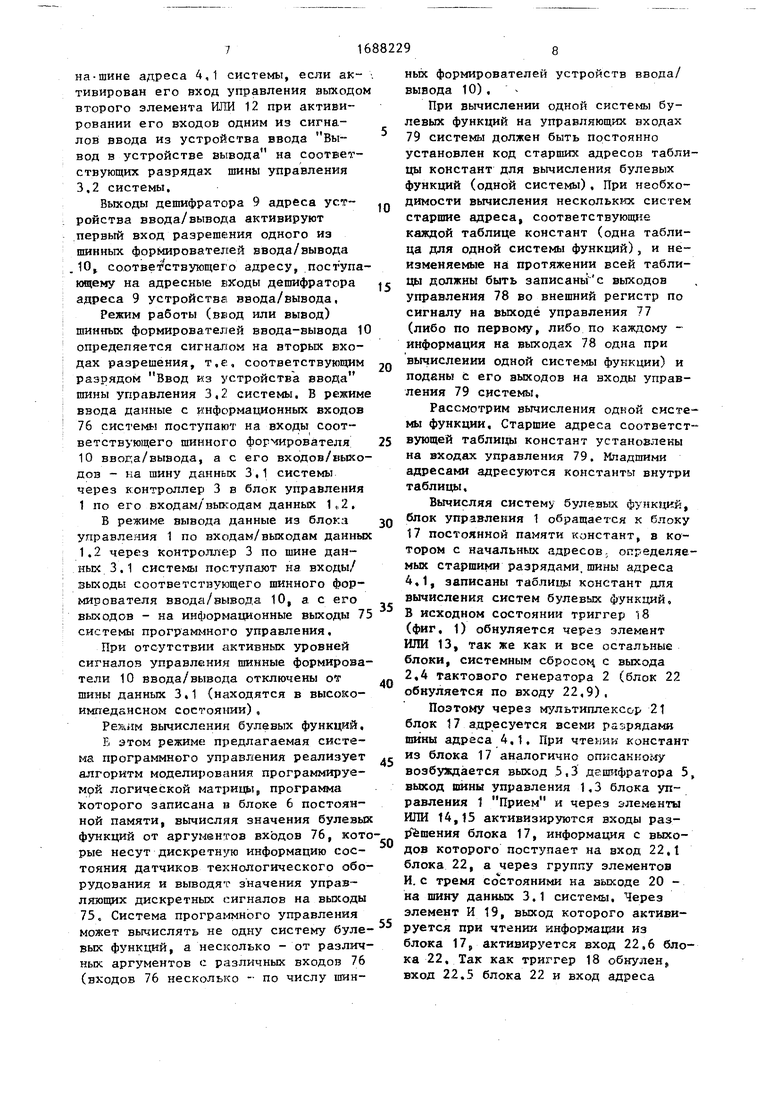

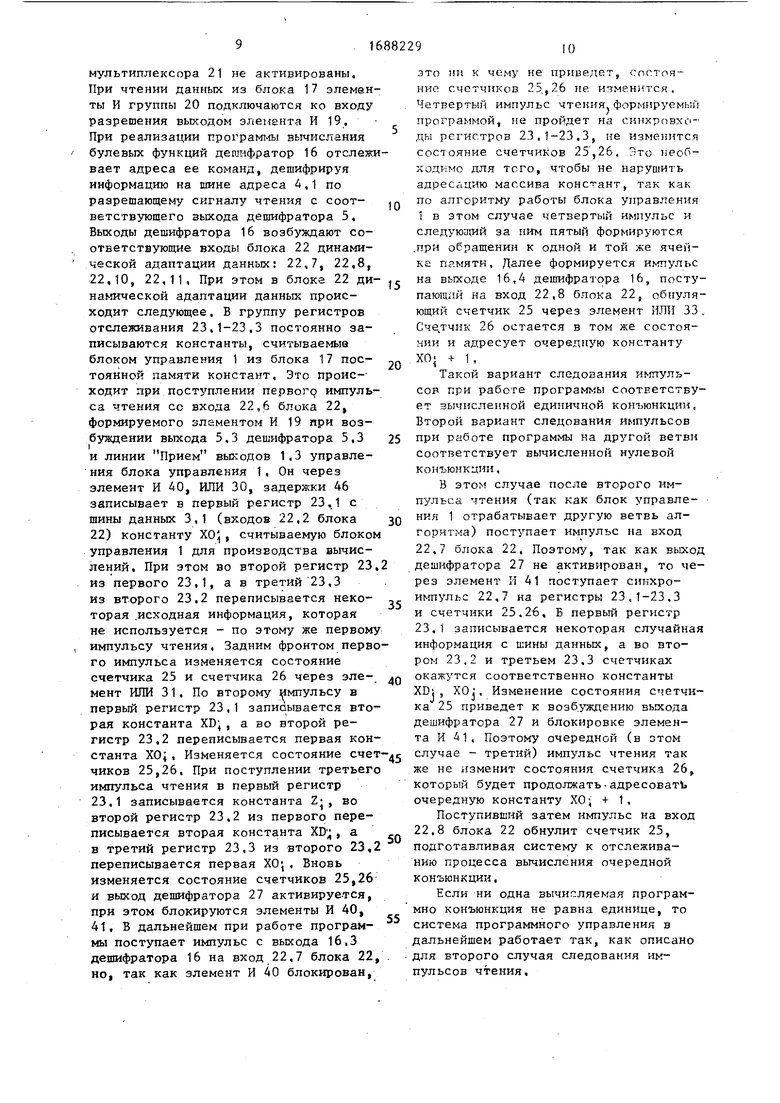

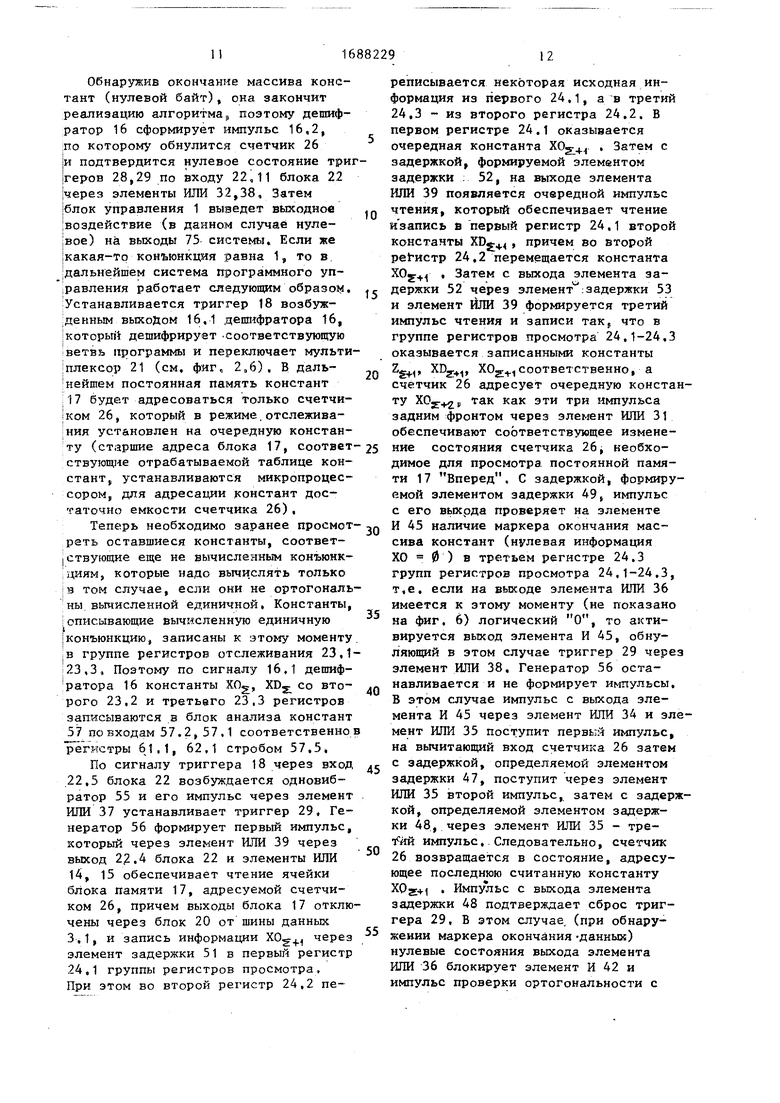

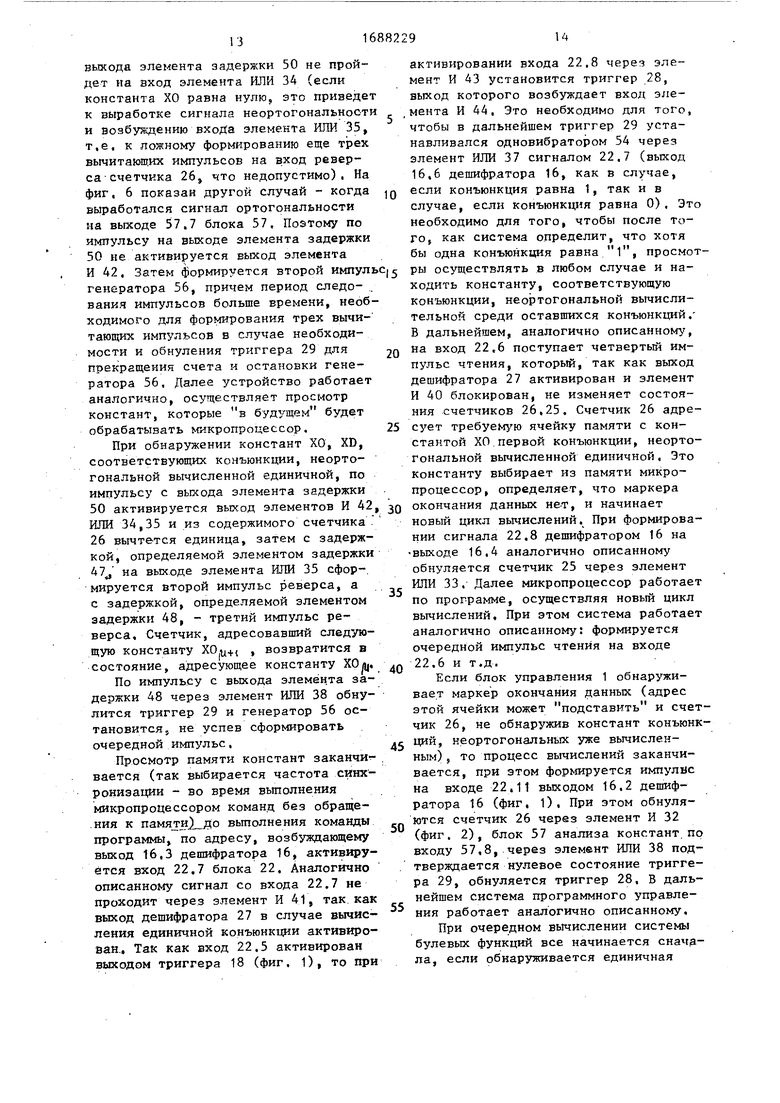

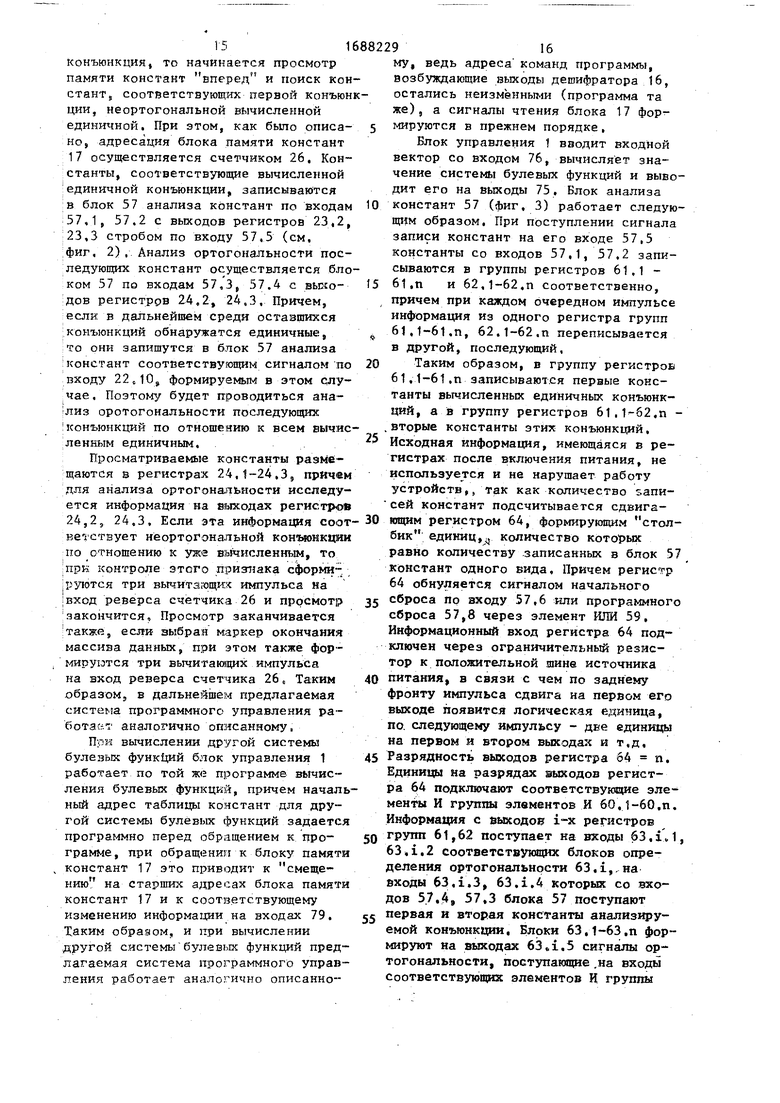

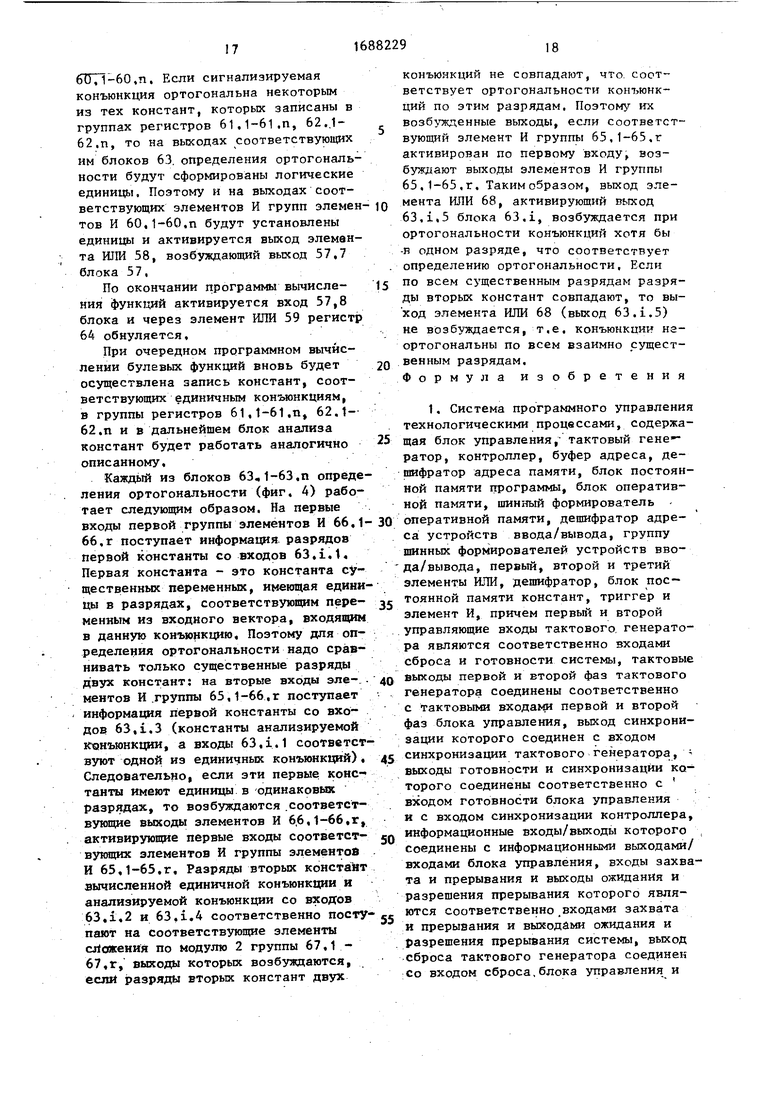

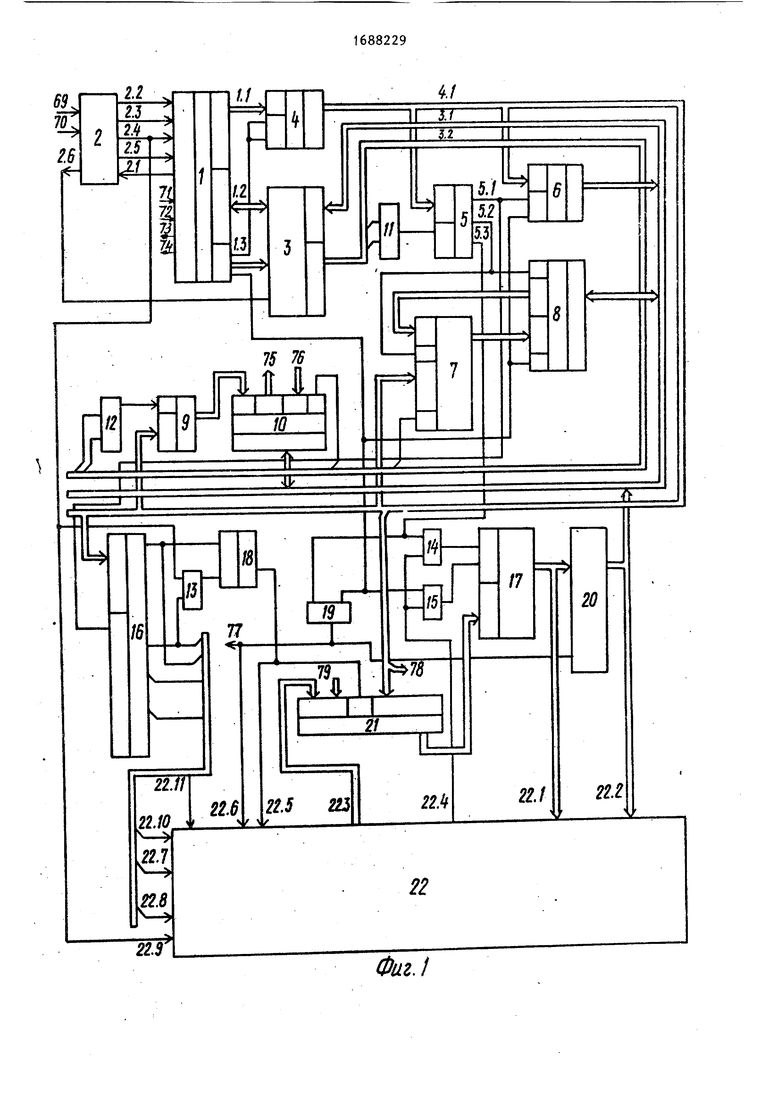

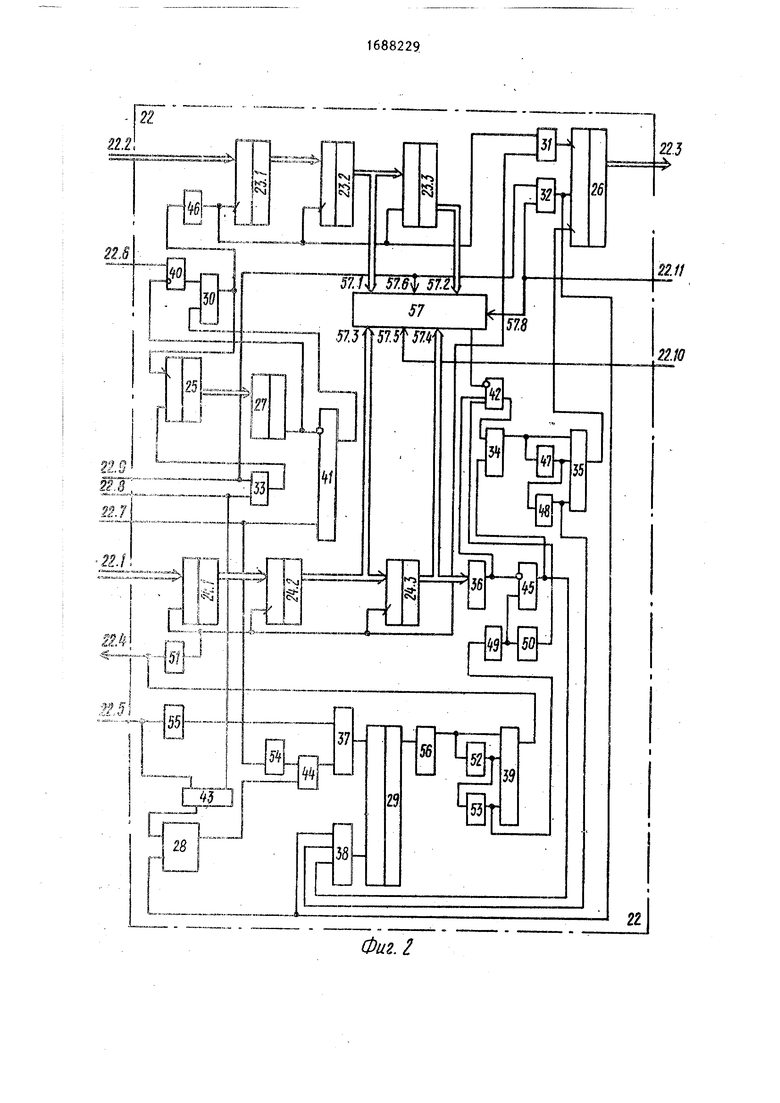

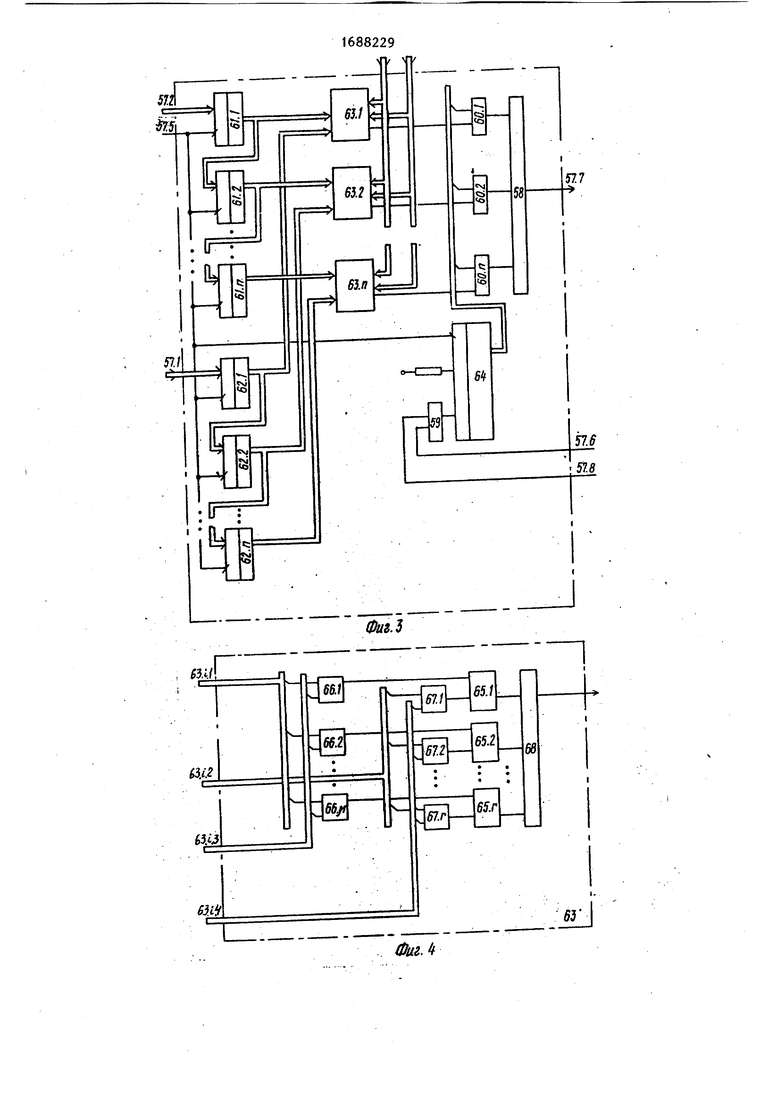

На фиг, 1 представлена функциональная схема предлагаемой системы программного управления технологическими процессами; на фиг, 2 - функцио.нальная схема блока динамической адаптации данных; на фиг. 3 - функциональная схема блока анализа констант; на фиг. 4 - функциональная схеа блока определения ортогональности, а фиг, 5 - временная диаграмма отлеживания констант в группе регистов4, на фиг, 6 - фрагмент временной иаграммы опережающего просмотра онстант с помощью группы регистров росмотра,

Система программного управления технологическими процессами содержит лок управления 1, имеющий адресные выходы 1,1, входы/выходы данных 1,2„ ыходы управления 1,3, тактовые входы ервой 1,4 и второй 1,5 фаз, вход сброса 1,6, вход готовности 1,7 и быход синхронизации 1,8 тактовый генератор 2J имекпций вход синхронизации 2,1f тактовые выходы первой и второй фаз 2,2 и 2,3, выход сброса 2.4, выход готовности 2,5, выход синхронизации 2,6, контроллер 3 с выходами/входами данных 3.1, являющимися Шиной данных системы, выходами управления 3,2, являющимися шиной управления системы, буфер адреса 4, выходами 4,1, являющимися шиной адреса системы; дешифратор 5 адреса памяти, содержащий выход 5,1 подключения блока постоянной памяти, выход 5,2 подключения блока оперативной памяти, выход 5,3 подключения блока постоянной памяти констант, блок 6 постоянной памяти программ, блок 7 оперативной памя1 п„ шинный формирова™ гель 8 оперативно памяти,, дешифратор 9 адреса устройств ввода/вывода, группу 10 шиннкх формирователей устройств ввода/выводаt первый Н - ая- тый 15 -элементы ИЛИ, дешифратор 16, блок 17 достоянной памяти констант, триггер 18, элемент И 19,, группу элементов И 20, мультиплексор 21, блок 22 динамической адаптации дачных.

Блок 22 содержат (фиг, 1,2} группу регистров отслеживания 23,1, 23,2, 23.3, группу регистров просмотра 24.1, 24„2 „ 24,3, первый 25 и второй 26 счетчики, дешифратор 27, первый 28 и второй 29 триггеры, первый 30 - десятый 39 элементы ИЛИ, первый 40 - шестой 45 элементы И, первый 46 - восьмой 53 элементы задержки,, первый 54 и второй 55 однозибраторы,, генератор 56, блок 57 анализа констант,

Блок 57 содержит (фиг. 2,3) первую 57,1 - четвертую 57,4 группы входов констант, вход 57,5 записи констант, вход 57,6 начального сброса, выход

5

0

5

0

5

0

5

0

5

57,7, вход 57,8 программного сброса, первый 58 и второй 59 элементы ИЛИ, группу элементов И 60,1-60.ns где п - максимальное копичество взаимно неортогональных конъюнкций в системах булевых функций, вычисляемых программно, группу регистров 61,1-61,п первой константы, группу регистров 62,1- 62,п второй константы, группу блоков 63,1-63,п определения ортогональности, каждый i-й блок определения ортого- нальности (i Т7п) содержит четыре группы информационных входов 63,1,1- 63.1.4 и выход 63.1.5, регистр 64,

Каждый блок 63 определения ортогональности содержит (фиг, 4) первую группу элементов И 65,1-65,г, где т - разрядность шины данных, вторую группу элементов И 66,1-66,г, группу элементов 67,1-67,г сложения по модулю два и элемент ИЛИ 68,

Система также содержит вход сброса 69, вход готовности 70, вход захвата 71, вход прерывания 72, зыход ожидания 73, выход 74 разрешения прерывания, информационные выходы 75, информационные входы 76, выход управления 77, группу выходОЕ управления 78, группу входов }правления 79,

Система программного управления технологическими процессгми работает следующим образом,

Обычный режим работы,

В данном режики тактовый генератор 2 (фиг, 1} формирует две неперекрывающиеся тактовые последовательности, которые с его выходов 2,2 и 2,3 поступают на тактовые входы первой 1,4 и второй 1,5 фаз блока управления 1«

Блок управления 1 генерирует сигналы адреса, данных и управления;

-посла подачь сигнала сброса на соответствующий его вход 1,6, причем внешний сигнал сброса со входа 69 программного управления стробируется в тактовом генераторе 2 и поступает на его выход 2,4j

-после установления уровня логической 1 на входе 70 готовности системы программного управления, причем сигнал готовности стробируетск

в тактовом генераторе 2 и с его выхода 2,5 поступает ка вход готовности 1,7 блока управления 1, Если же на входе 70 системы установлен сигнал логического О, то на выходе 73 системы устанавливается сигнал логической , свидетельствующий о

том, что блок управления 1 находит- ся в режиме ожидания готовности.

Блок управления 1 выдает слово состояния на шину данных, 1,2 по синхросигналу на соответствующем выходе 1.8, поступающему на вход 2, ,1 тактового генератора 2 в первом такте каждого цикла, а стробированный по первой фазе сигнал синхронизации (системный строб) с выхода 2,6 тактового генератора 2 поступает на вход синхронизации контроллера 3, в который записывается слово состояния блока управления 1 с входов/выходов данных 1,2, Контроллер 3, по слову состояния и сигналам с выходов управления 1,3 блока управления 1 формирует шину управления 3.2, а также формирует шину данных 3.1, обеспечивая ее требуемую нагрузочную способность и двунаправленность передачи данных на входах/выходах данных 1.2 блока управления 1,

памяти в блок управления 1 по шине данных 3.2 системы, через входы-выходы данных контроллера 3 на входы/ выходы данных 1.2 блока управления 1 в соответствии с адресами, поступающими на ее адресные входы с шины адреса 4.1,

Для считывания данных из блока оперативной памяти 7, кроме актпвирова15

10

ния входа управления, на вход записи

подается сигнал логического О с соответствующего разряда тины управления 3,2 системы Запись в память, а второй вход управления шинного формирователя 8 оперативной памяти активизируется разрядом выходов управления 1,3 блока управления 1 Прием, Это переводит шинный формирователь 2Q памяти 8 в режим приема, т.е. организуется передача данных с выходов блока 7 оперативной памяти на шину данных 3,1 системы. Данные считываются из блока 7 оперативной памяти

Буфер адреса 4 формирует по адрес- 25 по шине данных 1.3 системы в соответ

6882296

памяти в блок управления 1 по шине данных 3.2 системы, через входы-выходы данных контроллера 3 на входы/ выходы данных 1.2 блока управления 1 в соответствии с адресами, поступающими на ее адресные входы с шины адреса 4.1,

Для считывания данных из блока оперативной памяти 7, кроме актпвирова15

10

ния входа управления, на вход записи

подается сигнал логического О с соответствующего разряда тины управления 3,2 системы Запись в память, а второй вход управления шинного формирователя 8 оперативной памяти активизируется разрядом выходов управления 1,3 блока управления 1 Прием, Это переводит шинный формирователь 2Q памяти 8 в режим приема, т.е. организуется передача данных с выходов блока 7 оперативной памяти на шину данных 3,1 системы. Данные считываются из блока 7 оперативной памяти

| название | год | авторы | номер документа |

|---|---|---|---|

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1751772A1 |

| Программируемое логическое устройство | 1991 |

|

SU1777133A1 |

| Устройство для программного управления технологическим оборудованием | 1987 |

|

SU1476434A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА В МИКРОЭВМ ДИСКРЕТНЫХ СИГНАЛОВ | 1990 |

|

RU2007751C1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1988 |

|

SU1608679A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1786482A1 |

| Система для программного управления электроавтоматикой | 1988 |

|

SU1532899A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1988 |

|

SU1594554A1 |

| Устройство для моделирования конечных автоматов | 1980 |

|

SU955080A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в автоматизированных системах для программного управления технологическими процес- сами. Цель изобретения - сокращение . объема памяти констант за счет динамической адаптации данных, описывающих конъюнкции вычисляемой системы улевых функций. Поставленная цель достигается тем, что в известное .устройство, содержащее блок управления, тактовый генератор, контроллер, буфер адреса, дешифратор адреса памяти, блок постоянной памяти, блок оперативной памяти, шинный формирователь оперативной памяти, дешифратор адреса устройств ввода/вывода, группу шинных формирователей уст- ройств ввода/вывода, первый-третий элементы ИЛИ, дешифратор, блок постоянной памяти констант, триггер и элемент И, дополнительно введены блок динамической адаптации данных, четвертый и пятый элементы ИЛИ, группа элементов И и мультиплексор. Введение новых элементов позволяет осуществлять опережающий просмотр констант в блоке постоянной памяти констант без нарушений информации на шине данных, позволяет отключать младшие разряды постоянной памяти констант от младших разрядов шины адреса системы и адресовать ее адаптивно в режиме динамической адаптации данных, 2 з.п. ф-лы, 6 ил. (Л с& оо 00 1C ю со

ным сигналам на соответствующих 1,1 выходах блока управления 1 шину адреса 4,1, обеспечивая ее требуемую нагрузочную способность.

Блок управления 1 считывает и выполняет программу, записанную в блоке 6 .постоянной памяти либо в блоке 7 оперативной памяти, При этом дешифратор 5 адреса памяти дешифрирует адрес, выставленный на шине адреса

30

ствии с адресами, поступающими на ее адресные входы с шины адреса 4.1 системы,

Блок управления 1 может записывать данные в блок 7 оперативной памяти, при этом шинный формирователь 8 оперативной памяти по второму входу управления, с которого снимается активный уровень сигнала соответствующим разрядом выходов управления 1,3 бло4.1, если на шине управления 3,2 вые- 35 ка управления 1, переводится в режим

тавлен один из сигналов Чтение памяти, Запись в память, при этом активируется выход первого элемента ИЛИ 11 и вход управления дешифратора 5. Если на шине адреса 4,1 системы выставлен адрес блока 6 постоянной памяти, то активизируется выход 5,1 дешифратора 5 и первый вход управления блока 6 постоянной памяти,

Если на шине адреса 4.1 системы выставлен адрес блока 7 оперативной памяти, то активизируется выход 5,2 дешифратора 5, вход управления блока 7 оперативной памяти и первый вход управления шинного формирователя оперативной памяти 8,

Выходы блока постоянной памяти 6 подключаются к шине данных 3,2 системы, если активирован второй вход управления сигналом Прием с соответствующего разряда выходов управления 1.3 блока управления 1. Данные считываются из блока б постоянной

40

45

50

55

ввода данных с шины данных 3.1 системы. Блок 7 оперативной памяти, который активизируется по входу записи соответствующим разрядом Запись в память шины управления 3,2 системы, переводится в режим записи. Данные с шины данных 3.1 системы записываются в блок 7 оперативной памяти ъ соответствии с адресом, поступающим на его адресные входы с шины адреса 4,1 системы. При отсутствии активных уровней управляющих сигналов выходы блока 6 постоянной памяти и выходы/ входы шинного формирователя 8 оперативной памяти находятся в высокоимпе- дансном состоянии и отключены от шины данных 3,1 системы.

Система программного управления вводит данные со своих информационных входов 76 или выводит данные на свои информационные выходы 75, Дешифратор адреса 9 устройств ввода/вывода дешифрирует адрес, выставленный

ствии с адресами, поступающими на ее адресные входы с шины адреса 4.1 системы,

Блок управления 1 может записывать данные в блок 7 оперативной памяти, при этом шинный формирователь 8 оперативной памяти по второму входу управления, с которого снимается активный уровень сигнала соответствующим разрядом выходов управления 1,3 блока управления 1, переводится в режим

ка управления 1, переводится в режим

ввода данных с шины данных 3.1 системы. Блок 7 оперативной памяти, который активизируется по входу записи соответствующим разрядом Запись в память шины управления 3,2 системы, переводится в режим записи. Данные с шины данных 3.1 системы записываются в блок 7 оперативной памяти ъ соответствии с адресом, поступающим на его адресные входы с шины адреса 4,1 системы. При отсутствии активных уровней управляющих сигналов выходы блока 6 постоянной памяти и выходы/ входы шинного формирователя 8 оперативной памяти находятся в высокоимпе- дансном состоянии и отключены от шины данных 3,1 системы.

Система программного управления вводит данные со своих информационных входов 76 или выводит данные на свои информационные выходы 75, Дешифратор адреса 9 устройств ввода/вывода дешифрирует адрес, выставленный

на-шине адреса 4,1 системы, если активирован его вход управления выходом второго элемента ИЛИ 12 при активировании его входов одним из сигналов ввода из устройства ввода Вывод в устройстве вывода на соответствующих разрядах шины управления 3,2 системы.

Выходы дешифратора 9 адреса устройства ввода/вывода активируют первый вход разрешения одного из шинных формирователей ввода/вывода .10, соответствующего адресу, поступающему на адресные входы дешифратора адреса 9 устройства ввода/вывода,

Режим работы (ввод или вывод) шинных формирователей ввода-вывода 10 определяется сигналом на вторых входах разрешения, т.е. соответствующим разрядом Ввод из устройства ввода шины управления 3,2 системы, В режиме ввода данные с информационных входов 76 системы поступают на входы соответствующего шинного формирователя 10 ввода/вывода, а с его входов/выходов - на шину данных 3,1 системы через контроллер 3 в блок управления 1 по его входам/выходам данных 1,2.

В режиме вывода данные из блока управления 1 по входам/выходам данных 1.2 через контроллер 3 по шине данных 3.1 системы поступают на входы/ выходы соответствующего шинного формирователя ввода/вывода 10, а с его выходов - на информационные выходы 75 системы программного управления,

При отсутствии активных уровней сигналов управления шинные формирователи 10 ввода/вывода отключены от шины данных 3,1 (находятся в высоко- импедансном состоянии),

Режим вычисления булевых функций,

Г, этом режиме предлагаемая система программного управления реализует алгоритм моделирования программируемой логической матрицы, программа которого записана и блоке 6 постоянной памяти, вычислил значения булевых функций от аргументов входов 76, которые несут дискретную информацию состояния датчиков технологического оборудования и выводят значения управляющих дискретных сигналов на выходы 75, Система программного управления может вычислять не одну систему булевых функций, а несколько - от различных аргументов с различных входов 76 (входов 76 несколько - по числу шин

0

5

0

5

0

5

0

5

ных формирователей устройств ввода/ вывода 10),

При вычислении одной системы булевых функций на управляющих входах 79 системы должен быть постоянно установлен код старших адресов таблицы констант для вычисления булевых функций (одной системы), При необходимости вычисления нескольких систем старшие адреса, соответствующие каждой таблице констант (одна таблица для одной системы функций), и неизменяемые на протяжении всей таблицы должны быть записанное выходов управления 78 во внешний регистр по сигналу на выходе управления 77 (либо по первому, либо по каждому - информация на выходах 78 одна при вычислении одной системы функции) и поданы с его выходов на входы управления 79 системы.

Рассмотрим вычисления одной системы функции. Старшие адреса соответствующей таблицы констант установлены на входах управления 79. Младшими адресами адресуются константы внутри таблицы,

Вычисляя систему булевых ф нкций, блок управления 1 обращается к блоку 17 постоянной памяти констант, в котором с начальных адресов определяемых старшими разрядами, шины адреса 4,1, записаны таблицы констант для вычисления систем булевых функций, В исходном состоянии триггер 18 (фиг. 1) обнуляется через элемент ИЛИ 13, так же как и все остальные блоки, системным сбросом, с выхода 2,4 тактового генератора 2 (блок 22 обнуляется по входу 22,9),

Поэтому через мультиплексор 21 блок 17 адресуется всеми разрядами шины адреса 4,1, При чтении констант из блока 17 аналогично описанному возбуждается выход 5,3 дешифратора 5, выход шины управления 1,3 блока управления 1 Прием и через элементы ИЛИ 14,15 активизируются входы раз- р ёшения блока 17, информация с выходов которого поступает на вход 22,t блока 22, а через группу элементов И. с тремя со стояними на выходе 20 - на шину данных 3.1 системы. Через элемент И 19, выход которого активируется при чтении информации из блока 17, активируется вход 22.6 блока 22, Так как триггер 18 обнулен, вход 22.5 блока 22 и вход адреса

мультиплексора 21 не активированы. При чтении данных из блока 17 элементы И группы 20 подключаются ко входу разрешения выходом элемента И 19. При реализации программы вычисления булевых функций дешифратор 16 отслеживает адреса ее команд, дешифрируя информацию на шине адреса 4,1 по разрешающему сигналу чтения с соот- ветствуюшего выхода дешифратора 5, Выходы дешифратора 16 возбуждают соответствующие входы блока 22 динамической адаптации данных: 22,7, 22,8, 22,10, 22,11, При этом в блоке 22 ди- намической адаптации данных происходит следующее. В группу регистров отслеживания 23.1-23,3 постоянно записываются константы, считываемые

блоком управления 1 из блока 17 пос

тоянной памяти констант. Это происходит при поступлении первогр импульса чтения со входа 22,6 блока 22, формируемого элементом И 19 при возбуждении выхода 5,3 дешифратора 5,3 и линии Прием выходов 1,3 управления блока управления 1, Он через элемент И 40, ИЛИ 30, задержки 46 записывает в первый регистр 23,1 с шины данных 3,1 (входов 22,2 блока 22) константу ХО}, считываемую блоком управления 1 для производства вычислений. При этом во второй регистр 23, из первого 23,1, а в третий 23,3 из второго 23.2 переписывается неко- торая исходная информация, которая не используется - по этому же первому импульсу чтения, Задним фронтом первого импульса изменяется состояние счетчика 25 и счетчика 26 через эле- мент ИЛИ 31, По второму импульсу в первый регистр 23,1 записывается вторая константа XDj, а во второй регистр 23,2 переписывается первая константа ХО;, Изменяется состояние счет чиков 25,26, При поступлении третьего импульса чтения в первый регистр 23.1 записывается константа Z-, во второй регистр 23.2 из первого переписывается вторая константа XD;; , а в третий регистр 23,3 из второго 23,2 переписывается первая ХО;, Вновь изменяется состояние счетчиков 25,26 и выход дешифратора 27 активируется, при этом блокируются элементы И 40, 41, В дальнейшем при работе программы поступает импульс с выхода 16,3 дешифратора 16 на вход 22.7 блока 22, но, так как элемент И 40 блокирован,

„ 5

0

5 0 , д

5

это ни к чему не приведет, состояние счетчиков 25., 26 не изменится. Четвертый импульс чтения.формируемый программой, не пройдет на синхровхо- ды регистров 23.1-23.3, не изменится состояние счетчиков 25,26. то необ- ходкмо для тгго, чтобы не нарушить адресацию массива констант, так как по алгоритму работы блока управления 1 в этом случае четвертый импульс и следующий за ним пятый формируются .при обращении к одной и той же ячейка памяти. Далее формируется импульс на выходе 16,4 дешифратора 16, поступающая на вход 22,8 блока 22, обнуляющий счетчик 25 через элемент ИЛИ 33, Счечтчнк 26 остается в том же состоянии и адресует очередную константу Х0« + 1,

Такой вариант следования импульсов при работе программы соответствует вычисленной единичной конъюнкции, Второй вариант следования импульсов при работе программы на другой ветви соответствует вычисленной нулевой конъюнкции,

В этом случае после второго импульса чтения (так как блок управления 1 отрабатывает другую ветвь алгоритма) поступает импульс на вход

и счетчики 25.26, В первый регистр 23,1 записывается некоторая случайная информация с шины данных, а во втором 23,2 и третьем 23,3 счетчиках окажутся соответственно константы XDi, ХО;. Изменение состояния счетчика 25 приведет к возбуждению выхода дешифратора 27 и блокировке элемента И 41, Поэтому очередной (в этом случае - третий) импульс чтения так же не изменит состояния счетчика 26, который будет продолжать-адресовать очередную константу ХО; + 1,

Поступивший затем импульс на вход

Если ни одна вычисляемая программно конъюнкция не равна единице, то система программного управления в дальнейшем работает так, как описано для второго случая следования импульсов чтения.

Обнаружив окончание массива констант (нулевой байт), она закончит реализацию алгоритма„ поэтому дешифратор 16 сформирует импульс 16,2, по которому обнулится счетчик 26 и подтвердится нулевое состояние тригеров 28,29 по входу 22,11 блока 22 через элементы ИЛИ 32,38, Затем блок управления 1 выведет выходное воздействие (в данном случае нулевое) на выходы 75 системы. Если же какая-то конъюнкция равна 1, то в дальнейшем система программного управления работает следующим образом. Устанавливается триггер 18 возбужденным выходом 16,1 дешифратора 16, который дешифрирует соответствующую ветвь программы и переключает мультиплексор 21 (см, фиг, 2„б) . В дальнейшем постоянная память констант 17 будет адресоваться только счетчиком 26, который в режиме отслеживания установлен на очередную константу (старшие адреса бпока 17, соответствующие отрабатываемой таблице констант, устанавливаются микропроцессором, для адресации констант достаточно емкости счетчика 26),

Теперь необходимо заранее просмотреть оставшиеся константы, соответ- Iствугощие еще не вычисленным конъюнкциям, которые надо вычислять только в том случае, если они не ортогональны вычисленной единичной. Константы,

описывающие вычисленную единичную 1 конъюнкцию, записаны к этому моменту

в группе регистров отслеживания 23,1 23,3, Поэтому по сигналу 16,1 дешифратора 16 константы ХО, XD со второго 23,2 и третьего 23.3 регистров записываются в блок анализа констант 57 по входам 57.2, 57.1 соответственно рГегиетры 61,1, 62,1 стробом 57,5,

По сигналу триггера 18 через вход 22,5 блока 22 возбуждается одновиб- ратор 55 и его импульс через элемент ИЛИ 37 устанавливает триггер 29, Генератор 56 формирует первый импульс, который через элемент ИЛИ 39 через выход 22.4 блока 22 и элементы ИЛИ 14, 15 обеспечивает чтение ячейки блока памяти 17, адресуемой счетчиком 26, причем выходы блока 17 отключены через блок 20 от шины данных 3.1, и запись информации X0g+1 через элемент задержки 51 в первый регистр 24,1 группы регистров просмотра, При этом во второй регистр 24,2 пе

5

0

5

0

5

0

5

0

5

реписывается некоторая исходная информация из первого 24,1, а в третий 24,3 - из второго регистра 24.2. В первом регистре 24.1 оказывается очередная константа . Затем с задержкой, формируемой элементом задержки 52, на выходе элемента ИЛИ 39 появляется очередной импульс чтения, который обеспечивает чтение и запись в первый регистр 24,1 второй константы XDg.44 , причем во второй регистр 24,2 перемещается константа Затем с выхода элемента задержки 52 через элемент 1 задержки 53 и элемент ИЛИ 39 формируется третий импульс чтения и записи так, что в группе регистров просмотра 24,1-24.3 оказывается записанными константы Zg+1, XDg-, X0g-+1 соответственно, а счетчик 26 адресует очередную константу XOjr+2,, так как эти три импУльса задним фронтом через элемент ИЛИ 31 обеспечивают соответствующее изменение состояния счетчика 26, необходимое для просмотра постоянной памяти 17 Вперед, С задержкой, формируемой элементом задержки 491 импульс с его выхрда проверяет на элементе И 45 наличие маркера окончания массива констант (нулевая информация ХО 0 ) в третьем регистре 24,3 групп регистров просмотра 24,1-24,3, т.е. если на выходе элемента ИЛИ 36 имеется к этому моменту (не показано на фиг. 6) логический О, то активируется выход элемента И 45, обнуляющий в этом случае триггер 29 через элемент ИЛИ 38, Генератор 56 останавливается и не формирует импульсы, В этом случае импульс с выхода элемента И 45 через элемент ИЛИ 34 и элемент ИЛИ 35 поступит первь импульс, на вычитающий вход счетчика 26 затем с задержкой, определяемой элементом задержки 47, поступит через элемент ИЛИ 35 второй импульс, затем с задержкой, определяемой элементом задержки 48, через элемент ИЛИ 35 - тре- импульс. Следовательно, счетчик 26 возвращается в состояние, адресующее последнюю считанную константу XOgr-м . ИмпуЪьс с выхода элемента задержки 48 подтверждает сброс триггера 29, В этом случае (при обнаружении маркера окончания -данных) нулевые состояния выхода элемента ИЛИ 36 блокирует элемент И 42 и импульс проверки ортогональности с

выхода элемента задержки 50 не пройдет на вход элемента ИЛИ 34 (если константа ХО равна нулю, это приведе к выработке сигнала неортогональност и возбуждению входа элемента ИЛИ 35, т.е. к ложному формированию еще трех вычитаюших импульсов на вход реверса счетчика 26, что недопустимо), На фиг, 6 показан другой случай - когда выработался сигнал ортогональности на выходе 57.7 блока 57, Поэтому по импульсу на выходе элемента задержки 50 не активируется выход элемента И 42. Затем формируется второй импул генератора 56, причем период следования импульсов больше времени, необходимого для формирования трех вычитающих импульсов в случае необходимости и обнуления триггера 29 для прекращения счета и остановки генератора 56, Далее устройство работает аналогично, осуществляет просмотр констант, которые в будущем будет обрабатывать микропроцессор.

При обнаружении констант ХО, XD, соответствующих конъюнкции, неортогональной вычисленной единичной, по импульсу с выхода элемента задержки 50 активируется выход элементов И 42 ИЛИ 34,35 и из содержимого счетчика 26 вычтется единица, затем с задержкой, определяемой элементом задержки 47, на выходе элемента ИЛИ 35 сформируется второй импульс реверса, а с задержкой, определяемой элементом задержки 48, - третий импульс реверса. Счетчик, адресовавший следующую константу ХОд., , возвратится в состояние, адресующее константу Х0д|.

По импульсу с выхода элемента задержки 48 через элемент ИЛИ 38 обну- лится триггер 29 и генератор 56 остановится s не успев сформировать очередной импульс,

Просмотр памяти констант заканчивается (так выбирается частота синхронизации - во время выполнения микропроцессором команд без обращения к памяти)до выполнения команды программы, по адресу, возбуждающему выход 16,3 дешифратора 16, активируется вход 22.7 блока 22. Аналогично описанному сигнал со входа 22.7 не проходит через элемент И 41, так как выход дешифратора 27 в случае вычисления единичной конъюнкции активирован. Так как вход 22.5 активирован выходом триггера 18 (фиг. 1), то при

Q 0 5

0 Q

5

5

активировании входа 22.8 через элемент И 43 установится триггер 28, выход которого возбуждает вход эле- ,мента И 44, Это необходимо для того, чтобы в дальнейшем триггер 29 устанавливался одновибратором 54 через элемент ИЛИ 37 сигналом 22.7 (выход 16,6 дешифратора 16, как в случае, если конъюнкция равна 1, так и в случае, если конъюнкция равна 0), Это необходимо для того, чтобы после того, как система определит, что хотя бы одна конъюнкция равна 1, просмотры осуществлять в любом случае и находить константу, соответствующую конъюнкции, неортогональной вычислительной среди оставшихся конъюнкций. В дальнейшем, аналогично описанному, на вход 22,6 поступает четвертый импульс чтения, который, так как выход дешифратора 27 активирован и элемент И 40 блокирован, не изменяет состояния счетчиков 26,25, Счетчик 26 адресует требуемую ячейку памяти с константой ХО первой конъюнкции, неортогональной вычисленной единичной, Это константу выбирает из памяти микропроцессор, определяет, что маркера окончания данных нет, и начинает новый цикл вычислений. При формировании сигнала 22,8 дешифратором 16 на выходе 16,4 аналогично описанному обнуляется счетчик 25 через элемент ИЛИ 33. Далее микропроцессор работает по программе, осуществляя новый цикл вычислений. При этом система работает аналогично описанному: формируется очередной импульс чтения на входе 22.6 и т.д.

Если блок управления 1 обнаруживает маркер окончания данных (адрес этой ячейки может подставить и счетчик 26, не обнаружив констант конъюнкций, неортогональных уже вычисленным) , то процесс вычислений заканчивается, при этом формируется импулвс на входе 22,11 выходом 16.2 дешифратора 16 (фиг, 1), При этом обнуляются счетчик 26 через элемент И 32 (фиг. 2), блок 57 анализа констант по входу 57,8, через элемент ИЛИ 38 подтверждается нулевое состояние триггера 29, обнуляется триггер 28, В дальнейшем система программного управления работает аналогично описанному.

При очередном вычислении системы булевых функций все начинается сначала, если обнаруживается единичная

151

конъюнкция, то начинается просмотр памяти констант вперед и поиск констант, соответствующих первой конъюнции, неортогональной вычисленной единичной. При этом, как было описа- но, адресация блока памяти констант 17 осуществляется счетчиком 26, Константы, соответствующие вычисленной единичной конъюнкции„ записываются в блок 57 анализа констант по входам 57,1, 57.2 с выходов регистров 23,2, 23,3 стробом по входу 57,5 (см, фиг, 2). Анализ ортогональности последующих констант осуществляется блоком 57 по входам 57,3, 57.4 с вьссо- дов регистров 24,2, 24,3, Причем, если в дальнейшем среди оставшихся конъюнкций обнаружатся единичные, то они запишутся в бпок 57 анализа констант соответствующим сигналом по входу 22„10,, формируемым в этом случае. Поэтому будет проводиться анализ оротогональности последующих конъюнкций по отношению к всем вычисленным единичным.

Просматриваемые константы размещаются в регистрах 24,1-24,3, причем для анализа ортогональности исследуется информация на выходах регистров 24,2Э 24,3, Если эта информация соот вечствует неортогональной конъюнкции но отношению к уже вычисленным, то прк контроле этого признака сформируются три вычитающих импульса на вход реверса счетчика 26 и просмотр закончится, Просмотр заканчивается также, если выбран маркер окончания массива данных, при этом также формируются три вычитающих импульса на вход реверса счетчика 26, Таким образом, в дальнейшего предлагаемая система программного управления работа;- : аналогично описанному,

При вычислении другой системы булевых функций блок управления 1 работает по той же программе вычисления булевых функций, причем начальный адрес таблицы констант для другой системы булевых функций задается программно перед обращением к про- грамме, при обращении к блоку памяти констант 17 это приводит к смещению на старших адресах блока памяти констант 17 и к соответствующему изменению информации на входах 79, Таким образом, и при вычислении другой системы булевых функций предлагаемая система программного управления работает аналогично описанно

9

16

му, ведь адреса команд программы, возбуждающие выходы дешифратора 16, остались неизменными (программа та же), а сигналы чтения блока 17 формируются в прежнем порядке,

Блок управления 1 вводит входной вектор со входом 76, вычисляет значение системы булевых функций и выводит его на выходы 75, Блок анализа констант 57 (фиг, 3) работает следующим образом, При поступлении сигнала записи констант на его входе 57,5 константы со входов 57,1, 57,2 записываются в группы регистров 61,1 - 61,п и 62,1-62,п соответственно, причем при каждом очередном импульсе информация из одного регистра групп 61.1-61.П, 62.1-62.ti переписывается в другой, последующий,

Таким образом, в группу регистров 61,1-61,п записываются первые константы вычисленных единичных конъюнкций, а в группу регистров 61.1-62.п .вторые константы этих конъюнкций, Исходная информация, имеющаяся в регистрах после включения питания, не используется и не нарушает работу устройств,, так как количество запи сей констант подсчитывается сдвигающим регистром 64, формирующим столбик единиц, количество которых равно количеству записанных в блок 5 констант одного вида, Причем регистр 64 обнуляется сигналом начального сброса по входу 57,6 или программног сброса 57,8 через элемент ИЛИ 59, Информационный вход регистра 64 подключен через ограничительный резистор к положительной шине источника питания, в связи с чем по заднему фронту импульса сдвига на первом его выходе появится логическая единица, по. следующему импульсу - две единицы на первом и втором выходах и т.д. Разрядность вькодов регистра 64 п. Единицы на разрядах выходов регистра 64 подключают соответствующие элементы И группы элементов И 60,1-60.п Информация с выходов 1-х регистров групп 61,62 поступает на входы 63.1. 63.1.2 соответствующих блоков определения ортогональности 63,1,, на входы 63.1.3, 63.1.4 которых со входов 5.7.4, 57,3 блока 57 поступают первая и вторая константы анализируемой конъюнкции, Блоки 63,1-63,п формируют на выходах 63«1,5 сигналы ортогональности, поступающие .на входы соответствующих элементов И группы

бТГЛ-бО.п, Если сигнализируемая конъюнкция ортогональна некоторым из тех констант, которых записаны в группах регистров 61,1-61,п, 62..1- 62.п, то на выходах соответствующих им блоков 63. определения ортогональности будут сформированы логические единицы. Поэтому и на выходах соответствующих элементов И групп элементов И 60.1-60.п будут установлены единицы и активируется выход элемента ИЛИ 58, возбуждающий выход 57,7 блока 57,

По окончании программы вычисления функций активируется вход 57,8 блока и через элемент ИЛИ 59 регистр 64 обнуляется,

При очередном программном вычислении булевых функций вновь будет осуществлена запись констант, соответствующих единичным конъюнкциям, в группы регистров 61,1-61,и, 62.1- 62.п и в дальнейшем блок анализа констант будет работать аналогично описанному.

Каждый из блоков 63.1-63.п определения ортогональности (фиг. 4) работает следующим образом. На первые входы первой группы элементов И 66,1 66,г поступает информация разрядов первой константы со входов 63,1,1, Первая константа - это константа существенных переменных, имеющая единицы в разрядах, соответствующим переменным из входного вектора, входящим в данную конъюнкцию. Поэтому для определения ортогональности надо сравнивать только существенные разряды двух констант: на вторые входы эле- ментов И группы 65,1-66,г поступает информация первой константы со входов 63,1.3 (константы анализируемой конъюнкции, а входы 63,1.1 соответствуют одной из единичных конъюнкций), Следовательно, если эти первые константы имеют единицы в одинаковых разрядах, то возбуждаются .соответствующие выходы элементов И 6,6,1-66,гt активирующие первые входы соответствующих элементов И группы элементов И 65,1-65.г. Разряды вторых констант вычисленной единичной конъюнкции и анализируемой конъюнкции со входов 63,1,2 и 63.1.4 соответственно поступают на соответствующие элементы сложения по модулю 2 группы 67,1 - 67,г, выходы которых возбуждаются, если разряды вторых констант двух

конъюнкций не совпадают, что соответствует ортогональности конъюнкций по этим разрядам. Поэтому их возбужденные выходы, если соответствующий элемент И группы 65,1-65,г активирован по первому входу, возбуждают выходы элементов И группы 65,1-65,г. Таким образом, выход элеQ мента ИЛИ 68, активирующий выход 63,1,5 блока 63,1, возбуждается при ортогональности конъюнкций хотя бы -в одном разряде, что соответствует . определению ортогональности. Если

5 по всем существенным разрядам разряды вторых констант совпадают, то выход элемента ИЛИ 68 (выход 63.1.5) не возбуждается, т.е. конъюнкции нг- ортогональны по всем взаимно сущест0 венным разрядам,

Формула изобретения

г тоянной памяти констант, триггер и элемент И, причем первый и второй управляющие входы тактового генератора являются соответственно входами сброса и готовности системы, тактовые

0 выходы первой и второй фаз тактового генератора соединены соответственно с тактовыми входами первой и второй фаз блока управления, выход синхронизации которого соединен с входом

5 синхронизации тактового генератора, ; выходы готовности и синхронизации которого соединены соответственно с входом готовности блока управления и с входом синхронизации контроллера, информационные входы/выходы которого соединены с информационными выходами/ входами блока управления, входы захвата и прерывания и выходы ожидания и разрешения прерывания которого являются соответственно .входами захвата и прерывания и выходами ожидания и разрешения прерывания системы, выход сброса тактового генератора соединен со входом сброса,блока управления и

0

5

с первым ъходом третьего элемента ИЛИ выход которого соединен с входом сброса триггера, адресные выходы блока управления соединены с информационными входами буфера адреса, выходы которого являются адресной шиной системы и соединены с адресными входами блоков постоянной памяти программы и оперативной памяти и с информационными входами дешифратора адреса памяти t дешифратора адреса устройства ввода/вывода и дешифратора, группа управляющих выходов блока управления соединена с группой управляющих входов контроллера, выводы/входы которого чвлнются шиной данных системы и соединены с выходами блока постоянной памяти программ, -входами/выходами лиш его формирователя оперативной пампги и шинных формирователей устройств ввода/вывода, выход подтверждения захвата блока управления соединен с первым и вторым входами разрешения буфера адреса, выход приема блока управления соединен со вторыми входами разрешения блока постоянной памяти программы и шинного формирователя оперативной памятч, управляющие выходы контроллера образуют управляющую дану системы, разряды записи ,-j память и чтения памяти которой соединенны с соответствующими входами лср.эого элемента ИЛИ,, выход которого соединен с входом разрешения дешифратора адреса памяти, первый выход которого соединен с пеовым входом разрешения блока постоянной памяти программы и входом разрешения дешифратора г второй выход дешифратора соединен с входом разрешения блока оперативной памяти и первым входом разрешения шинного формирователя оперативной памяти, выходы которого соединены с информационными входами блока оперативной памяти, выходы которого соединены с входами шинного формирователя оперативной памяти, разряд записи в тамять шины управления соединен с входом записи блока оперативной памяти, разряд вывода в устройство вывода шины управления соединен с первым входом второго элемента ИЛИ, выход которого соединен с входом разрешения дешифратора адреса устройств ввода/вывода, вы- ходы которого с первыми входами разрешения соответствующих глинных формирователей устройств вво

5

0

5

0

5

0

5

0

5

да/вывода, выходы которых являются информационными выходами системы, разряд вводе из устройства ввода шины управления соединен со вторым входом второго элемента ИЛИ и со вторыми входами разрешения шинных формирователей устройств ввода/вывода, входы которых являются информационными входами системы, отличающаяся тем, что, с целью сокращения объема памяти констант в системе, в нее дополнительно введены четвертый и пятый элементы ИЛИ, группа элементов И и мультиплексор, а также блок динамической адаптации данных, содержащий группу регистров отслеживания, группу регистров просмотра, первый и второй счетчикиt дешифратор, первый и второй триггеры, первый - деся-Гый элементы ИЛИ, первый - шестой элементы И, первый - восьмой элементы задержки, первый и второй одновибраторы , генератор и блок анализа констант, причем первая группа информационных входов которого является входами первого регистра просмотра группы, выходы которого соединены с информационными входами второго регистра просмотра группы, выходы которого соединены с информационными входами третьего регистра просмотра группы и с третьей группой входов констант блока анализа констант, управляющий выход которого соединен с инверсным входом третьего элемента И, выход которого соединен с первые входом пятого элемента ИЛИ, выход которого соединен с входом второго элемента задержки и с первым зходом шестого элемента ИЛИ, выход которого соединен с входом обратного счета второго счетчика, выходы которого являются адресными входами блока, вторая группа информационных входов блока является входами первого регистра отслеживания группы, выходы которого соединены с информационными входами второго регистра отслеживания группы, выходы которого соединены с информационными входами третьего регистра отслеживания группы и с первой группой входов констант блока анализа констант,.выходы третьего регистра отслеживания группь) соединены со второй группой входов кфнстант блока анализа констант, выходы третьего регистра просмотра группы соединены с четвертой группой входов констант

блока анализа констант и с входами седьмого элемента ИЛИ, выход которого соединен с первым входом третьего элемента И и с инверсным входом шестого элемента И, выход которого соединен со вторым входом пятого элемента ИЛИ и с первым входом девятого элемента ИЛИ, выход которого соединен с входом сброса второго триггера, JQ выход которого соединен с входом управления, генератора, выход которого соединен с входом седьмого элемента задержки и с первым входом десятого элемента ИЛИ, выход которого объеди- нен с входом шестого элемента гадерж- ки и является выходом чтения блока, вход разрешения блока соединен с первым входом четвертого элемента И и входом второго одновибратора, вы- 2Q ход которого соединен с первым входом восьмого элемента ИЛИ, выход которого Соединен с установочным входом второго триггера, вход чтения блока соединен с первым входом первого элемен- 25 та И, выход которого соединен с первым входом первого элемента ИЛИ, выход которого соединен с входом прямого счета первого счетчика и с входом первого элемента задержки, выход ко- 30 торого соединен с входами синхронизации регистров отслеживания группы и с первым входом второго элемента ИЛИ,

выход которого соединен с входом прямого счета второго счетчика, вход « достижения адреса первой точки программы блока соединен с прямым входом второго элемента И и с входом первого одновибратора, выход которого соединен с первым входом пятого элемен- до та И, выход которого соединен со вторым входом восьмого элемента ИЛИ, вход достижения адреса второй точки программы блока соединен с первым входом четвертого элемента ИЛИ и со 45 вторым входом четвертого элемента И, выход которого соединен с входом установки первого триггера, выход которого соединен со вторым входом пятого элемента И, вход начального 50 сброса блока соединен со вторым входом четвертого элемента ИЛИ и с первым входом третьего элемента ИЛИ, выход которого соединен с входами сброса второго счетчика и первого триггера, со вторым входом девятого , элемента ИЛИ и с входом начального сброса блока анализа констант, вход достижения адреса третьей точки программы блока соединен с входом записи констант блока анализа констант, вход достижения адреса четвертой точки программы блока соединен со вторым входом третьего элемента ИЛИ и с входом программного сброса блока анализа констант, выход четвертого элемента ИЛИ соединен с входом сброса первого счетчика, информационные выходы которого соединены с входами дешифратора, выход которого соеди- .нен с инверсными входами первого и второго элементов И, выход которого соединен с вторым входом первого элемента ИЛИ, выход второго элемента задержки соединен с третьим входом шестого элемента ИЛИ и с входом третьего элемента задержки, выход которого соединен со вторыми входами шестого и девятого элементов ИЛИ, выход шестого элемента задержки соединен с входами записи регистров просмотра группы и со вторым входом второго элемента ИЛИ, выход седьмого элемента задержки соединен со вторым входом десятого элемента ИЛИ и с входом восьмого элемента задержки, выход которого соединен с третьим входом десятого элемента ИЛИ и с входом четвертого элемента задержки, выход которого соединен с прямым входом шестого элемента И и с входом пятого элемента задержки, выход которого соединен со вторым прямым входом третьего элемента И, третий выход дешифратора адреса памяти соединен с первыми входами элемента И и четвертого элемента ИЛИ, выход которого соединен с первым входом разрешения блока постоянной памяти констант, выходы которого соединены с первыми входами соответствующих элементов И группы и с первой группой информационных входов блока динамической адаптации данных, выход чтения которого соединен со вторым входом четвертого и первым входом пятого элементов ИЛИ, выход которого соединен со вторым входом разрешения блока постоянной памяти констант, управляющий выход прием блока управления соединен со вторыми входами пятого элемента ИЛИ и элемента И, выход которого соединен со вторыми входами элементов И группы, является выходом управления системы и соединен с входом чтения блока динамической адаптации данных, адресные выходы которого соедиены с первой группой адресных вхоов мультиплексора,, вторая группа адресных входов которого является группой входов управления системы,, выходы соединены с адресными входами блока постоянной памяти констант, первый выход дешифратора соединен с входом установки триггера, выход которого соединен с входами разрешения блока динамичес кой адаптации данных и мультиплексора, второй выход дешифратора соединен со вторым входом третьего элемента ИЛИ, первый четвертый выходы дешифратора соединены соответственно с входами достижения первой - четвертой точек программы блока динамической адаптации даь ных выход сброса тактового генератора соединен с входом сброса блока динамической адаптации данных, выходы группы элементов И соединены с шиной цаннык системы и второй группой информационных входов блока динамической адаптации данных,

1, Система по п, 1, отличающаяся тем, что блок анализа констант содержит перзый и второй элементы ИЛИ,- группу элементов И, группу регистров первой константы, группу регистров второй константы, группу блоков определения ортогональности и сдвигакэдий регистр, причем первая группа входов констант блока является информационными входами первого регистр группы регистров втооой константы выходы каждого из регистров группы регистров второй константы и регистров группы регистров первой константы, кроме последнего, подключены к информационным входам последяощего по номеру регистра x pyrmii, а входы синхронизации регистров 1 руппы объединены я являются. входом записр констант блока анализа констант, который также является входом сдвига сдвигающего регистра, выходы регистров группы -регистров первой константы подключены к первым грушам информационных входов соответствующих блоков определения ортогональности группы, выходы регистров группы регистров второй константы подключены ко вторым группам информационных входов соответствующих блоков определения ортогональности группы, третья и четвертая руппы информа

5

0

5

0

5

0

5

0

5

ционных входов которой являются четвертой и третьей группами входов констант блока соответственно, информационные входы первого регистра группы регистров первой константы являются второй группой входов констант блока, выходы блоков определения ортогональности группы соединены со вторыми входами соответствующих элементов И группы, первые входы которых подключены к соответствующим разрядам выходов сдвигающего регистра, выходы элементов И группы соединены с входами первого элемента ИЛИ, выход которого является управляющим выходом блока, входы начального сброса и программного сброса блока соединены соответственно со вторым и первым входами второго элемента ИЛИ, выход которого соединен с входом сброса сдвигающего регистра, информационный вход сдвига вправо которого через ограничительный резистор подключен к положительной шине источника питания.

I

3, Система по пп. 1 и 2, о т л ичающаяся тем, что каждый блок определения ортогональности содержит первую и вторую группы элементов И, группу элементов сложения по модулю два, элемент ИЛИ, причем первые входы элементов И второй группы подключены к соответствующим разрядам первой группы информационных входов блока, а вторые входы элементов И второй группы подключены к соответствующим разрядам третьей группы информационных входов блока, выходы элементов И второй группы подключены к первым входам соответствующих элементов И первой группы, вторые аходы которых подключены к выходам соответствующих элементов сложения по модулю два группы, первые входы элементов сложения по модулю два группы подключены к соответствующим разрядам второй группы информационных входов блока, а вторые входы элементов сложения .по модулю два группы подключены к соответствующим разрядам четвертой группы информационных входов блока, выходы элементов И первой группы подключены к соответствующим входам элемента ИЛИ, выход которого является информационным выходом блока.

Фиг. I

6zz889i

Фиг. 5

| Устройство программного управления | 1981 |

|

SU1012205A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Микропроцессорная система для программного управления технологическими процессами | 1987 |

|

SU1418653A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Авторское свидетельство СССР № (заявка К 4417537/24, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1991-10-30—Публикация

1989-05-03—Подача