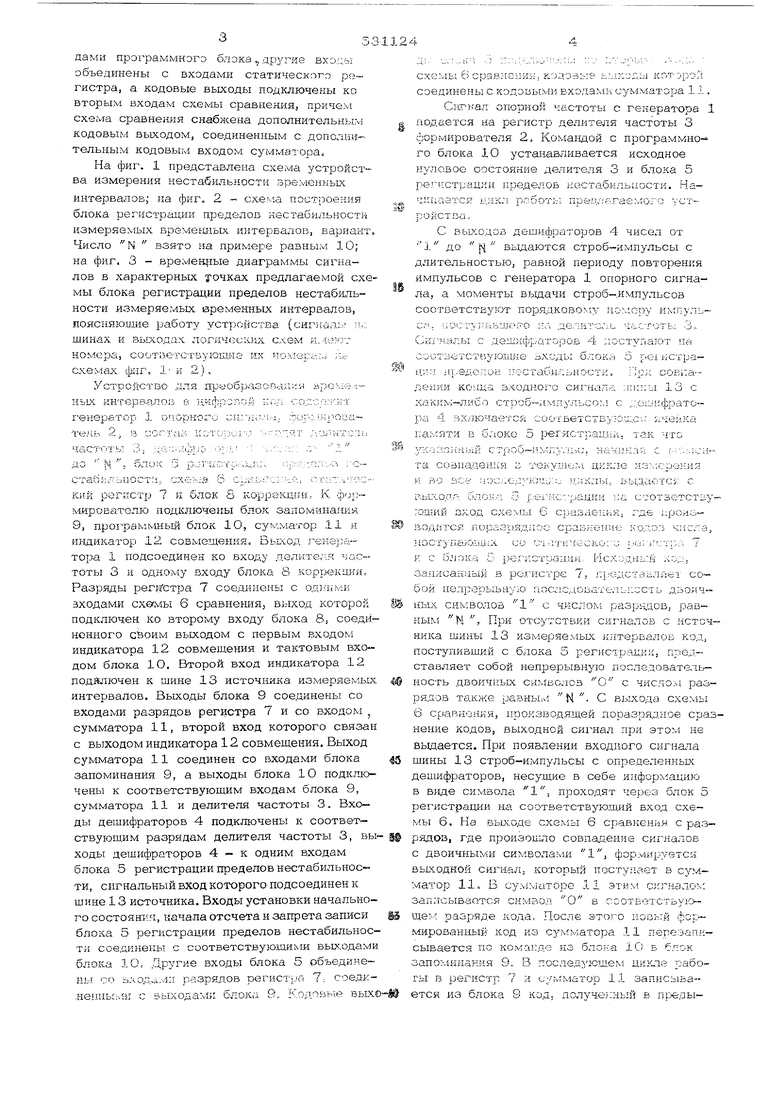

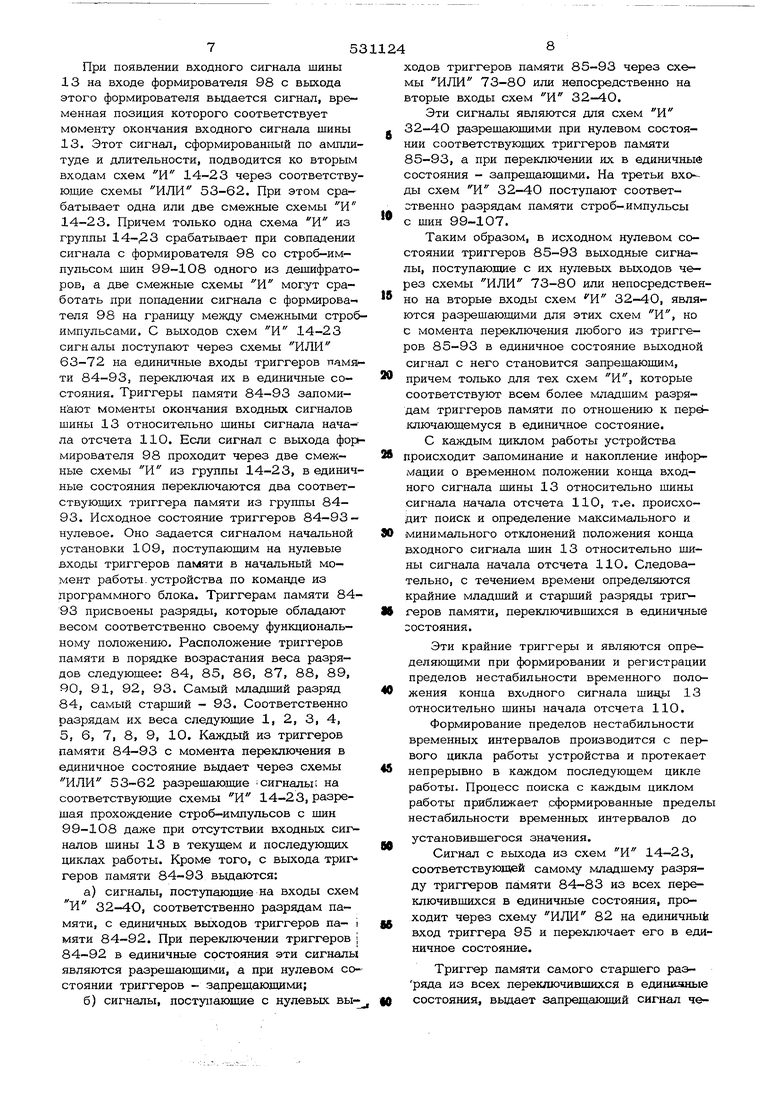

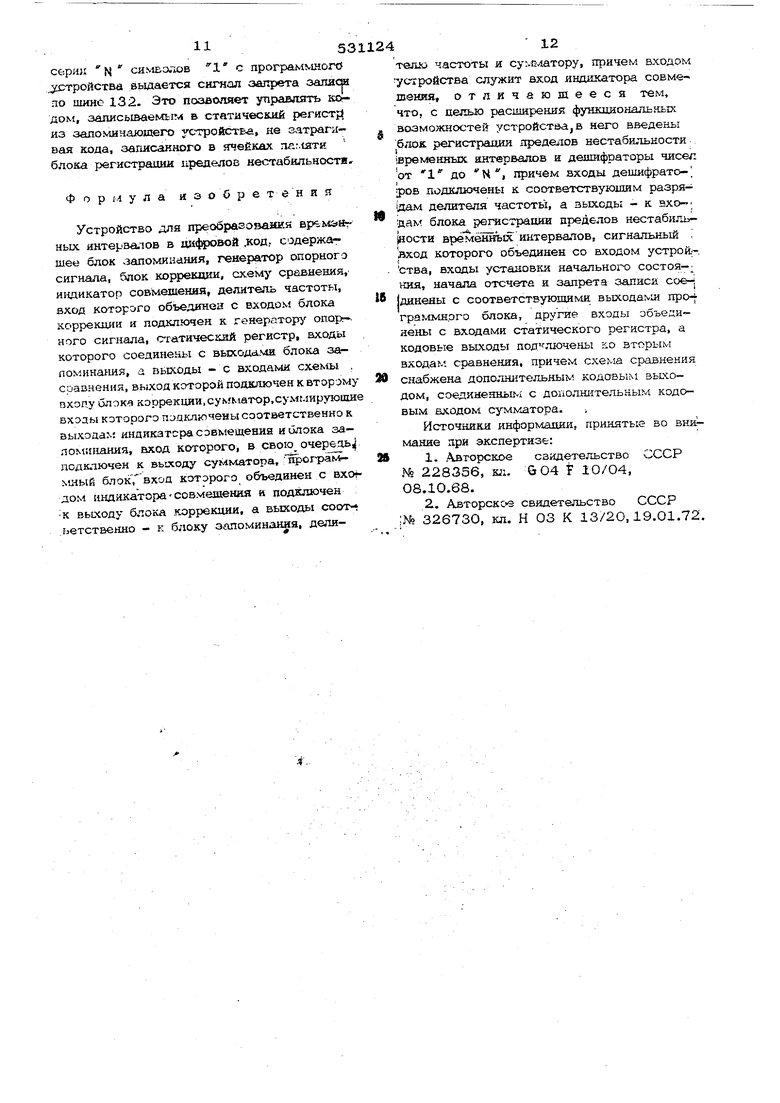

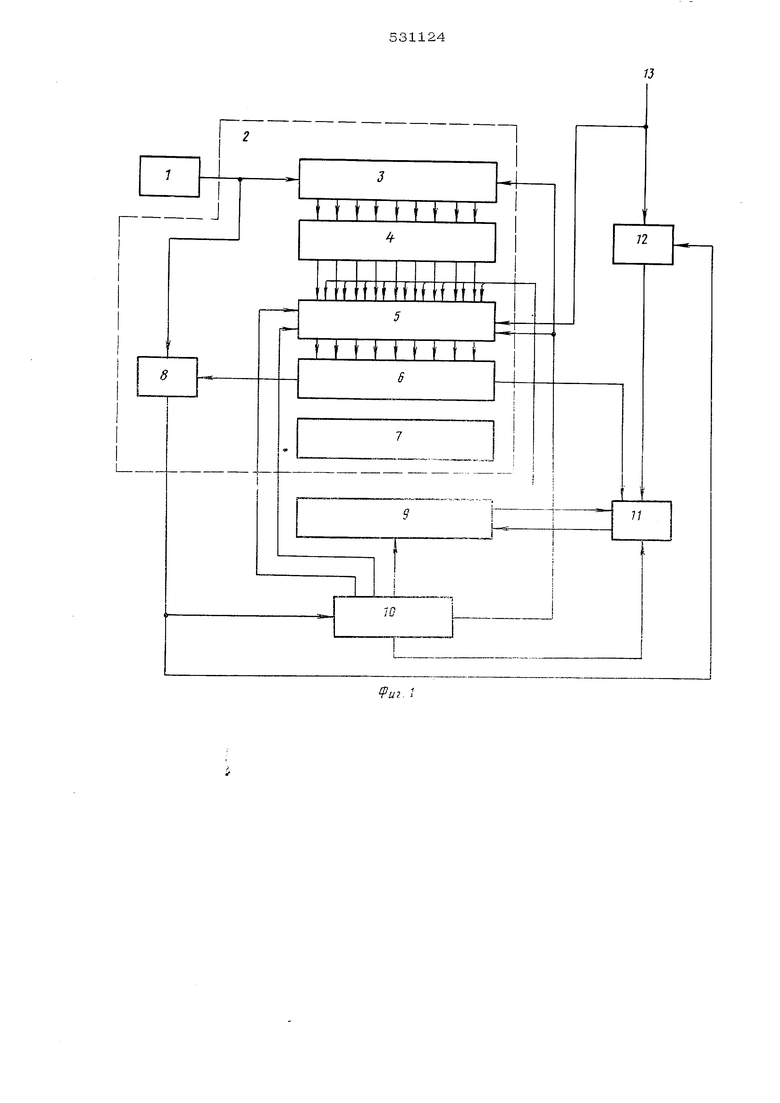

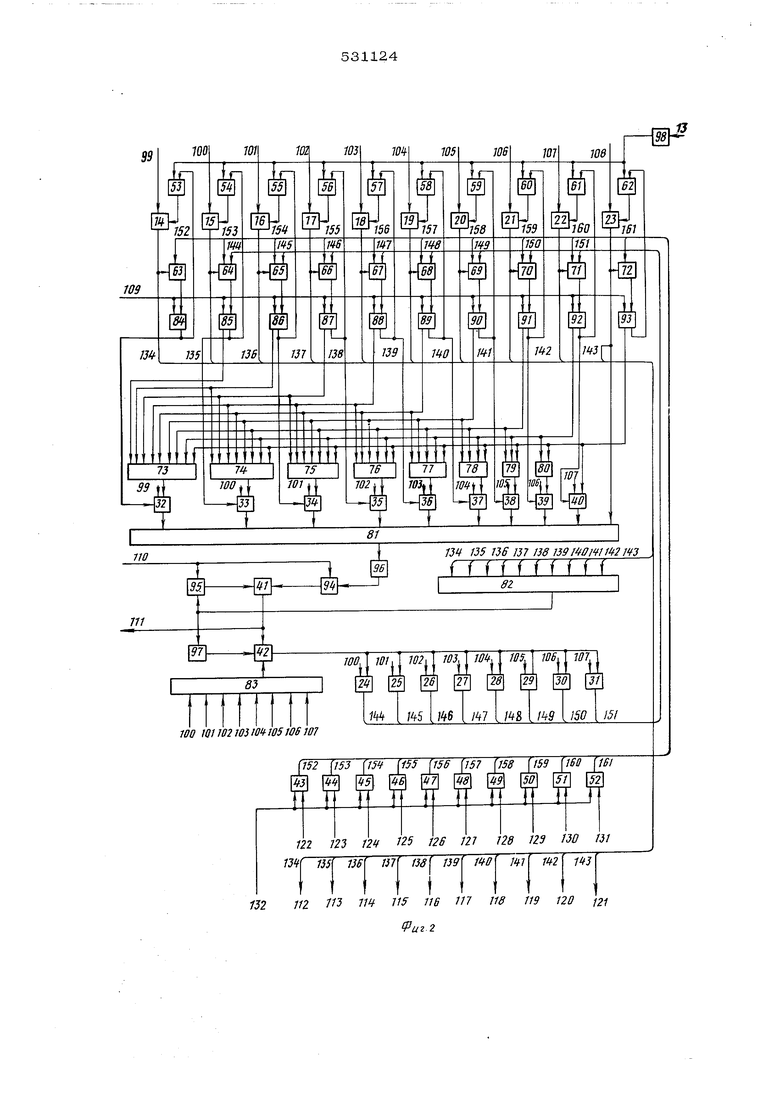

35 программного блока , др;/гке вхэ,:;,ы объединены с входами статического регистра, а кодовые выходы подключены ко вторым входам схемы сравнения, причем схема сравнения снабл-сена дополнительным кодовым выходом, соединенным с допОчТнительным кодовым входом суммаа-ора. На фиг. 1 нредставлена схема устройства измерения нестабильности зремениььх интервалов; на фиг, 2 схема построения блока регистрации пределов кестаби.а.ьности измеряемых времев-шых интервалов, вариант Число N взято на примере равным 10; на фиг. 3 - времекрые диаграммы сигналов в характерных точках предлагаемой схе мы блока регистрации пределов нестабильности измеряемых временных интервалов, поясняющие работу устройства (cHDiun:; ;ь:, шинах и выходах логических схем и.-ино-г номера, соответствующие их томесй;- i cсхемах фиг, 1-й 2), Устройство для пруобраооваи;-:я рс ;е-;-ных интервалов в нчФропой ;c. со,со;;};г гонератОр ,. . .7-и /и- - ,cu;j..j ;-:i.те;;ь 2; в согтав i;;;,TC;V;ui--; .ят ллиит;:1ь частоты 3; .:ju;;,.ub:.:o . : ,..::... ./ до Н , блок 5 р.;гис14н: ь,:и ;;j:::v ,;;v..л гсста6:;Ло1Юст:1; схеь;а Ь с;.й;.;-: :;::-лЛ: .-..-:ский регистр 7 и блок 8 корракции, К формирователю подключены блок запоминания 9, программный блок 10, сумматор 11 и И1:щикатор 12 совмещения, Бькод rei epa-тора 1 подсоединен ко входу делителя частоты 3 и одному входу блока 8 коррекции, Разргзды periiCTpa 7 соединены с оя1 ЕК:И зходами схемы 6 сравнения, выход кот-орой подключен ко второму входу блока 8; соеди ненного выходом с первым входом индикатора 12 совмещения и тактовым входом блока 1О. Второй вход индикатора 12 подйлючен к щине 13 источника измеряемы интервалов. Выходы блока 9 соединены со входами разрядов регистра 7 и со входом , сумматора 11, второй вход которого связа с выходом индикатора 12 совмещения. Выход сумматора 11 соединен со входами блока запоминания 9, а выходы блока 1О подклю чены к соответствующим входам блока 9, сумматора 11 и делителя частоты 3. Входы дешифраторов 4 подключены к соответ-ствуюшим разрядам делителя частоты 3, вы ходы дещифраторов 4 - к одним входам блока 5 регистрации пределов нестабильности, сигнальный вход которого подсоединен к щине 13 источника. Входы установки начально го состояния, начала отсчета и запрета записи блока 5 регистрации пределов нестабильнос ти соединены с соответствующими вььх.одам блока Ю. Другие входы блока 5 объединеразрядов perncTjja 7: соеди ,неиныг.и Сгсг-кал опорной частоты с генератора . подается на регистр делителя частоты 3 формирователя 2, Командой с программно- го блока 1О устанавливается исходное нулевое состояние делителя 3 и блока 5 репхстрадии пределов нестабильности. Начинается дик:1 роботы прецлагаемого устройства, С вь1х.одоа дешифраторов 4 чисел от до fi выдаются строб-импульсы с длительностью, равной периоду повторения импульсов с генератора 1 опорного сигнала, а моменты вьщачи строб-лмпульсов соответствуют порядковому момс-ру импульс,-, ;;осг,1Гйьшеро нл делитоль Сигналы с дешифраторов 4 лос соотзетстЕ1ую1 лие охсды блока ц;;:1 пределов 17: сгабил1 ности. ле;1ии Kouua входного сигнала каким-либо стооб-лмпульсо:.; с ра ч HXjjK}4aeTc; соотБетству;о памяти Е 6:iOK ; регистрации, так что та созиадения s текуык;М аккле изл;срения ю-щ:-.; длклы ььиаотс : с |:е1ччС-:-рацим ;;а ссотзетст11у;од;ий аход схемы о сразаения, гм водится поразияднос сраБ ;ение ;чо.Г1ОЗ члсла, 1ЮСТуГ1а Ол-1л1;Х ио 1Т1-Г:,:1СКО: J :/Сг ьг у|;.- / Y. с блока С регкстрааии. Исходнь:к xo.::. за.иисакаый в ре1 истре 7, клдстаЕЛле собой Н8лрерыьну;о Г10Слс.цоБателы:ссть дьоич- sibix символов 1 с ЧИСЛОМ разряцоВ; равным М % При отсутствии сигналов с источника шины 13 измеряемых кггтервалов код, поступивщий с блока 5 регис1раци 1, представляет собой непрерывную последовательность двоичных символов О с числом разрядов также равныл Н. С выхода схемы 6 сравконкя, производящей поразрядное сравнение кодов, выходной сигнал при этом не вьщается. При появлении входного сигнала щины 13 строб-импульсы с определенных дещифраторов, в себе инфор: ацию в виде символа 1, проходят через блок о регистраш-хи на соответствуюл1.ий вход схеMbi 6. На выходе схемы 6 сравнения с разрядов, где произошло совпа.цение сигналов с двоичными символами 1, форми : уется выходной сигнал, который поступает в сумматор 11, щет- разряде кода. После этого иопый мированный код из сумматора 11 перезаписывается по команде из блока 1О в блок запоминания 9„ В последующек цикле работы в регистр 7 и сумматор 11 записывается из блока 9 КОД; дслуче;,;нь;й в пр-е.аыДушем цикле измерений. Код излменается от цикла к циклу до полного совпадешш его с кодом, обратным поступающему с блч/ха 5, Причем все разряды кода в блоlie aar.otvUtHaniis 9, расположенные между двумя крайними разрядами с символом О, с помошью блока 5 также приобретают симаоп О, Этим самым подчеркивается и вьщеляется ;1нтерзал возможных значений нестабильных отрезков времени. При совмещении начала никла работы фор-; мирователя 2 с импульсом начала измеря-емого интервала времени код, записанный, в регистр 7, полностью характеризует как минимальное, так и максимальное значение измеряемого отрезка BpeMeHHj а следовательно и интервал его нестабильности к может быть подан в индикатор отсчета. С дополнительного выхода 5 регистрации выдается строб-импульс, соответ- ствуюший по длительности величине интервала нвстаби -1ьности.

Совмещение нача.-:а пикла работы формирователя 2 с импу,11--со;.; начала измеряемого интервела производится следующим обраОС ,

в 1-1ачальном цикле совмешения по команде из блока 10 в сумматор 11 записывается число, выраженное последовательностью двоичных символов 1 с количеством разрядов, равным К ...11...111. По: следующей команде из блока 10 эта. инфор мация в параллельном коде из Н разря-: дов поступает в соответствующие разряды , памяти регистра 7 и блок 5 регистрации. На выходе блока 5 при последовательном опросе его строб-И1 шульсами с дешифратора 4 по М , разрядам формируются сигна- лы, следующие на соответствующие разрядам входы схемы 6 сравнения в виде кода 111.,. 11 из N двоичных символов 1.,

Количество разрядов в регистре 7 и в , сумматоре 11 вьшрлняется больше числа N , но символы 1 приобретают только К смежных разрядов после записи кода. Остальные разряды наделяются символом , Со схемой б сравнения соединены только N смежных разрядов регистра 7.i

Таким образом, после начала цикла сов-смещения насхеме 6 сравнения происходит сравнение кода 111...1 из N разрядов с устройства 5 регистрации с кодом вида -000 11...11ООО с Н значащими разрядами регистра 7. При несовпадении всех значащих разрядов сравниваемых кодов дpyrf с другом вследствие их относительного ; сдвига с выхода схемы Ъ сравнения вьща- i ется сигнал. Сигнал формируется в момент регистрации первого несовпадения по раз- ь рядам и записывает 1 в блок 8 коррек- ции. За|писанная i. считывается очередным импульсом с генератора 1. При этом формируется сигнал окончания формир:е.:ого времепкого интервала (опорногс- Ч-:иг-на;ла).

I Сформированный снгкал поступает аа иь д цгатор 12, на второй вход которого по- ступает входной сигнал шлны 13. RpJi несовпадении импульсов, огоаничиваюли;х IMV- ;/еряемьш и сформированный временные интервалы, с индикатора 12 выдается сигка.ч

.ошибки в сумматор 11, В зависимос- и от знака ошибки код, записанный в сум.,;атор 11, сдвигается в ту илл иную сторону, Л.а-Tree он 1череписьтается по из блок,:;

,1О 3 блок -запоминания 9.

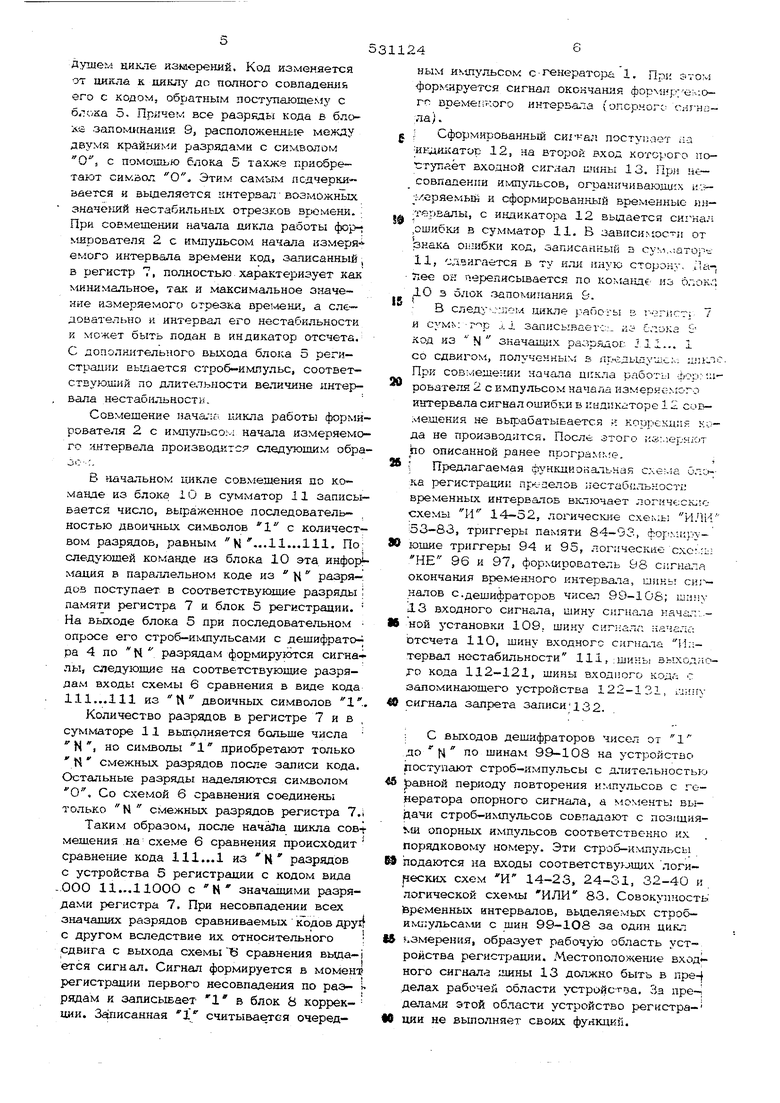

В следу .;:иом цикле }-апогы в tenicTi 7 и сумь;Г1р .i 1 записывает-;::.. й:з Слока t код из N значаигих разряд ос J11... 1 со сдвигом, полученным в ярвдьщулс.ч. ;л11-тс. При совме:1це; ии начала шгкла работы фор: .ирователя 2 с импульсом начала измеряемого интервала сигнал ошибы5 в 1:идикг;торе 12 сов- лющения не вьфабатывается .;-: кпррс.чд;1Я кода не производится. После этого нз:.;ер.ч;от по описанной ранее програмг е. J Предлагаемая функциокальная cxer.ia . ка регистрации прУзелов ь-естабильносп; временных интервалов В1и1ючает логкч€Ск: О схемы И 14-52, логичесю-ie схемы И/lii S3-83, триггеры памяти 84-93, фогмируюшие триггеры 94 и 95, логические cxor.:i:; НЕ 96 и 97, формирователь 98 сигнала окончания временного интервала, шякы си;налов с.дешифраторов чисел 99-108; ша.чу J.3 входного сигнала, шкну С гнала начал:.ной установки 109. шину С 1гиала пачалг-. отсчета 110, шину входного сигнала i тервал нестабильности 111, :1иинь1 зыход.-юго кода 112-121, шины входного код.з с запоминающего устройства 122-131, i.u;nry

сигнала запрета записи132.

; С выходов дешифраторов чисел от 1 до f4 по шинам 99-108 на устройство поступают строб-импульсы с длительностью

1равной периоду повторения иглпульсов с генератора опорного сигнала, а моменты вььдачи строб-ихтульсов совпадают с поз1щияSffl опорных импульсов соответственно их порядковому номеру. Эти строб-импульсы

подаются на входы соответству -)Ш1х логи|ческих схем И 14-23, 24-31, 32-40 и логической схемы ИЛИ 83. Совокуп 1ость Временных интервалов, вьщеляемьрс стробим1;ульсами с шин 99-1О8 за один цикл

.змерения, образует рабочую область устройства регистрации. Л естополо.ж.ение вход ного сигнала ишны 13 должно быть в пределах рабочей области устройс-т за. За пределами этой области устройство регистрации не вьшолняет своих функций.

При появлении входного сигнала шины 13 на входе формирователя 98 с выхода этого формирователя выдается сигнал, вре менная позиция которого соответствует моменту окончания входного сигнала шины 13. Этот сигнал, сформированный по амплитуде и длительности, подводится ко вторым входам схем И 14-23 через соответствующие схемы ИЛИ 53-62. При этом срабатывает одна или две смежные схемы И 14-23. Причем только одна схема И из группы срабатывает при совпадении сигнала с формирователя 98 со строб-импульсом шин 99-108 одного из дешифраторов, а две смежные схемы И могут сработать при попадении сигнала с формирователя 98 на границу между смежными стробимпульсами. С выходов схем И 14-23 сигналы поступают через схемы ИЛИ 63-72 на единичные входы триггеров памяти 84-93, переключая их в единичные состояния. Триггеры памяти 84-93 запоминают моменты окончания входных сигналов шины 13 относительно шины сигнала начал а отсчета 110. Если сигнал с выхода формирователя 98 проходит через две смежные схемы И из группы 14-23, в единичные состояния переключаются два соответствующих триггера памяти из группы 8493. Исходное состояние триггеров 84-93нулевое. Оно задается сигналом начальной установки 109, поступающим на нулевые входы триггеров памяти в начальный момент работы, устройства по команде из программного блока. Триггерам памяти 8493 присвоены разряды, которые обладают весом соответственно своему функциональному положению. Расположение триггеров памяти в порядке возрастания веса разрядов следующее: 84, 85, 86, 87, 88, 89, 90, 91, 92, 93. Самый младший разряд 84, самый старший - 93. Соответственно разрядам их веса следующие 1, 2, 3, 4, 5, 6, 7, 8, 9, 10. Каждый из триггеров памяти 84-93 с момента переключения в единичное состояние выдает через схемы ИЛИ 53-62 разрешающие сигналы; на соответствующие схемы И 14-23, разрешая прохождение строб-импульсов с шин 99-108 даже при отсутствии входных сигналов шины 13 в текущем и последующих циклах работы. Кроме того, с выхода триггеров памяти 84-93 вьщаются:

а)сигналы, поступающие на входы схем И 32-4О, соответственно разрядам памяти, с единичных выходов триггеров па- i мяти 84-92. При переключении триггеров j 84-92 в единичные состояния эти сигналы являются разрешающими, а при нулевом состоянии триггеров - запрещающими;

б)сигналы, поступающие с нулевых выходов триггеров памяти 85-93 через схемы ИЛИ 73-80 или непосредственно на вторые входы схем И 32-40.

Эти сигналы являются для схем И 32-4 О разрешающими при нулевом состоянии соответствующих триггеров памяти 85-93, а при переключении их в единичный состояния - запрещающими. На третьи вхо ды схем И 32-40 поступают соответственно разрядам памяти строб-импульсы с шин 99-107.

Таким образом, в исходном нулевом состоянии триггеров 85-93 выходные сигналы, поступающие с их нулевых выходов через схемы ИЛИ 73-8О или непосредственно на вторые входы схем И 32-40, явля ются разрешающими для этих схем И, но с момента переключения любого из триггеров 85-93 в единичное состояние выходной сигнал с него становится запрещающим, причем только для тех схем И, которые соответствуют всем более младшим разрядам триггеров памяти по отношению к nepeiключающемуся в единичное состояние.

С каждым циклом работы устройства происходит запоминание и накопление информации о временном положении конца входного сигнала шины 13 относительно шины сигнала начала отсчета 110, т.е. происходит поиск и определение максимального и минимального отклонений положения конца входного сигнала шин 13 относительно шины сигнала начала отсчета НО. Следовательно, с течением времени определяются крайние младший и старший разряды три1 геров памяти, переключившихся в единичные состояния.

Эти крайние триггеры и являются определяющими при формировании и регистрации пределов нестабильности временного положения конца входного сигнала шидь 13 относительно шины начала отсчета 110.

Формирование пределов нестабильности временных интервалов производится с первого цикла работы устройства и протекает непрерывно в каждом последующем цикле работы. Процесс поиска с каждым циклом работы приближает сформированные предел нестабильности временных интервалов до

установившегося значения.

Сигнал с выхода из схем И 14-23, соответствующей самому младшему разряду триггеров памяти 84-83 из всех переключившихся в единичные состояния, проходит через схему ИЛИ 82 на единичный вход триггера 95 и переключает его в единичное состояние.

Триггер памяти самого старшего раэряда из всех переключившихся в едининные состояния, вьщает запрещающий сигнал через ИЛИ 73-80 или непосредственно на вторые входы схем И 32-4О, соответствующие всем более младшим раз- рядам. Одновременно с этого триггера выдается разрешающий сигнал на соответству- юшую данному разряду схему И 32-40, через которую с момента переключения триггера в единичное состояние проходит строб-импульс, соответствующий этому разряду памяти, и через схему ИЛИ 81, схему НЕ 96 поступает на единичный вход триггера 94, переключая его в единичное состояние. Сигнал, соответствующий старшему разряду памяти, проходит на вход схемы ИЛИ 81 непосредственно с выхода схемы И 23.

В исходное нулевое состояние триггеры 94 и 95 переключаются сигналами шины начала отсчета 110, подаваемыми на нулевые входы триггеров. В этом состоянии с единичного выхода триггера 94 на один вход схемы И 41 выдается разрешающий сигнал, а с нулевого выхода триггера 95 на другой вход схемы И 41 - запрещающий сигнал. При переключении триггеров 94 и 95 в единичные состояния с триггера 94 на вход схемы И вьщается запрещающий сигнал, а с триггера 95 разрешающий. Таким образом, на ъкоде схемы И 41 формируется cигнaJ иины 111, определяющий своей длителы. пределы нестабильности временного положения конца входного сигнала шины 13 относительно шины сигнала начала отсчета 110. Схема переключает триггер 94 в единичное состояние задним фронтом сигнала, прошедшего через схему ИЛИ 81. Это необходимо для того, чтобы сформировать верхний, максимальный предел нестабильности на позиции первого тактового импульса, следуюшего с генератора опорного сигнала по окончании сигнала с формирователя 98 с максимальным выявленным отклонением относительно сигнала начала отсчета 110 в текущем цикле измерений.

Преобразование временных интервалов в код происходит следующим образом.

Если некоторые из триггеров памяти 82-93 между крайними младшим.и старшим разрядами триггеров, переключившимися в единичное состояние, не переведены в едчничные состояния входным сигналом 1Ш«1Ы 13, то, поскольку они входят в пределы нестабильности измеряемых временных интер алов, эти триггеры также переключаются в указанные состояния с помощью схемы формирования кода, состоящей из схем И 24-31, 42 схемы НЕ 97 и схемы ИЛИ 83.

На входы схемы ИЛИ 83 подаются

строб-И1 шульсы с шин 1ОО-107, т.е. все сигналы с дешифраторов чисел, кроме сиг налов с дешифратора числа 1 и числа М равны 10. С выхода схемы ИЛИ 83 эти сигналы поступают на один вход схемы И 42, на второй вход которой подаются через схему ИЛИ 82 и схему НЕ 97 сигналы с выходов схем И 14-23, а на третий вход подводится сигнал с выхода схемы И 41, соответствующий

по длительности сформированным пределам нестабильности. Сигнал с выхода схемы И 42 подается на объединенные первые входы схем И 24-31, на вторые входы которых подаются строб-импульсы с шин

в 1ОО-107 соответственно. Выходы схем И 24-31 подключены через соответствующие схемы ИЛИ 64-71 к единичкыь: входам триггеров памяти 85-92. Таким образом, в случае, если некоторые из триг0 герое памяти между крайними, перек г1ючлвшимися в единичные состояния, находятся в нулевом состоянии, то на выходе схемы И 42 формируется сигнал, которьШ, проходя через соответствующую схему И

5 24-31 и ИЛИ 64-71, переключает эти триггеры в единичные состояния.

Следовательно,код, зафиксированны-й в ячейках памяти устройства регистрации имеет вид, например, ООО111111О, где

0 общее число разрядов равно jvj равно 10, а серия О прерывается серией 1, определяющей пределы нестабильности измеряемого временного интервала. Код, соответствующий вышеуказанному, но только

в импульсном выражении, вьщается на вы-т ход устройства регистрации параллельным кодом с выходов схем И 14-23 по соответствующим шинам выходного кода 112- 121. Информация в ячейках памяти устройства регистрации очищается сигналом ши,ны начальной установки 109, а заносится по команде с программного устройства при измерении нескольких временных интервалов из запоминающего устройства по ши5 нам кода 122-131, поступающего через схемы И , схемы ИЛИ 63-72 на соответствующие триггеры памяти 8493. При этом сигнал, вьщаваемый на объеди .ные входы схем И 43-52 с

0 шины сигнала запрета записи 132, является разрешающим. Сигнал запрета записи кода из запоминающего устройства в устройство регистрации выдается по шине 132с программного устройства в опре5 деленные моменты времени. Например, при совмещении начала цикла работы формирующего устройства с импульсом начала измеряемого интервала времени в начальном цикле совмещения сразу же после за-

писи в устройстве регистрации кода из

серия N сймЕ.о.-юв 1 с програм шого устройства вьиается сигнал аалрета записи по щине 132. Это позволяет управлять кодом, записываемым в статический регистр из заломинающего устройств-а, не Зчатрагнвая кода, записанного в ячейках лаг.шти. блока регнстрашш пределов нестабильности,

Фор пула изобретеняя

Устройство для преобразовашг.я ных интервалов в ци(вой .код., содержащее блок запоминания, генератор опорного сигнала, блок коррекции, схему сравнения, индикатор совмещения, делитель частоты, вход которого объединеа с входом блока коррекции и подключен к генератору опорг-. ного сигнала, статичесалй регистр, входы которого соединены с выходами блока загпоминания, а выходы - с входами схемы . сравнения, выход которой подключен к второму входу блока коррекции,сумматор,суммирующие входы которого пэдключены соответственно к выходам индикатора совмещения иилока за- пом 1 1ания, вход которого, в свою onep eobifj подключен к выходу сумматора, Лсцр г-ра мный блок , вход которого объединен с Bxofдом индикатора-совмешення и подключен к выходу блока .коррекции, а выходы соот- ьетственно - Е блоку запоминания, делителю частоты и cy vJiviaTopy, причем входом устройства служит вход индикатора совмещения, отличающееся тем, что, с делью расширения функциональных возможностей устройства.в него введены

блок регистрадии лредедов нестабильности 1временных интервалов и дешифраторы чисел от до N, причем входы дешифрато- ров подключены к соответствующим разря дам делителя частоты, а выходы - к вхойам блока регистрации пределов нестабиль(иости времёншггх интервалов, сигнальный . вход которого объединен со входом устрой. ства, входы установки начального состояння, начала отсчета и запрета записи coe-i |динены с соответствующими выxoдa u про-; граглмнрго блока, другие входы объединены с входами статического регистра, а кодовые выходы под лючены ко вторым входам сравнения, причем схема сравнения снабжена дополш1тельным кодовым зькодом, соединенным с дополнительным кодовым входом сумматора. ,

Источники информации, принятые во внимание при экспертиза:

1.Авторское свидетельство СССР МЬ 228356, Ю1. &О4 Т 10/О4, О8.10.68.

2.Авторское свидетельство СССР

;№ 326730, кл. Н 03 К 13/20,19.01.72.

J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля знаний обучаемых | 1987 |

|

SU1524082A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ В АДАПТИВНЫХ ТЕЛЕМЕТРИЧЕСКИХ СИСТЕМАХ | 1995 |

|

RU2103745C1 |

| Телевизионный пеленгатор | 1989 |

|

SU1670805A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для определения координат треков | 1985 |

|

SU1255976A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| Устройство для сглаживания периодических случайных сигналов | 1983 |

|

SU1242987A2 |

MTT

i.

/j /J5 /j7 //

( f f f f ff f f f ,

wo mw2Wimio5ioswj

152 J53 15t 155 156 /57 l58 I59 {ISO ISI ЛЙЙЙЙЙЙЙЙЙ

132 112 11 Т1Ч- 115 П6 Т Л 1W 119 120 21

W I 7W, 1 7 I 1 ад 1 j I 06. IffT ЙЙЙЙЙЙЙЙ

I m M т I I т isi

Vu2-2

t

м

и

&

Авторы

Даты

1976-10-05—Публикация

1975-05-12—Подача