(5) УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ ДАТЧИКОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Вероятностное устройство для решения краевых задач | 1982 |

|

SU1101838A1 |

| Микропрограммное устройство управления | 1981 |

|

SU987623A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1138809A1 |

| Устройство для централизованного управления вычислительной системой | 1985 |

|

SU1259261A1 |

| Устройство для формирования входных воздействий в системе программного контроля | 1983 |

|

SU1138803A1 |

| Устройство для отладки специализированных микроЭВМ | 1990 |

|

SU1741135A1 |

Изобретение относится к вычислител ной технике и автоматике и может быть использовано для управления технологи оборудованием с большим количеством датчиков и иcпoлниteльныx органов в машиностроительной, электронной и других отраслях промышленности. Известно устройство преобразования дискретных сигналов для управления производственными механизмами, которое содержит группу входных шин, по которым сигналы о состоянии управляемого объекта через входные преобразователи поступают на решающий узел, который производит преобразование входных дискретных сигналов в соот ветствии с управляющей программой, записанной в памяти программ, после чего .преобразованные сигналы с помощью дешифратора запоминаются в соответствующих выходных преобразователях на выходных шинах которых осуществляется коммутация исполнительных оргаНОВ согласно заданному закону управления т . Известное устройство не обеспечивает высокого быстродействия преобразования дискретных сигналов при управ лении сложным оборудованием ввиду применения последовательных алгоритмов, имеет низкую достоверность результатов преобразования, что сужает область его применения. Наиболее близким по технической сущности к изобретению явлАеТся устройство, которое содержит генератор тактовых импульсов, входной модуль, на входные контакты которого подается информация о состоянии внешнего устройства и преобразуется им в логическую величину О или 1. По команде, находящейся в памяти управляющей программы (памяти программ), при помощи схемы изменения входа (входной коммутатор) информация от соответствующего внешнего устройства поступает на схемулогических oneраций, где производится ее анализ на требуемое состояние в соответствии с текущей командой. Последовательность управления требуемой цепной диаграммой определяется последовательностью команд управляющей программы, вводимой в память программ с помощью схемы последовательного ввода. Результирующее управляющее выходное значение, полученное с помощью схемы логических операций, поступает через схему изменения выхода (дешифратор) и схему преобразования и запоминания (выходной преобразователь) на выходные устройства. Контрольная флаго-ts гут вая система, входящая в схему логических операций, запоминая удовлетворительный результат операций ИЛИ или неудовлетворительный;результат операции И, позволяет пропустить оставшуюся часть операции . Недостатком данного устройства яв ляется то, что для реализации одной логической функции требуется произво дить опрос внешнего сигнала и анализ его на требуемое состояние с запоминанием результата по неоколько раз в течение одного цикла вычисления. Это приводит к снижению быстродействия, увеличению шагов программирования, а значит и обьема управляющей программы в целом. Помимо этого, для реализации нескольких функций, имеющих общую часть, требуется производить обработку ее для каждой функции Это также ведет к увеличению времени цикла решения управляющей программы, ее объема и увеличению шагов програм мирования. Кроме того, известное устройство не имеет возможности возврата к нача лу программы после завершения послед ней логической операции, что приводи к увеличению времени обработки за счет опроса всего объема памяти, заложенного в устройстве, так как рабочая программа может анимать незна чительную ее часть. Недостатком этого устройства явля ется также отсутствие возможности запоминания и сохранения информации о местоположении управляемого объекта в цикле, что существенно снижает область применения данного устройст.ва, так как полностью детерменирЛван ные объекты управления применяются достаточно редко. Например, при многократном возврате механизма в одно

то же положение необходимо запоминание количества совершенных ходов.

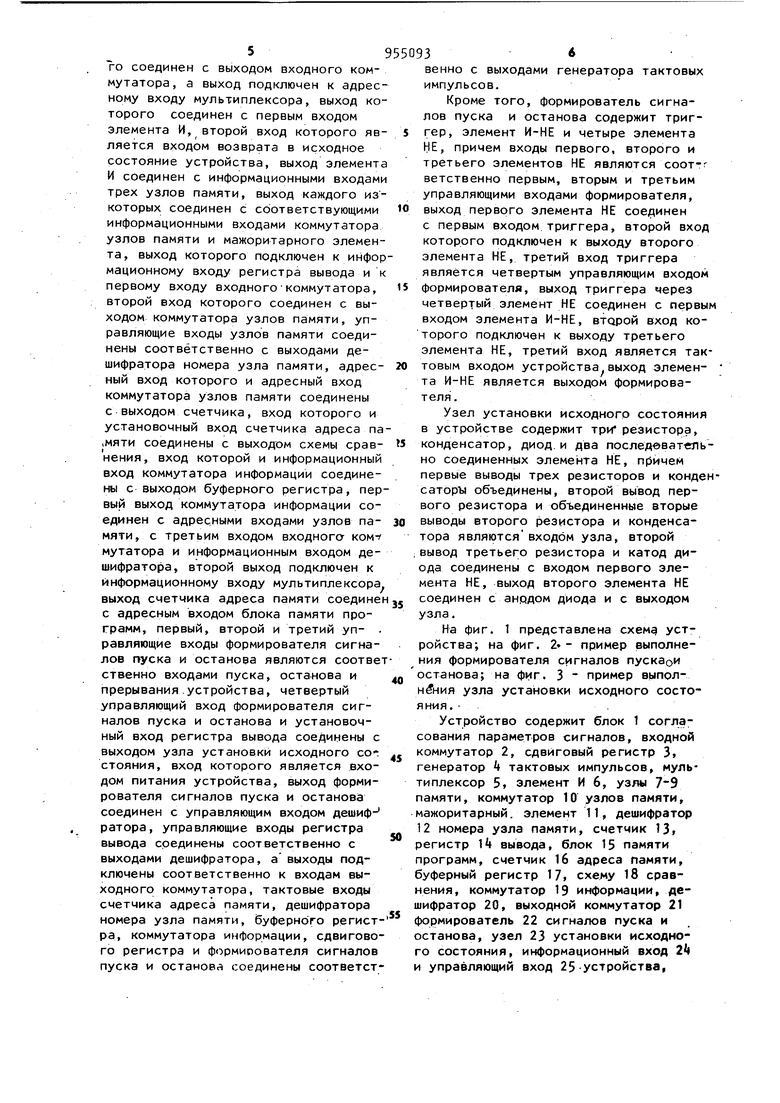

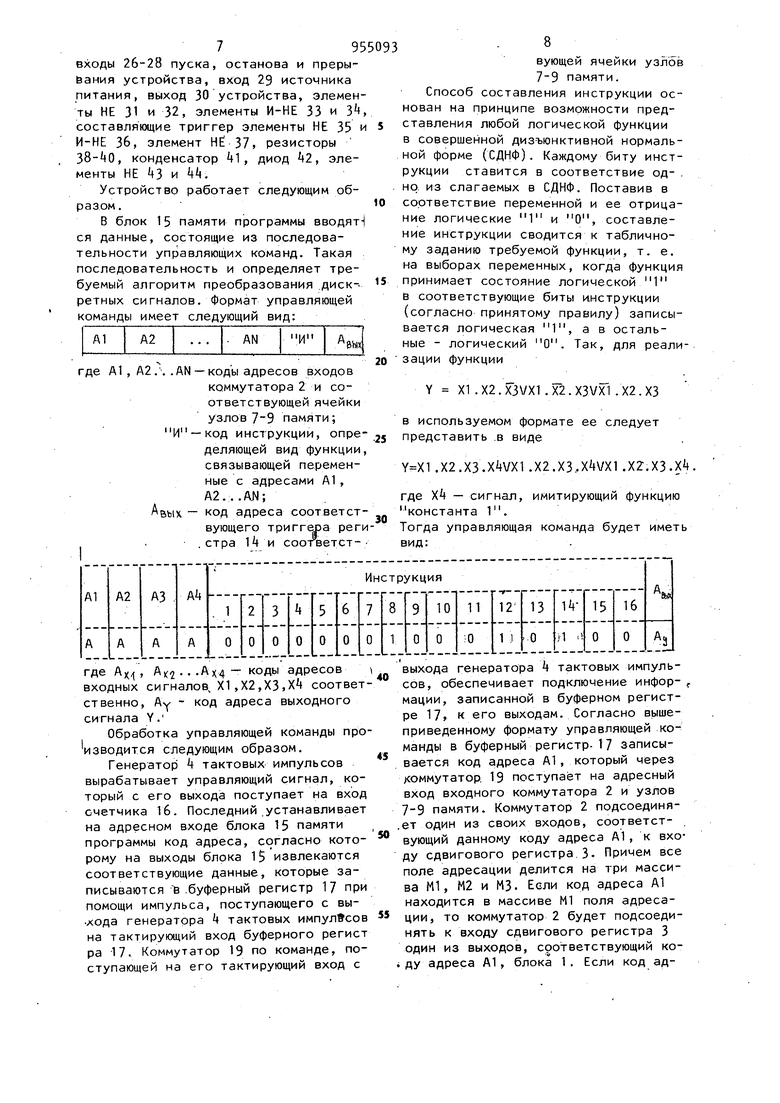

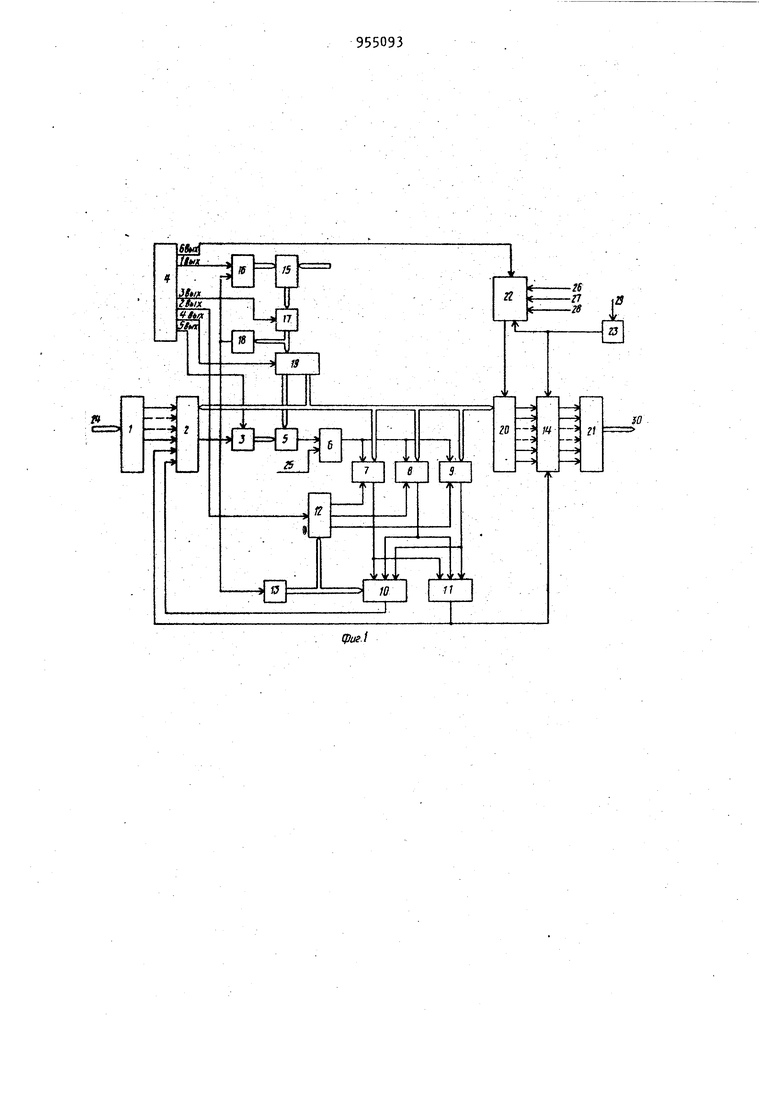

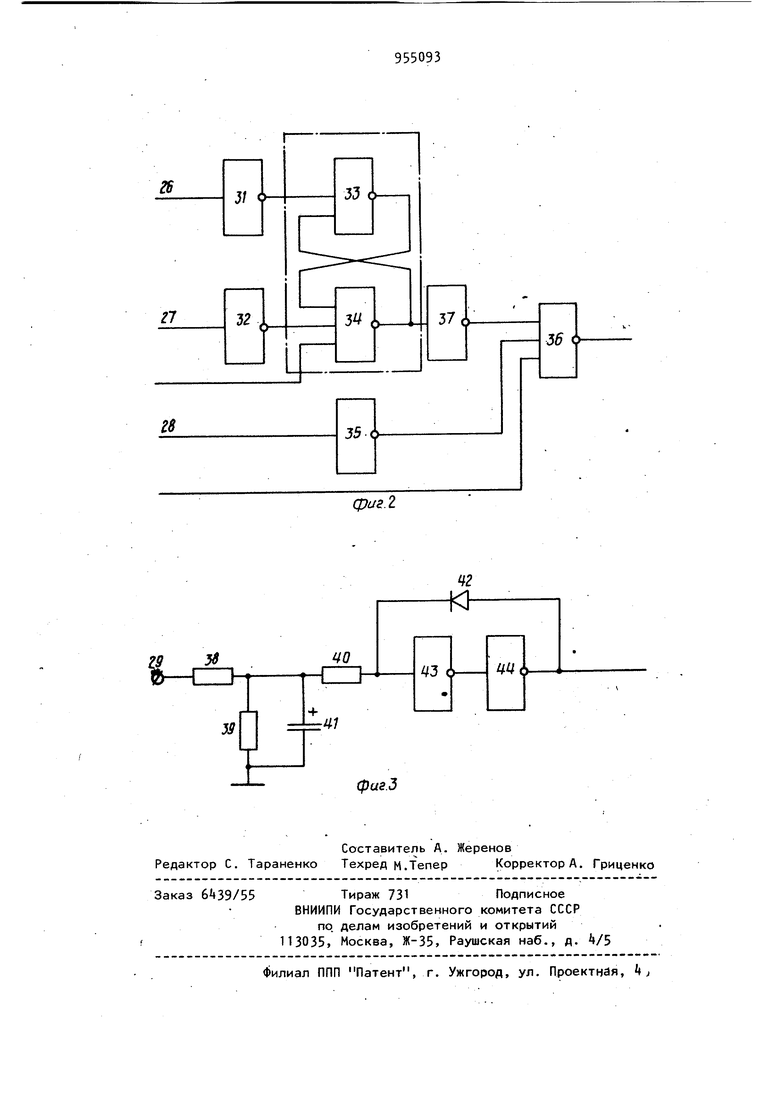

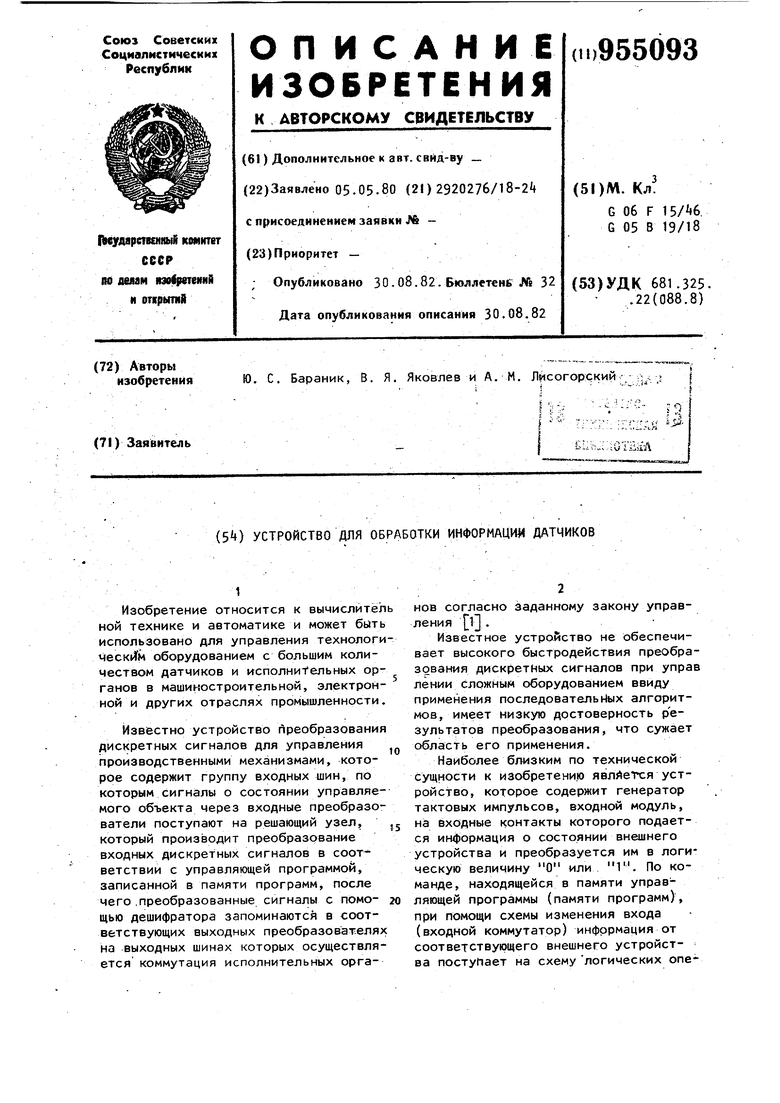

Кроме того, работа известного устройства в условиях индустриальных помех подвержена ложным срабатываниям, ввиду того, что на исполнительные органы поступают выходные сигналы в результате однократной обработки входных сигналов. Особенно это критично при подключении к выходным преобразователям быстродействующих исполнительных оргайов (например, при подключении тиристорных усилителей) и при наличии синхронных помех, которые мосовпадать с обработкой одних и тех же участков программы. Таким образом, достоверность преобразования входных сигналов известным устройством в условиях промышленной эксплуатаций невысокая. Данное устройство требует последовательного включения питания самого устройства и питания исполТ1ительных , органов, которые подключены к выходам выходных преобразователей устройства. Это связано с тем, что при одновременной пода.че питания на устройство и ,. исполнительные органы возможны ложные срабатывания последних из-за неопределенности состояния элементов памяти устройства. Этот недостаток снижает, область применения устройства и его надежность. . Цель изобретения - повышение быстродействия и надежности устройства. Поставленная цель достигается тем, что в устройство, содержащее входной коммутатор, информационные входы которого соединены соответственно с выходами блока рассогласования параметров сигналов, вход которого является первым информационным входом устройства, выходной коммутатор, выход которого является выходом.устройства, блок памяти программ, информационный вход которого является вторым информационным входом устройства, а выход подключен к информационному входу буферного регистра,- дешифратор и генератор .тактовых импульсов, введены счетчик адреса памяти, схема сравнения, коммутатор информации, формирователь сигналов пуска и останова, узел установки исходного состояния, регистр вывода, узел памяти, и,мультиплексор,дешифратор номера узяа памяти,счетчик,коммутатор узлов памяти,мажоритарный э 1емент и сдвиговый егистр, и нформационный вход котррого соединен с выходом входного коммутатора, а выход подключен к адрес ному входу мультиплексора, выход которого соединен с первым входом элемента И, второй вход которого является входом возврата в исходное состояние устройства, выход элемента И соединен с информационными входами трех узлов памяти, выход каждого изкоторых соединен с сбответствующими информационными входами коммутатора узлов памяти и мажоритарного элемента, выход которого подключен к инфор мационному входу регистра вывода и к первому входу входного-коммутатора, второй вход которого соединен с выходом коммутатора узлов памяти, управляющие входы узлов памяти соединены соответственно с выходами дешифратора номера узла памяти, адресный вход которого и адресный вход коммутатора узлов памяти соединены с выходом счетчика, вход которого и установочный вход счетчика адреса па ,мяти соединены с выходом схемы еравнения, вход которой и информационный вход коммутатора информации соединены с выходом буферного регистра, пер вый выход коммутатора информации соединен с адресными входами узлов памяти, с третьим входом входного коммутатора и информационным входом дешифратора, второй выход подключен к информационному входу мультиплексора выход счетчика адреса памяти соедине с адресным входом блока памяти программ, первый, второй и третий управляющие входы формирователя сигналов пуска и останова являются соотве ственно входами пуска, останова и прерывания.устройства, четвертый управляющий вход формирователя сигналов пуска и останова и установочный вход регистра вывода соединены с выходом узла установки исходного со-. стояния, вход которого является входом питания устройства, выход формирователя сигналов пуска и останова соединен с управляющим входом дешифратора, управляющие входы регистра вывода соединены соответственно с выходами дешифратора, а выходы подключены соответственно к входам выходного коммутатора, тактовые входы счетчика адреса памяти, дешифратора номера узла памяти, буфернбго регист ра, коммутатора информации, сдвигово го регистра и формирователя сигналов пуска и останова соединены соответст венно с выходами генератора тактовых импульсов. Кроме того, формирователь сигналов пуска и останова содержит триггер, элемент И-НЕ и четыре элемента НЕ, причем входы первого, второго и третьего элементов НЕ являются соот-г ветственно первым, вторым и третьим управляющими входами формирователя, выход первого элемента НЕ соединен с первым входом триггера, второй вход которого подключен к выходу второго элемента НЕ, третий вход триггера является четвертым управляющим входом формирователя, выход триггера через четвертый элемент НЕ соединен с первым входом элемента И-НЕ, второй вход которого подключен к выходу третьего элемента НЕ, третий вход является тактовым входом устройства.выход элемента И-НЕ является выходом формирователя. Узел установки исходного состояния в устройстве содержит три резистора, конденсатор, диод.и два последовательно соединенных элемента НЕ, прзичем первые выводы трех резисторов и конденсаторы объединены, второй вывод первого резистора и объединенные вторые выводы второго резистора и конденсатора являютсявходом узла, второй вывод третьего резистора и катод диода соединены с входом первого элемента НЕ, выход второго элемента НЕ соединен с анрдом диода и с выходом узла. На фиг. 1 представлена схема устройства; на фиг. 2 - пример выполнения формирователя сигналов пускаои останова; на фиг. 3 пример выполн ния узла установки исходного состояния. Устройство содержит блок 1 согласования параметров сигналов, входной коммутатор 2, сдвиговый регистр 3, генератор 4 тактовых импульсов, мультиплексор 5, элемент И 6, узлы памяти, коммутатор 10 узлов памяти, мажоритарный, элемент 11, дешифратор 12 номера узла памяти, сметчик 13 регистр 14 вывода, блок 15 памяти программ, счетчик 16 адреса памяти, буферный регистр 17i схему 18 сравнения, коммутатор 19 информации, деифратор 20, выходной коммутатор 21 формирователь 22 сигналов пуска и станова, узел 23 установки исходного состояния, информационный вход 2k и управляющий вход 25-устройства. 795 входы 26-28 пуска, останова и прерыйания устройства, вход 29 источника питания, выход 30 устройства, элементы НЕ 31 и 32, элементы И-НЕ 33 и 3, составляющие триггер элементы НЕ 35 и И-НЕ 36, элемент НЕ 37, резисторы 38-40, конденсатор 41, диод 42, элементы НЕ 43 и 44. Устройство работает следующим образом. В блок 15 памяти программы вводятся данные, состоящие из последовательности управляющих команд. Такая последовательность и определяет требуемый алгоритм преобразования .диск-ретных сигналов. Формат управляющей команды имеет следующий вид: где А1 , А2. . .AN -коды адресов входов коммутатора 2 и соответствующей ячейки узлов памяти; И -код инструкции, определяющей вид функции связывающей переменные с адресами А1, A2...A.N; АВЫХ - код адреса соответствующего триггера реги . стра 14 и соответстгде АХ, А 2--- Х4- коды адресов входных сигналов, XI,Х2,ХЗ,Х4 соответ ственно, AY - код адреса выходного сигнала Y. Обработка управляющей команды про изводится следующим образом. Генератор 4 тактовых импульсов вырабатывает управляющий сигнал, который с его выхода поступает на вход счетчика 16. Последний .устанавливает на адресном входе блока 13 памяти программы код адреса, согласно кото рому на выходы блока 15 извлекаются соответствующие данные, которые записываются в .буферный регистр 17 при помощи импульса, поступающего с выхода генератора 4 тактовых импульсов на тактирующий вход буферного регист ра 17. Коммутатор 19 по команде, поступающей на его тактирующий вход с вующей ячейки узлов 7-9 памяти. Способ составления инструкции основан на принципе возможности представления любой логической функции в совершенной дизъюнктивной нормальной форме (СДНФ). Каждому биту инструкции ставится в соответствие од- . но из слагаемых в СДНФ. Поставив в соответствие переменной и ее отрицание логические 1 и О, составление инструкции сводится к табличному заданию требуемой функции, т. е. на выборах переменных, когда функция принимает состояние логической 1 в соответствующие биты инструкции (согласно принятому правилу) записывается логическая 1, а в остальные - логический О. Так, для реализации функции Y XI .X2.X3VX1.X2.X3VXl .Х2.ХЗ в используемом формате ее следует представить в виде .X2.X3.X4VX1.X2.X3,X4VX1.X2.X3.X4, где Х4 - сигнал, имитирующий функцию константа 1. Тогда управляющая команда будет иметь выхода генератора 4 тактовых импульсов, обеспечивает подключение информации, записанной в буферном регистре 17, к его выходам. Согласно вышеприведенному формату управляющей команды в буферный регистр-17 записывается код адреса А1, который через коммутатор 19 поступает на адресный вход входного коммутатора 2 и узлов памяти. Коммутатор 2 подсоединяет один из своих входов, соответст- , вующий данному коду адреса А1, к входу сдвигового регистра.3. Причем все поле адресации делится на три массива Ml, М2 и МЗ. Если код адреса А1 находится в массиве Ml поля адресации, то коммутатор 2 будет подсоединять к входу сдвигового регистра 3 один из выходов, соответствующий коду адреса А1, блока 1. Если код ад995реса А1 находится в массиве М2 поля адресации, то к входу сдвигового регистра 3 будет подсоединяться выход мажоритарного элемента 11, а в случае, когда код адреса А1 находится в массиве МЗ, коммутатор 2 подсоединяет выход коммутатора 10 к входу сдвигового регистра 3. Поле адресаци трех узлов 7-9 памяти состоит из мас сивов М2 и МЗ, совпадающих между собой, т. е. появление на адресных вхо дах узлов памяти двух одноименных кодов, относящихся к массивам М2 и МЗ, вызывает обращение к одним и тем же ячейкам памяти. Например, исключение дешифрации старшего разря да кода адреса в узлах памяти, отличающего массивы М2 и ИЗ между собой, вызывает обращение к одним и тем же ячейкам. Дешифратор 12 по сиг налу, поступающему на его вход с выхода генератора k тактовых импульсов, обеспечивает режим чтения узлов 7-9 памяти, на время обработки кода адреса А1. Сигнал, соответствующий коду адре са А1, запоминается в сдвиговом реги стре 3 при поступлении на его тактирующий вход сигнала с выхода генератора k тактовых импульсов. Далее генеоатор k вырабатывает следующий сигнал, который с его выхода поступает . на вход счетчика 16. Последний инициирует извлечение из блока 15 памяти программ и запись в буферный регистр 17 кода адреса А2 согласно приведенному формату управляющей команды. Обработка кода адреса А2 производится аналогично обработке кода адреса А1 и заканчивается запоминанием в сдвиговом регистре 3 выбранного сигнала, соответствующего коду адреса А2. Таким же образом производится обработка кода адреса A3 и кода адреса А4, В результате этого в сдвиговом регист рё 3 будет находиться информация о текущем состоянии группы (четырех) переменных, которая подается на,адресный вход мультиплексора 5. Затем генератор Ц тактовых .импульсов вырабатывает еще один управляющий сигнал, который с его выхода поступает на вход счетчика 16. Последний ини циирует извлечение из блока 15 и запись в.буферный регистр 17 кода инструкции И и кода адреса выхода Agyj,, в соответствии с приведенным форматом управляющей команды. Коммутатор 19 осуществляет подсоединение кода 10 : адреса выхода к одному выходу, а кода инструкции И к второму выходу, который связан с информационным входом мультиплексора 5. Последний подсоединяет к информационным входам трех ; узлов памяти через элемент И 6 тот бит инструкции И, который соответствует требуемому значению функции для текущего набора значений переменных, записанных в сдвиговом регистре 3. Дешифратор 12 по сигналу, поступающему на его вход с выхода генератора t, осуществляет выбор узла памяти в соответствии с кодом, поступающим с выхода счетчика 13. В выбранный узел памяти производится запись сигнала с информационного вж)да по адресу, установленному на его адресных входах. Затем дешифратор 12 переводит все три узла 7-9 памяти в режим чтения. Считанная информация поступает на входы мажоритарного элемента 11, осуществляющего логику типа два из трех, т. е. на выходе будет состряние, соответствующее состоянию хотя бй двух входов элемента. Полученный на выходе мажоритарного элемента 11 сигнал поступает на информационный вход регистра 1, в один из триггеРОВ которого, соответствующий коду адреса, установленному на входах дешифратора 20, производится запись сигнала с информационного входа при помощи возбуждения соответствующего входа записи регистра It по команде, поступающей с выхода генератора тактовых импульсов на управляющий вход дешифратора 2t) через формирователь 22. Выходы триггеров регистра 1 связаны с входами коммутатора 21, на выходах которого осуществляется коммутация исполнительных органов управляемого объекта. После завершения обработки всей программы, состоящей из Набора описанных выше управляющих команд, из блока 15 памяти программы йзвлекает запрещенныйкод адреса А ся все нули) и записывается в пример. буферный регистр 17. Схема 18 сравнения представляющая собой схему совпадения по нулям, трактует этот код как команду конца цикла выполнения программы и на ее выходе появляется сигнал, который поступает на установочный вход счетчика 16 и на . вход счетчика 13- Осуществляется переход к началу управляющей программы а содержимое счетчика 13 увеличивает 1, Счетчик 13 имеет модуль ся на равный трем, и его сбдержимое счета, является указателем узла 7 памяти либо 8, либо 9. в который в текущем цикле обработки управляющей программы производится запись получаемых результатов. Таким образом, в трех последовательнах циклах выполнения программы производится запись результатов обработки информации в одноименные ячейки трех различных узлов памяти, что позволяет иметь на выходе мажоритарного элемента 11 временную интегральную оценку обработки информации при одновременном чтении содержимого одноименных ячеек трех узлов 7-9 памяти. На выходе ком мутатора 10, выполняющего функции селектора, в отличие от выхода мажоритарного элемента 11 присутствуют результаты обработки, выполненные в текущем цикле управляющей программы. Коммутатор.10, будучи подключенным к одному из входов коммутатора 2, позволяет реализовать функции запоминания предыдущих состояний входных устройств. Это позволяет сохранять информацию о местоположении управляемого объекта в цикле при повторяющихся входных условиях в цикле. Начилие этой связи, кроме тог, позволяет реализовать счет повторяющихся циклов. Использование в качестве резуль татов обработки информации ее интегрального значения, которое присутствует на выходе мажоритарного элемента 11, позволяет значительно увеличить достоверность преобразования ин формации, так как выход мажоритарного элемента 11 определяет состояние регистра 14 и, как следствие, состояние исполнительных органов управляемого объекта. Использование мажоритарного элемента 11 в качестве промежуточного результата преобразования информации также позволяет повысить достоверность информации при дальнейшей обработке. Для установки устройства в исходное состояние, т. е.. сбросе всех . промежуточных запоминаний состояний управляемого объекта, служит внешний сигнал возврата в исходное состояние, который подается на один из входов элемента И 6, что приводит к обнулению узлов памяти в течение трех циклов обработки управляющей програм1мы. 9 312 При подаче напряжения питания на устройство для исключения ложных срабатываний исполнительных органов за счет неопределенности состояния регистра 1t служит узел 23, на выходе которого формируется сигнал установки регистра в исходное состояние (фиг. 3).На резистор 38 подается напряжение источника питания ( ) всего устройства. При подаче питания конденсатор 1 заряжается через резистор 38 и на выходе элемента ti удерживается сигнал логического О до того момента, пока конденсатор не зарядится до уровня порога сраба - тывания элемента 43. Для исключения генерации при достижении порога срабатывания выход элемента 3 соединен через диод 42 с входом элемента k, создавая положительную обратную связь. Таким образом, при включении питания на выходе узла формируется сигнал, служащий для установки в исходное состояние регистра 1 4 и запрета прохождения тактовых импульсов через формирователь 22. Формирователь 22 (фиг. 2) работает следующим образом. Сигнал С выхода триггера, инвертированный сигнал внешнего прерывания и сигнал с тактирующего вхоДа поступает на элемент 36. На выходе элемента 36 тактовые импульсы появятся в том случае, если отсутствуют сигналы внешнего прерывания, запрета и триггер установлен в единичное состояние сигналом внешнего пуска. Сигнал С управляюще го входа запрета поступает на второй триггер и служит для удерживания триггера в момент подачи напряжения питания. Формула изобретения 1. Устройство для обработки информации датчиков, содержащее входной коммутатор, информациояные входы которрго соединены соответственно с выходами блока согласования параметров сигналов, вход которого является первым информационным входом устройства, выходной коммутатор, выход которого является выходом устройства, блок памяти программ, информационный вход которого является вторым информационным входом устройства, а выход подключен к информационному входу буферного регистра, дешифратор и генератор тактовых импульсов, отличающееся тем, что, с целью повышения быстродействия и надежности, в него введены счетчик адреса памяти, схема сравнения, коммутатор информации, формирователь сигналов пуска и останова, узел установки исходного состояния, регистр вывода, узлы памяти, элемент И, мультиплексор, дешифратор номера узла памяти, счетчик, коммутатор узлов памяти, мажоритарный элемент и сдвиговый регистр, информационный вход которюго соединен о выходом входного коммутатора, а выход подключен к адресному входу мультиплексора, выход которого соединен с первым входом элемента И, второй вход которого является входом возврата в исходное состояние устройства, выход элемента И соединен с информа- 20 ре

ционными входами трех;- узлов памяти, выход каждого из которых соединен с соответствующими информационными входами коммутатора узлов памяти и мажоритарного элемента, выход которого Подключен к информационному входу регистра вывода и к первому входу входного коммутатора, второй вход которого соединен с выходом коммутатора узлов памяти, управляющие входы узлов памяти соединены соответственно с выходами дешифратора номера узла памяти, адресный вход которого и адресный вход коммутатора узлов памяти соединены с выходом счетчика, вход KOTOpoго и установочный вход счетчика адреса памяти соединены с выходом схемы сравнения, вход которой и информационный- вход коммутатора информации соединены с выходом буферного регистра, первый выход коммутатора информации соединен с адресными входами узлов памяти с третьим входом входного коммутатора и информационным входом де иифратора, второй выход подключен к информационному входу мультиплексора, выход счетчика адреса памяти соединен с адресным входом блока памяти программ, первый, второй и тоетий управляющие входы формирователя сигналов пуска и останова являются соответственно входами пуска, останова и прерывания устройства, четвертый управляющий вход, формирователя сигналов пуска и останова и установочный вход регистра вывода соедикень с выхо дом узла установки исходного состоя ния, вход которого является входом

питания устройства, выход формирователя сигналов пуска и останова соединен с управляющим входом дешифратора, управляющие входы регистра вывода соединены соответственно с выходами дешифратора, а выходы подключены соответственно к входам выходного коммутатора, тактовне входы счетчика адреса памяти, дешифратора номера узла памяти, буферного регистра, коммутатора информации, сдвигового регистра и формирователя сигналов пуска и останова соединены соответственно с выходами генератора тактовых импульсов.

-JTn

-26

- ti

L

-

h--9

БН -

-

.ZT

Г

/0

-

f/

т -

гб

J/

ъг

г7

37

фиг.1

Авторы

Даты

1982-08-30—Публикация

1980-05-05—Подача