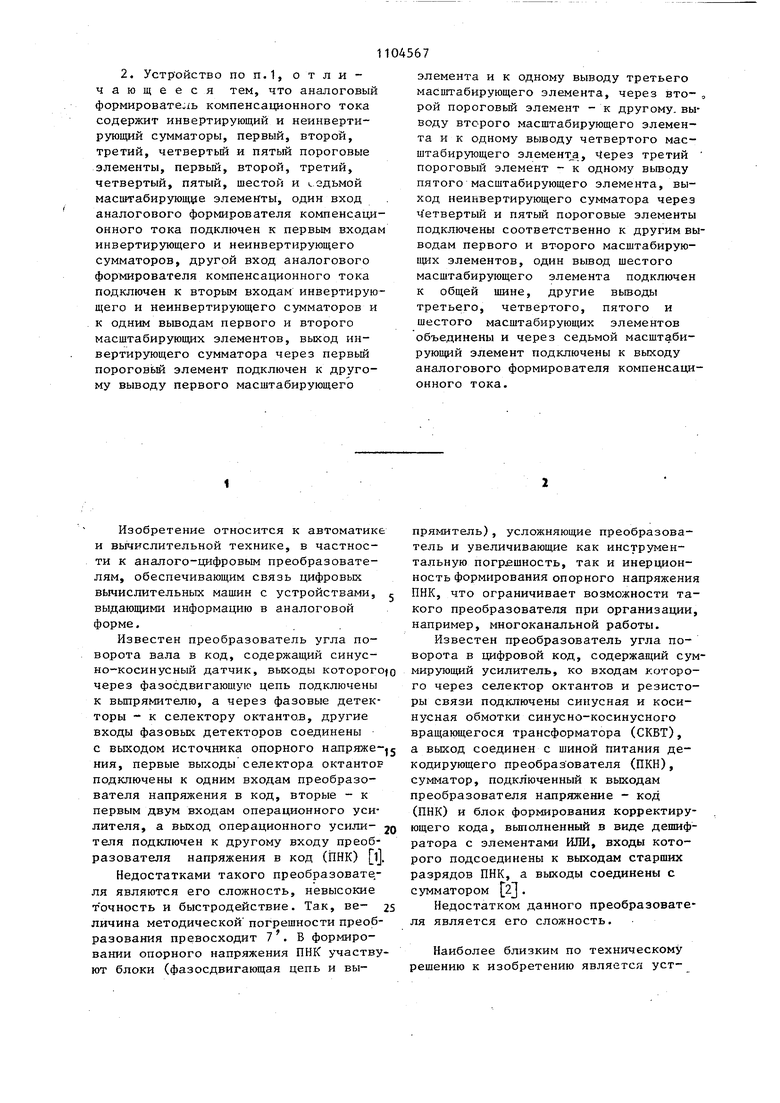

Синуснь/й

Фиг.1 выход

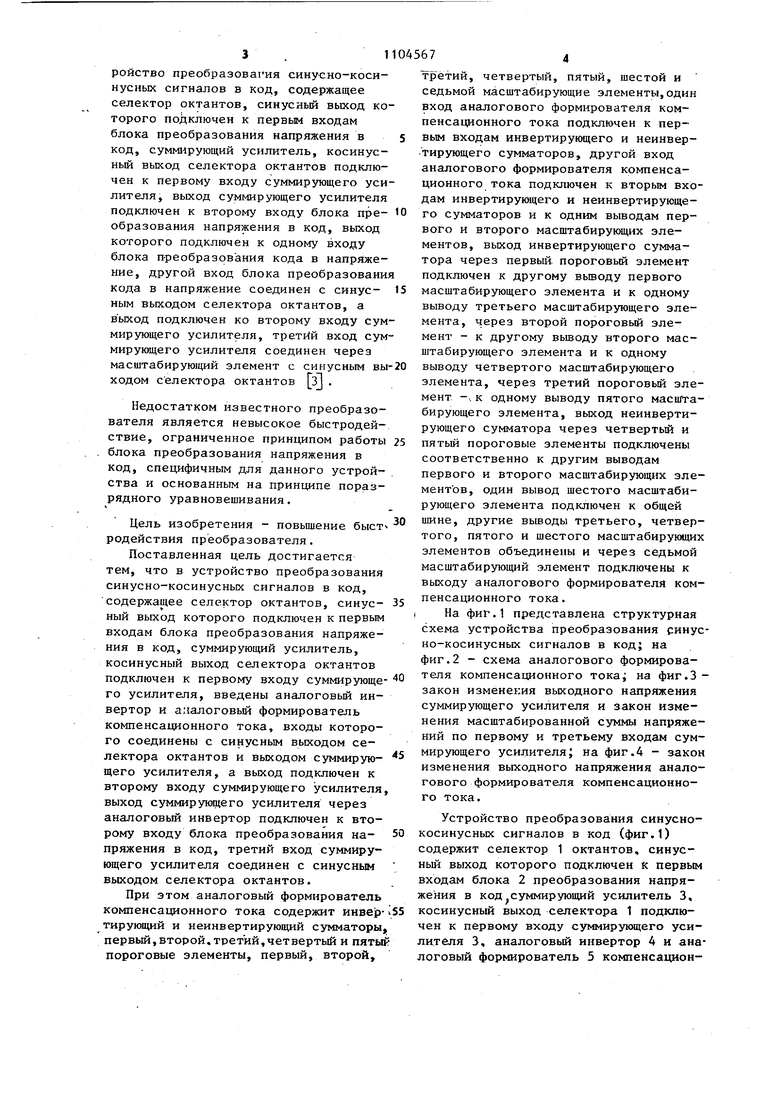

2. Устройство ПОП.1, отличающееся тем, что аналоговый формировате хь компенсационного тока содержит инвертирующий и неинвертирующий сумматоры, первый, второй, третий, четвертый и пятьй пороговые элементы, первый, второй, третий, четвертый, пятый, шестой и сгдьмой масштабирующуе элементы, один вход аналогового формирователя компенсационного тока подключен к первым входа инвертирующего и неинвертирующего сумматоров, другой вход аналогового формирователя компенсационного тока подключен к вторым входам инвертирующего и неинвертирующего сумматоров и к одним выводам первого и второго масштабирующих элементов, выход инвертирующего сумматора через первый пороговьй элемент подключен к другому выводу первого масштабирующего

элемента и к одному выводу третьего масштабирующего элемента, через второй пороговьй элемент - к другому, выводу второго масштабирующего элемента и к одному выводу четвертого масштабирующего элементна, iepes третий пороговый элемент - к одному выводу пятого масштабирующего элемента, выход неинвертирующего сумматора через четвертый и пятый пороговые элементы подключены соответственно к другим выводам первого и второго масштабирующих элементов, один вьюод шестого масштабирующего элемента подключен к общей шине, другие вьшоды третьего, четвертого, пятого и шестого масштабирующих элементов объединены и через седьмой масштабирующий элемент подключены к выходу аналогового формирователя компенсационного тока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь угла поворота вала в код | 1990 |

|

SU1751850A1 |

| Преобразователь угла поворота вала в код | 1984 |

|

SU1231610A1 |

| Цифроаналоговый синусно-косинусный преобразователь | 1982 |

|

SU1073780A1 |

| Преобразователь угла поворота вала в код | 1983 |

|

SU1113830A2 |

| Следящий преобразователь угла поворота вала в код | 1984 |

|

SU1243092A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1261118A2 |

| Преобразователь угла поворота вала в код | 1981 |

|

SU993303A1 |

| Преобразователь угол-код | 1986 |

|

SU1336242A1 |

| Устройство для синусно-косинусного цифро-аналогового преобразования | 1983 |

|

SU1129632A1 |

| Преобразователь угла поворота вала в двоичный код | 1977 |

|

SU657447A1 |

1. УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ СИНУСНО-КОСИНУСНЫХ СИГНАЛОВ В КОД, содержащее селектор октантов, синусньй выход которого подключен к первым входам блока преобразования напряжения в код, суммирующий усилитель, косинусный выход селектора октантов подключен к первому входу суммирующего усилителя, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены аналоговый инвертор и аналоговый формирователь компенсационного тока, входы которого соединены с синусным выходом.селектора октантов и выходом суммирующего усилителя, а выход подключен к второму входу суммирующего усилителя, выход суммирующего усилителя через аналоговый инвертор по,чключен к второму входу i блока преобразования напряжений в код, третий вход суммирукщего усили(Я теля соединен с синусным выходом сес: лектора октантов.

Изобретение относится к автоматике и вычислительной технике, в частности к аналого-цифровьм преобразователям, обеспечивающим связь цифровых вычислительных машин с устройствами, с выдающими информацию в аналоговой форме.

Известен преобразователь угла поворота вала в код, содержащий синусно-косинусный датчик, выходы которого о через фазосдвигаюшую цепь подключены к выпрямителю, а через фазовые детекторы - к селектору октантов, другие входы фазовых детекторов соединены с выходом источника опорного напряже- д ния, первые выходы селектора октантов подключены к одним входам преобразователя напряжения в код, вторые - к первым двум входам операционного усилителя, а выход операционного усили- 20 теля подключен к другому входу преобразователя напряжения в код (ilHK) lj.

Недостатками такого преобразовате,ля являются его сложность, невысокие точность и быстродействие. Так, ве- 25 личина методической погрешности преобразования превосходит 7. Б формировании опорного напряжения ПНК участвуют блоки (фазосдвигающая цепь и выпрямитель) , усложняющие преобразователь и увеличивающие как инструментальную погрешность, так и инерционность формирования опорного напряжения ПНК, что ограничивает возможности такого преобразователя при организации, например, многоканальной работы.

Известен преобразователь угла поворота в цифровой код, содержащий суммирующий усилитель, ко входам которого через селектор октантов и резисторы связи подключены синусная и косинусная обмотки синусно-косинусного вращающегося трансформатора (СКБТ), а выход соединен с шиной питания декодирующего преобразователя (ПКН), сумматор, подключенный к выходам преобразователя напряжение - код (ПНК) и блок формирования корректирующего кода, выполненный в виде дешифратора с элементами ИЛИ, входы которого подсоединены к выходам старших разрядов ПНК, а выходы соединены с сумматором zj .

Недостатком данного преобразователя является его сложность.

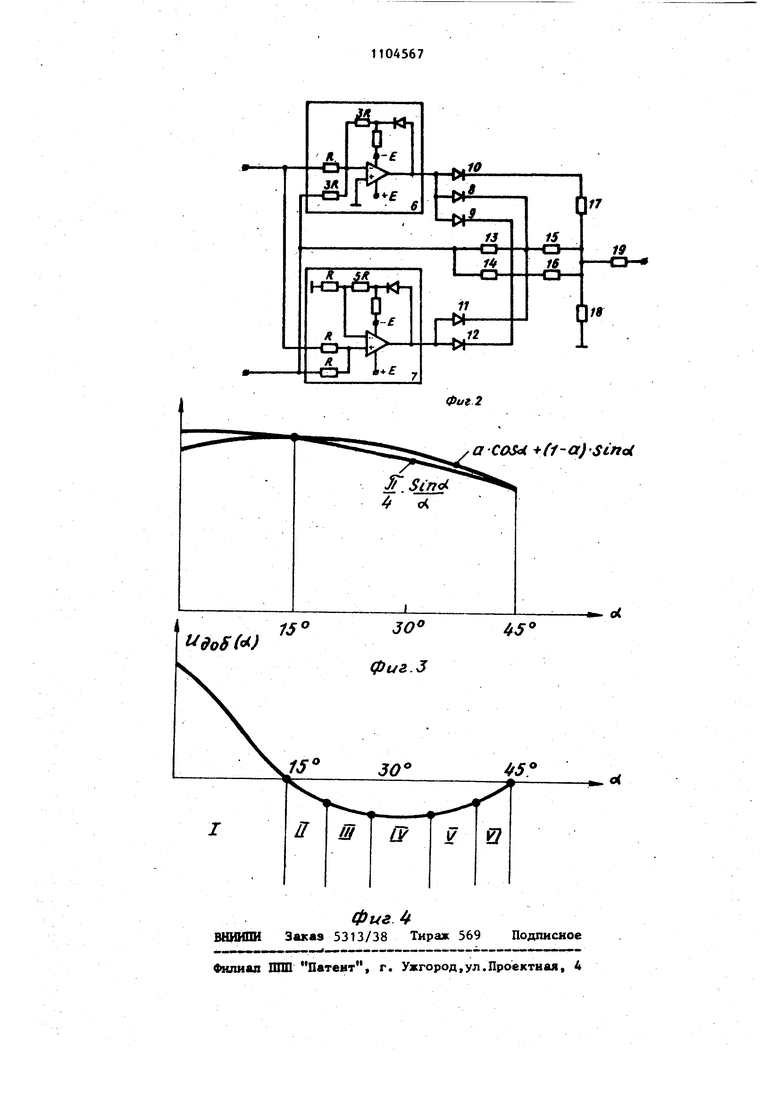

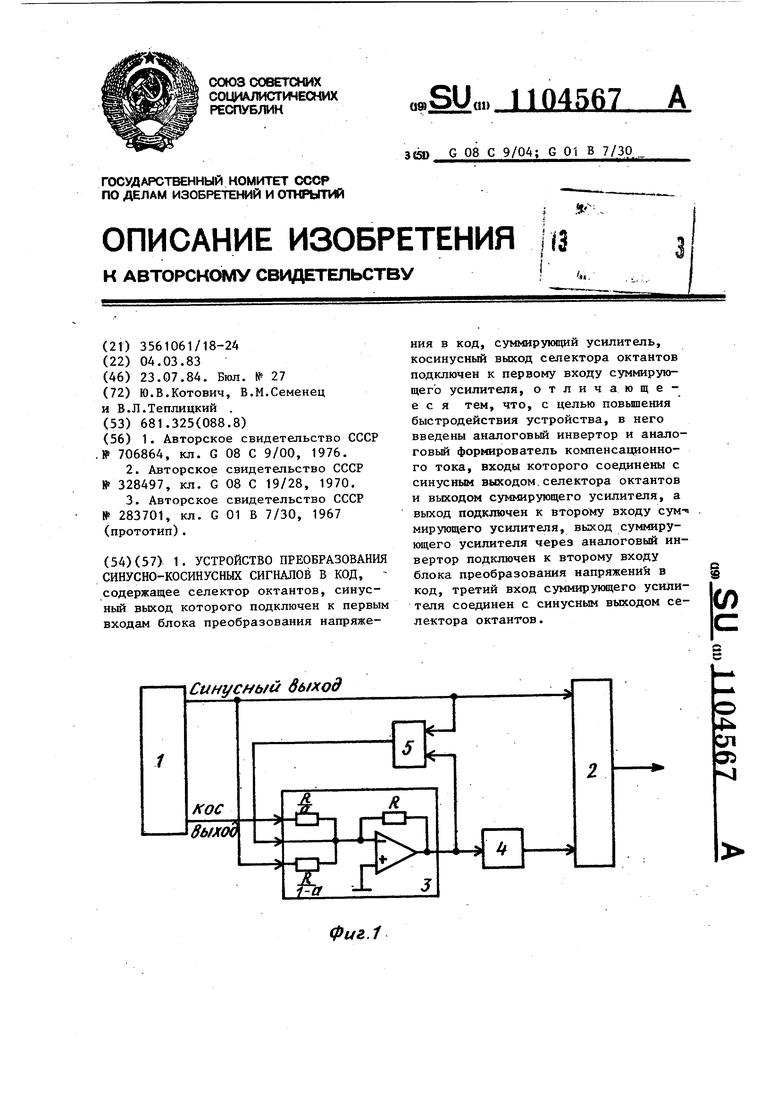

Наиболее близким по техническому решению к изобретению является устройство преобразовагия синусно-косинусных сигналов в код, содержащее селектор октантов, синусный выход ко торого подключен к первым входам блока преобразования напряжения в код, суммирующий усилитель, косинусный выход селектора октантов подключен к первому входу суммирующего уси лителя, выход суммирующего усилителя подключен к второму входу блока преобразования напряжения в код, выход которого подключен к одному входу блока преобразования кода в напряжение, другой вход блока преобразовани кода в напряжение соединен с синусным выходом селектора октантов, а выход подключен ко второму входу сум мирующего усилителя, третий вход сум мирующего усилителя соединен через масштабирующий элемент с синусным вы ходом селектора октантов 3j . Недостатком известного преобразователя является невысокое быстродействие, ограниченное принципом работы блока преобразования напряжения в код, специфичньм для данного устройства и основанным на принципе поразрядного уравновешивания. Цель изобретения - повышение быст родействия преобразователя. Поставленная цель достигается тем, что в устройство преобразования синусно-косинусных сигналов в код, содержащее селектор октантов, синусный выход которого подключен к первым входам блока преобразования напряжения в код, суммирующий усилитель, косинусный выход селектора октантов подключен к первому входу суммирующе го усилителя, введены аналоговый инвертор и аналоговый формирователь компенсационного тока, входы которого соединены с синусным выходом селектора октантов и выходом суммирующего усилителя, а выход подключен к второму входу суммирующего усилителя выход суммирующего усилителя через аналоговый инвертор подключен к второму входу блока преобразования напряжения в код, третий вход суммирующего усилителя соединен с синусным выходом селектора октантов. При этом аналоговый формирователь компенсационного тока содержит инвер тирующий и неинвертирующий сумматоры первый,второй,третий,четвертый и пяты пороговые элементы, первый, второй. 1 674 третий, четвертый, пятый, шестой и седьмой масштабирующие элементы,один вход аналогового формирователя компенсационного тока подключен к первым входам инвертирующего и неинвертирующего сумматоров, другой вход аналогового формирователя компенсационного тока подключен к вторым входам инвертирующего и неинвертирующего сумматоров и к одним выводам первого и второго масштабирующих элементов, выход инвертирующего сумматора через первый, пороговый элемент подключен к другому вьшоду первого масштабирующего элемента и к одному выводу третьего масштабирующего элемента, через второй пороговый элемент - к другому вьшоду второго масштабирующего элемента и к одному выводу четвертого масштабирующего элемента, через третий пороговый элемент -S к одному выводу пятого масиггабирующего элемента, выход неинвертирующего сумматора через четвертый и пятый пороговые элементы подключены соответственно к другим выводам первого и второго масштабирующих элементов, один вывод шестого масштабирующего элемента подключен к общей шине, другие вьшоды третьего, четвертого, пятого и шестого масштабирующих элементов объединены и через седьмой масштабирующий элемент подключены к выходу аналогового формирователя компенсационного тока, На фиг.1 представлена структурная схема устройства преобразования ринусно-косинусных сигналов в код; на фиг.2 - схема аналогового формирователя компенсационного тока; на фиг.З закон изменения выходного напряжения суммирующего усилителя и закон изменения масштабированной суммы напряжений по первому и третьему входам суммирующего усилителя; на фиг.4 - закон изменения выходного напряжения аналогового формирователя компенсационного тока. Устройство преобразования синуснокосинусных сигналов в код (фиг.1) содержит селектор 1 октантов, синусный выход которого подключен к первым входам блока 2 преобразования напряжения в код суммирующий усилитель 3, косинусный выход селектора 1 подключен к первому входу суммирующего усилителя 3, аналоговый инвертор 4 и аналоговый формирователь 5 компенсационЯого тока, входы которого соединены р синусным выходом селектора 1 октан тов и выходом суммирующего усилителя 3, а выход подключен к второму входу суммирующего усилите.пя 3, выход суммирующего усилителя 3 через аналоговый инвертор 4 подключен к второму входу блока преобразования напряжения в код, третий вход суммирующего усилителя соединен с синусным выходом селектора октантов. Аналоговый формирователь 5 компен сационного тока содержит инвертирующий 6 и неинвертирующий. 7 сумматоры, первый 8, второй 9, третий 10, четвертьй 11 и пятый 12 пороговые элементы (диоды), первый 13, второй 14, третий 15, четвертый 16, пятый 17, шестой 18 и седьмой 19 масштабирующи элементы (реэисторы), один вход аналогового формирователя 5 компенсационного тока подключен к первым входам инвертирующего 6 и неинвертирующего 7 сумматоров, другой вход аналогового формирователя 5 компенсационного тока подключен к вторым входам инвертирующего 6 и неинвертирующего 7 сумматоров и к одним выводам первого 13 и второго 14 резисторов, выход инвертирующего сумматора 6 через первый диод 8 подключен к другому вьшоду первого резистора 13 и к одному выводу третьего резистора 15, через второй диод 9 - к другому выводу второго резистора 14 и к одному выводу четвертого резистора 16, через третий диод 10 - к одному вьшоду пятого резистора 17, выход неинвертирующего сумматора 7 через четвертьй 11 и пятый 12 диоды подключен соответственно к другим вьшодам первого 13 и второго 14 резисторов, один вьшод шестого резистора 18 подключен к общей шине, другие выводы третьего 15, четвертого 16, пятого 17 и шестого 18 резисторов объединены и через седьмой резистор 19 подключены к выходу аналогового формирователя 5 компенсационного тока. Устройство работает следующим образом. Селектор 1 формирует на своих выходах сигналы, пропорциональные синусу и косинусу угла 06 в пределах первого октанта, причем оба этих сиг нала имеют положительную фазу, а амп литуда синусного сигнала не превосходит амплитуды косинусного сигнала. На опорный вход блока 2 подается с выхода инвертора 4 напряжение Uon , амплитуда которого с высокой точностью пропорциональна величине/ul., На измерительньй вход блока 2 подается с синусного выхода селектора 1 напряжение, пропорциональное Уузм оЬ Выходной код Q преобразователя получается пропорциональным углу об в пределах первого октанта угла из отношения напряжений Uj. к Uon: . Важным достоинством устройства является возможность построения блока 2по любому из известных методов аналого-одфрового преобразования, в том числе и. по Нсшболее быстр одействующему методу параллельного преобразования (считывания), что обусловлено отсутствием зависимости опорного (эталонного) напряжения от выходного кода. Рассмотрим более подробно процесс формирования опорного напряжения UgnНа выходе суммирующего усилителя 3воспроизводится напряжение , амплитуда которого изменяется по закону {a.uco6ot+0-c« Us;nottUg((i)-J i: iii°i, где ,73205 - коэффициент; iJg()--добавочное напряжение, равное по величине произведению выходного компенсационного тока формирователя 5 на величину сопротивления обратной связи суммирующего усилителя 3. На фиг.З показан закон изменения идеального опорного напряжения И- - и той части напряжения U2 которая определяется величинами сигналов, подаваемых на первый и третий входы суммирующего усилителя 3: асо5о(-4( . Эта часть является основной так как составляет не менее 937, от напряения 112 Введение в устройство формирова ля 5 компенсационного тока по воля7 . ет приблизить закон изменения напряжения Uj к требуемому виду ,, sinit необходимой степенью Оо точности, При подаче напряжения U 9чп А с синусного выхода селе.ктора 1 на перв входы сумматоров 6 и 7 и напряжения Ug с выхода суммирующего усилителя 3 на вторые входы сумматоров 6 и 7 на их выходах формируются (если пренебречь падением напряжения на диодах) следующие напряжения: U - 5Ueinat- + , Uj 3i. U. Эти два напряжения, подаваемые на пороговые элементы (аноды диодов) со ответственно 8, 9, 10 и 11, 12, а также напряжение U , подаваемое на общие вьюоды масштабирующих элементов (резисторов) 15 и 16, формируют на выходе формирователя 5, а именно на резисторе 12, подсоединенном к второму входу суммирующего уси лителя 3-, компенсационный ток, величина которого в зависимости от угла поворота «L может изменяться по шести нелинейным законам. Напряжение И(otl имеет вид, изображенный на фиг.4, и для каждого из шести участков компенсации описывается следукицими вьфа жениями: -на первом участке (открыты диод 8-10): ,-иб-, -на втором (открыты диоды 8 и 9) UgUbkz-Ufii -на третьем (открыт диод 8): DgkbbU - -iUjV / on -на четвертом (диоды 8-1/ запер . У -на пятом участке (открыт диод UgU , -на шестом участке (открыты диоды 1 1 и 12): и(« |--К211т; где К, Kj, К, к;, постоянные коэффициенты, определяемые величинами резисторов 13-19 678 При выборе номиналов этих резисторов из условия R,3 0,799R , 4,310R ,K,5 2,229R , 2,143R, R,, 2,3R , R,e Q,105R , R, 2R, a . 0,73205, где R - сопротивление обратной связи суммирующего усилителя 3, величина методической погрешности линейного преобразования синусно-косинусных сигнгшов в код не превьюит 1,4 угловых минуты. При соответствующем усложнении формирователя 5, связанном с увеличением числа участков компенсации, величина методической погрешности может быть уменьшена. Вспомогательные диоды, включенные в цепи рбратной связи сумматоров 6 и 7, служат для компенсации порога включения диодов 8-12, а отрицательное смещение, подаваемое на катоды вспомогательных диодов, необходимо для предотвращения их запирания при отрицательных значениях напряжений llb.Ur . Сформированное на выходе суммирующего усилителя 3 напряжение поступае т далее на инвертор 4, который „. g выполнен в виде операцион„ого усилителя с коэффициентом переда ,.- . я На выходе инвертора 4 формируется опорное напряжение ПОР - Ь для типового АЦП (в котором и преобразуемое и ortopHoe напряжения должны быть положительными). При работе с АЦП, допускающим подачу на опорный вход отрицательных напряжений, на этот вход может быть подано непосредственно напряжение 11 В рассмотренном устройстве в качестве блока 2 преобразования напряжения в код можно использовать АЦП параллельного или последовательноттапа nn m urkr«r unLT ттпг пегтппЯТАГТ1 НП - параллельного типа, поскольку входное и опорное напряжения являются неквантованными, а при использовании АЩ1 поразрядного кодирования уменьшается время переходных процессов в процессе преобразования. В результате время преобразования уменьшается, т.е. быстродействие устройства повышается. Экономический эффект от использования устройства определяется его техническим преимуществом.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Преобразователь угла поворота вала в код | 1976 |

|

SU706864A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-07-23—Публикация

1983-03-04—Подача