Изобретение относится к автоматике и вычислительной технике и может быть использовано в средствах отображения информации.

Известно устройство обработки данных с несколькими взаимосвязанными генераторами символов, состоящее из буферного запоминающего устройства, двух генераторов символов, устройства управления, селектора и индикатора 1.

Однако в данном устройстве каждый генератор символов предназначен для воспроизведения символов только одного определенного формата, что является существенным недостатком, поскольку изменения формата символов достигаются коммутацией генераторов, количество которых равно количеству используемых форматов символов. В целом, устройство обладает больщой аппаратурной сложностью и низкой надежностью работы.

Известен способ и устройство для генерации наборов символов. Устройство предназначено для восстановления исходной последовательности символов, содержащей минимальное число точек из сжатого формата сомволов, который содержит примерно в два раза меньшее количество точек. В устройстве имеется память для хранения сжатого формата символов в виде набора опорных точек из контуров. Хотя качество символов, синтезируемых из точек, будет низким, но зато требуется малый объем памяти. Для повыщения качества символов искусственно добавляются точки в исходный контур. Устройство содержит дещифратор, который по сигналам из памяти восстанавливает каждую пропущенную точку, формируя исходный формат символа. В устройстве имеется смеситель точек, объединяющий точки с выходов памяти и дещифратора. Управление работой устройства осуществляется блоком управления и синхронизации 2.

Недостатками такого устройства являются его сложность из-за необходимости восстановления примерно 50% точек в каждом из знаков, больщие временные затраты на преобразование из-за последовательного во времени восстановления каждой отсутствующей точки, а также малая универсальность при смене форматов отображаемых символов (при необходимости введения новых форматов).

Известно устройство формирования символов с помощью матричного шаблона элементов изображения, содержащее первый накопитель, хранящий число, соответствующее горизонтальному увеличению первоначального символа, второй накопитель хранит число, соответствующее вертикальному увеличению первоначального символа, независимо от первого накопителя, два формирователя дополнительных точек по строкам и столбцам в преобразованном символе для восстановления его исходной формы. Посгтедовательность работы задается блоком управления и синхронизации 3.

Недостатками данного устройства являются наличие двух накопителей (ПЗУ), в

которых должны храниться все возможные комбинации для формирования различных форматов, т.е. накопители должны иметь больщую емкость памяти, а также низкая универсальность из-за необходимости перепрограммирования накопителей при необходимости изменения форматов символов. Наиболее близким по технической сущности и достигаемому эффекту к изобретению является устройство преобразования матрицы знака (формирования символов),

содержащее блок преобразования размера по колонкам, коммутатор размера по колонкам, буферную память, блок преобразования размера по строкам, коммутатор размера по строкам, устройство управления матричным преобразователем. Это устройство позволяет увеличить исходную матрицу символа в два раза за счет введения дополнительных точек в строки и столбцы знака 4.

Недостатками известного устройства являются получение преобразованных матриц

по отношению к исходной только удвоенной кратности, что снижает функциональную гибкость устройства, низкая скорость преобразования из-за последовательного во времени преобразования (сначала все колонки, а затем все столбцы). Преобразованный (увеличенный) в устройстве символ имеет низкое качество и плохую читаемость из-за того, что дополнительные точки не вводятся в наклонные элементы символов (такие точки вводятся только в вертикальные и горизонтальные элементы). Кроме того, устройство не позволяет формировать матрицу символов, не кратную двум.

Цель изобретения - расширение области применения устройства за счет увеличения количества форматов точечно синтезируемых символов.

Поставленная цель достигается тем, что в устройство для формирования символов, содержащее последовательно соединенные блок памяти, первый блок элементов И и блок селекции, другой вход которого подключей к первому выходу блока коммутации, выход которого соединен с одним из входов регистра, другой вход которого соединен с третьим выходом блока управления, четвертый выход которого соединен с одним из входов блока памяти, другой вход которого является первым входом устройства, вторым входом которого является первый вход блока управления, пятый выход которого является первым выходом устройства, выход блока селекции подключен к второму входу блока коммутации и к одному из входов второго блока элементов И, другой вход которого соединен с выходом регистра, введены интерполятор наклонных отрезков, анализатор форматов, логический сумматор и

третий блок элементов И, выход которого является вторым выходом устройства, один из входов третьего блока элементов И подключен к шестому выходу блока управления, другой вход - к выходу регистра, подключенному к одному из входов интерполятора наклонных отрезков, другой вход которого соединен с выходом блока селекции, выход интерполятора наклонных отрезков подключен к одному из входов логического сумматора, другой вход которого соединен с выходом второго блока элементов И, выход логического сумматора подключен к третьему входу блока коммутации, один из входов анализатора форматов является третьим входом устройства, а другой вход - первым входом устройства, а выход анализатора форматов подключает к второму входу блока управления.

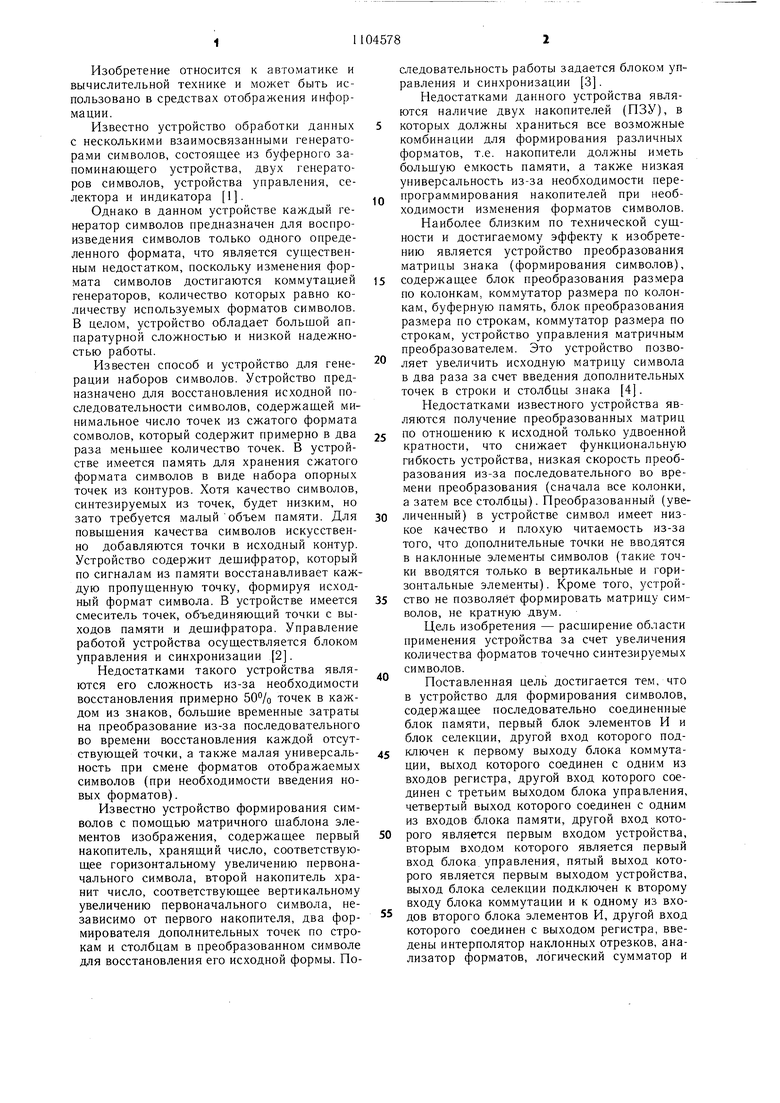

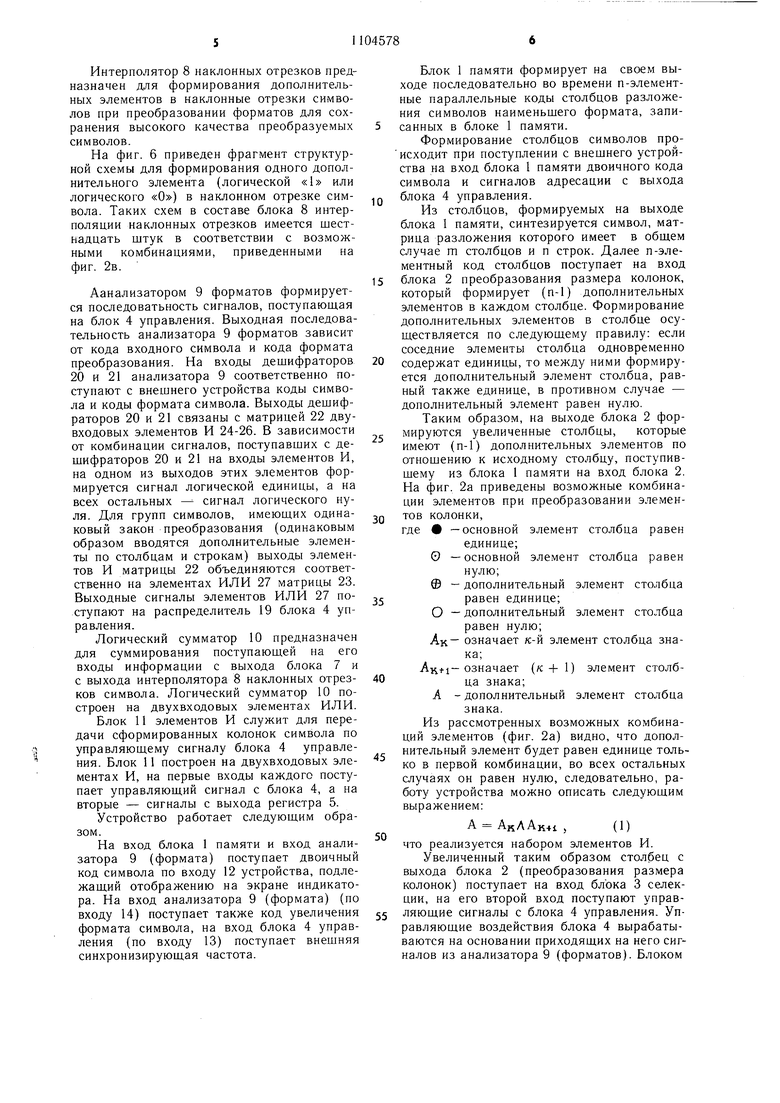

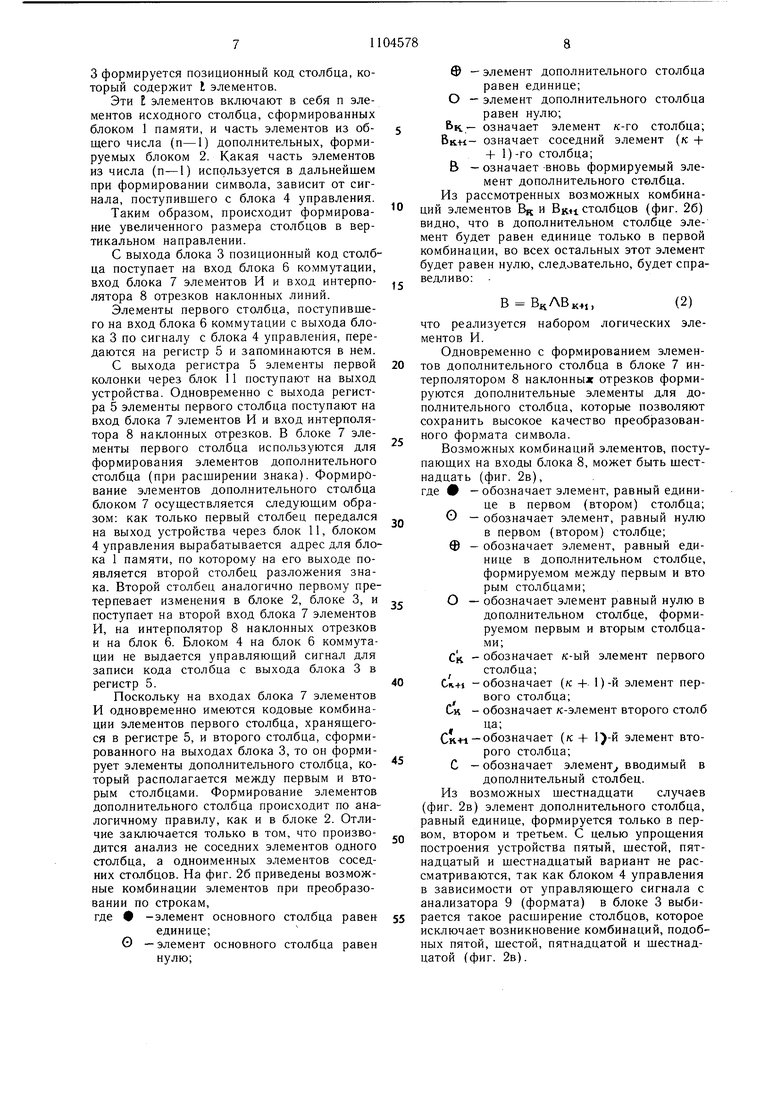

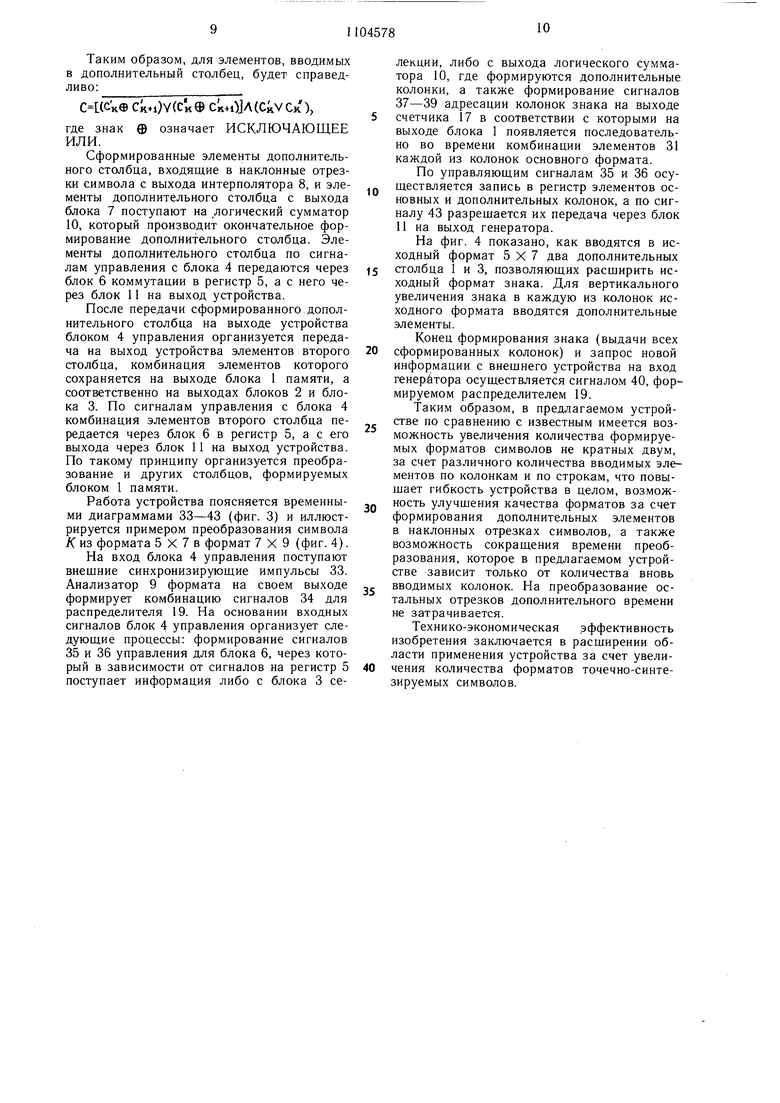

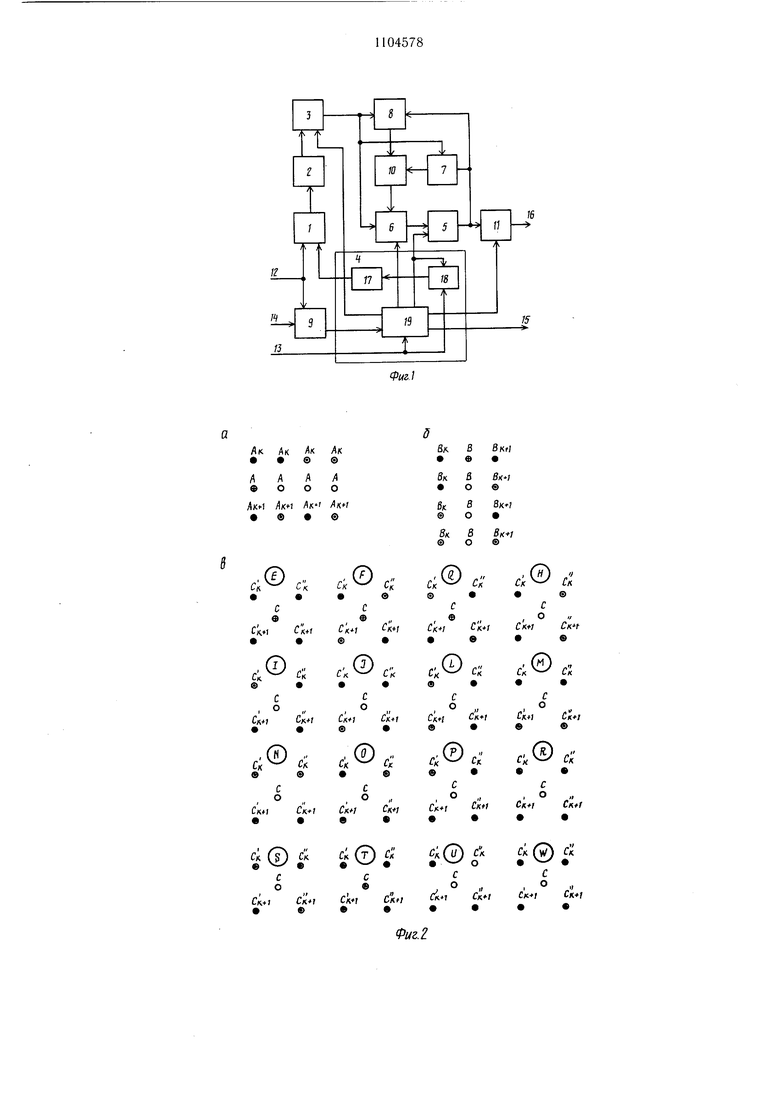

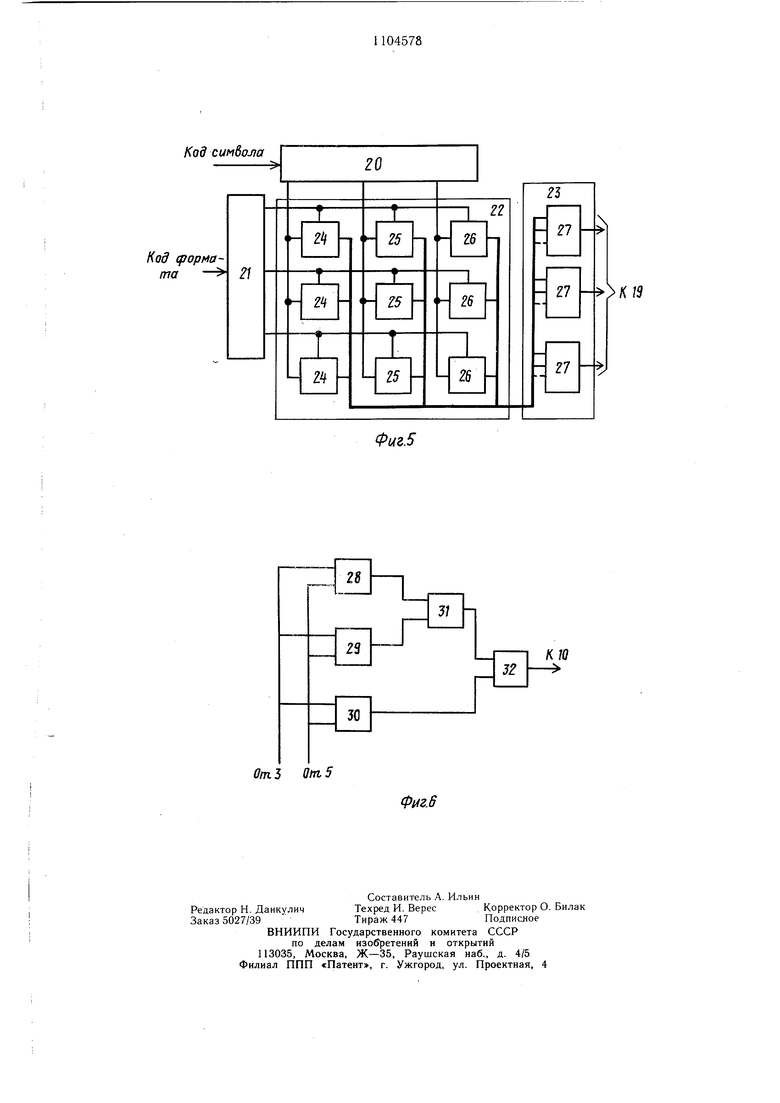

На фиг. 1 приведена структурная схема устройства; на фиг. 2а - возможные комбинации элементов при преобразовании колонки символа; на фиг. 26 - возможные комбинации элементов при преобразовании символа по строкам (при расширении); на фиг. 2в - возможные комбинации элементов при интерполяции наклонных отрезков; на фиг. 3 - временная диаграмма работы устройства; на фиг. 4 - преобразование символа формата 5x7 в формат 7x9; на фиг. 5 - структурная схема анализатора форматов; на фиг. 6 - фрагмент структурной схемы интерполятора наклонных отрезков.

Устройство содержит блок 1 памяти, первый блок 2 элементов И, блок 3 селекции, блок 4 управления, регистр 5, блок 6 коммутации, второй блок 7 элементов И, интерполятор 8 наклонньгх отрезков, анализатор 9 форматов знака, логический сумматор 10, третий блок 11 элементов И, первый 12, второй 13 и третий 14 входы устройства, первый 15 и второй 16 выходы устройства, блок 4 управления содержит счетчик 17 адресов, элемент И 18 и распределитель 19 импульсов.

Анализатор 9 форматов содержит дешифратор 20 кода символа, дешифратор 21 кода формата, матрицы 22 и 23 элементов И 24 - 26 и элементов ИЛИ 27 соответственно.

Интерполятор 8 наклонных отрезков содержит элементы ИСКЛЮЧАЮЩЕГО ИЛИ 28 и 29 элемент ИЛИ 30, элемент ИЛИ-НЕ 31 и элемент И 32 размера колонок. Управление блоком 1, блоком 3 осуществляется синхросигналами с блока 4 управления, на вход которого поступает стробируюший сигнал по входу 13 с внешнего устройства (не показан) и сигнал с выхода анализатора 9 форматов (знака), выход блока 3 связан со входами блока 6 коммутации, блока 7 и интерполятора 8 наклонных отрезков. Вторые входы блока 7 и интерполятора 8 наклонных отрезков связаны с выходом регистра 5, а выходы блока 7 и интерполятора 8 связаны

со входами логического сумматора 10. С выхода сумматора 10 сигналы подаются на второй вход блока 6 коммутации.

Блок 1 памяти предназначен для хране5 ния кодов разложения символов, служащих для отображения на экране матричного индикатора.

Блок 2 элементов И предназначен для увеличения размера колонки за счет ввеQ дения дополнительных элементов между основными элементами колонки. Построен блок 2 (для преобразования по колонкам) на логических двухвходовых элементах И. На первый вход элемента И поступает, например, первый, основной элемент (логичес5 кая «1 или логический «О) колонки, а на второй вход - второй элемент. На выходе элемента И формируется таким образом дополнительный элемент (логическая «1 или логический «О) между первым и вторым основными элементами колонки. Блок 3 селек0 ции предназначен для выделения из поступающей на его вход комбинации элементов колонки определенных элементов в зависимости от сигналов, поступающих на его вход с блока 4 управления.

5Блок 4 управления предназначен для

формирования последовательности управляющих сигналов, для управления блоками, входящими в состав устройства (для точечно-синтезируемых символов изменяемого формата). На вход распределителя 19 по0 ступает комбинация сигналов с выхода анализатора форматов и внешние синхронизирующие импульсы. На выходе распределителя 19 формируется последовательность сигналов, с помощью которых управляется работа узлов и блоков всего устройства. Для

5 формирования адреса блока 1 служит счетчик 17 адресов, на вход которого поступают управляющие сигналы с выхода элемента И 18. На один вход элемента И 18 поступает управляющий сигнал с выхода распределителя 19, а на второй - внешние синхроим пульсы по входу 13.

Блок 6 коммутации предназначен для переключения на вход регистра 5 информации либо с выхода блока 3 селекции, либо с выхода логического сумматора 10.

,Блок 7 элементов И предназначен для

расширения знаков. Построение этого блока аналогично построению блока 2. Построен блок 7 (для преобразования размера по строкам) на двухвходовых элементах И, на первый вход элемента поступает, напри0 мер, первый элемент (логическая «1 или логический «О) первой колонки символа, а на второй вход - первый элемент второй колонки символа. На выходе элемента И формируется таким образом первый элемент (логическая «1 или логический «О) до5 полнительной колонки, которая должна быть расположена между первой и второй колонками исходного формата символа, что позволяет увеличитвать символ по строкам.

Интерполятор 8 наклонных отрезков предназначен для формирования дополнительных элементов в наклонные отрезки символов при преобразовании форматов для сохранения высокого качества преобразуемых символов.

На фиг. 6 приведен фрагмент структурной схемы для формирования одного дополнительного элемента (логической «1 или логического «О) в наклонном отрезке символа. Таких схем в составе блока 8 интерполяции наклонных отрезков имеется шестнадцать штук в соответствии с возможными комбинациями, приведенными на фиг. 2в.

Аанализатором 9 форматов формируется последоватьпость сигналов, поступающая на блок 4 управления. Выходная последовательность анализатора 9 форматов зависит от кода входного символа и кода формата преобразования. На входы дешифраторов 20 и 21 анализатора 9 соответственно поступают с внешнего устройства коды символа и коды формата символа. Выходы дешифраторов 20 и 21 связаны с матрицей 22 двувходовых элементов И 24-26. В зависимости от комбинации сигналов, поступавших с дешифраторов 20 и 21 на входы элементов И, на одном из выходов этих элементов формируется сигнал логической единицы, а на всех остальных сигнал логического нуля. Для групп символов, имеющих одинаковый закон преобразования (одинаковым образом вводятся дополнительные элементы по столбцам и строкам) выходы элементов И матрицы 22 объединяются соответственно на элементах ИЛИ 27 матрицы 23. Выходные сигналы элементов ИЛИ 27 поступают на распределитель 19 блока 4 управления.

Логический сумматор 10 предназначен для суммирования поступающей на его входы информации с выхода блока 7 и с выхода интерполятора 8 наклонных отрезков символа. Логический сумматор 10 построен на двухвходовых элементах ИЛИ.

Блок 11 элементов И служит для передачи сформированных колонок символа по управляющему сигналу блока 4 управления. Блок 11 построен на двухвходовых элементах И, на первые входы каждого поступает управляющий сигнал с блока 4, а на вторые - сигналы с выхода регистра 5.

Устройство работает следующим образом.

На вход блока 1 памяти и вход анализатора 9 (формата) поступает двоичный код символа по входу 12 устройства, подлежащий отображению на экране индикатора. На вход анализатора 9 (формата) (по входу 14) поступает также код увеличения формата символа, на вход блока 4 управления (по входу 13) поступает внешняя синхронизирующая частота.

Блок 1 памяти формирует на своем выходе последовательно во времени п-элементные параллельные коды столбцов разложения символов наименьшего формата, запи5 санных в блоке 1 памяти.

Формирование столбцов символов про исходит при поступлении с внешнего устройства на вход блока 1 памяти двоичного кода символа и сигналов адресации с выхода Q блока 4 управления.

Из столбцов, формируемых на выходе блока 1 памяти, синтезируется символ, матрица разложения которого имеет в общем случае m столбцов и п строк. Далее п-элементный код столбцов поступает на вход 5 блока 2 преобразования размера колонок, который формирует (п-1) дополнительных элементов в каждом столбце. Формирование дополнительных элементов в столбце осуществляется по следующему правилу: если соседние элементы столбца одновременно 0 содержат единицы, то между ними формируется дополнительный элемент столбца, равный также единице, в противном случае - дополнительный элемент равен нулю.

Таким образом, на выходе блока 2 фор5 мируются увеличенные столбцы, которые имеют (п-1) дополнительных элементов по отношению к исходному столбцу, поступившему из блока 1 памяти на вход блока 2. На фиг. 2а приведены возможные комбинации элементов при преобразовании элеменQ тов колонки,

где -основной элемент столбца равен

единице; 0 -основной элемент столбца равен

нулю;

Ф - дополнительный элемент столбца равен единице;

О - дополнительный элемент столбца

равен нулю;

АК означает к-й элемент столбца знака;

A ti-означает (к + 1) элемент столбца знака; А -дополнительный элемент столбца

знака.

Из рассмотренных возможных комбинаций элементов (фиг. 2а) видно, что допол нительный элемент будет равен единице только в первой комбинации, во всех остальных случаях он равен нулю, следовательно, работу устройства можно описать следующим выражением:

А АкЛАк41,(1)

что реализуется набором элементов И.

Увеличенный таким образом столбец с выхода блока 2 (преобразования размера колонок) поступает на вход блока 3 селекции, на его второй вход поступают управ5 ляющие сигналы с блока 4 управления. Управляющие воздействия блока 4 вырабатываются на основании приходящих на него сигналов из анализатора 9 (форматов). Блоком

3формируется позиционный код столбца, который содержит I элементов.

Эти элементов включают в себя п элементов исходного столбца, сформированных блоком 1 памяти, и часть элементов из общего числа (п-1) дополнительных, формируемых блоком 2. Какая часть элементов из числа (п-1) используется в дальнейшем при формировании символа, зависит от сигнала, поступившего с блока 4 управления.

Таким образом, происходит формирование увеличенного размера столбцов в вертикальном направлении.

С выхода блока 3 позиционный код столбца поступает на вход блока 6 коммутации, вход блока 7 элементов И и вход интерполятора 8 отрезков наклонных линий.

Элементы первого столбца, поступившего на вход блока 6 коммутации с выхода блока 3 по сигналу с блока 4 управления, передаются на регистр 5 и запоминаются в нем.

С выхода регистра 5 элементы первой колонки через блок 11 поступают на выход устройства. Одновременно с выхода регистра 5 элементы первого столбца поступают на вход блока 7 элементов И и вход интерполятора 8 наклонных отрезков. В блоке 7 элементы первого столбца используются для формирования элементов дополнительного столбца (при расширении знака). Формирование элементов дополнительного столбца блоком 7 осушествляется следующим образом: как только первый столбец передался на выход устройства через блок 11, блоком

4управления вырабатывается адрес для блока 1 памяти, по которому на его выходе появляется второй столбец разложения знака. Второй столбец аналогично первому претерпевает изменения в блоке 2, блоке 3, и поступает на второй вход блока 7 элементов

И, на интерполятор 8 наклонных отрезков и на блок 6. Блоком 4 на блок 6 коммутации не выдается управляющий сигнал для записи кода столбца с выхода блока 3 в регистр 5.

Поскольку на входах блока 7 элементов И одновременно имеются кодовые комбинации элементов первого столбца, хранящегося в регистре 5, и второго столбца, сформированного на выходах блока 3, то он формирует элементы дополнительного столбца, который располагается между первым и вторым столбцами. Формирование элементов дополнительного столбца происходит по аналогичному правилу, как и в блоке 2. Отличие заключается только в том, что производится анализ не соседних элементов одного столбца, а одноименных элементов соседних столбцов. На фиг. 26 приведены возможные комбинации элементов при преобразовании по строкам, где -элемент основного столбца равек

единице; О -элемент основного столбца равен

нулю;

Ф -элемент дополнительного столбца

равен единице; О - элемент дополнительного столбца

равен нулю;

БК..- означает элемент /с-го столбца; Вк«- означает соседний элемент (к +

+ 1) -го столбца;

В - означает -вновь формируемый элемент дополнительного столбца. Из рассмотренных возможных комбинаций элементов BR и BK«I столбцов (фиг. 26) видно, что в дополнительном столбце элемент будет равен единице только в первой комбинации, во всех остальных этот элемент будет равен нулю, следовательно, будет справедливо: .

В В«ЛВкп,(2)

что реализуется набором логических элементов И.

Одновременно с формированием элементов дополнительного столбца в блоке 7 интерполятором 8 наклонных отрезков формируются дополнительные элементы для дополнительного столбца, которые позволяют сохранить высокое качество преобразованного формата символа.

Возможных комбинаций элементов, поступающих на входы блока 8, может быть шестнадцать (фиг. 2в),

где - обозначает элемент, равный единице в первом (втором) столбца; О - обозначает элемент, равный нулю

в первом (втором) столбце; Ф - обозначает элемент, равный единице в дополнительном столбце, формируемом между первым и вто рым столбцами;

О - обозначает элемент равный нулю в дополнительном столбце, формируемом первым и вторым столбцами;

Ск - обозначает /с-ый элемент первого столбца;

CR..H -обозначает (к + 1)-й элемент первого столбца;

С-к - обозначает /с-элемент второго столб , ца;

Ск-и -обозначает (к + элемент второго столбца; С - обозначает элемент вводимый в

дополнительный столбец. Из возможных щестнадцати случаев (фиг. 2в) элемент дополнительного столбца, равный единице, формируется только в первом, втором и третьем. С целью упрощения построения устройства пятый, шестой, пятнадцатый и шестнадцатый вариант не рассматриваются, так как блоком 4 управления в зависимости от управляющего сигнала с анализатора 9 (формата) в блоке 3 выбирается такое расширение столбцов, которое исключает возникновение комбинаций, подобных пятой, шестой, пятнадцатой и шестнадцатой (фиг. 2в).

Таким образом, для элементов, вводимых в дополнительный столбец, будет справедливо:

(СкФ Ck+i)Y(CK® (CkV Ск ),

где знак ф означает ИСКЛЮЧАЮЩЕЕ ИЛИ.

Сформированные элементы дополнительного столбца, входящие в наклонные отрезки символа с выхода интерполятора 8, и элементы дополнительного столбца с выхода блока 7 поступают на логический сумматор 10, который производит окончательное формирование дополнительного столбца. Элементы дополнительного столбца по сигналам управления с блока 4 передаются через блок б коммутации в регистр 5, а с него через блок 11 на выход устройства.

После передачи сформированного дополнительного столбца на выходе устройства блоком 4 управления организуется передача на выход устройства элементов второго столбца, комбинация элементов которого сохраняется на выходе блока 1 памяти, а соответственно на выходах блоков 2 и блока 3. По сигналам управления с блока 4 комбинация элементов второго столбца передается через блок 6 в регистр 5, а с его выхода через блок 11 на выход устройства. По такому принципу организуется преобразование и других столбцов, формируемых блоком 1 памяти.

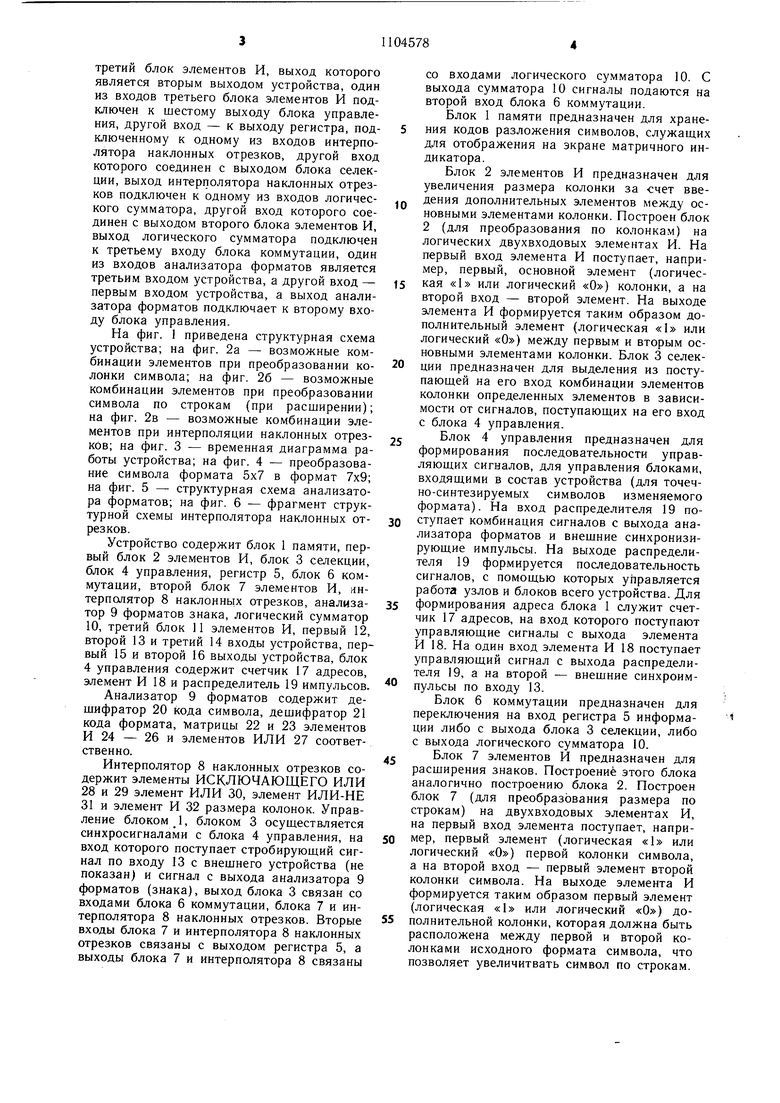

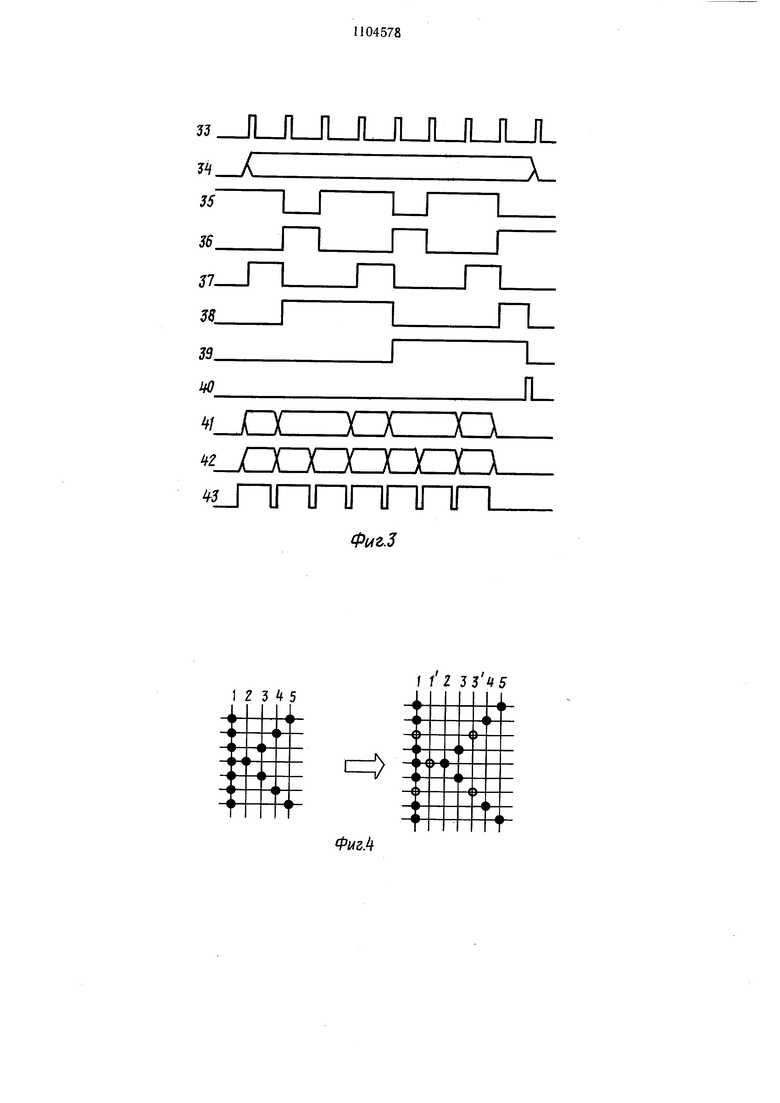

Работа устройства поясняется временными диаграммами 33-43 (фиг. 3) и иллюстрируется примером преобразования символа /С из формата 5 X 7 в формат 7x9 (фиг. 4).

На вход блока 4 управления поступают внешние синхронизирующие импульсы 33. Анализатор 9 формата на своем выходе формирует комбинацию сигналов 34 для распределителя 19. На основании входных сигналов блок 4 управления организует следующие процессы: формирование сигналов 35 и 36 управления для блока 6, через который в зависимости от сигналов на регистр 5 поступает информация либо с блока 3 селекции, либо с выхода логического сумматора 10, где формируются дополнительные колонки, а также формирование сигналов 37-39 адресации колонок знака на выходе 5 счетчика 17 в соответствии с которы.ми на выходе блока 1 появляется последовательно во времени комбинации элементов 31 каждой из колонок основного формата. По управляющим сигналам 35 и 36 осу- ществляется запись в регистр элементов основных и дополнительных колонок, а по сигналу 43 разрешается их передача через блок 11 на выход генератора.

На фиг. 4 показано, как вводятся в исходный формат 5X7 два дополнительных

5 столбца 1 и 3, позволяющих расширить исходный формат знака. Для вертикального увеличения знака в каждую из колонок исходного формата вводятся дополнительные элементы.

Конец формирования знака (выдачи всех

0 сформированных колонок) и запрос новой информации с внешнего устройства на вход генерйтора осуществляется сигналом 40, формируемом распределителем 19.

Таким образом, в предлагаемом устройстве по сравнению с известным имеется возможность увеличения количества формируемых форматов символов не кратных двум, за счет различного количества вводимых элементов по колонкам и по строкам, что повышает гибкость устройства в целом, возмож- ность улучшения качества форматов за счет формирования дополнительных элементов в наклонных отрезках символов, а также возможность сокращения времени преобразования, которое в предлагаемом устройстве зависит только от количества вновь

вводимых колонок. На преобразование остальных отрезков дополнительного времени не затрачивается.

Технико-экономическая эффективность изобретения заключается в расширении области применения устройства за счет увели0 чения количества форматов точечно-синтезируемых символов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Линейный интерполятор | 1985 |

|

SU1298714A1 |

| СПОСОБ КОМПЛЕКСНОЙ ЗАЩИТЫ РАСПРЕДЕЛЕННОЙ ОБРАБОТКИ ИНФОРМАЦИИ В КОМПЬЮТЕРНЫХ СИСТЕМАХ И СИСТЕМА ДЛЯ ОСУЩЕСТВЛЕНИЯ СПОСОБА | 2001 |

|

RU2259639C2 |

| УСТРОЙСТВО ДЛЯ ПАРАЛЛЕЛЬНОЙ ОБРАБОТКИ ДАННЫХ | 1991 |

|

RU2028664C1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1982 |

|

SU1084864A1 |

| Устройство для двухкоординатного управления рабочим органом | 1990 |

|

SU1815620A1 |

| Устройство для отображения информации на газоразрядной индикаторной панели | 1983 |

|

SU1119065A1 |

| Устройство для отображения информации | 1985 |

|

SU1265835A1 |

| Устройство для поиска информации на перфокартах | 1974 |

|

SU555398A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Устройство для формирования символов | 1980 |

|

SU934540A1 |

УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СИМВОЛОВ, содержащее последовательно соединенные блок памяти, первый блок элементов И и блок селекции, другой вход которого подключен к первому выходу блока управления, второй выход которого соединен с первым входом блока коммутации, выход которого соединен с одним из входов регистра, другой вход которого соединен с третьим выходом блока управления, четвертый выход которого соединен с одним из входов блока памяти, другой вход которого является первым входом устройства, вторым входом которого является первый вход блока управления, пятый выход которого является первым выходом устройства, выход блока селекции подключен к второму входу блока коммутации и к одному из входов второго блока элементов И, другой вход которого соединен с выходом регистра, отличающееся тем, что, с целью расширения области применения устройства за счет увеличения количества форматов точечно синтезируемых символов, оно содержит интерполятор наклонных отрезков, анализатор форматов, логический сумматор и третий блок элементов И, выход которого является вторым выходом устройства, один из входов третьего блока элементов И подключен к шестому выходу блока управления, другой вход - к выходу регистра, подключенному к одному из входов интерполятора наклонных отрезков, другой вход которого соединен с выходом блока селекции, выход (Л интерполятора наклонных отрезков подключен к одному из входов логического сумматора, другой вход которого соединен с выходом второго блока элементов И, выход логического сумматора подключен к третьему входу блока коммутации, один из входов анализатора форматов является третьим входом устройства, а другой вход - первым входом устройства, а выход анализатора 4 форматов подключен к второму входу блосл ка управления. 00

ЛкЛкЛкАк

®®

/1АЛ/4

ФОоО

Ак«-1 KtiЛх f

®®

, () „

С

, ® „

С 1fxtf

.

о

Сс

., о „, о

)

®®

, СО - (f) л

сх ск

®®

сс

о„, о „

9

c; (0 f-i

« -

с

®

Cj(«fCxf/

ВSKf

®

Вfl.;

О®

о

8BK- t

О®

с. С-;

с.

с:

С О

Сх+;

е

е

.;

а

с о

е

C/i

л

.Q

C о

с о

Сл:-/

JLJLJLJLJLJLJLJLJL

33

Фиг.З

/ f2

Фиг.5

Авторы

Даты

1984-07-23—Публикация

1983-03-01—Подача