Изобретение относится к области автоматики и вычислительной техники, в частности к устройствам управления станками с программным управлением, машинами термической резки металла,

Цель изобретения - устранение указанного недостатка.

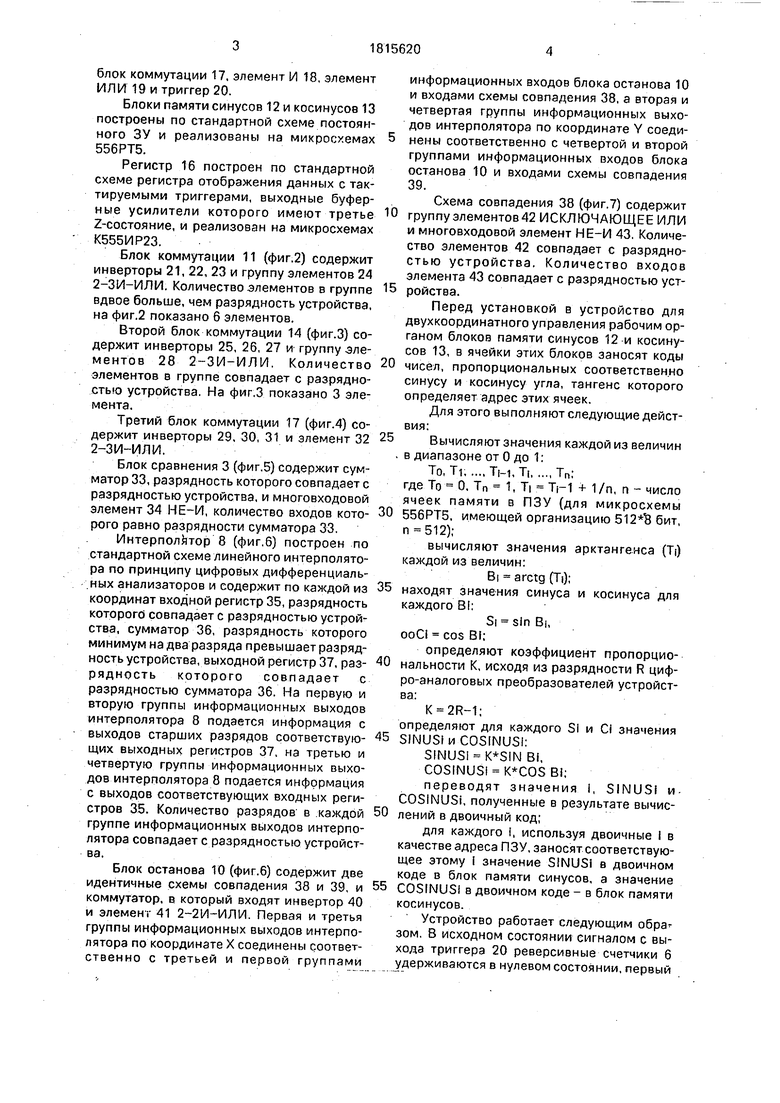

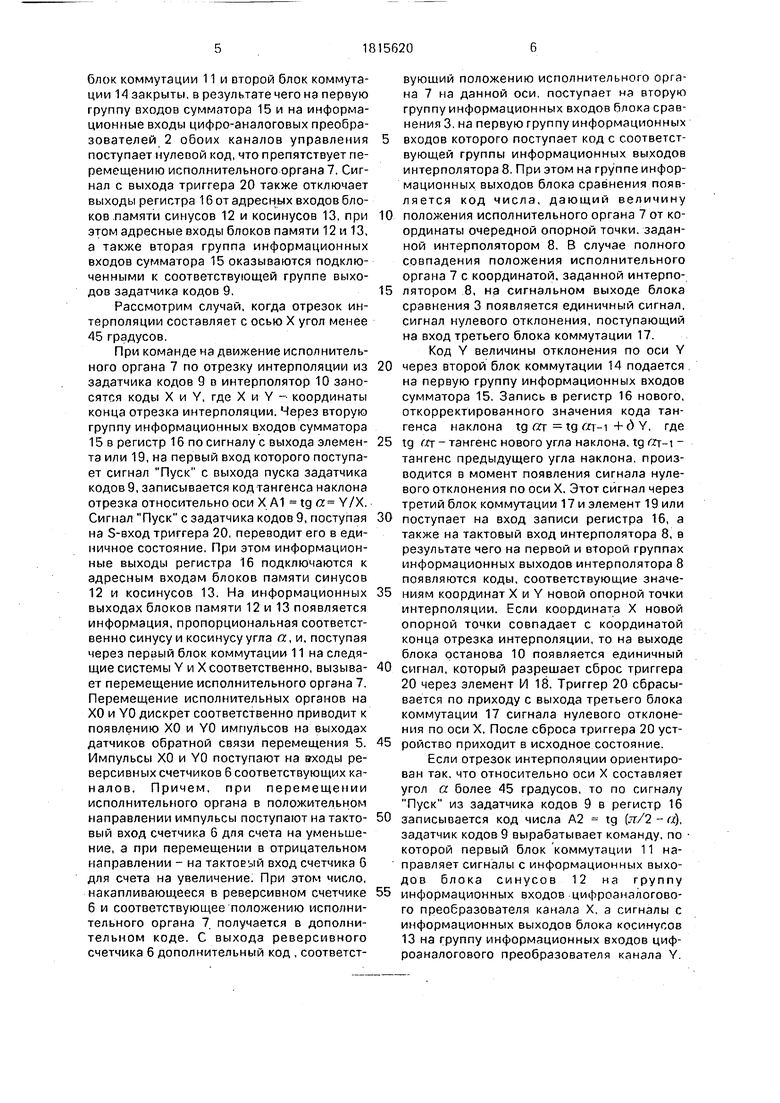

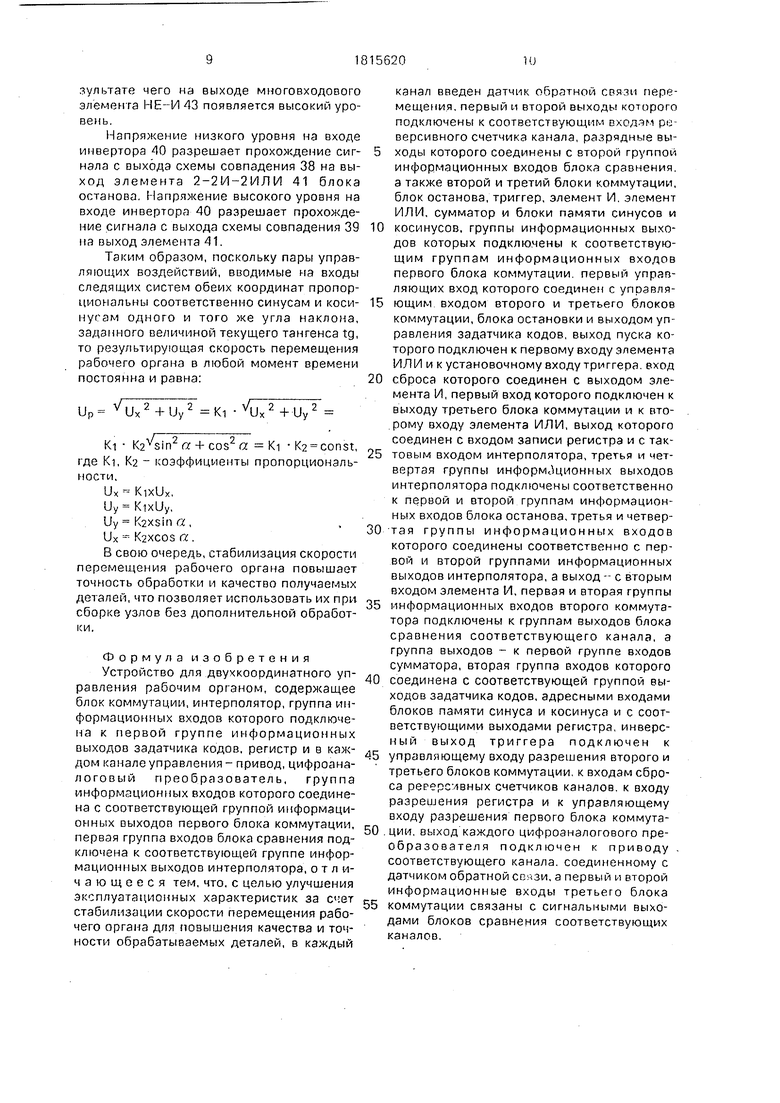

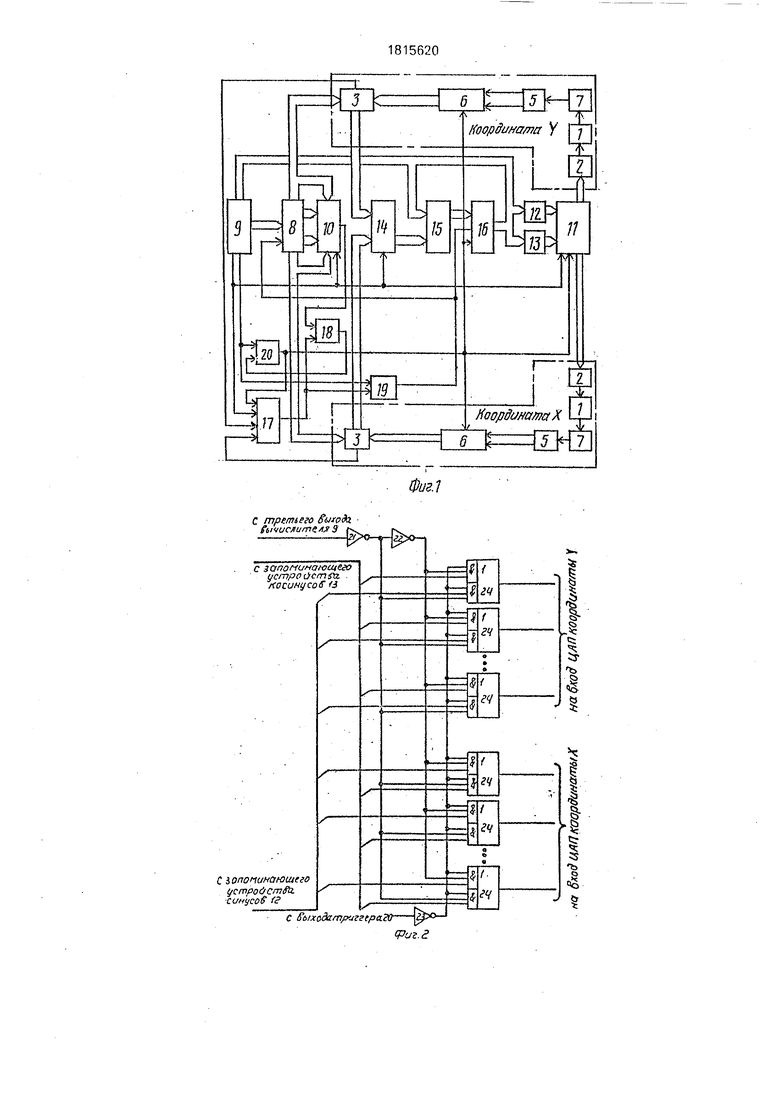

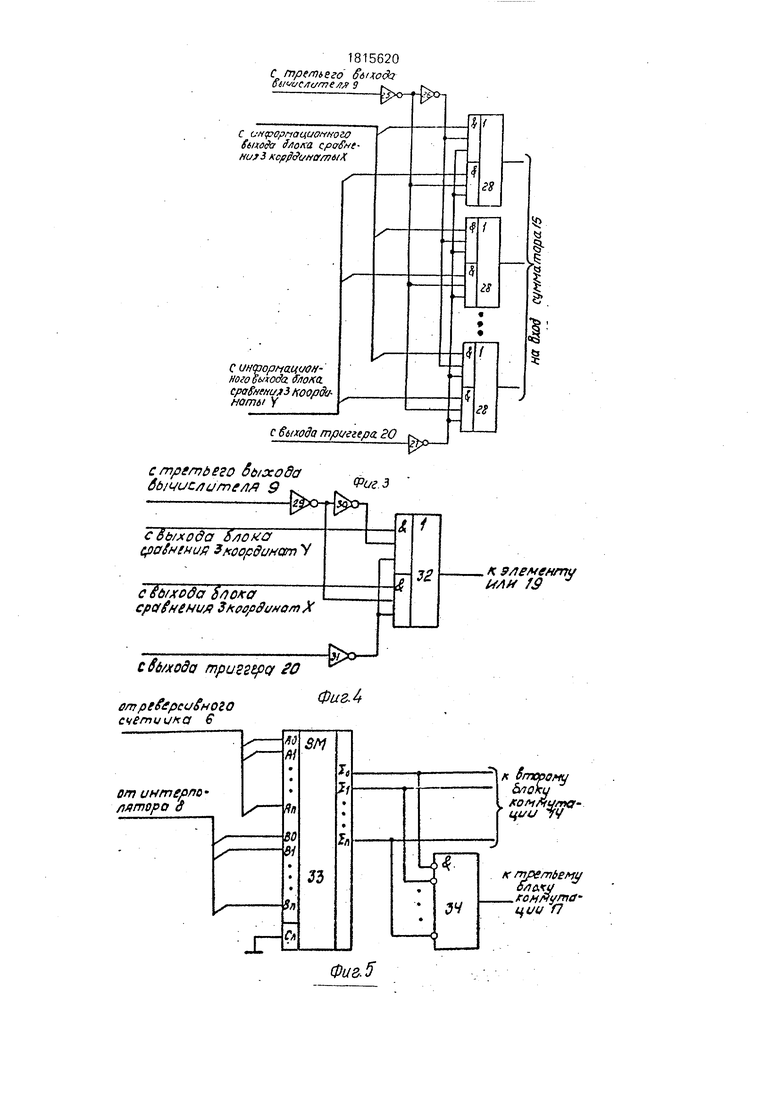

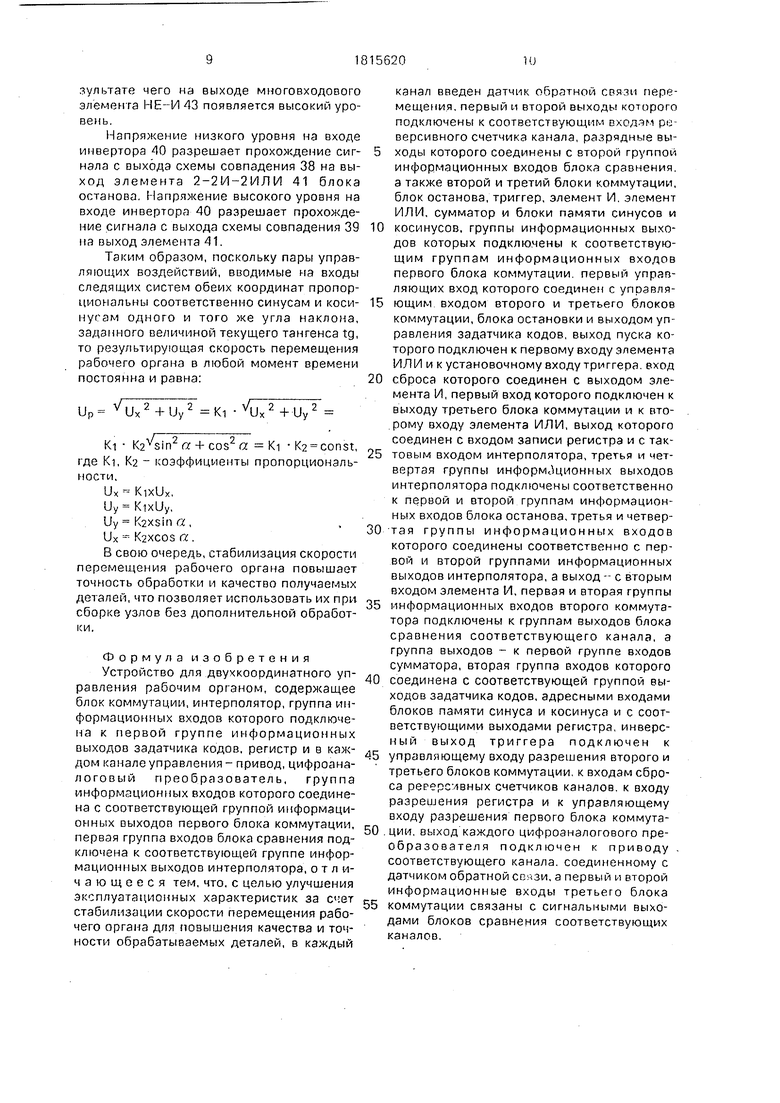

На фиг.1 представлена структурная схема устройства; на фиг.2 - функциональная схема первого блока коммутации; на фиг.З - функциональная схема второго блока коммутации; на фиг.4 - функциональная схема третьего блока коммутации: на фиг.5 - функциональная схема блока сравнения; на

фиг.6 - структурная схема интерполятора с блоком останова; на фиг.7 - функциональная схема схемы совпадения.

Устройство (фиг.1) содержит в каждом из каналов X и Y привод 1, цифроаналого- вый преобразователь 2, блок сравнения 3, цепь обратной связи 4, включающую датчик обратной связи перемещения 5 и реверсив- , ный счетчик б, исполнительный орган 7. В устройство входят также интерполятор 8, задатчик кодов 9, блок останова 10, блок коммутации 11, блок памяти синусов 12, блок памяти косинусов 13, второй блок коммутации 14, сумматор 15, регистр 16, третий

ел о к о

блок коммутации 17, элемент И 18, элемент ИЛИ 19 и триггер 20.

Блоки памяти синусов 12 и косинусов 13 построены по стандартной схеме постоянного ЗУ и реализованы на микросхемах 556РТ5.

Регистр 16 построен по стандартной схеме регистра отображения данных с тактируемыми триггерами, выходные буферные усилители которого имеют третье Z-состояние, и реализован на микросхемах К555ИР23.

Блок коммутации 11 (фиг.2) содержит инверторы 21, 22, 23 и группу элементов 24 2-ЗИ-ИЛИ. Количество элементов в группе вдвое больше, чем разрядность устройства, на фиг.2 показано 6 элементов.

Второй блок коммутации 14 (фиг.З) содержит инверторы 25, 26, 27 и группу элементов 28 2-ЗИ-ИЛИ. Количество элементов в группе совпадает с разрядностью устройства. На фиг.З показано 3 элемента.

Третий блок коммутации 17 (фиг.4) содержит инверторы 29, 30, 31 и элемент 32 2-ЗИ-ИЛИ.

Блок сравнения 3 (фиг.5) содержит сумматор 33,разрядность которого совпадает с разрядностью устройства, и многовходовой элемент 34 НЕ-И, количество входов которого равно разрядности сумматора 33.

Интерполятор 8 (фиг.6) построен по стандартной схеме линейного интерполято- ра по принципу цифровых дифференциаль- .ных анализаторов и содержит по каждой из координат входной регистр 35, разрядность которого совпадает с разрядностью устройства, сумматор 36, разрядность которого минимум на два разряда превышает разрядность устройства, выходной регистр 37, разрядность которого совпадает с разрядностью сумматора 36. На первую и вторую группы информационных выходов интерполятора 8 подается информация с выходов старших разрядов соответствующих выходных регистров 37, на третью и четвертую группы информационных выходов интерполятора 8 подается информация с выходов соответствующих входных регистров 35. Количество разрядов в .каждой группе информационных выходов интерполятора совпадает с разрядностью устройства.

Блок останова 10 (фиг.6) содержит две идентичные схемы совпадения 38 и 39, и коммутатор, в который входят инвертор 40 и элемент 41 2-2И-ИЛИ. Первая и третья группы информационных выходов интерполятора по координате X соединены соответственно с третьей и первой группами

информационных входов блока останова 10 и входами схемы совпадения 38, а вторая и четвертая группы информационных выходов интерполятора по координате Y соеди- неиы соответственно с четвертой и второй группами информационных входов блока останова 10 и входами схемы совпадения 39.

Схема совпадения 38 (фиг.7) содержит группу элементов 42 ИСКЛЮЧАЮЩЕЕ ИЛИ и многовходовой элемент НЕ-И 43. Количество элементов 42 совпадает с разрядностью устройства. Количество входов элемента 43 совпадает с разрядностью уст- 5 ройства.

Перед установкой в устройство для двухкоординатного управления рабочим органом блоков памяти синусов 12 и косинусов 13, в ячейки этих блоков заносят коды 0 чисел, пропорциональных соответственно синусу и косинусу угла, тангенс которого определяет адрес этих ячеек.

Для этого выполняют следующие действия:

5 Вычисляют значения каждой из величин . в диапазоне от 0 до 1:

То, TL .... Ti-i.Ti, ..., Tn; где То - 0. Tn 1, TI Tr1 + 1/n, n - число ячеек памяти в ПЗУ (для микросхемы 0 556РТ5, имеющей организацию бит, п 512);

вычисляют значения арктангенса (Tj) каждой из величин:

Bi arctg (Ti);

5 находят значения синуса и косинуса для каждого Bi:

Si sin Bi, ooCi cos Bi;

определяют коэффициент пропорцио- 0 нальности К, исходя из разрядности R цифро-аналоговых преобразователей устройства:

K 2R-1;

определяют для каждого Si и Ci значения 5 SINUSinCOSINUSI:

SINUSi Bi, COSINUSi K COSBi; переводят значения i, SINUSi и COSINUSi, полученные в результате вычис- 0 лений в двоичный код;

для каждого I, используя двоичные I в качестве адреса ПЗУ, заносят соответствующее этому i значение SINUSi в двоичном коде в блок памяти синусов, а значение 5 COSINUSI в двоичном коде - в блок памяти косинусов.

Устройство работает следующим обра зом. В исходном состоянии сигналом с выхода триггера 20 реверсивные счетчики б удерживаются в нулевом состоянии, первый

блок коммутации 11 и второй блок коммутации 14 закрыты, в результате чего на первую группу входов сумматора 15 и на информационные входы цифро-аналоговых преобразователей 2 обоих каналов управления поступает нулевой код, что препятствует перемещению исполнительного органа 7. Сигнал с выхода триггера 20 также отключает выходы регистра 16 от адресных входов блоков .памяти синусов 12 и косинусов 13, при этом адресные входы блоков памяти 12 и 13, а также вторая группа информационных входов сумматора 15 оказываются подключенными к соответствующей группе выходов задатчика кодов 9.

Рассмотрим случай, когда отрезок интерполяции составляет с осью X угол менее 45 градусов.

При команде на движение исполнительного органа 7 по отрезку интерполяции из задатчика кодов 9 в интерполятор 10 заносятся коды X и Y, где X и Y - координаты конца отрезка интерполяции. Через вторую группу информационных входов сумматора 15 в регистр 16 по сигналу с выхода элемента или 19, на первый вход которого поступает сигнал Пуск с выхода пуска задатчика кодов 9, записывается код тангенса наклона отрезка относительно оси X А1 tg а Y/X. Сигнал Пуск с задатчика кодов 9, поступая на S-вход триггера 20, переводит его в единичное состояние. При этом информационные выходы регистра 16 подключаются к адресным входам блоков памяти синусов 12 и косинусов 13. На информационных выходах блоков памяти 12 и 13 появляется информация, пропорциональная соответственно синусу и косинусу угла а, и, поступая через первый блок коммутации 11 на следящие системы Y и X соответственно, вызывает перемещение исполнительного органа 7. Перемещение исполнительных органов на ХО и YO дискрет соответственно приводит к появлению ХО и YO импульсов на выходах датчиков обратной связи перемещения 5. Импульсы ХО и YO поступают на входы реверсивных счетчиков 6 соответствующих ка- налов. Причем, при перемещении исполнительного органа в положительном направлении импульсы поступают на тактовый вход счетчика 6 для счета на уменьшение, а при перемещении в отрицательном направлении - на тактовый вход счетчика 6 для счета на увеличение. При этом число, накапливающееся в реверсивном счетчике 6 и соответствующее положению исполнительного органа 7 получается в дополнительном коде. С выхода реверсивного счетчика 6 дополнительный код , соответствующий положению исполнительного органа 7 на данной оси. поступает на вторую группу информационных входов блока сравнения 3.на первую группу информационных 5 входов которого поступает код с соответствующей группы информационных выходов интерполятора 8. При этом на группе информационных выходов блока сравнения появляется код числа, дающий величину

0 положения исполнительного органа 7 от координаты очередной опорной точки, заданной интерполятором 8. В случае полного совпадения положения исполнительного органа 7 с координатой, заданной интерпо5 лятором 8, на сигнальном выходе блока сравнения 3 появляется единичный сигнал, сигнал нулевого отклонения, поступающий на вход третьего блока коммутации 17.

Код Y величины отклонения по оси Y

0 через второй блок коммутации 14 подается . на первую группу информационных входов сумматора 15. Запись в регистр 16 нового, откорректированного значения кода тангенса наклона tg от tg «т-i +д Y, где

5 tg «т-тангенс нового угла наклона, tg щ- - тангенс предыдущего угла наклона, производится в момент появления сигнала нулевого отклонения по оси X. Этот сигнал через третий блок коммутации 17 и элемент 19 или

0 поступает на вход записи регистра 16, а также на тактовый вход интерполятора 8, в результате чего на первой и второй группах информационных выходов интерполятора 8 появляются коды, соответствующие значе5 ниям координат X и Y новой опорной точки интерполяции. Если координата X новой опорной точки совпадает с координатой конца отрезка интерполяции, то на выходе блока останова 10 появляется единичный

0 сигнал, который разрешает сброс триггера 20 через элемент И 18. Триггер 20 сбрасывается по приходу с выхода третьего блока коммутации 17 сигнала нулевого отклонения по оси X. После сброса триггера 20 уст5 ройство приходит в исходное состояние.

Если отрезок интерполяции ориентирован так. что относительно оси X составляет угол а более 45 градусов, то по сигналу Пуск из задатчика кодов 9 в регистр 16

0 записывается код числа А2 tg (я/2-«), задатчик кодов 9 вырабатывает команду, по которой первый блок коммутации 11 направляет сигналы с информационных выходов блока синусов 12 на группу

5 информационных входов цифроаналогово- го преобразователя канала X. а сигналы с информационных выходов блока косинусов 13 на группу информационных входов циф- роаналогового преобразователя канала Y.

По этой же команде второй блок коммутации 14 подключает к первой группе информационных входов сумматора 15 группу информационных выходов блока сравнения 3 канала X, а третий блок коммутации 17 пропускает на вход записи в регистр 16 сигнал нулевого отклонения от блока сравнения 3 канала Y. В остальном работа устройства не отличается от описанного случая для угла менее 45 градусов.

Первый блок коммутации 11 (фиг.2) работает следующим образом. Если на вход инвертора 23 подано напряжение высокого уровня, то элементы 24 закрыты и на их выходах, а значит на информационных выходах блока коммутации 11 присутствует напряжение низкого уровня независимо от состояния остальных входов. Напряжение низкого уровня на входах инверторов 23 и 24 разрешает прохождение данных от группы информационных выходов блока памяти синусов 12 на выходы элементов 24, соединенные с группой информационных входов цифроаналогового преобразователя канала Y, а данные от группы информационных выходов блока памяти косинусов 13 на выходы элементов 24, соединенные с группой информационных входов цифроаналогового преобразователя канала X. Напряжение низкого уровня на входе инвертора 23 и высокого уровня на входе инвертора 24 разрешает прохождение данных от группы информационных выходов блока памяти синусов 12 на выходы элементов 24, соединенные с группой информационных входов цифроаналогового преобразователя канала X, а данные от группы информационных выходов блока памяти косинусов 13 на выходы элементов 24, соединенные с группой информационных входов цифрозналогового преобразователя канала Y.

Второй блок коммутации 14 (фиг.З) работает следующим образом. Если на вход инвертора 27 подано напряжение высокого уровня, то элементы 28 закрыты и на их выходах присутствует напряжение низкого уровня независимо от состояния остальных входов. Напряжение низкого уровня на входах инверторов 27 и 25 разрешает прохождение данных от информационных выходов блока сравнения 3 канала Y на выходы элементов 28, т.е. первая группа информационных входов второго блока коммутации оказывается подключенной к его группе информационных выходов. Напряжение низкого уровня на входе инвертора 27 и высокого уровня на входе инвертора 25 разрешает прохождение данных от информационных выходов блока сравнения 3 канала X на выходы элементов 28, т.е. вторая группа информационных входов второго блока коммутации оказывается подключенной к его группе информационных выходов.

Третий блок коммутации 17(фиг.4) работает следующим образом. Если на вход инвертора 31 подано напряжение высокого уровня, то элемент 32 закрыт и на его выходе присутствует напряжение низкого уровня независимо от состояния остальных

0 входов. Напряжение низкого уровня на входах инверторов 31 и 29 разрешает прохождение сигнала от сигнального выхода блока сравнения 3 канала X на выход элемента 32. Напряжение низкого уровня на входе ин5 вертора 31 и высокого уровня на входе инвертора 29 разрешает прохождение сигнала от сигнального выхода блока сравнения 3 канала Y на выход элемента 32.

Блок сравнения 3 (фиг.5) работает сле0 дующим образом. На вход переноса сумматора 33 всегда подается напряжение низкого уровня. На вторую группу информационных входов АО, А1. ..., AN сумматора с группы выходов реверсивного счетчика 6

5 поступают данные в дополнительном коде . об истинном положении исполнительного органа 7. На первую группу информационных входов ВО, В1, ..., BN сумматора б с соответствующей группы информационных

0 выходов интерполятора 8 подается координата очередной опорной точки в прямом коде. На выходе сумматора появляется код, соответствующий разности заданной ин- терполятором 8 координаты и истинной ко5 ординаты исполнительного органа 7, который поступает на информационные выходы блока сравнения 3 и на входы элемента 34. При совпадении заданной и истинной координат на всех выходах сумматора 33

0 появляется напряжение низкого уровня и на выходе элемента 34 вырабатывается сигнал высокого уровня, который свидетельствует о нулевом отклонении истинной координаты от заданной и подается на сигнальный

5 выход блока сравнения 3.

По приходу импульса с выхода элемента или 19 на тактовый вход мнтерполятора 8 (фиг.6) на выходах его выходных регистров 37 появляются коды, соответствующие ко0 ординатам очередной опорной точки интер- поляции. Во входных регистрах 35 интерполятора 8 хранятся коды, соответствующие координатам конца отрезка интерполяции,

5При совпадении кодов на выходах регистров 35 и 37, которые соответствующим образом попарно подключены к схемам совпадения 38 и 39 (фиг.7), на выходах всех элементов 42 ИСКЛЮЧАЮЩЕЕ ИЛИ появляется напряжение низкого уровня, в результате чего на выходе многовходового элемента НЕ-И 43 появляется высокий уровень.

Напряжение низкого уровня на входе инвертора 40 разрешает прохождение сигнала с выхода схемы совпадения 38 на выход элемента 2-2И-2ИЛИ 41 блока останова. Напряжение высокого уровня на входе инвертора 40 разрешает прохождение сигнала с выхода схемы совпадения 39 на выход элемента 41.

Таким образом, поскольку пары управляющих воздействий, вводимые на входы следящих систем обеих координат пропорциональны соответственно синусам и коси- нугам одного и того же угла наклона, заданного величиной текущего тангенса tg, то результирующая скорость перемещения рабочего органа в любой момент времени постоянна и равна:

Up V Ux 2 + Uy 2 Ki VUX2 + Uy2

Ki a -f cos2 a - Ki K2 const, где Ki, K 2 - коэффициенты пропорциональности.

Ux KixUx,

Uy KixUy,

Uy K2XSina,

Ux K2xcos a.

В свою очередь, стабилизация скорости перемещения рабочего органа повышает точность обработки и качество получаемых деталей, что позволяет использовать их при сборке узлов без дополнительной обработки.

Формула изобретения Устройство для двухкоординатного управления рабочим органом, содержащее блок коммутации, интерполятор, группа информационных входов которого подключена к первой группе информационных выходов задатчика кодов, регистр и в каждом канале управления- привод, цифроана- логовый преобразователь, группа информационных входов которого соединена с соответствующей группой информационных выходов первого блока коммутации, первая группа входов блока сравнения подключена к соответствующей группе информационных выходов интерполятора, отличающееся тем, что. с целью улучшения эксплуатационных характеристик за счет стабилизации скорости перемещения рабочего органа для повышения качества и точности обрабатываемых деталей, в каждый

канал введен датчик обратной связи перемещения, первый и второй выходы которого подключены к соответствующим входам реверсивного счетчика канала, разрядные вы- 5 ходы которого соединены с второй группой информационных входов блока сравнения. а также второй и третий блоки коммутации, блок останова, триггер, элемент И. элемент ИЛИ, сумматор и блоки памяти синусов и

0 косинусов, группы информационных выходов которых подключены к соответствующим группам информационных входов первого блока коммутации, первый управляющих вход которого соединен с управля5 ющим входом второго и третьего блоков коммутации, блока остановки и выходом управления задатчика кодов, выход пуска которого подключен к первому входу элемента ИЛИ и к установочному входу триггера, вход

0 сброса которого соединен с выходом элемента И, первый вход которого подключен к выходу третьего блока коммутации и к второму входу элемента ИЛИ, выход которого соединен с входом записи регистра и с так5 товым входом интерполятора, третья и четвертая группы информационных выходов интерполятора подключены соответственно к первой и второй группам информационных входов блока останова, третья и четвер0 тая группы информационных входов которого соединены соответственно с первой и второй группами информационных выходов интерполятора, а выход- с вторым входом элемента И, первая и вторая группы

5 информационных входов второго коммутатора подключены к группам выходов блока сравнения соответствующего канала, а группа выходов - к первой группе входов сумматора, вторая группа входов которого

0 соединена с соответствующей группой выходов задатчика кодов, адресными входами блоков памяти синуса и косинуса и с соответствующими выходами регистра, инверсный выход триггера подключен к

5 управляющему входу разрешения второго и третьего блоков коммутации, к входам сброса ререрсмвных счетчиков каналов, к входу разрешения регистра и к управляющему входу разрешения первого блока коммута0 . ции, выход каждого цифроанзлогового преобразователя подключен к приводу . соответствующего канала, соединенному с датчиком обратной связи, а первый и второй информационные входы третьего блока

5 коммутации связаны с сигнальными выходами блоков сравнения соответствующих каналов.

1815620

С третьего fiutxockt Sdvirc/rume/ 9 t

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматического управления (его варианты) | 1984 |

|

SU1249481A1 |

| Устройство для реализации быстрого преобразования Фурье | 1984 |

|

SU1233166A1 |

| Линейный интерполятор для систем интерактивной графики | 1988 |

|

SU1608691A1 |

| Круговой интерполятор | 1985 |

|

SU1359772A1 |

| Цифровой линейный интерполятор | 1987 |

|

SU1434406A1 |

| Устройство для вычисления тригонометрических функций | 1984 |

|

SU1166103A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU955082A1 |

| Синусно-косинусный преобразователь | 1981 |

|

SU1042013A1 |

| Генератор векторов | 1987 |

|

SU1437880A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1693592A1 |

Изобретение относится к области автоматики и вычислительной техники, в частности, к устройствам управления станками с программным управлением, машинами термической резки металла. Цель изобретения - улучшение эксплуатационных характеристик устройства за счет стабилизации скорости перемещения рабочего органа для повышения качества и точности обрабатываемых деталей. Устройство для двухкоординатного управления рабочим органом, содержит блок коммутации, интерполятор, группа информационных входов которого подключена к первой группе информационных выходов задатчика кодов, регистр и в каждом канале управления привод, цифроана- логовый преобразователь, группа информационных входов которого соединена с соответствующей группой информационных выходов первого блока коммутации, первая группа входов блока сравнения подключена к соответствующей группе информационных выходов интерполятора. Новым в устройстве является то, что в каждый канал введен датчик обратной связи перемещения, блок останова, триггер, элемент И, элемент ИЛИ, сумматор и блоки памяти синусов и косинусов. 7 ил. (Л С

cmps/rjbsso бь/хода бьщис/ш телд д

свб/хода mpu&tpy 2O

ofnpefapcuSHOZQ счетицка ff

Фиг.4

от интерпб- лятора д

J3

fa

JT

Сл

Фи&.5

Фиг.э

. к элементу МИ 73

л йтороми &локи

xoflifitufnat- щ/и

к третье ни

олсху fCM/fy/TTtr

ц и ц П

К блоку срабне ия координаты X

С третьего .. С выхода ВыхоЗа г Вычислителя 9 вычислителя:)

Фиг.6

К блоку сра#не/а/я

1 KOD/}dV//ff/7X / У

| Булаков А.А | |||

| Исследование квазинепрерывных систем | |||

| - М.: Наука, с.92 | |||

| Авторское свидетельство СССР N2853610,005819/21,1970. |

Авторы

Даты

1993-05-15—Публикация

1990-12-13—Подача