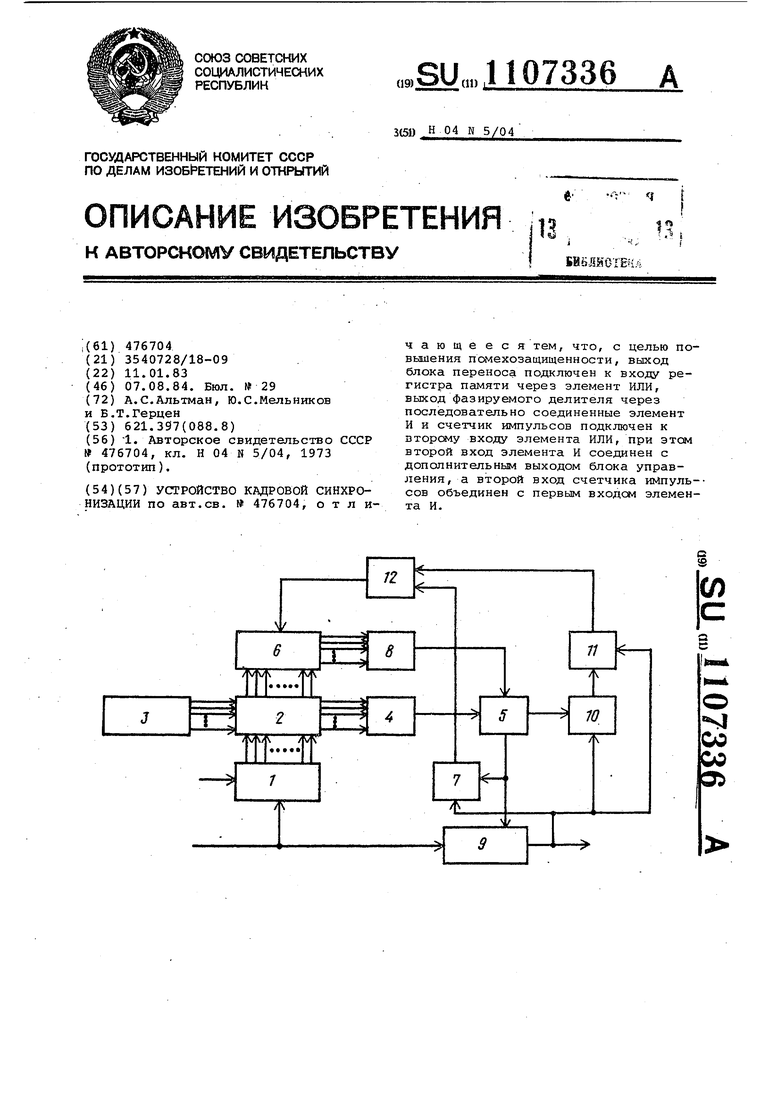

Изобретение относится к телевидению. По основному авт.св. № 476704 известно устройство кадровой синхронизации, содержащее блок сравнения, один вход которого подключен к блоку эталона синхрокода, а другой - к регистру сдвига, на один из входов которого подается видеосигнал, а на Другой - импульс синхронизации, один выход блока сравнения подсоединен к входу регистра памяти, другой через блок управления - к одному входу фазируемого делителя и к одному входу блока переноса, причем импульсы кадровой синхронизации подаются на второй вход фазируемого делителя, с выхода которого импульсы кадровой ckHx ронизации подаются на второй вход блока переноса, выход которого подключен к входу регистра памяти, при этом выхо,ды блока сравнения поразряд но соединены с входами регистра памяти, а выходы регистра памяти и вто рые выходы блока сравнения подключены к входам блока управления через сумматоры Cl Недостатком устройства кадровой синхронизации является низкая помехозащищенность. Цель изобретения - повышение поме хозащищенности устройства кадровой синхронизации. Указанная цель достигается тем, что в устройстве кадровой синхронизации, содержащем регистр сдвига, информационный вход которого является входом группового видеосигнала, вход управления соединен с счетным входом фазируемого делителя и с входом импульсов тактовой синхронизации, а разрядные выходы - с первыми |входами блока сравнения, вторые входы которого соединены с разрядными выходами блока эталона синхрокода, первые выходы - с разрядныг ж входами регистра памяти, а вторые выходы с разрядными входами первого суммато ра , выход которого соединен с первым входом блока управления, разрядные выходы регистра памяти через второй сумматор соединены с вторым входом блока управления, первый выход которого соединен с входом коррекции фазируемого делителя и с первым входом блока переноса, второй вход которого соединен с выходом фазируемого делителя, выход блока переноса подключен к входу регистра- памяти через элемен ИЛИ, выход .фазируемого делителя чере последовательно соединенные злемент И и счетчик импульсов подключен к второму входу элемента ИЛИ, при этом второй вход элемента И соединен с дополнительным выходом блока управления, а второй вход счетчика импуль сов объединен с первым входом элемен та И. На чертеже представлена структурная электрическая схема устройства кадровой синхронизации. Устройство кадровой синхронизации содержит регистр 1 сдвига, блок 2 сравнения, блок 3 эталона синхрокода, первый сумматор 4, блок 5 управления, регистр 6 памяти, блок 7 переноса, второй сумматор 8, фазируемый делитель 9, элемент И 10, счетчик 11 импульсов, злемент ИЛИ 12. Устройство кадровой информации работает следующим образом. Групповой видеосигнал, содержащий в потоке информационных символов п-разрядные коды синхронизации, поступает На информационный вход регистра 1 сдвига, управляемый импульсами тактовой синхронизации. N-разрядные коды с выхода регистра 1 сдвига в блоке 2 сравнения сравниваются с п-разрядным кодом, поступающим с блока 3 эталона синхрокода. Результат сравнения с блока 2 сравнения поступает на входы первого сумматора 4 и на информационные входы регистра 6 памяти, сигнал с выходов которого через второй сумматор 8 поступает на второй вход блока 5 управления, на первый вход которого поступает сигнал с выхода первого сумматора 4. Влок 5 управления имеет два выхода. На его основном первом выходе сигнал появляется только в случае превышения сигналом с первого сумматора 4 сигнала с второго сумматора 8. Сигнал с первого выхода блока 5 управления через блок 7 переноса и элемент ИЛИ 12 осуществляет запись текущего значения из блока 2 сравнения в регистр 6 памяти для последующегоанализа. Этот же сигнал с первого выхода блока 5 управления Фазирует фазируемый делитель 9, который защищает устройство от кратковременных пропаданий синхрокодов на входе устройства. На втором дополнительном выходе блока 5 управления сигнал появится при равенстве содержимых первого 4 и второго 8 сумматоров. Этот сигнал поступает на второй вход элемента И 10, на первый вход которого поступает кадровый импульс с выхода фазируемого делителя 9. При синхронном состоянии фазируемого делителя 9 относительно входного сигнала импульсы на входе элемента И 10 совпадают по времени, при этом с выхода элемента И 10 поступает импульс на первый вход счетчика 11 импульсов, на второй вход которого поступают импульсы с частотой кадров. Если за время t TN (т - период следования кадровых синхроимпульсов) N - их количество) на первый вход счетчика 11 импульсов поступает меньше k импульсов, то на его выходе фор311073364

мируется дополнительный импульс пере- Таким образом, введение в устройстноса, который через элемент ИЛИ 12во элемента И, счетчика импульсов и

записывает в регистр б памяти теку-элемента ИЛИ позволяет путем оценки

щее значение результата сравнения.качества синхроканала непрерывЕсли же за это время это число им-но контролировать найденную фазупульсов больше К, то дополнительный 5кадровой синхронизации и восстаимпульс переноса не формируется, инавливать ее истинное положение в регистре 6 памяти записанное ранеев случае потери синхронизазначение не меняется.ции.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство кадровой синхронизации | 1973 |

|

SU476704A1 |

| Устройство кадровой синхронизации | 1975 |

|

SU567217A1 |

| Устройство кадровой синхронизации | 1986 |

|

SU1356257A1 |

| Устройство кадровой синхронизации | 1977 |

|

SU651495A1 |

| Генератор видеосигнала системы передачи данных | 1973 |

|

SU527020A1 |

| Способ формирования и приема телевизионного сигнала при передаче изображения и система для его осуществления | 1986 |

|

SU1453619A1 |

| Устройство для воспроизведения видеосигнала | 1987 |

|

SU1555918A1 |

| Устройство для распознавания контуров изображений | 1983 |

|

SU1156103A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162248C2 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162247C2 |

УСТРОЙСТВО КАДРОВОЙ СИНХРОНИЗАЦИИ по авт.св. 476704, отличающееся тем, что, с целью повышения псмехозащищенности, выход блока переноса подключен к входу регистра памяти через элемент ИЛИ, выход фазируемого делителя через последовательно соединенные элемент И и счетчик импульсов подключен к вторсму входу элемента ИЛИ, при этом второй вход элемента И соединен с дополнительным выходом блока управления, а второй вход счетчика иМпуль-сов объединен с первым входом элемента И. (Л «SJ 00 :

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство кадровой синхронизации | 1973 |

|

SU476704A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-08-07—Публикация

1983-01-11—Подача