арифметико-погического блока, вторым входом третьего счетчика, четвертым входом формирователя порога и является первым входом устройства, вторым входом которого является шестой вход арифметико-логического блока.

2. Устройство по п.1, о т л и чающееся тем, что арифметико-логический блок содержит последовательно соединенные второй вычитатель, делитель и второй пороговый -j элемент, второй вход и выход которого

являются, соответственно шестым входом и первым выходом арифметико-логического блока, вторым выходом которого является второй выход делителя, второй, третий и четвертый входы которого являются соответственно третьим, четвертым и пятым входами арифметикологического блока, вторым входом которого является первый вход второго вычитателя, второй вход которого соединен с пятым входом делителя и является первым входом арифметико-логического блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распознавания контуров изображений объектов | 1985 |

|

SU1359788A2 |

| Устройство для распознавания контуров изображений объектов | 1985 |

|

SU1270781A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1997 |

|

RU2116670C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1999 |

|

RU2149446C1 |

| Устройство для выделения изображений подвижных объектов | 1987 |

|

SU1462373A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ЭТАЛОННОЙ КАРТЫ МЕСТНОСТИ ДЛЯ НАВИГАЦИОННЫХ СИСТЕМ | 1992 |

|

RU2022355C1 |

| Устройство поиска псевдослучайной последовательности | 1991 |

|

SU1788592A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА КАНАЛА СВЯЗИ | 2002 |

|

RU2216865C1 |

| Устройство для передачи и приема информации | 1987 |

|

SU1449989A1 |

1. УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ КОНТУРОВ ИЗОБРАЖЕНИЙ, содержащее формирователь порога и последовательно соединенные датчик видеосигнала, блок дифференцирования, первьй пороговый элемент и блок регистрации, причем первый и второй входы формирователя порога подключены соответственно к первому и второму выходам датчика видеосигнала, третий выход которого подключен ко второму входу блока дифференцирования и третьему входу формирователя порога, отличающееся тем, что, с целью повьшения достоверности распознавания контуров изображений в условиях низкого контраста и пространственных помех, в . устройство заведены первый вычитатель, первый вход которого подключен к выходу формирователя порога, первый блок памяти, последовательно соединенные второй блок памяти и арифметико-логический блок, второй и третий входы которого подключены соответственно к первому выходу первого блока памяти и второму выходу второго блока памяти, третий и четвертый выходы которого подключены к первым входам соответственно блока регистрации и первого блока памяти, и последовательно соединенные первьш: элемент И, первьм счетчик, второй счетчик, второй элемент И и третий счетчик, выход которого подключен ко второму входу первого вычитателя, выход которого подключен ко второму входу первого порогового элемента, выход которого подключен к первому входу второго элемента И, четвертым входам первого блока памяти и второго блока памяти и ко второму входу первого счет(Л чика, третий вход которого соединен со вторыми входами второго счетчика, второго элемента И, первого блока памяти, с первым входом второго блока памяти и подключен ко второму выходу датчика видеосигнала, пятьм вход и второй выход первого блока памяти 01 подключены соответственно ко второму 05 выходу формирователя порога и к третьему входу второго счетчика, выход которого подключен ко второму 00 входу второго блока памяти, третий вход которого соединен с третьим входом первого блока памяти, четвертым входом арифметико-логического блока, вторыми входами блока регистрации и первого элемента И и подключен к третьему выходу датчика видеосигнала а первьй и второй выходы арифметикологического блока подключены соответственно к третьему и четвертому входам блока регистрации, пятый вход которого соединен с пятым входом

Изобретение относится к автоматике и вычислительной технике и может быть использовано для автоматизации, процесса распознавания изображения размерных объектов по признаку наличия заданного числа связных элементов контура изображения объекта.

Известно устройство для распознавания контуров изображений, содержащее блок принятия решений, последовательно соединенные блок динамической расфокусировки, блок поэлементного считьюания информации и К идентичных каналов, где К определяется числом анализируемых совместно пар смежных элементов изображения,причем каждьй из каналов состоит из последовательно соединенных элемента сравнения и блока формирования импульса, а каждьй из К первых и вторых выходов блока поэлементного считьшания информации соединен, соответственно для каждого из К каналов, с первым и вторым выходами элемента сравнения а выходы блоков формирования импульсов каждого из К каналов соединены соответственно с К входами блока прИ нятия решений 1J .

Недостатком этого устройства является то, что оно работает при одной заранее заданной величине порогового эталонного сигнала. В результате около 75% элементов ложных контуров остаются неопознанными,

что приводит к низкой достоверности

распознавания объекта.

Наиболее близким к предлагаемому по технической сущности является устройство для распознавания контуров изображений, содержащее формирователь порога и последовательно соединенные датчик видеосигнала, блок дифференцирования, пороговьй элемент и блок регистрации, причем выход формирователя порога подключен ко второму входу порогового элемента,, а первый и второй входы формирователя порога подключены соответственно к первому и второму выходам датчика эидеосигнапа, третий выход которого подключен ко второму входу блока диф ференцирования и третьему входу формирователя порога И

Данное устройство позволяет адаптивно изменять величину порогового сигнала, однако характеризуется низкой достоверностью распознавания контуров сложных изображений. Применение адаптивного порога позволяет повысить достоверность распознавания только для изображений объектов с прямолинейным контуром. При этом указанньй положительный эффект достигается путем понижения порогового уровня при простых равномерных фонах и повышением этого уровня при сложных фонах.

Целью изобретения является повышение достоверности распознавания контуров изображений в условиях низкого контраста и пространственных помех.

Поставленная цель достигается тем, что в устройство распознавания контуров изображений, содержащее формирователь порога и последовательно соединенные датчик видеосигнала, блок дифференцирования, первый пороговый элемент и блок регистрации, причем первый и второй входы формирователя порога подключены соответственно к .первому и второму выходам датчика видеосигнала, третий выход которого подключен ко второму входу блока дифференцирования и третьему входу форг мирователя порога, дополнительно введены первый вычитатель, первый вход которого подключен к выходу формирователя порога, первый блок па.мяти, последовательно соединенные второй блок памяти и арифметико-логический блок, второй и третий входы которого подключены соответственно к первому выходу первого блока памяти и второму выходу второго блока памяти, третий и четвертый выходы которого подключены к первым входам соответственно блока регистрации и первого блока памяти, и последовательно соединенны первый элемент И, первый счетчик, второй счетчик, второй элемент И и третий счетчик, выход которого под- ключей ко второму входу первого вычитателя, выход которого подключен ко второму входу первого порогового элемента, выход которого подключен к первому входу второго элемента И, четвертым входам первого блока памяти и второго блока памяти и ко второму входу первого счетчика, третий вход которого соединен со вторыми входами второго счетчика,второго элемента И, первого блока памяти, с первым входом второго блока памяти и подключен ко второму выходу датчика видеосигнала, пятый вход и второй выход первого блока памяти подключены соответственно ко второму выходу формирователя порога и к третьему входу второго счетчика, выход которого подключен ко второму входу второго блока памя ти, третий вход которого соединен с третьим входом первого блока памяти, четвертым входом арифметико-логического блока, вторыми входами блока регистрации и первого элемента И и подключен к третьему выходу датчика : видеосигнала, а первый и второй выходы арифметико-логического блока подключены соответственно к третьему

и четвертому входам блока регистрации, пятый вход которого соединен с пятым входом арифметико-логического блока, вторым входом третьего счетчика, четвертым входом формирователя порога и является лервым входам устройства, вторым входом которого является шестой вход арифметико-логического блока.

Кроме того, арифметико-логический блок содержит последовательно соединенные второй вычитатель, делитель и второй пороговый элемент, второй вход и выход которого являются соответственно шестым входом и первым выходом арифметико-логического бло|Ка, вторым выходом которого является второй выход делителя, второй, третий и четвертый входы которого являются соответственно третьим, четвертым и пятым входами арифметикологического блока, вторым входом которого является первьй вход второго вычитателя, второй вход которого соединен с пятым входом делителя и является первым входом арифметикологического блока.

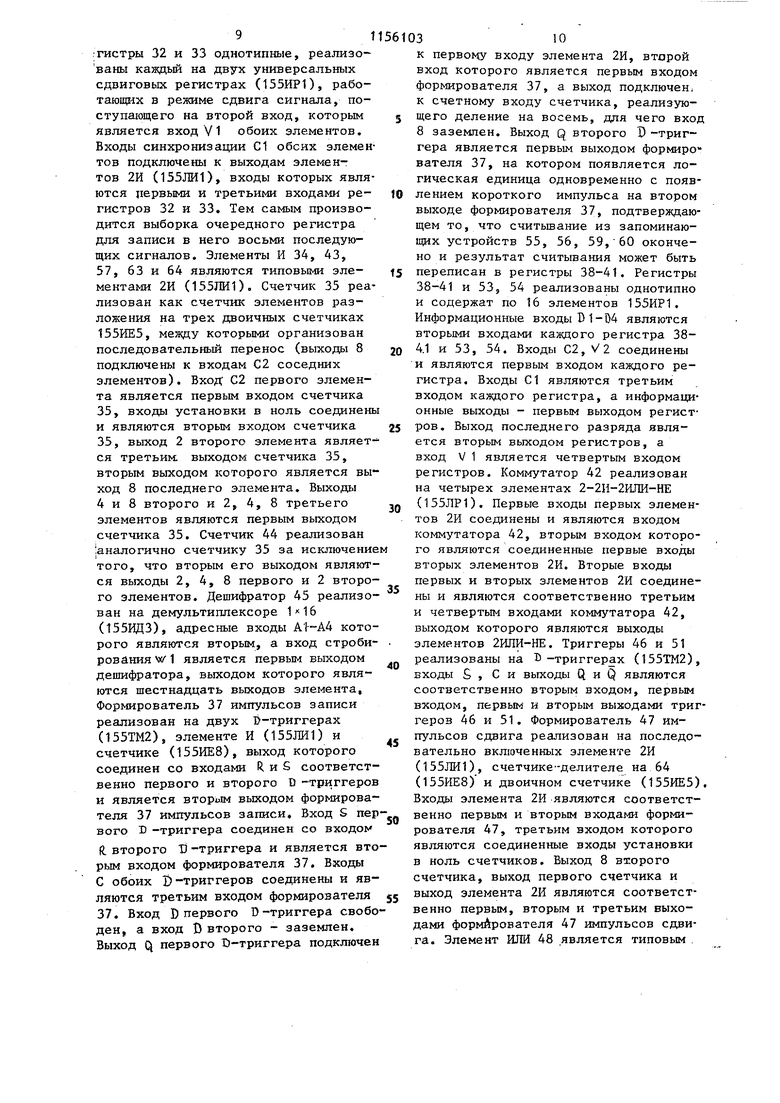

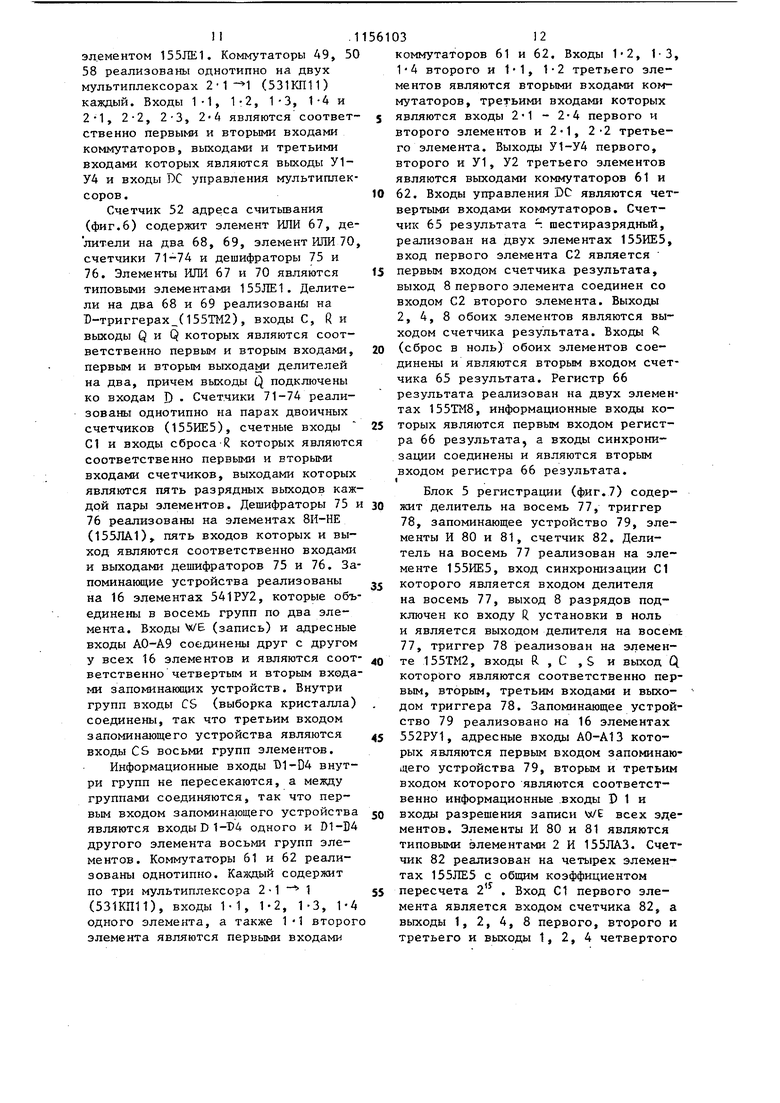

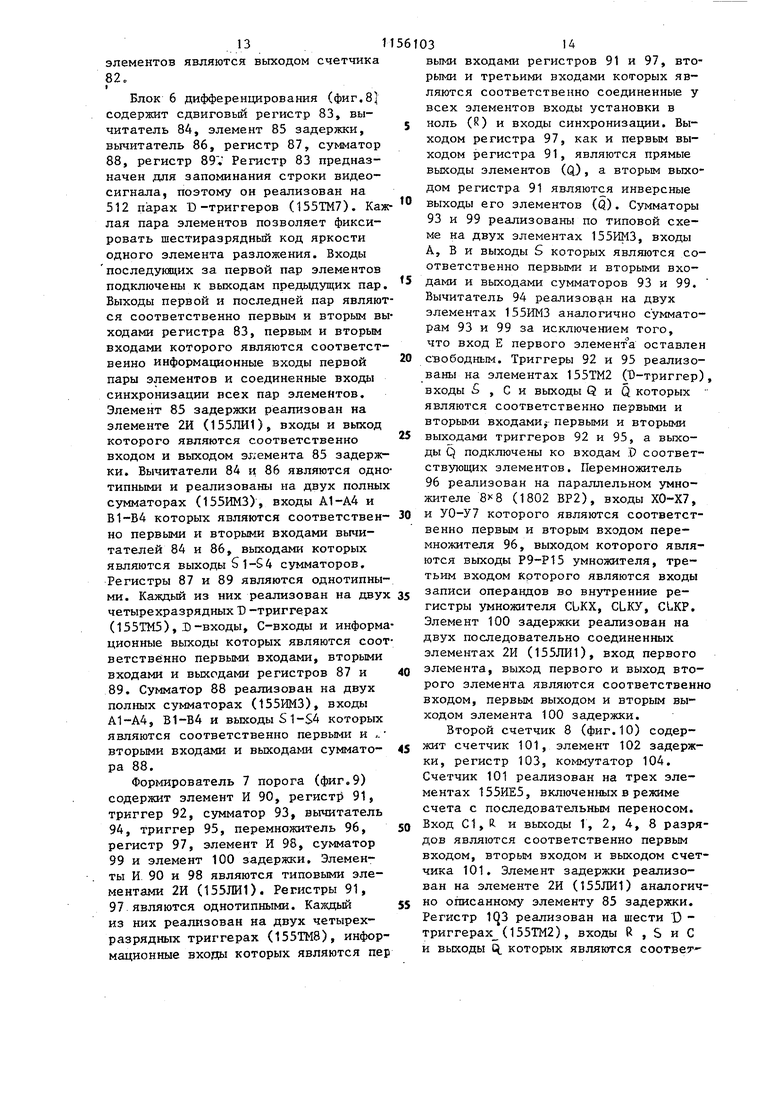

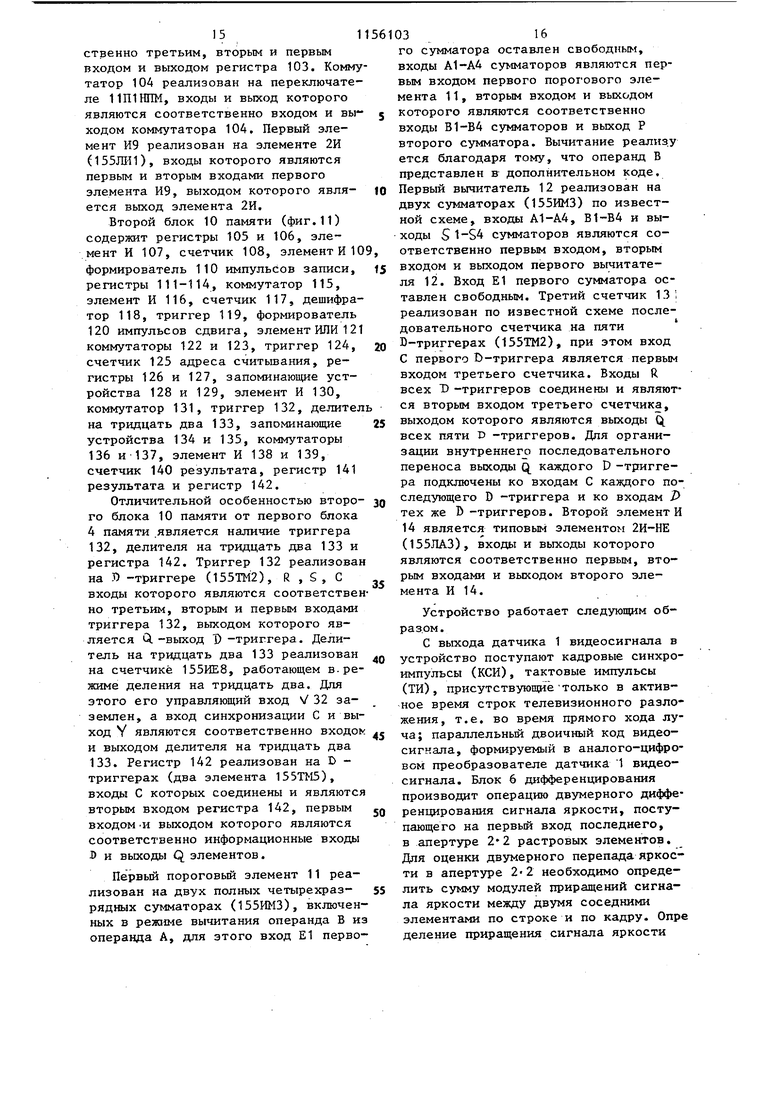

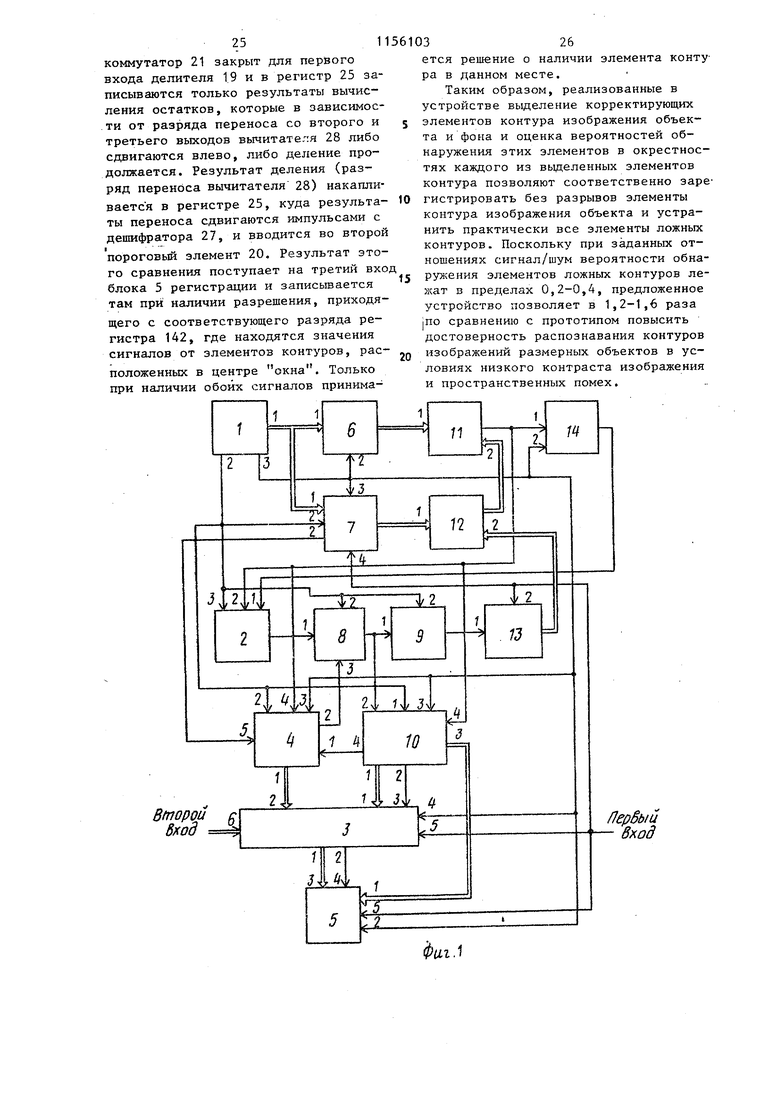

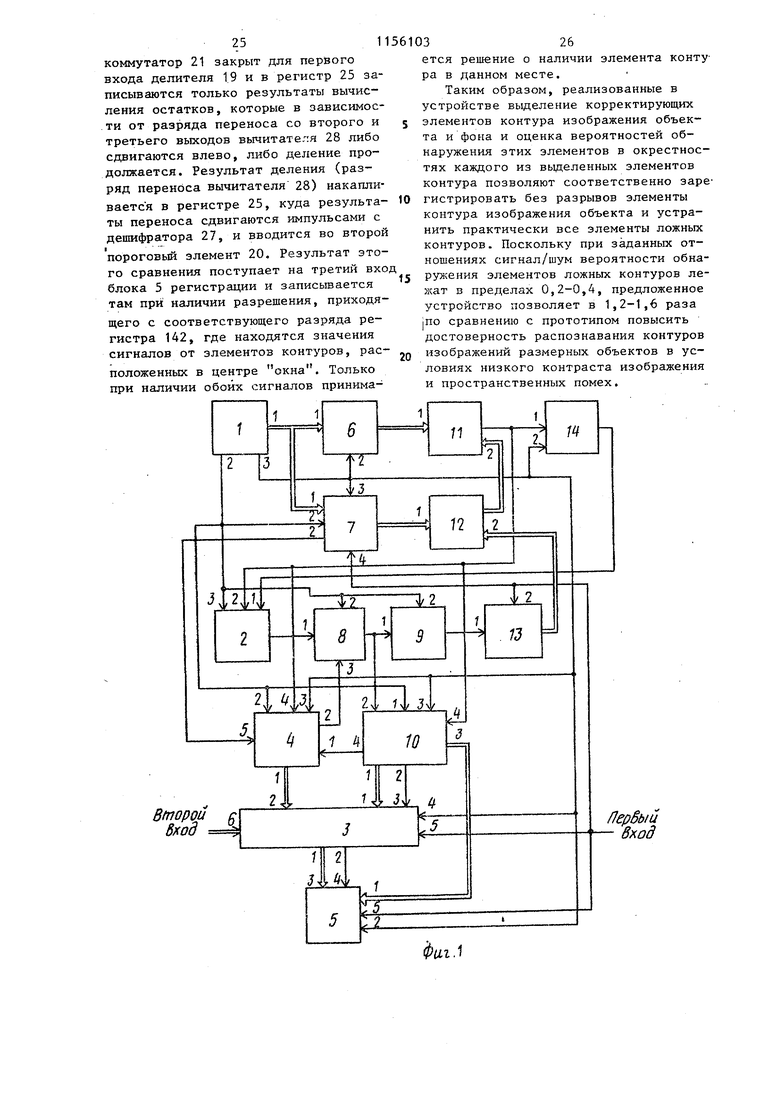

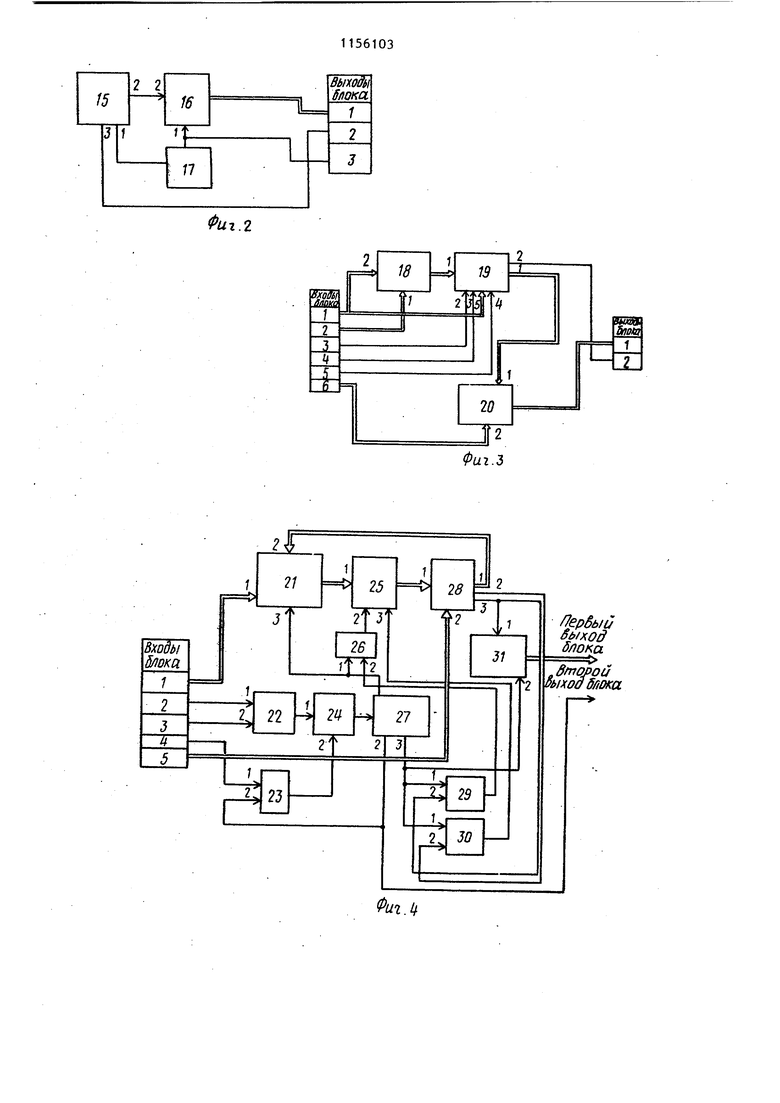

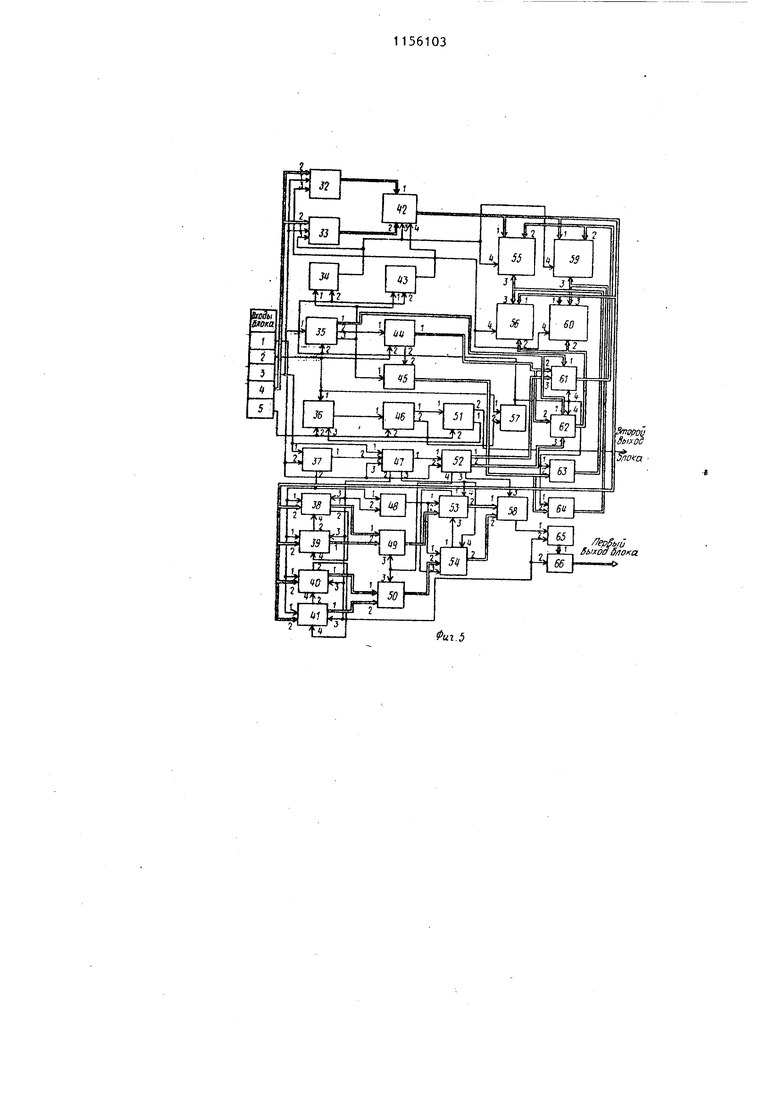

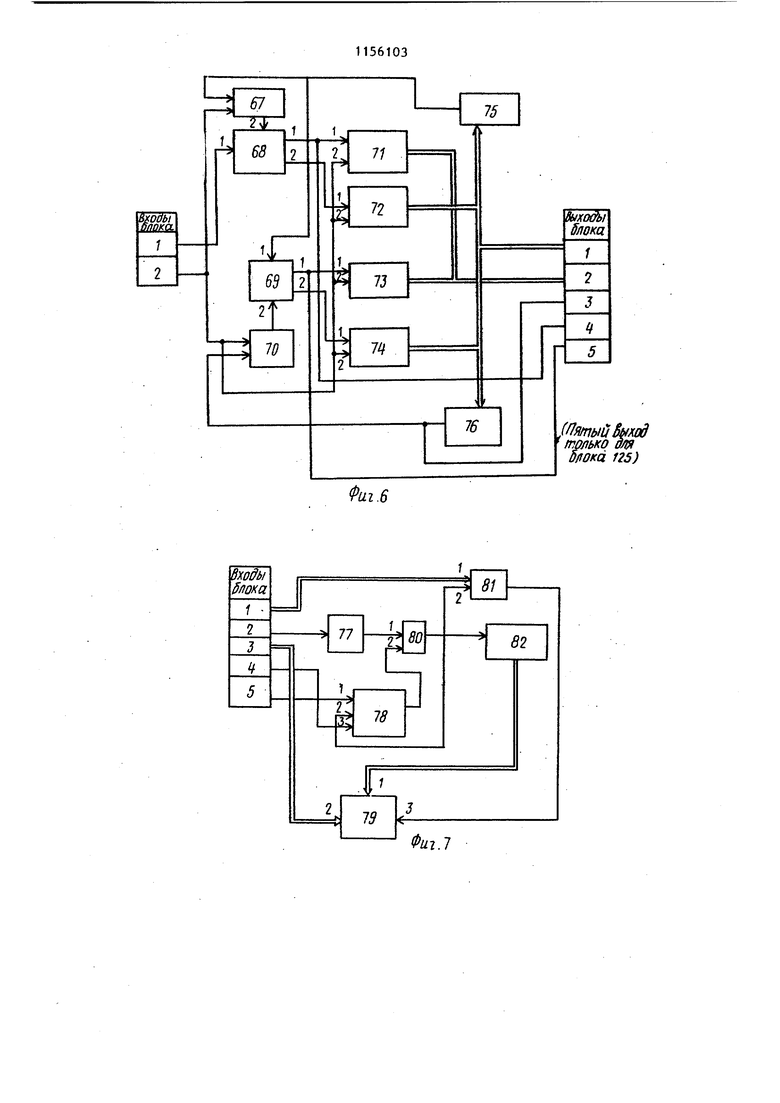

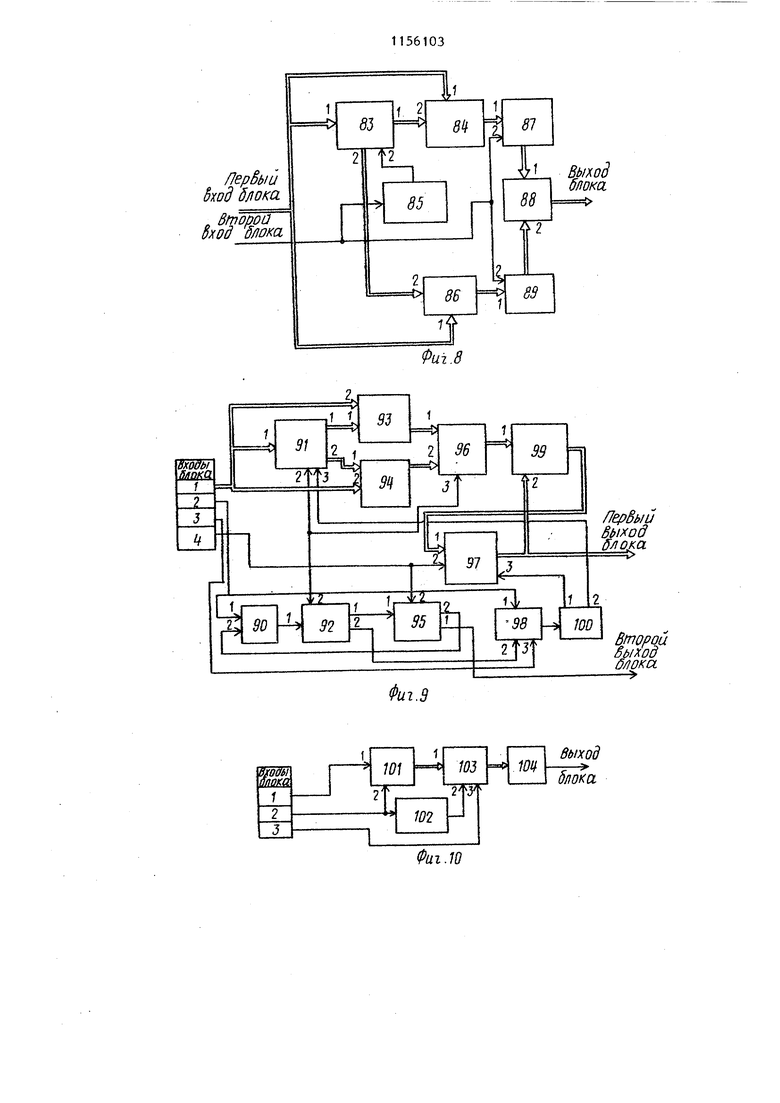

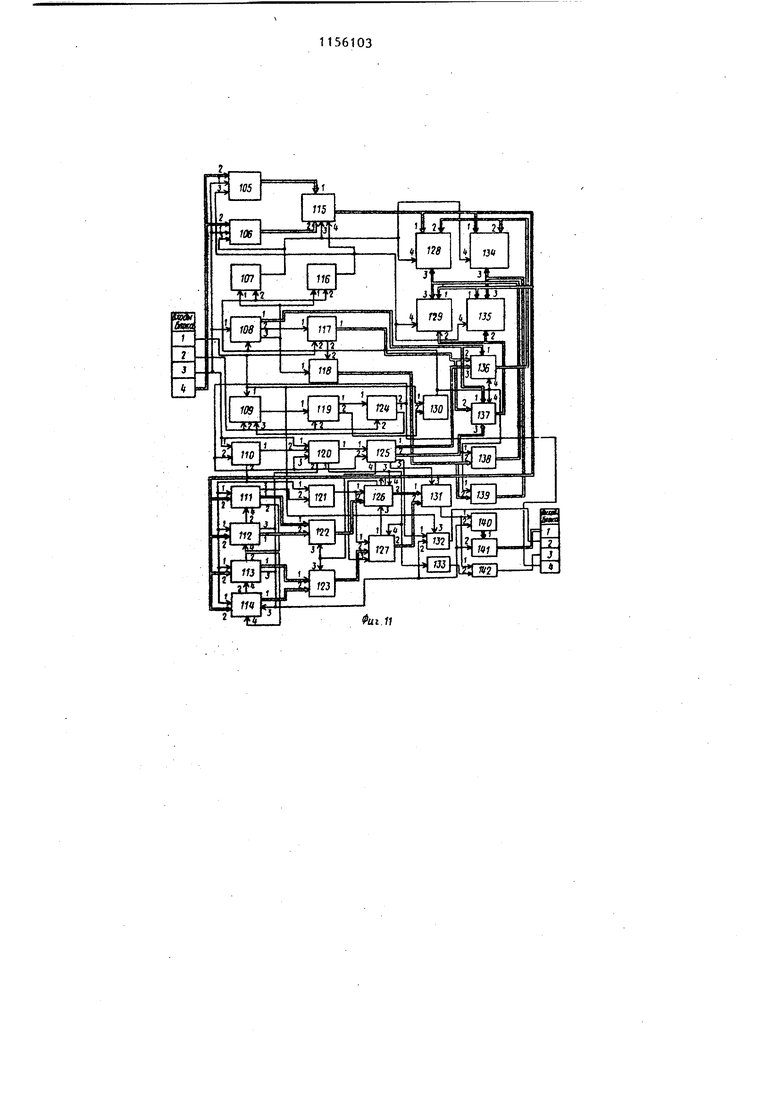

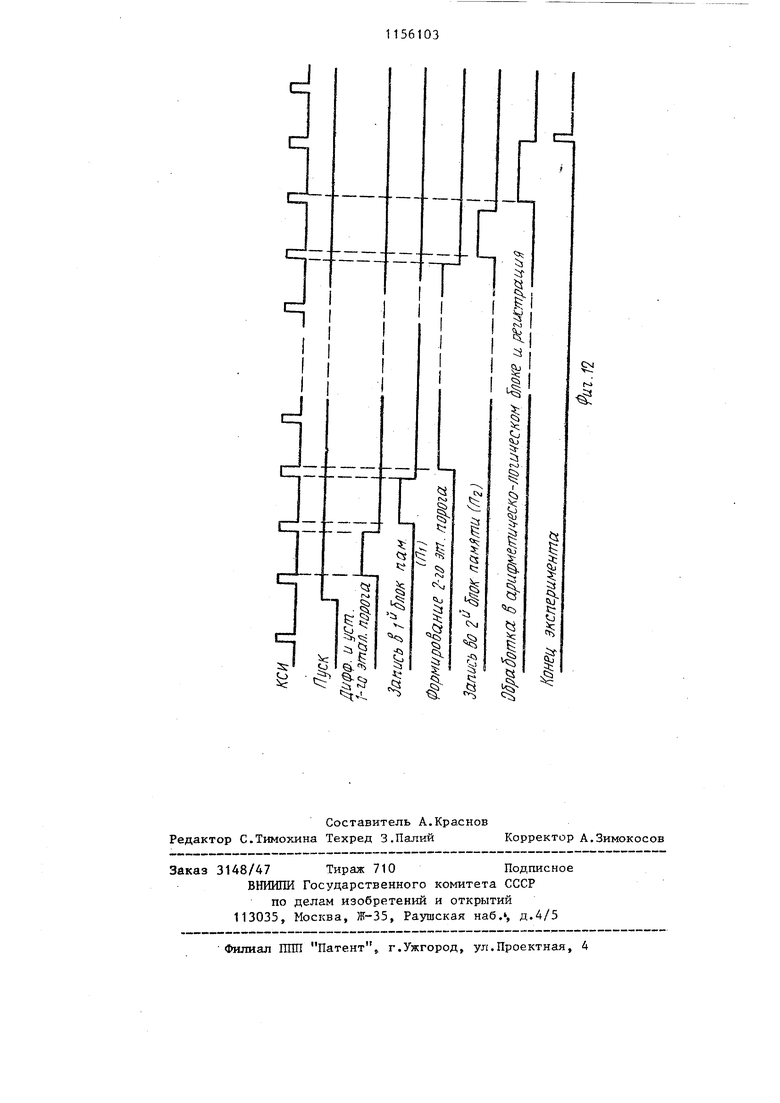

На фиг.1 изображена функциональная схема предлагаемого устройства; на фиг.2 - структурная схема датчика видеосигнала-, на фиг.З - структурная схема арифметико-логического блока-, на фиг.4 - структурнс1я схема делителяi на фиг.З - структурная схема первого блока памяти на фиг.6 - структурная схема счетчика адреса считывания; на фиг.7 -структурная схема блока регистрации; на фиг.8 - структурная схема блока дифференцирования J на фиг.9 - структурная схема формирователя порога на фиг.10 - структурная схема второго счетчикаi на фиг.11 - структурная схема второго блока памяти на фиг.12 - временные диаграммы, поясняющие работу устройства.

Устройство содержит (фиг.1) датчик 1 видеосигнала, первый счетчик 2, арифметико-логический блок 3,- первый блок 4 памяти, блок 5 регистрации, блок 6 дифференцирования, формирователь 7 порога, второй счетчик 8, первый элемент И 9, второй блок 10 памяти, первый пороговый элемент 11, первый вычитатель 12, третий счетчик 13, второй элемент И 14, первый вход которого сое динен с четвертыми входами первого 4 и второго 10 блоков памяти, со вторым входом первого счетчика 2 и подключен к выходу первого порогового элемента 11, первый и второй входы которого подключены к выходам соответственно блока 6 дифференцирования и первого вычитателя 12, первый и второй входы которого подключены к выходам соответственно формирователя 7 порога и третьего счетчика 13, первый вход которого соединен с выходом первого элемента И 9, а второй вход соединен с чет вертым входом формирователя 7 порога, с пятыми входами арифметикологического блока 3 и блока 5 регист рации и является первым входом устройства. Вторым входом устройства является шестой вход арифметико-логического блока 3, первый, второй и третий входы которого подключены соответственно к первому выходу второго блока 10 памяти, к первому выходу первого блока 4 памяти и ко второму выходу второго блока 10 памяти, а первый и второй выходы подключены соответственно к третьему и четверто му входам блока 5 регистрации, первый вход которого подключен к третье му выходу второго блока 10 памяти, а второй вход соединен с четвертым входом арифметико-логического блока 3, со вторыми входами блока 6 дифференцирования и второго элемента И 14, с третьими входами первого 4 и второго 10 блоков памяти и формирователя 7 порога и подключен к третьему выходу датчика 1 видеосигнала, первый выход которого подключен к первым входам блока 6 дифференцирования и формирователя 7 порога, а второй выход подключен ко вторым входам фор мирователя 7 порога, второго счетчика 8, первого элемента И 9, первого блока 4 памяти, к первому входу второго блока 10 памяти и к третьему входу первого счетчика 2, первый вхо которого подключен к выходу второго элемента И 14, а вьпсод подключен к первому входу второго cчetчикa 8, третий вход которого подключен ко второму выходу первого блока 4 памя. ти, первьй и пятьй входы которого подключены соответственно к чeтвepтo му выходу второго блока 10 памяти и второму выходу формирователя 7 порога. Первый вход первого элемента И 9 соединен со вторым входом второго 1 3 блока 10 памяти и подключен к выходу второго счетчика 8. Датчик 1 видеосигнала (фиг,2) содержит телевизионную камеру 15, аналого-цифровой преобразователь (АЦП) 16 и генератор 17. Телевизионная камера 15 реализована, например, на передающей телевизионной трубке ЛИ-17 промышленной телевизионной установки ИОАН-4. Камера работает в режиме прогрессивной развертки с частотой кадров 25 Гц. Число строк 625. С первого выхода камеры 15 поступают строчные синхроимпульсы, запускающие генератор 17, реализованный по стандартной схеме на линии задержки, вход и выход которой подключен COOT ветственно к выходу и первому входу элемента 2И-НЕ (155ЛАЗ), второй вход которого является входом генератора, Разрешающим сигналом с первого выхода камеры является логическая единица, с появлением которой на первьй вход АЦП 16 поступают импульсы с частотой разложения элементов (12,5мГц), необходимые для преобразования аналог-цифра, которое выполняется АЦП 16, реализованным на микросхеме 1107ПВ1. С выхода АЦП 16 получаем параллельный шестиразрядный код яркости каждого элемента разложения. Третий выход камеры 15 является выходом внутреннего генератора кадровых синхроимпульсов. Первый счетчик 2 реализован по типовой схеме счетчика-делителя с перестраиваемым коэф фициентом деления на четырехразрядном двоичном счетчике-делителе 155ИЕ5, счетный вход С1 которого является первым входом первого счет ика 2, а выходы 1, 2, 4 и 8 подключены к переключателю типа 4П1НПМ, выход которого подключен к первому входу элемента ЗИ-НЕ (155JIA4), втоРой и третий входы которого являются соответственно вторым и третьим выходами первого счетчика 2, а выход соединен со входами R -двоичного счетчика ИЕ5 для осуществления сброса последнего в трех случаях: при отсутствии сигнала с выхода первого порогового элемента 11, при совпаде«™ состояния счетчика с положением переключателя, выполняющим функцию коммутатора и при поступлении кадро3° ° синхроимпульса. Арифметико-логический блок 3 (фиг.З) содержит последовательно соединенные второй вычитатель 18, делитель 19 и второй пороговый элемент 20, второй вход и выход которого являются соответственно шестым входом и первым выходом арифметико-логи ческого блока 3, вторым и третьим, четвертым и пятым входами которого являются соответственно первый вход второго вычитателя 18, второй, третий и четвертый входы делителя 19, пятый вход которого соединен со вторым входом второго вычитателя 18 и является первым входом арифметикологического блока 3, а второй выход является вторым выходом арифметикологического блока 3. Второй вычитатель 18 реализован по типовой схеме вычитателя на двух полных четырехразрядных сумматорах (155ИМЗ), входы А1-А4 первого слагаемого которых являются вторым входом второго вычитателя 18, входы В1-В4 второго слагаемого подключены к выходам соответствующих инверторов (155ЛН1), входы которых являются первым входом второ-75 го вычитателя 18. Цепь переноса замыкается соединением выхода переноса Р первого сумматора со входом Е вто|РОГО. Выходы S1-S4 первого и S1, .2 второго сумматоров являются выходом второго вычитателя 18. Делитель 19 (фиг.4) содержит коммутатор 21, элемент И 22,элемент И 23, счетчик 24, регистр 25, элемент ИЛИ 26 дешифратор 27, вычитатель 28, элемент И 29, элемент И 30 и регистр 31. Коммутатор 21 реализован на двух мультиплексорах 2x1 - 1 (531КП11), входы , 1-3, 1-4, которых являются первым входом коммутатора 21, входы 2-1,.22, , 24 являются вторьЫ входом коммутатора 21, третьим входом которого являются соединенные управ,ляющие входы С обоих мультиплексо-. ров, а выходы У1, У2, УЗ, У4являютс; выходом коммутатора 21. Элементы И 22 23, 29 и 30 являются стандартными элементами 2И (155ЛИ1). Счетчик 24 реализован на двоичном четырехразрядном счетчике (155ИЕ5), входы С1 и ll которого являются соответственно первым и вторым входами счетчика 24. Регистр 25 реализован на двух четырехразрядных универсальных сдвиговых регистрах (155ИР1), информационные входы В1, D 2, D 3, D 4 первого и В1 Ъ2 второго являются первым входом регистра 25, информационные выходы 1,

2, 4, 8 первого и 1, 2 второго являются выходом регистра 25, управляющие входы С2 иУ2 (запись) являются вторым входом регистра 25, а управляющий вход С1 (сдвиг) является третьим входом регистра 25. Элемент ИЛИ 26 является типовым элементом 2ШШ (155ЛЕ1). Дешифратор 27 реализован на демультиштексоре (155ИДЗ) 116,

управлякнцие адресные входы которого А1-А4 являются входом дешифратора 27, первым и вторым входами которого являются соответственно первьй и седьмой выходы демультиплексора, выходы которого со второго по седьмой подключены к семи входам элемента 8И-НЕ (155ЛАО выход которого является третьим входом дешифратора 27. Вычитатель 28 реализован на двух

элементах 155ИМЗ, включенных в режиме вычитания, для этого вход Е первого элемента оставлен свободным, входы А1-А4 первого элемента и А1, А2 второго являются первым входом вычитателя 28, входы В1-В4 первого элемента и В1, В2 второго подключены к выходам соответствующих инверторов, входы которых являются вторым входом вычитателя 28, выходы 1-4 первого элемента и 1, 2 второго являются первым выходом вычитателя 28, вторым и третьим выходами которого являются соответственно выход инвертора (155ЛН1) и выход 3 второго элемента, подключенный также ко входу последнего инвертора. Регистр 31 реализован на двух универсальных регистрах 155ИР1, входы С1 и VI которых являются соответственно вторьтм и первым входами регистра 31, выходами которого являются информационные выходы 1,2, 4, 8 первого и 1, 2 второго элементов. Первый блок 4 памяти (фиг.5) содержит регистры 32 и 33, элемент И 34, счетчик 35, элемент И 36, формирователь 37 импульсов записи, регистры 38-41, коммутатор 42, элемент И 43, счетчик 44, дешифратор 45, триггер 46, формирователь импульса сдвига, элемент ИЛИ 48, коммутаторы 49 и 50, триггер 51, счетчик 52 адреса считьшания, регистры 53 и 54, запоминанщие устройства 55 и 56, элемент И 57, коммутатор 58, эапоминакяцие устройства 59 и 60, коммутаторы 61 и 62, элементы И 63 и 64, счетчик 65 результата и регистр 66 результата. Регистры 32 и 33 однотипные, реализованы каждьй на двух универсальных сдвиговых регистрах (155ИР1), работающих в режиме сдвига сигнала, поступающего на второй вход, которым является вход V1 обоих элементов. Входы синхронизации С1 обеих элемен тов подключены к выходам элементов 2И (155ЛИ1), входы которых явля ются первыми и третьими входами регистров 32 и 33. Тем самым производится выборка очередного регистра для записи в него восьми последующих сигналов. Элементы И 34, 43, 57, 63 и 64 являются типовыми элементами 2И (155ЛИ1). Счетчик 35 реа лизован как счетчик элементов разложения на трех двоичных счетчиках 155ИЕ5, мезкду которыми организован последовательный перенос (выходы 8 подключены к входам С2 соседних элементов). Вход С2 первого элемента является первым входом счетчика 35, входы установки в ноль соединен и являются вторым входом счетчика 35, выход 2 второго элемента являет ся третьим, выходом счетчика 35, вторым выходом которого является вы ход 8 последнего элемента. Выходы 4 и 8 второго и 2, 4, 8 третьего элементов являются первым выходом счетчика 35. Счетчик 44 реализован аналогично счетчику 35 за исключени того, что вторым его выходом являют ся выходы 2, 4, В первого и 2 второ го элементов. Дешифратор 45 реализо ван на демультиплексоре (155ИДЗ), адресные входы Al-А4 кото рого являются вторым, а вход строби рования W1 является первым выходом дешифратора, выходом которого являются шестнадцать выходов элемента. Формирователь 37 импульсов записи реализован на двух lj-триггерах (155ТМ2), элементе И (155ЛИ1) и счетчике (155ИЕ8), выход которого соединен со входами R. и S соответст венно первого и второго D -триггеро и является вторим выходом формирова теля 37 импульсов записи. Вход S пе вого И -триггера соединен со входом R. второго 13-триггера и является вт рым входом формирователя 37. Входы С обоих D-триггеров соединены и яв ляются третьим входом формирователя 37. Вход D первого D-триггера своб ден, а вход В второго - заземлен. Выход Q первого 15-триггера подключе к первому входу элемента 2И, второй вход которого является первым входом формирователя 37, а выход подключен, к счетному входу счетчика, реализующего деление на восемь, для чего вход 8 заземлен. Выход Q второго I) -триггера является первым выходом формирователя 37, на котором появляется логическая единица одновременно с появлением короткого импульса на втором выходе формирователя 37, подтверждающем то, что считьшание из запоминающих устройств 55, 56, 59,60 окончено и результат считывания может быть переписан в регистры 38-41, Регистры 38-41 и 53, 54 реализованы однотипно и содержат по 16 элементов 155ИР1, Информационные входы 1)1-04 являются вторыми входами каждого регистра 384.1 и 53, 54. Входы С2, V2 соединены и являются первьм входом каждого регистра. Входы С1 являются третьим входом каждого регистра, а информационные выходы - первым выходом регистров. Выход последнего разряда является вторым выходом регистров, а вход V 1 является четвертым входом регистров. Коммутатор 42 реализован на четырех элементах 2-2Н-2ИЛИ-НЕ (155ЛР1), Первые входы первых элементов 2И соединены и являются входом коммутатора 42, вторым входом которого являются соединенные первые входы вторых элементов 2И. Вторые входы первых и вторых элементов 2И соединены и являются соответственно третьим и четвертым входами коммутатора 42, выходом которого являются выходы элементов 2ИЛИ-НЕ, Триггеры 46 и 51 реализованы на D -триггерах (155ТМ2), входы , С и выходы Q и Q являются соответственно вторым входом, первым входом, первым и вторым выходами триггеров 46 и 51. Формирователь 47 импульсов сдвига реализован на последовательно включенных элементе 2И (155ЛИ1), счетчике-делителе на 64 (155ИЕ8) и двоичном счетчике (155ИЕ5). Входы элемента 2И являются соответственно первым и вторым входами формирователя 47, третьим входом которого являются соединенные входы установки в ноль счетчиков. Выход 8 второго счетчика, выход первого счетчика и выход элемента 2И являются соответственно первым, вторым и третьим выходами формирователя 47 импульсов сдвига. Элемент ИЖ 48 является типовым .

элементом 155ЛЕ1. Коммутаторы 49, 50 58 реализованы однотипно на двух мультиплексорах 21 (531КП11) каждый. Входы 1-1, 1-2, 1-3, 1-4 и 2-1, 2-2, 2-3, 2-4 являются соответственно первыми и вторыми входами коммутаторов, выходами и третьими входами которых являются выходы У1У4 и входы DC управления мультиплексоров.

Счетчик 52 адреса считьшания (фиг.6) содержит элемент ИЛИ 67, делители на два 68, 69, элемент ИЛИ 70, счетчики 71-74 и дешифраторы 75 и 76. Элементы ИЛИ 67 и 70 являются типовыми элементами 155ЛЕ1. Делители на два 68 и 69 реализованы на 1)-триггерах(155ТМ2), входы С, R и выходы Q и Q которых являются соответственно первым и вторым входами, первым и вторым выходами делителей на два, причем выходы Q подключены ко входам D Счетчики 71-74 реализованы однотипно на парах двоичных счетчиков (155ИЕ5), счетные входы С1 и входы сброса-R которых являются соответственно первыми и вторыми входами счетчиков, выходами которых являются пять разрядных выходов каждой пары элементов. Дешифраторы 75 и 76 реализованы на элементах 8И-НЕ (155ЛА1),. пять входов которых и выход являются соответственно входами и выходами дешифраторов 75 и 76. Запоминагацие устройства реализованы на 16 элементах 541РУ2, которые объединены в восемь групп по два элемента. Входы WE (запись) и адресные входы АО-А9 соединены друг с другом у всех 16 элементов и являются соответственно четвертым и вторым входами запоминающих устройств. Внутри групп входы CS (выборка кристалла) соединены, так что третьим входом запоминающего устройства являются входы С& восьми групп элементов.

Информационные входы 01-04 внутри групп не пересекаются, а между группами соединяются, так что первым входом запоминающего устройства являются входы D 1-1)4 одного и D1-D4 другого элемента восьми групп элементов. Коммутаторы 61 и 62 реализованы однотипно. Каждый содержит по три мультиплексора 21 1 (531КП11), входы 1-1, 1-2, 1-3, 1-4 одного элемента, а также 11 второго элемента являются первыми входами

коммутаторов 61 и 62. Входы 12, Г 3, 1-4 второго и 1-1, 1-2 третьего элементов являются вторыми входами коммутаторов, третьими входами которых являются входы 21 - 2-4 первого и второго элементов и 2-1, 2-2 третьего элемента. Выходы У1-У4 первого, второго и У1, У2 третьего элементов являются выходами коммутаторов 61 и 62. Входы управления DC являются четвертыми входами коммутаторов. Счетчик 65 результата -. шестиразрядный, реализован на двух элементах 155ИЕ5, вход первого элемента С2 является первым входом счетчика результата, выход 8 первого элемента соединен со входом С2 второго элемента. Выходы 2, 4, 8 обоих элементов являются выходом счетчика результата. Входы (сброс в ноль) обоих элементов соединены и являются вторым входом счетчика 65 результата. Регистр 66 результата реализован на двух элементах 155ТМ8, информационные входы которых являются первым входом регистра 66 результата, а входы синхронизации соединены и являются вторым

входом регистра 66 результата.

Блок 5 регистрации (фиг.7) содержит делитель на восемь 77, триггер 78, запоминающее устройство 79, элементы И 80 и 81, счетчик 82. Делитель на восемь 77 реализован на элементе 155ИЕ5, вход синхронизации С1 которого является входом делителя на восемь 77, выход 8 разрядов подключен ко входу R установки в ноль и является выходом делителя на восемь 77, триггер 78 реализован на элементе 155ТМ2, входы R , С ,S и выход Q которого являются соответственно первым, вторым, третьим входами и выходом триггера 78. Запоминающее устройство 79 реализовано на 16 элементах 552РУ1, адресные входы АО-А13 которых являются первым входом запоминающего устройства 79, вторым и третьим входом которого являются соответственно информационные .входы D 1 и входы разрешения записи WE всех эдементов. Элементы И 80 и 81 являются типовыми элементами 2 И 155ЛАЗ. Счетчик 82 реализован на четырех элементах 155ЛЕ5 с общим коэффициентом пересчета 2 . Вход С1 первого элемента является входом счетчика 82, а выходы 1, 2, 4, 8 первого, второго и третьего и выходы 1, 2, 4 четвертого 13 элементов являются выходом счетчика Блок 6 дифференцирования (фиг,84 содержит сдвиговый рех-истр 83, вычитатель 84, элемент 85 задержки, вычитатель 86, регистр 87, сумматор 88,регистр 89. Регистр 83 предназначен для запоминания строки видеосигнала, поэтому он реализован на 512 парах D -триггеров (155ТМ7). Каж лая пара элементов позволяет фиксировать шестиразрядный код яркости одного элемента разложения. Входы последукнцих за первой пар элементов подключены к выходам предыдущих пар Выходы первой и последней пар являют ся соответственно первым и вторым вы ходами регистра 83, первым и вторым входами которого являются соответственно информационные входы первой пары элементов и соединенные входы синхронизации всех пар элементов. Элемент 85 задержки реализован на элементе 2И (155ЛИ1), входы и выход которого являются соответственно входом и выходом элемента 85 задержки. Вычитатели 84 и 86 являются одно типными и реализованы на двух полных сумматорах (155ИМЗ), входы А1-А4 и В1-В4 которых являются соответственно первыми и вторыми входами вычи- тателей 84 и 86, выходами которых являются выходы51-54 сумматоров. Регистры 87 и 89 являются однотипными. Каждый из них реализован на двух четырехразрядных D-триггерах (155ТМ5),D-входы, С-входы и информа ционные выходы которых являются соот ветственно первыми входами, вторыми входами и выходами регистров 87 и 89.Сумматор 88 реализован на двух полных сумматорах (155ШЗ), входы А1-А4, В1-В4 и выходы S1-S4 которых являются соответственно первыми и .. вторыми входами и выxoдa ш сумматора 88. Формирователь 7 порога (фиг.9) содержит элемент И 90, регистр 91, триггер 92, сумматор 93, вычитатель 94, триггер 95, перемножитель 96, регистр 97, элемент И 98, сумматор 99 и элемент 100 задержки. Элементы И 90 и 98 являются типовыми элементами 2И (155ЛИ1). Регистры 91, 97.являются однотипными. Каждьй из них реализован на двух четырехразрядных триггерах (155ТМ8), информационные входы которых являются пер 0314 выми входами регистров 91 и 97, вторыми и третьими входами которых являются соответственно соединенные у всех элементов входы установки в ноль (R) и входы синхронизации. Выходом регистра 97, как и первым выходом регистра 91, являются прямые выходы элементов (ф, а вторым выходом регистра 91 являются инверсные выходы его элементов (Q). Сумматоры 93 и 99 реализованы по типовой схеме на двух элементах 155ИМЗ, входы А, В и выходы S которых являются соответственно первыми и вторыми входами и выходами сумматоров 93 и 99. Вычитатель 94 реализован на двух элементах 155ИМЗ аналогично сумматорам 93 и 99 за исключением того, что вход Е первого элементна оставлен свободным. Триггеры 92 и 95 реализованы на элементах 155ТМ2 (П-триггер), входы , С и выходы Q и Q которых являются соответственно первыми и вторыми входами,- первыми и вторыми выходами триггеров 92 и 95, а выходы Q подключены ко входам р соответствующих элементов. Перемножитель 96 реализован на параллельном умножителе 8x8 (1802 ВР2), входы ХО-Х7, и УО-У7 которого являются соответственно первым и вторым входом пере- множителя 96, выходом которого являются выходы Р9-Р15 умножителя, третьим входом Которого являются входы записи операндов во внутренние регистры умножителя СЬКХ, CLKY, CLKP. Элемент 100 задержки реализован на двух последовательно соединенных элементах 2И (155ЛИ1), вход первого элемента, выход первого и выход второго элемента являются соответственно входом, первым выходом и вторым выходом элемента 100 задержки. Второй счетчик 8 (фиг.10) содержит счетчик 101, элемент 102 задержки, регистр 103, коммутатор 104. Счетчик 101 реализован на трех элементах 155ИЕ5, включенных в режиме счета с последовательным переносом. Вход С1, R. и выходы 1, 2, 4, 8 разрядов являются соответственно первым входом, вторым входом и выходом счетчика 101. Элемент задержки реализован на элементе 2И (155ЛИ1) аналогично описанному элементу 85 задержки. Регистр 1Q3 реализован на шести D триггерах(155ТМ2)5 входы R , S и С и выходы Я. которых являются соответственно третьим, вторым и первым входом и выходом регистра 103. Комму татор 104 реализован на переключателе ИПИШМ, входы и выход которого являются соответственно входом и выходом коммутатора 104. Первый элемент И9 реализован на элементе 2И (155ЛИ1), входы которого являются первым и вторым входами первого элемента И9, выходом которого является выход элемента 2И. Второй блок 10 памяти (фиг.11) содержит регистры 105 и 106, элемент И 107, счетчик 108, элементИ1 формирователь 110 импульсов записи, регистры 111-114, коммутатор 115, элемент И 116, счетчик 117, дешифратор 118, триггер 119, формирователь 120 импульсов сдвига, элемент ИЛИ 12 коммутаторы 122 и 123, триггер 124, счетчик 125 адреса считьшания, регистры 126 и 127, запоминающие устройства 128 и 129, элемент И 130, коммутатор 131, триггер 132, делител на тридцать два 133, запоминающие устройства 134 и 135, коммутаторы 136 и 137, элемент И 138 и 139, счетчик 140 результата, регистр 141 результата и регистр 142. Отличительной особенностью второго блока 10 памяти от первого блока 4 памяти .является наличие триггера 132,делителя на тридцать два 133 и регистра 142. Триггер 132 реализован на -Т) -триггере (155ТМ2), R , S, С входы которого являются соответствен но третьим, вторым и первым входами триггера 132, выходом которого является О.-выход Т)-триггера. Делитель на тридцать два 133 реализован на счетчике 155ИЕ8, работающем в. режиме деления на тридцать два. Для этого его управляющий вход / 32 заземлен, а вход синхронизации С и выход V являются соответственно входок и выходом делителя на тридцать два 133.Регистр 142 реализован на Е триггерах (два элемента 155ТМ5), входы С которых соединены и являются вторым входом регистра 142, первым входом И выходом которого являются соответственно информационные входы 1 и вькоды Q элементов. Первьш пороговый элемент 11 реализован на двух полных четырехразрядных сумматорах (155ИМЗ), включенных в режиме вычитания операнда В из операнда А, для этого вход Е1 первого сумматора оставлен свободным, входы А1-А4 сумматоров являются первым входом первого порогового элемента 11, вторым входом и выходом которого являются соответственно входы В1-В4 сумматоров и выход Р второго сумматора. Вычитание реализ.у ется благодаря тому, что операнд В представлен в дополнительном коде. Первый вычитатель 12 реализован на двух сумматорах (155ИМЗ) по известной схеме, входы А1-А4, В1-В4 и выходы сумматоров являются соответственно первым входом, вторым входом и выходом первого вычитателя 12. Вход Е1 первого сумматора оставлен свободным. Третий счетчик 13; реализован по известной схеме последовательного счетчика на пяти D-триггерах (155ТМ2), при этом вход С первого Ь-триггера является первым входом третьего счетчика. Входы R всех Т -триггеров соединены и являются вторым входом третьего счетчика, выходом которого являются выходы 0 всех пяти тэ -триггеров. Дпя организации внутреннего последовательного переноса выходы ( каждого D -триггера подключены ко входам С каждого последующего D -триггера и ко входам D тех же D -триггеров. Второй элемент И 14 является типовым элементом 2И-НЕ (155ЛАЗ), входы и выходы которого являются соответственно первым, вторым входами и выходом второго элемента И 14. Устройство работает следующим обра з.ом. С выхода датчика 1 видеосигнала в устройство поступают кадровые синхроимпульсы (КСИ), тактовые импульсы (ТИ), присутствующиеТОЛЬКО в активное время строк телевизионного разложения, т.е. во время прямого хода луча; параллельный двоичный код видеосигнала, формируемый в аналого-цифровом преобразователе датчика 1 видеосигнала. Блок 6 дифференцирования производит операцию двумерного дифференцирования сигнала яркости, поступающего на первый вход последнего, в апертуре растровых элементов. Дпя оценки двумерного перепада яркости в апертуре 2-2 необходимо определить сумму модулей приращений сигнала яркости между двумя соседними элементами по строке и по кадру. Опре деление приращения сигнала яркости

171

по строке производится с помощью вычитателя 86, на второй и первый вход которого поступают значения сигналов яркости соответственно текущего элемента и прерьщущего элемента разложе ния по строке. Определение приращения сигнала яркости по кадру (между соседними элементами двух смежных ; строк разложения) производится с помощью, вычитателя 84, на первый и вто рой входы которого поступают значени сигналов яркости соответственно текущего элемента разложения и предыдущего элемента разложения по кадру (т.е. соседнего элемента по вертикали), Запоминание сигналов яркости элементов разложения активной части строки производится сдвиговым регистром 83, на первый вход которого подается сигнал яркости с первого выхода датчика 1 видеосигнала, а на второй вход - задержанйый тактовый импульс, по которому производится запись сигнала яркости текущего элемента и сдвиг уже записанных сигналов яркоети. Задержка на запись и сдвиг вводится для того, чтобы успеть записать величины приращений сигналов яркости по строке и по кадру соответственно в регистр 87 и регистр 89, на первые входы которых поступают сигналы приращений, а на вторые входы - импульсы записи (тактовые импульсы). Оценка двумерного перепада яркости получается на выходе сумматора 88 непрерывно в течение всего эксперимента. Работа устройства в режиме распознавания контуров изображений объектов начинается с момента появления на первом входе устройства сигнала логической единицы (Пуск). Первым в работу включается формирователь 7 порога. По сигналу Пуск разрешается запись текущего сигнала яркости в регистр 91 и запись промежуточных результатов вычисления порогового эталонного сигнала в регистр 97, а также разрешается работа триггеров 92 и 95, которые совместно с элементом И 90 предназначены для вьщеления активной части первого кадра после прихода сигнала Пуск. Это вьщеление происходит следующим образом. Триггеры 92 и 95 включены таким образом, что со вторым кадровьм синхроимпульсом на втором выходе триггера 95 устанавливается логический ноль, за318

прещающий дальнейшее прохождение кадровых синхроимпульсов через элемент И 90 на счетный вход триггера 92. Со второго выхода триггера 92 снимается импульс, начинающийся с первым и кончающийся со вторым кадровым синхроимпульсом. Элемент И 98 разрешает прохождение тактовых импульсов на вход элемента 100 задержки во время активной части строк первого кадра, с первого выхода которого поступают импульсы записи промежуточных результатов вычислений на третий вход регистра 97, а со второго выхода на третий вход регистра 91 поступают импульсы записи текущих сигналов яркости. Регистр 91 предназначен для задержки сигналов яркости на время одного элемента разложения для вычисления разности и суммы яркостей соседних элементов по строке, что вычисляется соответственно вычислителем 94 и сумматором 93. Перемножение разностного и суммарного сигналов производится перемножителем 96, а накопление и вычисление промежуточных сумм произведений производится соответственно регистром 97 и сумматором 99. Таким образом, к концу первого кадра на выходе регистра 97 образуется суммарный сигнал, являющийся первым эталонным пороговым сигналом. По окончании процесса формирования первого эталонного порогового сигнала на первом выходе триггера 95 появляется, логическая единица (сигнал Конец формирования эталонного порога) , поступающая на пятый вход первого блока 4 памяти. Начинается второй кадр, за время которого производится запись в первый блок 4 памяти сигналов от элементов контура изображения объектов и фона, формируемых первым пороговым элементом 11, реализующим функцию вычитания первого эталонного порогового сигнала из суммарного сигнала двумерного перепада, поступающих соответственно с выходов первого вычитателя 12 и блока 6 дифференцирования. Вначале на второй вход первого вычитателя 12 поступает нулевой корректирующий пороговый сигнал с выхода третьего счетчика 13.

Рассмотрим запись сигналов от элементов контура изображения объектов и фона в йервьй блок 4 памяти. Началом записи является момент появления 191 сигнала логической единицы на пятом входе первого блока 4 памяти, являющимся входом схемы выделения активной части второго кадра, состоящей из элемента И 36, .триггера 46, триг гера 51 и элемента И 57, с выхода которого импульс начинающийся от зад него фронта второго кадрового импуль са и кончающийся с передним фронтом третьего кадрового импульса (фиг.12) поступает на вторые входы элементов И ЗА и 43, разрешая прохождение импульсов записи в запоминающие устройства 55, 56, 59 и 60. Сигнал выде ленных элементов контура изображения объекта и фона с выхода первого поро гового элемента 11, поступающий на четвертый вход первого блока 4 памяти, записывается в регистры 32 и 33 под действием тактовых импульсов. Записью в регистры управляет сигнал с третьего выхода счетчика 35, который является сигналомJ полученным при делении частоты тактовых импульсов на шестнадцать. Таким образом, восемь значений -сигналов от элементов контуров и фона записываются в регистр 32, а следующие восемь - в .регистр 33. В моменты записи входных сигналов в один регистр из другого регистра происходит считывание восьми последовательных значений сигналов от элементов контуров и фона и запись их в соответствующие ячейки памяти запоминающих устройств 55, 56, 59 и 60. Управление работой запоминающих устройств в режиме записи производится сигналами, формируемыми счетчиками 35, 44 и дещифратором 45. На первых выходах счетчиков 35 и 44, которые являются соответственно счет чиками элементов и счетчиком строк, присутствуют разряды с пятого по девятый каждого счетчика. Разряды счетчика 44 с первого по четвертый поступают на второй вход дешифраторе 45, выходные сигналы которого представляют собой сигналы выбора одной из шестнадцати пар корпусов ОЗУ запоминакяцих устройств 55, 59 или 56, 60. Точное определение номера пары корпусов запоминающих устройств номера 1-8 принадлежит запоминающим устройствам 55 и 56, а номера 9-16 соответственно запрминающим устройствам 59 и 60. Выбор пары запоминающих устройств (55 и 59 или 56 и 60) производится с помощью сигналов за320писи с третьих выходов элеме}гтов И 34 и 43. При такой opгaнизaц m памяти оказалось возможным записать, например, сигналы от элементов матрицы 8 эл. X 8 эл. таким образом, что они оказались в ячейках памяти одного запоминающего устройства, имею1цих одинаковые адреса, что оказалось удобным при считывании из блоков памяти (как первого блока 4 памяти, так и второго блока 10 памяти По окончании записи сигналов от элементов контуров изображений объектов и фона появляется уровень логической единицы на втором выходе триггера 51 (конец записи в первый блок памяти), поступающий на третий вход второго счетчика 8. Начинается цикл корректировки (уменьшения) первого порогового эталонного сигнала на втором входе первого порогового элемента 11. Первым этапом корректировки является подсчет количества связных элементов контура объекта вдоль строки. Этот подсчет производится первым счетчиком 2, на первый вход которого поступают сигналы с выхода второго элемента И 14, который необходим для работы первого счетчика 2, поскольку с выхода первого порогового элемента поступает сигнал, свидетельствующий лшиь о наличии контура, а не о его протяженности. Появление каждого очередного импульса на выходе первого счетчика 2 свидетельствует о том, что обнаружена последовательность связных элементов контура изображения объекта и фона вдоль строки, число которых превышает заданное, например 4, установленное с помощью коммутатора, подключенного к выходным разрядам первого счетчика 2. Вторым этапом корректировки (уменьшения) первого эталонного порогового сигнала является подсчет общего числа вьщеленных связных элементов контура изображения объекта и фона и сравнение подсчитанного числа выделенных элементов с эталонным числом связных элементов. Этот подсчет и сравнение производится вторым счетчиком 8. На первый вход счетчика 101 поступают сигналы от групп связных элементов вдоль стро- ки. Подсчет числа связных элементов контура изображения объекта и фона с точностью до числа элементов в группе по группам ведется на протяжении

активной части кадра. Сброс показаний счетчика 101 производится по кадровому синхроимпульсу, с момента появления сигнала конца записи в первый блок памяти на третьем входе регистpa 103 последний начинает выполнять свою функцию, а именно фиксировать максимальное состояние счетчика 101 к концу кадра, а так как сброс регистра 103 задержан с помощью элемента 102 задержки относительно кадрового синхроимпульса, то сигнал превышения числа связных элементов по кадру заданного эталонного числа связных элементов, выбираемого с помощью коммутатора 104, удерживается на первом входе первого элемента И 9 в течение кадрового синхроимпульса (гасящий кадровый)о Таким образом, на выходе второго счетчика 8 присутствует логическая единица до тех пор, пока не произойдет превышение измеренного числа связных элементов контура изобралсения объекта и фона заданной эталонной величины. До тех пор пока на выходе второго сметчика 8 - логическая единица, чере: первьй элемент И 9 кадровые синхроимпульсы поступают на первый вход третьего счетчика 13, состояние которого является величиной, корректирующей первый эталонный пороговый сигнал путем вычитания из первого эталонного порогового сигнала, поступающего, на пе1эвый вход первого вычитателя 12, корректз-гоующего сигнала, поступающего на второй вход последнего. Корректировка продолжается до тех пор, пока на выходе второго счетчика 8 не появится логический ноль, что свидетельствует одно временно о конце корректировки первого эталонного порогового сигнала и о начале записи сигналов от выделенных и корректируюшрнх элементов контура изображения объектов и фона при скорректированном (уменьшенном) эталонном пороговом сигнале по критерию максимальной связности элементов контура изображения объекта и фона. Таг: КИМ образом, завершается процесс уменьшения порогового эталонного сигнала, после чего осуществляется вьзделение корректирующих элементов контура изображения объекта и фона путем сравнения сумм абсолютных значений разностей амплитуд сигналов яркости от элементов изображения объекта и фона с уменьшенным

noporoBbiM эталонным сигналом. Процесс записи массива сигналов от элементов контура при скорректированном пороговом эталонном сигнале во второй блок 10 памяти происходит аналогично описанному процессу записи в первый блок памяти. По окончании записи во второй блок 10 памяти на четвертом выходе последнего по-,, является уровень логической единицы поступающий на первый вход первого блока 4 памяти и разрешает считывание иа последнего, а также и из второго блока 10 памяти, где является внутренним сигналом.

Считывание из обоих блоков 4 и 10 памяти должно производиться синхронно, поэтому рассмотрим процесс считывания из второго блока 1Q памяти, который начинается с того, что разрешается работа формирователя 110 имггульсов записи, формирователя 120 импульсов сдвига и счетчика 125 адреса считывания. На втором выходе фор1Шрователя 110 импульсов записи появляется импульс, поступающий на первые входы регистров 111-114 и под его управлением производится загшсь выходной информации с запомиЧ яа ся1их устройств 128, 129, 134 и 135 Как указывалось при рассмотрении процесса записи, в шестидесяти четырех ячейках каждого запоминающего устройства, доступных по одному адресу, находятся значения сигналов- от элементов контуров изображений объектов и фона, расположенных в матрице () элементов. Таким образом, считывая одновременно из четырех запоминающих устройств 128, 129, 134 и 35 значения сигналов от четырех таких матриц, расположенных так, что они образуют общую матрицу 16x16 элементов, записывая их в регистры 111-114, а затем переписывая содержимое двух, регистров 111 и 113 или 112 и 114 через коммутаторы 122 и 123 в регистры 126 и 127, появляется возможность путем сдвига сигналов, записанных в регистры 126 и 127 (а именно здесь находятся сигналы от элементов контуров изображений объектов и фона двух матриц элементов, расположенных одна под другой), и накопления этих сигналов в счетчике 140 результата вычислять количество элементов контуров изображений объектов и фона, находящихся в пределах матрицы 88 эле ментов разложения. При этом одновременно получаются результаты о всех восьми матрицах, что происходит путем перемещения окна 8-8 элементов вертикально вниз по матрице 8-16, полученной из двух матриц, находящих ся в регистрах 126 и 127 и переписанных туда под действием сигнала со второго выхода формирователя 110 импульсов записи. Сдвиг содержимого регистров 126 и 127 производится под действием импульсов, поступающих с третьего выхода формирователя 120 импульсов сдвига и являющихся тактовыми импульсами, стробированными режимом считывания из блоков 4и 10 памяти. По проществии 64 тактовых импульсов на втором выходе формирователя 120 импульсов сдвига сформируется импульс, по которому переписывается состояние счетчика 140 результата в регистр 141 результата, обнуляется счетчик 140 результата, происходит сдвиг содержимого регистров 111-114 таким образом, что при следующей записи в регистры 126 и 127 в них также формируется матрица 816 элементов, при этом центр этой матрИ1№1 уже сдвигается по отношению к центру такой же матрицы в предьщущем ау1кп& .на один элемент разложения вдоль строки. Таким образом,за очередные 64 тактовых импульса в счетчи ке 140 результата оказываются резуль таты суммирования сигналов от элеме тов контуров изображений объекта и фона в очередных восьми матрицах В элементов. Результаты накопления в счетчике 140 результата переписываются в регистр результата 141, откуд они поступают в арифметико-логически блок 3. Переход к следующей матрице элементов по строке связан с необходимостью сменить адрес лишь у запоминающего устройства 129, а так как считьшание из запоминающих устройств 128, 129, 134 и 135 производится в те же регистры 111-114, то для верного движения окна необходимо изменить направление сдвига в регистрах 111-114 на противоположное, что и делается путем изменения выбранного для считывания регистра (111 или 112 113 или 114) через коммутаторы 122 и 123. Для реализации описанного движения окна по столбцу и по строке счетчик 125 адреса считывашш содержит два счетчика 71 и 72, состояния которых являются адресами соответственно запоминающих устройств 129, 135 и 128, 134, При этом счетчик 71 считывает каждый второй импульс окончания сдвига окна, начиная со второго, а счетчик 72 - каждый второй импульс окончания сдвига окна, начиная с первого. Такой режим достигается применением делителя на два 68. Такая же асинхронность необходима и при сдвиге матрицы 16-16. элементов (по отнощению к первому проходу вдоль строк) на восемь элементов вниз по столбцу (по кадру). Эта асинхронность в работе счетчиков 73 и 74 достигается с помощью делителя на два 69 с противофазными выходами. Сброс обоих делителей на два 68 и 69 осуществляется при помощи дешифрации конечных состояний счетчиков 72 и 74 дешифраторами соответственно 75 и 76. Процесс вычисления плотностей вероятностей появления корректирующих элементов проводится одновременно со считьгоанием сигналов от элементов контуров изображений объектов и фона из первого блока 4 памяти и из второго блока 10 памяти. Вычисление вероятностей появления корректирующих элементов ведется при каждом положении окна 8-8 элементов и начинат ется каждый раз по сигналу, приходящему с выхода триггера 132 (начало обработки .АЛУ) на третий вход .арифметико-логического блока 3, на первый и второй входы которого приходят величины суммарных сигналов от элементов контуров соответственно из второго to и из первого 4 блока памяти. Количество корректирующих элементов определяется нахождением разности сигналов соответственно с первого и со второго входов арифметикологического блока 3. Эту операцию выполняет второй вычитатель 18. Нахождение отношения числа корректирующих элементов окна к общему числу обнаруженных элементов производится делителем 19 по стандартной схеме сдвига делимого и проверке разряда переноса при вычислении остатка от деления на каждом шаге. Работой делителя 19 управляет дешифратор 27, выдающий гребенку импульсов, первый из которых производит запись входного числа в регистр 25. В дальнейшем 251 коммутатор 21 закрыт для первого входа делителя 19 и в регистр 25 записываются только результаты вычисления остатков, которые в зависимости от разряда переноса со второго и третьего выходов вычитателя 28 либо сдвигаются влево, либо деление продолжается. Результат деления (разряд переноса вычитателя 28) накапливается в регистре 25, куда результаты переноса сдвигаются импульсами с дешифратора 27, и вводится во второй пороговый элемент 20. Результат этого сравнения поступает на третий вхо блока 5 регистрации и записьюается там при наличии разрешения, приходящего с соответствующего разряда регистра 142, где находятся значения сигналов от злементов контуров, расположенных в центре окна. Только при наличии обоих сигналов принимаПервыйвход 3 ется решение о наличии элемента контура в данном месте. Таким образом, реализованные в устройстве выделение корректирующих элементов контура изображения объекта и фона и оценка вероятностей обнаружения этих злементов в окрестностях каждого из вьщеленных элементов контура позволяют соответственно зарегистрировать без разрывов элементы контура изображения объекта и устранить практически все элементы ложных контуров. Поскольку при заданных отношениях сигнал/шум вероятности обнаружения элементов ложных контуров лежат в пределах 0,2-0,4, предложенное устройство позволяет в 1,2-1,6 раза по сравнению с прототипом повысить достоверность распознавания контуров изображений размерных объектов в условиях низкого контраста изображения и пространственных помех.

Фиг.г

Фи1.Ъ

оь/ход Впока

второй

ui.k

Фиг.8

выход 5лока

Фиг.Ю

t

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР № 754453, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР №760133, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-05-15—Публикация

1983-12-27—Подача