Изобретение относится к вычислительной технике, в частности к технике аналоговых.запоминающих устройств, и может быть использовано при построении аналого-цифровых пре- 5 обраэователей (АЦП).

Известно аналоговое запоминающее устройство, содержащее компаратор, цифро-аналоговый преобразователь, элементы И, счетчик и усилитель (11 . О

Недостатком устройства является сравнительно большое время выборки входного сигнала, обусловленное временем отслеживания входного сигнала через цепь отрицательной обратной tS связи (ООС), содержащую компаратор напряжения, реверсивный счетчик и цифротаналоговый-преобразователь (ЦАП). Кроме того, точность выборки в зтих устройствах принципиально 20 ограничена шагом квантования (разрядностью) ЦАП.

Наиболее близким к предлагаемому по технической сущности является аналоговое запоминающее устройство, лизованное на основе АЦП параллельного типа и содержащее компараторы, инвертирующие входы которых объединены и являются входом устройства, а неинвертирующие подключены соответ-зо ственно к выходам формирователя опорных напряжений, выходы компараторов через схемы стробирования подключены к блоку памяти, в котором происходит запоминание выбранного значения вход- с ного сигнала в виде унитарного цифрового кода. Состояние блока памяти считывается посредством кодирующей логики и далее поступает на ЦАП, на выходе которого уже образуется выбран- о ное значение входного сигнала в аналоговой форме Г21.

Недостатком данного устройства является низкая точность, обусловленная. ограниченной точностью и разрядноетью АЦП;

Целью изобретения является повышение точности устройства.

Поставленная цель достигается тем, что и аналоговое запоминающее уст- 50 ройство, содержащее компараторы с паятью, первые входы которых являются входом устройства, вторые входы компараторов соединены с шиной управления ,формирователь опорных напряженип 55 выходы которого соединены с третьими ходами компараторов, усилитель, выод которого является выходом устройства,, блок памяти, введен сумматор, входы группы которого соединены с выходами компараторов, выход сумматора соединен с инвертирующим входом усилителя, неинвертирующий вход которого соединен с выходом блока памяти, первый вход блока памяти соединен с выходом усилителя, второй вход блока памяти является входом устройства, а третий вход блока памяти соединен с шиной управления, вход сумматора соединен с последним выходом формирователя опорных напряжений.

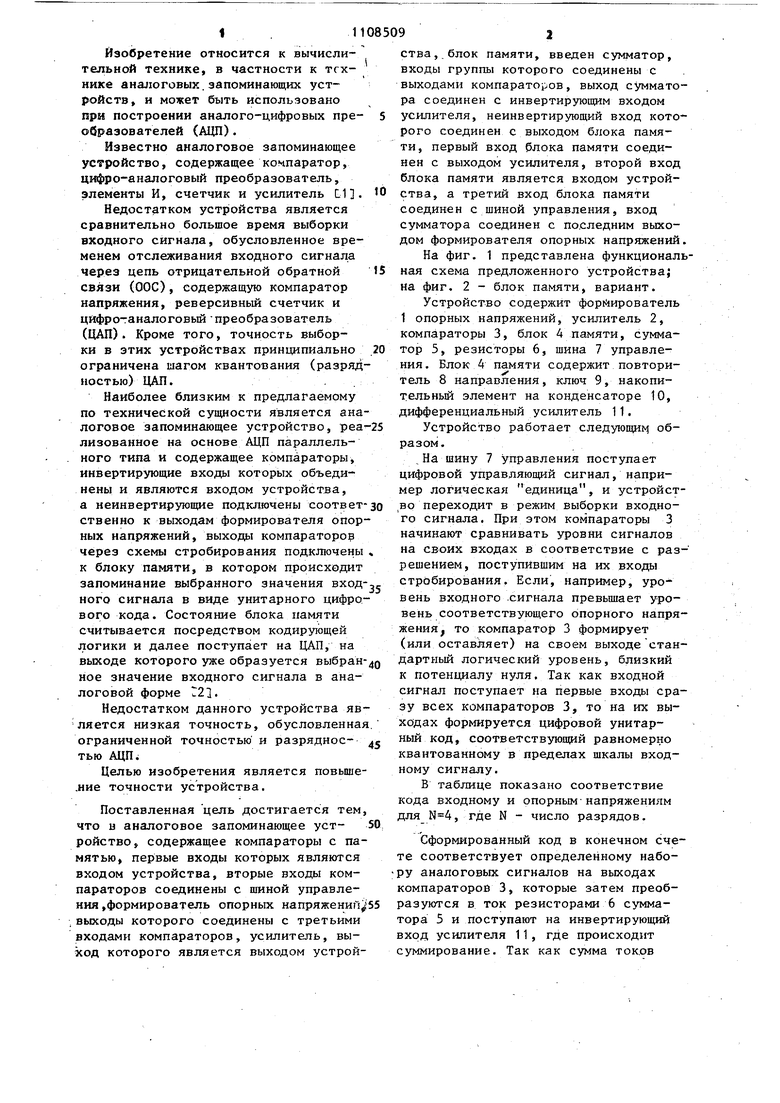

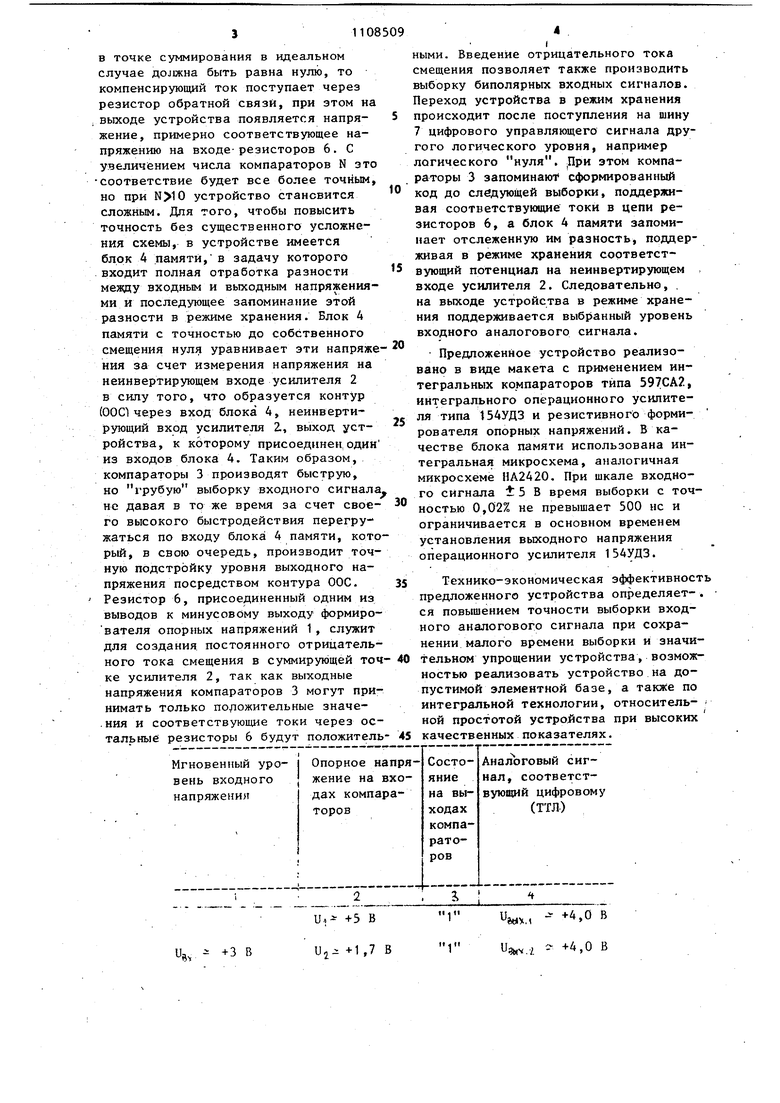

На фиг. 1 представлена функциональная схема предложенного устройства; на фиг. 2 - блок памяти, вариант.

Устройство содержит формирователь 1 опорных напряжений, усилитель 2, компараторы 3, блок 4 памяти, сумматор 5, резисторы 6, шина 7 управления. Блок 4 памяти содержит повторитель 8 направления, ключ 9, накопительньй элемент на конденсаторе 10, дифференциальный усилитель 11.

Устройство работает следующим образом.

На шину 7 управления поступает цифровой управляющий сигнал, например логическая единица, и устройство переходит в режим выборки входного сигнала. При этом компараторы 3 начинают сравнивать уровни сигналов на своих входах в соответствие с разрешением, поступившим на их входы стробирования. Если, например, уровень входного .сигнала превьш1ает уровень соответствующего опорного напряжения то компаратор 3 формирует (или оставляет) на своем выходе стандартньш логический уровень, близкий к потенциалу нуля. Так как входной сигнал поступает на первые входы сразу всех компараторов 3, то на их выходах формируется цифровой унитарный код, соответствующий равномерно квантованному в пределах шкалы входному сигналу.

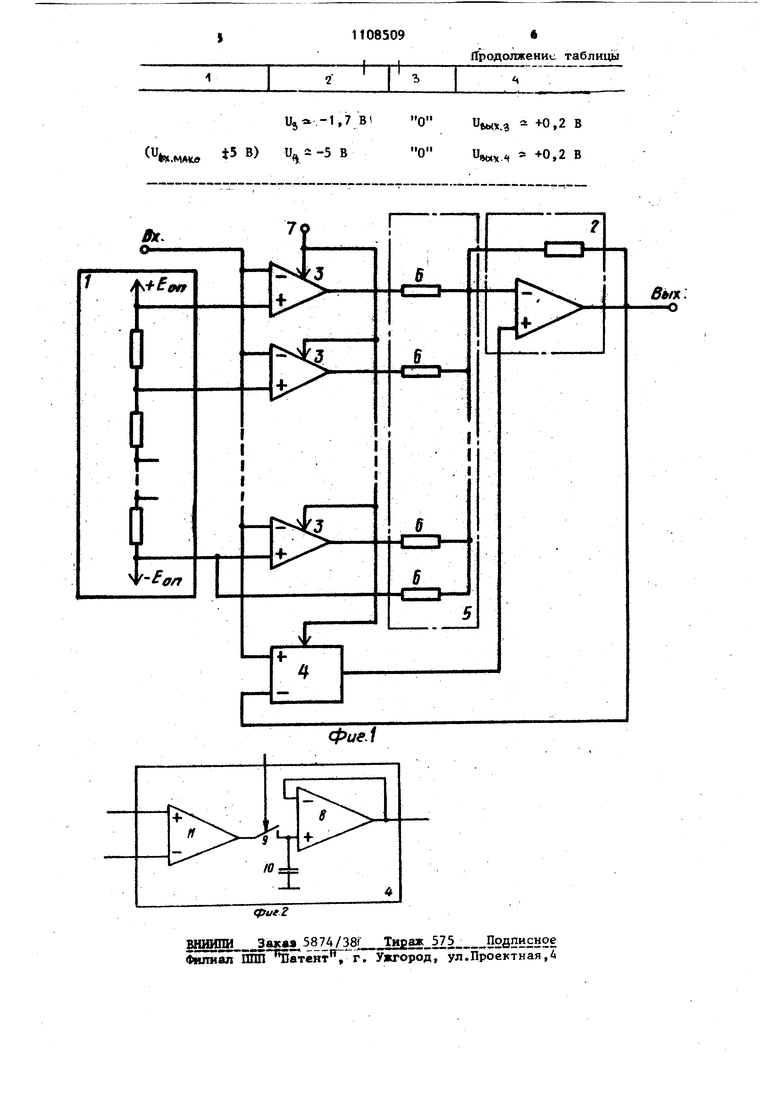

В таблице показано соответствие кода входному и опорнымнапряжениям ля , где N - число разрядов.

Сформированный код в конечном счее соответствует определенному набоу аналоговых сигналов на выходах омпараторой 3, которые затем преобазуются в ток резисторами 6 суммаора 5 и поступают на инвертирующий ход усилителя 11, где происходит уммирование. Так как сумма токов в точке суммирования в идеальном случае должна быть равна нулю, то компенсирующий ток поступает через резистор обратной связи, при этом на , выходе устройства появляется напряжение, примерно соответствующее напряжению на входе-резисторов 6. С увеличением числа компараторов N это соответствие будет все более точным, но при устройство становится сложным. Для того, чтобы повысить точность без существенного усложнения схемы, в устройстве имеется блок 4 памяти, в задачу которого входит полная отработка разности между входным и выходным напряжениями и последующее запоминание этой разности в режиме хранения. Блок 4 памяти с точностью до собственного смещения нуля уравнивает эти напряжб ния за счет измерения напряжения на неинвертирующем входе усилителя 2 в силу того, что образуется контур (ООО через вход блока 4, неинвертирующий вход усилителя 2., выход устройства, к которому присоединен, один из входов блока 4. Таким образом, компараторы 3 производят быструю, но грубую выборку входного сигнала не давая в то же время за счет своего высокого быстродействия перегру жаться по входу блока 4 памяти, кото рый, в свою очередь, производит точную подстройку уровня выходного напряжения посредством контура сое. Резистор 6, присоединенный одним из выводов к минусовому выходу формирователя опорных напряжений 1, служит для создания постоянного отрицательного тока смещения в суммирук1щей точ ке усилителя 2, так как выходные напряжения компараторов 3 могут принимать только по южительные значе.ния и соответствующие токи через ос тальные резисторы 6 будут положител ными. Введение отрицательного тока смещения позволяет также производить выборку биполярных входных сигналов. Переход устройства в режим хранения происходит после поступления на шину 7 цифрового управляющего сигнала другого логического уровня, например логического нуля. .При этом компараторы 3 зaпoминaюt сформированный код до следующей выборки, поддерживая соответствующие токи в цепи резисторов 6, а блок 4 памяти запоминает отслеженную им разность, поддерживая в режиме хранения соответствующий потенциал на неинвертирующем , входе усилителя 2. Следовательно, , на выходе устройства в режиме хранения поддерживается выбранный уровень входного аналогового сигнала. Предпоженное устройство реализовано в виде макета с применением интегральных компараторов типа 597СА., интегрального операционного усилителя типа 154УДЗ и резистивного формирователя опорных напряжений. В качестве блока памяти использована интегральная микросхема, аналогичная микросхеме НА2420. При шкале входного сигнала 1 5 В время выборки с точностью 0,02% не превышает 500 не и ограничивается в основном временем установления выходного напряжения операционного усилителя 154УДЗ. Технико-экономическая эффективность предложенного устройства определяет- . ся повышением точности выборки входного аналогового сигнала при сохранении малого времени выборки и значительном упрощении устройства, возможностью реализовать устройство на допустимой элементной базе, а также по интегральной технологии, относительной простотой устройства при высоких качественных показателях.

| название | год | авторы | номер документа |

|---|---|---|---|

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1181144A1 |

| СОСТАВНОЙ БЫСТРОДЕЙСТВУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2006 |

|

RU2311731C1 |

| ИЗМЕРИТЕЛЬ ПОТЕРЬ МОЩНОСТИ (ВАРИАНТЫ) | 2011 |

|

RU2467337C2 |

| Устройство преобразования синусно-косинусных сигналов в код | 1983 |

|

SU1104567A1 |

| Цифровой регистратор повторяющихся сигналов | 1987 |

|

SU1610279A1 |

| ФОРМИРОВАТЕЛЬ ТРЕХФАЗНЫХ ГАРМОНИЧЕСКИХ СИГНАЛОВ | 2014 |

|

RU2553418C1 |

| Устройство для автоматического контроля параметров интегральных схем | 1988 |

|

SU1649474A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ИЗМЕНЕНИЯ МОЩНОСТИ НАГРУЗКИ ТОКОВЕДУЩИХ ЭЛЕМЕНТОВ СИСТЕМ ЭЛЕКТРОСНАБЖЕНИЯ | 1994 |

|

RU2079886C1 |

| УСТРОЙСТВО СЛЕДЯЩЕГО ТИПА ДЛЯ ОПРЕДЕЛЕНИЯ МОДУЛЯ ВТОРОЙ ОРТОГОНАЛЬНОЙ СОСТАВЛЯЮЩЕЙ ВЕКТОРА | 2000 |

|

RU2187839C2 |

АНАЛОГОВОЕ ЗАПОМИНМЩЕЕ УСТРОЙСТВО, содержащее компараторы с памятью, первые входы которых являются входом устройства, вторые входыI компараторов соединены с шиной управ ления, формирователь опорных напряжений, выходы которого соединены с третьими вхадами компараторов, усилитель, выход которого является выходом устройства, блок памяти, о тл и ч а ю щ е е с я тем,, что, с целью повышения точности устройства, в него введен сумматор, входа группы которого соединены с выходами компараторов, выход сумматора соединен с инвертирующим входом усилителя, меинвертирующий вход которого соединен с выходом блока памяти, первый вход памяти соединен с выходом усилителя , второй вход блока памяти является входом устройства, а третий вход блока памяти соединен с шиной управления, вход сумматора соединен с последним выходом формирователя опорных напряжений.

Uii, 3 В

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Бахтиаров Г.Д | |||

| и др.Аналогоцифровые преобразователи, М., Советское радио,.1980, с | |||

| Способ применения резонанс конденсатора, подключенного известным уже образом параллельно к обмотке трансформатора, дающего напряжение на анод генераторных ламп | 1922 |

|

SU129A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Там же, с.130-131 (прототип); | |||

Авторы

Даты

1984-08-15—Публикация

1982-11-03—Подача